## **Linear Regulator Series**

## **BDxxFA1 Series Application Information**

The information in this application note only provides hints for IC mounting. For this reason, these notes should not be considered as an IC quality explanation or a warranty. See the latest data sheet for the IC standard values. Also, note that the application circuits used in the explanations for each item have been simplified. Be sure to verify operations using the actual application.

#### Table of contents

| 1. Typical Application Circuit                                  | 2  |

|-----------------------------------------------------------------|----|

| 1.1. Adjustable output type BD00FA1WEFJ                         |    |

| 1.2. Fixed output type BDxxFA1MG-M                              |    |

| 1.3. Fixed output type BDxxFA1FP3                               |    |

| 2. Output voltage setting (Adjustable output type)              |    |

| 3. Kelvin connection                                            |    |

| 4. Output voltage tolerance                                     | 6  |

| 5. Study of input/output voltage difference and characteristics | 7  |

| 6. Output control (EN) pin                                      | 7  |

| 7. Output capacitor                                             |    |

| 8. Input capacitor                                              |    |

| 9. Load                                                         |    |

| 10. Efficiency                                                  | 10 |

| 11. Thermal design                                              | 11 |

| 12. Terminal protection                                         | 18 |

| 13. Soft start                                                  | 21 |

| 14. Sequence for turning power on                               | 22 |

| 15. Sequence for turning power off                              | 26 |

| 16. Inrush current                                              | 29 |

| 17. Over current protection (OCP)                               | 30 |

| 18. Thermal shutdown (TSD)                                      | 30 |

| 19. Input-output equivalent circuit                             | 31 |

## 1. Typical Application Circuit

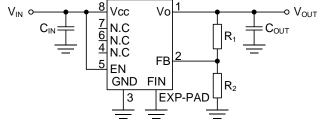

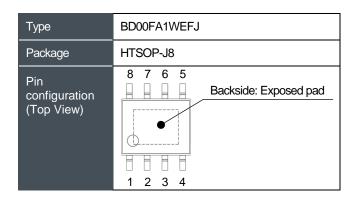

## 1.1. Adjustable output type BD00FA1WEFJ

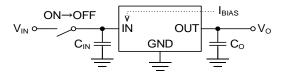

Figure 1-1. When using the output ON/OFF function

Figure 1-2. When not using the output ON/OFF function

| Pin<br>number | Pin<br>name | Function                                                                                                                                                                                                                                                                                      |

|---------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | Vo          | Output pin Supplies electrical power to the load. To prevent vibrations on this pin, connect Vo and GND with a capacitor. → See page 8.                                                                                                                                                       |

| 2             | FB          | Output voltage setting pin  The FB pin is a tolerance amp input pin. Based on the ground, the FB pin voltage can be outputted from 3.0 V to 12 V at 0.8 V. Connect a resistor divider circuit. → See page 5.                                                                                  |

| 3             | GND         | Ground This is the ground for the regulator circuit.                                                                                                                                                                                                                                          |

| 4             | N.C         | Unconnected pin This is not connected to the internal circuit. Leave this open or connect GND.                                                                                                                                                                                                |

| 5             | EN          | Enable pin  The IC can be set to shutdown status by using the EN pin. Set to the pin to "High" to turn output on, and to "Low" to turn output off. → See page 7.                                                                                                                              |

| 6, 7          | N.C         | Unconnected pin This is not connected to the internal circuit. Leave this open or connect GND.                                                                                                                                                                                                |

| 8             | Vcc         | Input pin  Power is supplied to the IC through the input pin. To stabilize the pin input, connect Vcc and GND with a ceramic capacitor. Place the capacitor near the pin. → See page 9.                                                                                                       |

| EXP-PAD       | FIN         | Exposed pad  The exposed pad is connected to the die via the lead frame. We recommend soldering exposed pad to a ground plane with a wide copper foil area to improve heat dispersion efficiency. Also, exposed pad is electrically connected to GND in the package internally via substrate. |

## 1. Typical Application Circuit

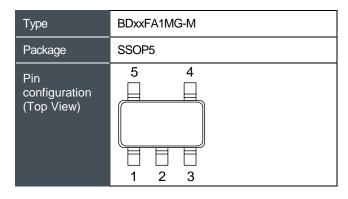

## 1.2. Fixed output type BDxxFA1MG-M

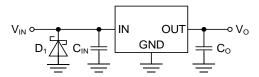

Figure 1-3. When using the output ON/OFF function

Figure 1-4. When not using the output ON/OFF function

| Pin<br>number | Pin name | Function                                                                                                                                                                                            |

|---------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | Vcc      | Input pin  Power is supplied to the IC through the input pin. To stabilize the pin input, connect Vcc and GND with a ceramic capacitor. Place the capacitor near the pin. $\rightarrow$ See page 9. |

| 2             | GND      | Ground This is the ground for the regulator circuit.                                                                                                                                                |

| 3             | EN       | Enable pin  The IC can be set to shutdown status by using the EN pin. Set to the pin to "High" to turn output on, and to "Low" to turn output off. → See page 7.                                    |

| 4             | N.C      | Unconnected pin This is not connected to the internal circuit. Leave this open or connect GND.                                                                                                      |

| 5             | Vo       | Output pin Supplies electrical power to the load. To prevent vibrations on this pin, connect Vo and GND with a capacitor. → See page 8.                                                             |

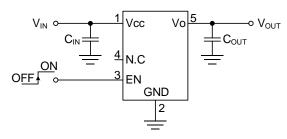

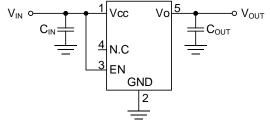

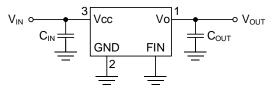

## 1. Typical Application Circuit

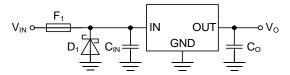

## 1.3. Fixed output type BDxxFA1FP3

Figure 1-5. Typical application circuit

| Pin<br>number | Pin name | Function                                                                                                                                                                                                                                                         |

|---------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | Vo       | Output pin Supplies electrical power to the load. To prevent vibrations on this pin, connect Vo and GND with a capacitor. → See page 8.                                                                                                                          |

| 2             | GND      | Ground This is the ground for the regulator circuit.                                                                                                                                                                                                             |

| 3             | Vcc      | Input pin  Power is supplied to the IC through the input pin. To stabilize the pin input, connect Vcc and GND with a ceramic capacitor. Place the capacitor near the pin. → See page 9.                                                                          |

| -             | FIN      | Heat radiation fins, Ground FIN is electrically connected to GND in the package internally. The FIN is connected to the die via the lead frame. We recommend soldering FIN to a ground plane with a wide copper foil area to improve heat dispersion efficiency. |

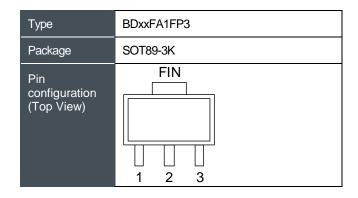

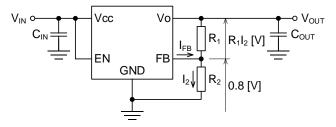

# 2. Output voltage setting (Adjustable output type)

Adjustable output voltage types use an external resistor divider, allowing the output voltage to be set from 3.0 V to 12 V. The output voltage can be calculated with the following equation.

$$V_{OUT} = 0.8 \times \frac{R_1 + R_2}{R_2} \quad [V]$$

(2-1)

Figure 2-1. Output voltage setting

The FB pin of this IC outputs at 0.8 V, based on the ground. The  $I_2$  current of  $R_2$  can be calculated at 0.8 V/R2, with the addition of the bias current  $I_{FB}$  of FB pin. The bias current of the FB pin flows into the ground through  $R_2$  at approximately 0.4  $\mu A$ . To keep the output voltage tolerance down that occurs due to the FB pin's bias current, we recommend a value of 5k to  $30k\Omega$  for  $R_2$ . A smaller  $R_2$  value and a larger  $I_2$  value will allow the  $I_{FB}$  value to be ignored. The voltage of  $R_1$  multiplied by  $I_2$  added to 0.8 V is the output voltage  $V_{OUT}$ , as shown in the following equation.

$$V_{OUT} = 0.8 + R_1 I_2 = 0.8 + R_1 \frac{0.8}{R_2} = 0.8 \times \left(1 + \frac{R_1}{R_2}\right)$$

To obtain the optimum load regulation performance, directly connect the PCB traces to the bottom side of the output voltage setting resistor.

The setting resistance for a typical output voltage is shown next. In this example. The E24 series is used for the nominal resistance values. Use the same type of resistors for  $R_1$  and  $R_2$ . If different types are used, the ratio for  $R_1$  and  $R_2$  will change due to the differences in their tolerances and temperature characteristics, which may degrade the output voltage precision. When using chip resistances at or below a size of 0402 mm (01005 inch), select the parts while using caution for the rated power of the resistor and the maximum voltage.

Setting with minimum number of components

| Target<br>V <sub>O</sub> (V) | R <sub>1</sub> (kΩ) | R <sub>2</sub> (kΩ) | Calc.<br>V <sub>o</sub> ' (V) | Error<br>(%) |

|------------------------------|---------------------|---------------------|-------------------------------|--------------|

| 3                            | 33                  | 12                  | 3.000                         | 0            |

| 3.1                          | 18                  | 6.2                 | 3.123                         | + 0.728      |

| 3.2                          | 30                  | 10                  | 3.200                         | 0            |

| 3.3                          | 47                  | 15                  | 3.307                         | + 0.202      |

| 3.4                          | 39                  | 12                  | 3.400                         | 0            |

| 3.5                          | 51                  | 15                  | 3.520                         | + 0.571      |

| 3.7                          | 33                  | 9.1                 | 3.701                         | + 0.03       |

| 5                            | 43                  | 8.2                 | 4.995                         | - 0.098      |

| 5.4                          | 75                  | 13                  | 5.415                         | + 0.285      |

| 6                            | 33                  | 5.1                 | 5.976                         | - 0.392      |

| 6.3                          | 47                  | 6.8                 | 6.329                         | + 0.467      |

| 7                            | 100                 | 13                  | 6.954                         | - 0.659      |

| 8                            | 82                  | 9.1                 | 8.009                         | + 0.11       |

| 9                            | 160                 | 15                  | 9.333                         | + 3.704      |

| 10                           | 150                 | 13                  | 10.031                        | + 0.308      |

| 12                           | 130                 | 9.1                 | 12.229                        | + 1.905      |

High precision setting

| Target<br>Vo (V) | R <sub>1</sub> (kΩ) | R <sub>2</sub> (kΩ) | Calc.<br>Vo' (V) | Error<br>(%) |

|------------------|---------------------|---------------------|------------------|--------------|

| 3                | 33                  | 12                  | 3.000            | 0            |

| 3.1              | 33+1.5              | 12                  | 3.100            | 0            |

| 3.2              | 30                  | 10                  | 3.200            | 0            |

| 3.3              | 16+1.5              | 5.6                 | 3.300            | 0            |

| 3.4              | 39                  | 12                  | 3.400            | 0            |

| 3.5              | 33+0.75             | 10                  | 3.500            | 0            |

| 3.7              | 33                  | 9.1                 | 3.701            | + 0.03       |

| 5                | 51+1.5              | 10                  | 5.000            | 0            |

| 5.4              | 56+1.5              | 10                  | 5.400            | 0            |

| 6                | 47+18               | 10                  | 6.000            | 0            |

| 6.3              | 68+0.75             | 10                  | 6.300            | 0            |

| 7                | 75+18               | 12                  | 7.000            | 0            |

| 8                | 68+22               | 10                  | 8.000            | 0            |

| 9                | 120+3               | 12                  | 9.000            | 0            |

| 10               | 100+15              | 10                  | 10.000           | 0            |

| 12               | 130+10              | 10                  | 12.000           | 0            |

#### 3. Kelvin connection

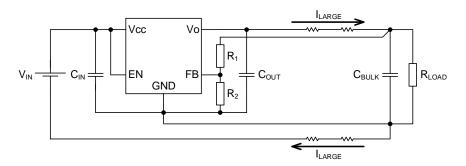

Normally, the optimum regulation can be achieved at the time that the output voltage setting resistor is connected to the Vo pin. For applications where the load current is frequent, the wiring width is narrow, the distance to the load is great and so on, the voltage may drop due to resistance in the PCB traces, which may result in a lower voltage at the load point. You can eliminate this influence by bringing the upper side of the output voltage setting resistance divider as close to the load as possible to connect. Place resistance voltage dividers with high impedance close to the IC and stretch out the traces on the upper side of the resistor with low impedance, to achieve noise tolerance. Connect the GND side of the IC as well using an independent ground trace to the load, so that it is not influenced by voltage drops in load current. As the IC's output capacitor Cout is used to prevent oscillation, place it close to the IC; and place a large capacitance capacitor CBULK close to the load to respond to abrupt loads (Figure 3-1).

## 4. Output voltage tolerance

The maximum output voltage tolerance for a fixed output type is the sum of the output voltage tolerance, the input constancy tolerance and the load constancy tolerance. For an adjustable output type, the maximum output voltage tolerance is the sum of the reference-voltage (FB terminal voltage V<sub>FB</sub>) tolerance times the tolerance external resistor for output voltage settings (see the following formula), the input constancy tolerance and the load constancy tolerance.

Output voltage tolerance for adjustable output type

Minimum value

$$V_{OUT(MIN)} = V_{FB(MIN)} \times \frac{R_{1(MIN)} + R_{2(MAX)}}{R_{2(MAX)}} \quad [V]$$

(4-1)

Maximum value

$$V_{OUT(MAX)} = V_{FB(MAX)} \times \frac{R_{1(MAX)} + R_{2(MIN)}}{R_{2(MIN)}} [V]$$

(4-2)

Figure 3-1. Kelvin connection (Adjustable output type)

## 5. Study of input/output voltage difference and characteristics

For the minimum value of the input voltage, the minimum input/output voltage at the load current to be used is read from the "Input/output voltage difference vs. output current" graph on the data sheet, to get the voltage added to the output voltage. As this time, this works as DC, but the control capacity is degraded. When there are fluctuations in the load, a large current cannot be supplied in a short period of time from input to output, as the input/output voltage difference is small. In other words, the load responsiveness will slow down. The slowness in responsiveness will also show up as a degradation in PSRR characteristics. If only the minimum voltage amount of the input/output voltage difference is ensured because efficiency is emphasized, the expected characteristics of the LDO will not be achieved. Increase the input voltage until the high-speed load responsiveness and PSRR capabilities are achieved, and find a compromise between efficiency and each characteristic.

## 6. Output control (EN) pin

The output can be turned on/off by using the EN pin. When EN is at a low level, Vo will turn off; and as the operations of the entire IC will be turned off, the current consumption will be zero. When EN is at the high level, the IC turns on, and Vo turns on. To make certain that IC is turned on/off, apply the voltage that is listed in the electrical characteristics on the data sheet for the EN pin voltage. For the designed reference values, the threshold median value is approximately 1.8 V, the tolerance is around  $\pm 0.2$  V, the temperature characteristic is around 1.9 V to 1.6 V ( $\pm 40$ °C to  $\pm 105$ °C), and overall is around 1.4 V to 2.1 V.

The EN pin is an output voltage on/off control pin and operates as a switch, but is designed based on the assumption that switching between High/Low on the normal EN input will be over a short time. Stabilize the EN pin at the midpoint potential of the High/Low switch. At the intermediate potential, the output voltage may become unstable.

There are no restrictions on the start sequence for Vcc and EN.

When not using the output control function, connect the EN pin to Vcc. At this time, a series resistor is unnecessary.

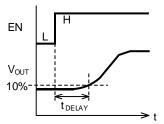

The delay time between when the EN pin reaches "High" and the output voltage starts is approximately 20 µs (design reference value; Figure 6-1).

Figure 6-1. Definition of startup delay time

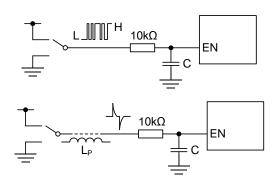

Controlling the EN pin via mechanical switch may cause chattering in the output voltage, due to chattering in the switch. Insert an RC filter before the EN pin, and make sure that the chattering waveform does not reach the EN pin (upper part of Figure 6-2). If the wiring between the EN pin and switch is long, a large pulse wave may be generated due to the inductance component of the wiring; and if this voltage exceeds the voltage capacity of the EN pin, the IC may break down. It is necessary to insert an RC filter before the EN pin, in order to lower the peak value of the pulse waveform (lower part of Figure 6-2). Change the C value to adjust the waveform.

Figure 6-2. RC filter circuit for EN pin

## 7. Output capacitor

Place the output capacitor within 3 cm of the Vo-GND pin IC, in order to stabilize the loop. Connect a capacitor with an actual capacitance of 1 µF or greater (BDxxFA1FP3 is 0.3 µF or greater), considering the tolerance and temperature characteristics. If the capacitance is too small, oscillation may occur. Although there is no limit to the maximum value for the output capacitance, the following points must be considered. Increasing the capacitance will lengthen the charging time when the power is on, and the discharging time when the power is off. Since it is possible that the IC can be damaged when turning off the power due to an input and output voltage inversion, which causes a large current to flow back into the IC, connect a reverse current bypass diode or a reverse current protection diode.

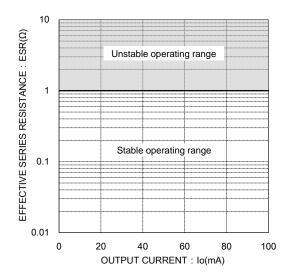

Figure 7-1. ESR stable operating range

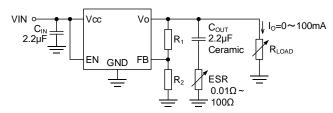

Figure 7-2. ESR stable operating range evaluation circuit

Refer to Figure 7-1 for the ESR. This graph is based on an evaluation circuit for Figure 7-2, and is not perfectly equal to the capacitor that is actually used. Also, as this is based on the IC alone and the resistive load, it will change in reality due to the

wiring impedance and input power impedance on the board. For this reason, check sufficiently whether there are oscillations by using the conditions of the final product.

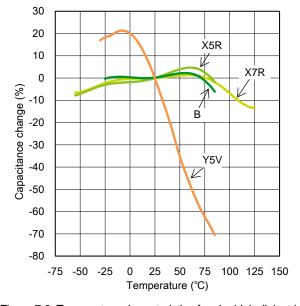

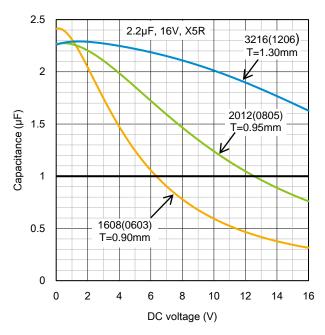

When using a ceramic capacitor, we recommend the use of an X5R or X7R, which have good temperature characteristics. Do not use Z5U, Y5V or F, which have large capacitance variances (Figure 7-3). Although the capacitance value will fall below the nominal value due to differences in tolerance, temperature characteristics and DC bias characteristics, set it so that the capacitance does not fall below the minimum value. For the DC bias characteristics, the capacitance tends to drop more with smaller sizes (Figure 7-4).

|     |          | Temperature Characteristic |                         |  |

|-----|----------|----------------------------|-------------------------|--|

| STD | STD Char | TEMP Range                 | Capacity Change<br>Rate |  |

| JIS | В        | -25 to +85 °C              | ±10%                    |  |

| EIA | X5R      | -55 to +85 °C              | ±15%                    |  |

| EIA | X7R      | -55 to +125 °C             | ±15%                    |  |

| EIA | X7U      | -55 to +125 °C             | +22%, -56%              |  |

| JIS | F        | -25 to +85 °C              | +30%, -80%              |  |

| EIA | Y5V      | -30 to +85 °C              | +22%, -82%              |  |

| EIA | Z5U      | +10 to +85 °C              | +22%, -56%              |  |

| EIA | Z5V      | +1010+65 C                 | +22%, -82%              |  |

Figure 7-3. Temperature characteristic of major high dielectric constant multilayer ceramic capacitor

Figure 7-4. DC bias characteristic of high dielectric constant multilayer ceramic capacitor, comparison by size

Although electrolytic capacitors are inexpensive and offer a large capacitance, caution must be used, as the electrolyte may harden at low temperatures, leading to a sudden drop in capacitance and an increase in ESR. Also, if the heat from the LDO reaches the electrolytic capacitor, the electrolyte will become hot, which has an impact on the lifespan of the capacitor. To resolve this, place the electrolytic capacitor further away so that it does not get too hot, or reduce the width of the copper wiring to the minimum current capacity tolerance, so that heat is not easily transmitted from the LDO.

If the fluctuations in the load current are abrupt, ripple voltage may occur in output. To reduce the ripple voltage, increase the capacitance of the output capacitor. Since ceramic capacitors with a large capacitance are expensive, you can reduce costs by adding an aluminum electrolytic capacitor, using small-capacitance ceramic capacitors in parallel as a bulk capacitor. Increasing the output capacitance will increase the electrical charge that charges the output capacitor from the input side. For this reason, a voltage drop may occur if the load responsiveness of the input side power is not good. To prevent this, use a larger input capacitor that is appropriate for the output capacitance.

## 8. Input capacitor

The purpose of the input capacitor is to keep down the phase fluctuations in the power line during circuit operations, stabilizing the IC input. When the input trace is particularly long or when the input power impedance is high, the input capacitor is effective in ensuring the stability of the LDO input power. Connect the capacitor within 1 cm of the Vcc-GND pin IC. The purpose of the input capacitor is to make the source impedance smaller. For this reason, we recommend a ceramic capacitor with a small ESR. Connect a capacitor with an actual capacitance of 1 µF or greater (BDxxFA1FP3 is 0.3 µF or greater). Although the capacitance value will fall below the nominal value due to differences in tolerance, temperature characteristics and DC bias characteristics, set it so that the capacitance does not fall below the minimum value. If the output current changes drastically, increasing the capacitance of the output capacitor will reduce the ripple voltage. However, if there are momentary problems with the current supply potential on the input current side due to the larger output capacitor, the input voltage may drop. To prevent this, increase the capacitance of the input capacitor as well, so that it approximates the input capacitance. For the bulk capacitor, connect an aluminum electrolytic capacitor in parallel with the ceramic capacitor.

## 9. Load

As this IC has over current protection (OCP) characteristics resembling the number "7", when the load is a constant current source or when the output voltage is negative when starting up, the output voltage will not rise if the load current exceeds the IC output (supply) current, and the IC will fail to start up.

The IC will operate when the constant current load is on after the IC's output voltage is at the default value on startup; but afterwards, if the thermal shutdown circuit operates and the output goes off, the IC cannot be restarted. Further, if the IC cannot be started, constant current load will flow to the electrostatic breakdown protection diode (between Vo-GND). Due to this, the chip temperature will rise depending on the current value, which may result in destruction of the IC or solder melting. For this reason, use of constant current load is not recommended.

## 10. Efficiency

The efficiency can be calculated with the following equation.

$$\eta = \frac{P_{OUT}}{P_{IN}} = \frac{V_{OUT} \times I_{OUT}}{V_{CC} \times (I_{OUT} + I_{CC})} \times 100 \quad [\%]$$

(10-1)

$V_{CC}$ : Input voltage [V]  $V_{OUT}$ : Output voltage [V]  $I_{OUT}$ : Output current [A]  $I_{CC}$ : IC circuit current [A]

Note that when  $I_{\rm CC} \ll I_{\rm OUT}$ , efficiency can be calculated with the following equation.

$$\eta = \frac{V_{OUT}}{V_{CC}} \times 100 \quad [\%] \tag{10-2}$$

We can see from the equation that smaller voltage differences between inputs/outputs result in better efficiency.

## 11. Thermal design

To ensure highly reliable operations, it is necessary to make sure that the IC junction temperature does not exceed 150°C. The junction temperature estimate can be calculated using the following two methods.

1. When measuring the IC temperature using the surface temperature, use thermal characteristic parameter  $\psi_{JT}$  for the calculation. If the thermocouple can be firmly stabilized at the package surface center, the temperature  $T_T$  at the package surface center can be precisely measured. Because of this, the junction temperature can be calculated precisely by using this thermal characteristic parameter.

$$T_{I} = T_{T} + \psi_{IT} \times P \quad [^{\circ}C]$$

(11-1)

$T_T$ : Temperature at the center of the package surface [°C]

$\psi_{\mathit{IT}}$ : Thermal characteristics parameter from junction to center of package surface  $[^{\circ}C/W]$

P: IC consumption power [W]

P can be calculated by the IC consumption power using the following equation.

$$P = (V_{CC} - V_{OUT}) \times I_{OUT} + (V_{CC} \times I_{CC}) \quad [W]$$

(11-2)

$V_{CC}$ : Input voltage [V] $V_{OUT}$ : Output voltage [V]  $I_{OUT}$ : Output current [A]

$I_{CC}$ : IC circuit current [A]

Also, the peak output current that can flow constantly can be calculated with the following equation.

$$I_{OUT(MAX)} = \frac{T_{J(MAX)} - T_T}{(V_{CC} - V_{OUT}) \times \psi_{JT}}$$

[A] (11-3)

$T_{I(MAX)}$ : Absolute maximum rating for junction temperature [°C]

$T_T$ : Temperature at the center of the package surface [°C]

$\psi_{\scriptscriptstyle IT}$ : Thermal characteristics parameter from junction to center of package surface  $[^{\circ}C/W]$

$V_{CC}$ : Input voltage [V]  $V_{OUT}$ : Output voltage [V] 2. Use thermal resistance  $\theta_{JA}$  to easily calculate the junction temperature.

$$T_I = T_A + \theta_{IA} \times P \quad [^{\circ}C] \tag{11-4}$$

$T_A$ : Ambient temperature [°C]

$\theta_{IA}$ : Thermal resistance between junction and ambient temperature [°C/W]

P: IC consumption power [W]

Also, the peak output current that can flow constantly can be calculated with the following equation.

$$I_{OUT(MAX)} = \frac{T_{J(MAX)} - T_A}{(V_{CC} - V_{OUT}) \times \theta_{IA}}$$

[A] (11-5)

$T_{I(MAX)}$ : Absolute maximum rating for junction temperature [°C]

$T_A$ : Ambient temperature [°C]

$\theta_{IA}$ : Thermal resistance between junction and ambient temperature  $[^{\circ}C/W]$

$V_{CC}$ : Input voltage [V] $V_{OUT}$ : Output voltage [V]

The thermal characteristics parameter  $\Psi_{JT}$  and thermal resistance  $\theta_{JA}$  are values measured using a specific PCB. As the influence of PCB characteristics, copper foil layout, parts layout, chassis shape, surrounding environment and so on cause heat radiation to change, the thermal characteristics parameter and thermal resistance will also change. It is necessary to consider that the values will differ from the actual equipment board.

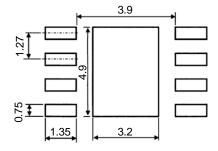

HTSOP-J8 package thermal resistance

| PCB type        | <i>ψ<sub>/T</sub></i> (°C/W) | <i>θ<sub>JA</sub></i> (°C/W) |

|-----------------|------------------------------|------------------------------|

| 1 layer (1s)    | 21                           | 206.4                        |

| 4 layers (2s2p) | 13                           | 45.2                         |

SSOP5 package thermal resistance

| PCB type        | <i>ψ<sub>/T</sub></i> (°C/W) | $	heta_{\!\!\!/\!\!\!A}(^\circ\!\!\!\!\mathrm{C/W})$ |

|-----------------|------------------------------|------------------------------------------------------|

| 1 layer (1s)    | 40                           | 376.5                                                |

| 4 layers (2s2p) | 30                           | 185.4                                                |

SOT89-3K package thermal resistance

| PCB type        | <i>ψ<sub>/T</sub></i> (°C/W) | <i>θ<sub>JA</sub></i> (°C/W) |

|-----------------|------------------------------|------------------------------|

| 1 layer (1s)    | 46                           | 267.0                        |

| 4 layers (2s2p) | 26                           | 71.1                         |

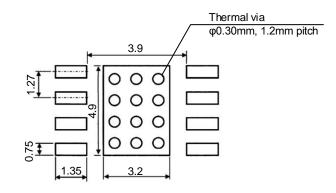

Table 11-1 to 11-6 and Figure 11-1 through 11-27 shows the specifications for the PCB used in measurement.

HTSOP-J8 package PCB specifications, 1 layer (1s)

Conforms to JEDEC standard JESD51-3

| Item                                  | Value              |

|---------------------------------------|--------------------|

| Board thickness                       | 1.57 mm            |

| Board outline dimensions              | 76.2 mm × 114.3 mm |

| Board material                        | FR-4               |

| Trace thickness<br>(Finish thickness) | 70 μm (2 oz)       |

| Lead width                            | 0.254 mm           |

| Copper foil area                      | Footprint          |

Table 11-1. 1-layer PCB specifications

Figure 11-1. Top Layer Trace

Figure 11-2. Footprint

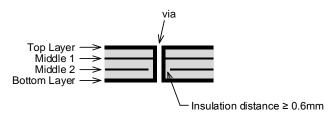

Figure 11-3. 1-layer board sectional view

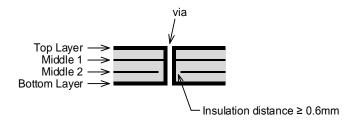

HTSOP-J8 package PCB specifications, 4 layers (2s2p) Conforms to JEDEC standard JESD51-5/-7

| Item                                                             |                                       | Value                                                                                                                                         |

|------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Board thickness                                                  |                                       | 1.60 mm                                                                                                                                       |

| Board outline dimer                                              | nsions                                | 76.2 mm × 114.3 mm                                                                                                                            |

| Board material                                                   |                                       | FR-4                                                                                                                                          |

| Trace thickness (Finish thickness)  Top Middle 1 Middle 2 Bottom |                                       | 70 µm (2 oz)<br>35 µm (1 oz)<br>35 µm (1 oz)<br>70 µm (2 oz)                                                                                  |

| Lead width                                                       |                                       | 0.254 mm                                                                                                                                      |

| Copper foil area                                                 | Top<br>Middle 1<br>Middle 2<br>Bottom | Footprint<br>5505 mm <sup>2</sup> (74.2 mm × 74.2 mm)<br>5505 mm <sup>2</sup> (74.2 mm × 74.2 mm)<br>5505 mm <sup>2</sup> (74.2 mm × 74.2 mm) |

Table 11-2. 4-layer PCB specifications

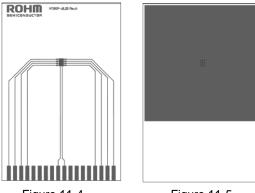

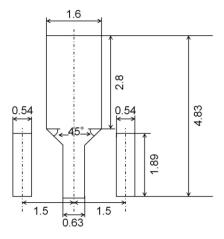

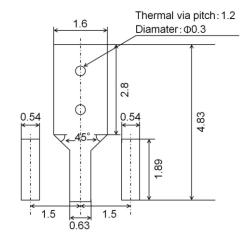

Figure 11-4. Figure 11-5. Top Layer Trace Middle 1 Layer Trace

Figure 11-6. Figure 11-7.

Middle 2 Layer Trace Bottom Layer Trace

Figure 11-8. Footprint

Figure 11-9. 4-layer board sectional view

SSOP5 package PCB specifications, 1 layer (1s)

Conforms to JEDEC standard JESD51-3

| Item                                  | Value              |

|---------------------------------------|--------------------|

| Board thickness                       | 1.57 mm            |

| Board outline dimensions              | 76.2 mm × 114.3 mm |

| Board material                        | FR-4               |

| Trace thickness<br>(Finish thickness) | 70 μm (2 oz)       |

| Lead width                            | 0.254 mm           |

| Copper foil area                      | Footprint          |

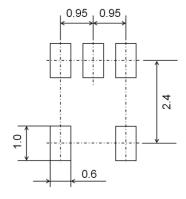

Table 11-3. 1-layer PCB specifications

Figure 11-10. Top Layer Trace

Figure 11-11. Footprint

Figure 11-12. 1-layer board sectional view

SSOP5 package PCB specifications, 4 layers (2s2p) Conforms to JEDEC standard JESD51-7

| ltem                                  |                                       | Value                                                                                                                                         |

|---------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Board thickness                       |                                       | 1.60 mm                                                                                                                                       |

| Board outline dimer                   | nsions                                | 76.2 mm × 114.3 mm                                                                                                                            |

| Board material                        |                                       | FR-4                                                                                                                                          |

| Trace thickness<br>(Finish thickness) | Top<br>Middle 1<br>Middle 2<br>Bottom | 70 µm (2 oz)<br>35 µm (1 oz)<br>35 µm (1 oz)<br>70 µm (2 oz)                                                                                  |

| Lead width                            |                                       | 0.254 mm                                                                                                                                      |

| Copper foil area                      | Top<br>Middle 1<br>Middle 2<br>Bottom | Footprint<br>5505 mm <sup>2</sup> (74.2 mm × 74.2 mm)<br>5505 mm <sup>2</sup> (74.2 mm × 74.2 mm)<br>5505 mm <sup>2</sup> (74.2 mm × 74.2 mm) |

Table 11-4. 4-layer PCB specifications

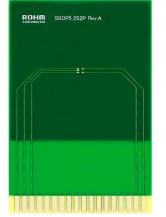

Figure 11-13.

Top Layer Trace

Figure 11-14. Middle 1 Layer Trace

Figure 11-15. Middle 2 Layer Trace

Figure 11-16.

Bottom Layer Trace

Figure 11-17. Footprint

Figure 11-18. 4-layer board sectional view

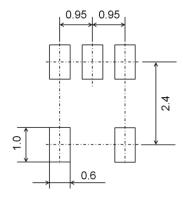

SOT89-3K package PCB specifications, 1 layer (1s) Conforms to JEDEC standard JESD51-3

| Item                                  | Value              |

|---------------------------------------|--------------------|

| Board thickness                       | 1.57 mm            |

| Board outline dimensions              | 76.2 mm × 114.3 mm |

| Board material                        | FR-4               |

| Trace thickness<br>(Finish thickness) | 70 μm (2 oz)       |

| Lead width                            | 0.254 mm           |

| Copper foil area                      | Footprint          |

Table 11-5. 1-layer PCB specifications

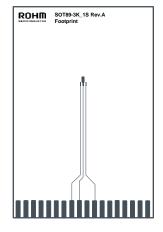

Figure 11-19. Top Layer Trace

Figure 11-20. Footprint

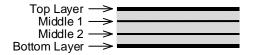

SOT89-3K package PCB specifications, 4 layers (2s2p)

Conforms to JEDEC standard JESD51-5/-7

| Item                                  |                                       | Value                                                                                                                                         |  |

|---------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Board thickness                       |                                       | 1.60 mm                                                                                                                                       |  |

| Board outline dimer                   | nsions                                | 76.2 mm × 114.3 mm                                                                                                                            |  |

| Board material                        |                                       | FR-4                                                                                                                                          |  |

| Trace thickness<br>(Finish thickness) | Top<br>Middle 1<br>Middle 2<br>Bottom | 70 µm (2 oz)<br>35 µm (1 oz)<br>35 µm (1 oz)<br>70 µm (2 oz)                                                                                  |  |

| Lead width                            |                                       | 0.254 mm                                                                                                                                      |  |

| Copper foil area                      | Top<br>Middle 1<br>Middle 2<br>Bottom | Footprint<br>5505 mm <sup>2</sup> (74.2 mm × 74.2 mm)<br>5505 mm <sup>2</sup> (74.2 mm × 74.2 mm)<br>5505 mm <sup>2</sup> (74.2 mm × 74.2 mm) |  |

Table 11-6. 4-layer PCB specifications

Figure 11-22. Top Layer Trace

Figure 11-23. Middle 1 Layer Trace

Figure 11-24. Middle 2 Layer Trace

Figure 11-25. Bottom Layer Trace

Figure 11-26. Footprint

Figure 11-27. 4-layer board sectional view

#### 12. Terminal protection

If inverse or excess voltage is applied to the IC terminals, the device may be damaged or the output voltage may not rise. When the following conditions are anticipated, we recommend that the terminals be adequately protected.

- 1. When the input/output voltage conditions are reversed

- → Reverse current bypass

- 2. When the output load is conductive

- → Output reverse voltage protection

- 3. Possibility of input polarities connected in reverse

- → Input reverse voltage protection

- 4. Hot-plugging → Hot-plugging countermeasures

- 5. Load exists between disparate power sources

- → Reverse current bypass

- 6. Positive-negative power source (both power sources)

- 1. When the input/output voltage conditions are reversed

When the capacitance of the output capacitor is large, and a load remains in the output capacitor even after the input power shuts down, or the speed that the input power shuts down is extremely fast, reverse current will flow from output to input via parasitic elements in the IC because the input/output voltage state will be inverted. Operation is not guaranteed for parasitic elements, and this can degrade or destroy elements.

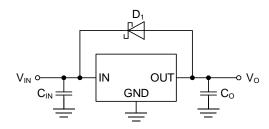

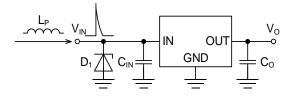

As a countermeasure, connect a reverse current bypass diode externally (Figure 12-1), so that the reverse current does not pass through the inside of the IC. Note that when the input side is left open and the IC is powered down, no degradation of parasitic elements or breakdown will occur due to the reverse current value being a slight IC bias current only. Owing to this, the bypass diode is not necessary (Figure 12-2).

It is necessary for the bypass diode to turn on before the parasitic element in the IC. As the voltage to turn on the internal parasitic element is approximately 0.6 V for the MOSFET type regulator, a low forward voltage of  $V_{\rm F}$  is required. When the value of the reverse current is large, a considerable amount of diode leakage current will flow from input to output, even if the output is off during shutdown. For this reason, a small value (around 1  $\mu$ A or less) must be selected. Select an inverse rated

voltage that is larger than the input/output voltage difference (80% derating or less) to be used. Select a forward direction rated current that is larger than the reverse rated current value (50% derating or less) to be used. From the above conditions, we recommend a rectifier diode or Schottky barrier diode; but as the inverse current of many Schottky barrier diodes is generally large, select one with a small value.

Figure 12-1. Reverse current bypass diode

Figure 12-2. When the input is open

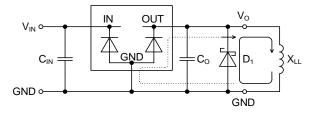

#### 2. When the output load is conductive

When the output load is conductive, the energy stored in the conductive load at the instant the output voltage goes off will be shunted to ground. A diode is used between the IC output pin and GND pin to prevent electrostatic breakdown. If a large electric current flows to this diode, the IC may break down. To prevent this, connect a Schottky barrier diode in parallel to the electrostatic breakdown prevention diode (Figure 12-3).

When the IC output pin and load are connected via a long wire, a conductive load may occur. Measure the waveform using an oscilloscope. Aside from this, when the load is a motor, a diode is necessary due to counter electromotive force in the motor, which causes the same kind of current to flow.

Figure 12-3. Conductive load current path (when output is off)

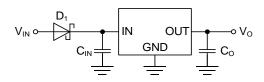

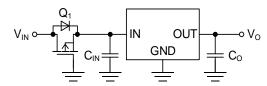

#### 3. Possibility of input polarities connected in reverse

When connecting an input to power, if the positive and negative terminals are connected in reverse due to careless error, a large electric current may flow between the IC input pin and the GND pin to the electrostatic breakdown prevention diode (Figure 12-4). The easiest countermeasure is to connect a Schottky barrier diode or a rectifier diode in series with the power, as shown in Figure 12-5. Using the correct connection, a power loss will occur in V<sub>F</sub>xI<sub>O</sub> due to a voltage drop in the forward voltage V<sub>F</sub> of the diode, so this is not suitable for a battery-operated circuit. The V<sub>F</sub> for a Schottky barrier diode is lower than that of a rectifier diode, so the loss will be somewhat smaller. Since the diode will get hot, select a diode with a wide margin of power dissipation. When connected in reverse, current for the diode will flow in reverse, but the value will be slight.

Figure 12-4. Current path when the input is connected in reverse

Figure 12-5. Countermeasure #1 against reverse connection

Figure 12-6 shows how to connect the diode in parallel with the power source. Since it is necessary for the diode to turn on faster than the electrostatic breakdown protection diode inside the IC, use a Schottky barrier diode with a low V<sub>F</sub>. Using the correct connection, this will operate in the same way as without the diode. Since the total current will keep flowing to the diode when connected in reverse, heat will occur, which may lead to breakdown if the current capacity in the previous stage is too large. The prerequisites for this circuit are either to protect the circuit from accidental mistakes over the short-term, or for an over current protection circuit to be present in the previous stage.

For placing greater emphasis on safety by using a protection circuit, connect the power source in series to the fuse. Although maintenance of the fuse is required, this will protect the circuit with even greater certainty (Figure 12-7).

Figure 12-6. Countermeasure #2 against reverse connection

Figure 12-7. Countermeasure #3 against reverse connection

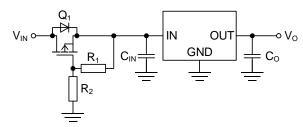

Figure 12-8 shows how to connect the P-ch MOSFET in series with the power source. The diode between the MOSFET drainsource is a body diode (parasitic element). Using the correct connection, the P-ch MOSFET will be on, and the voltage drop here will be the ON resistance of MOSFET times the output current Io. As this is smaller than the voltage drop via diode (Figure 12-5), the power loss will be smaller. When connecting in reverse, MOSFET will not turn on, so there will be no current flow.

When this value exceeds the rated voltage between MOSFET gate-source (in consideration of derating), divide the resistance between gate and source, and lower the gate-source voltage as shown in Figure 12-9.

Figure 12-8. Countermeasure #4 against reverse connection

Figure 12-9. Countermeasure #5 against reverse connection

#### 4. Hot-plugging

When connecting a wire to the IC input while the supply side power is on, a pulse waveform will be generated due to contact between the wiring inductance component and the metal of the connector plug. If this surge voltage exceeds the IC's absolute maximum rating, the IC may break down. Use a TVS (transient voltage suppressor) diode to absorb the surge, so that the surge voltage does not reach the IC input pin (Figure 12-10).

Figure 12-10. Hot-plugging countermeasure

#### 5. Load exists between disparate power sources

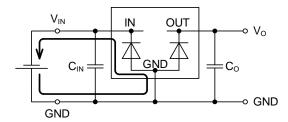

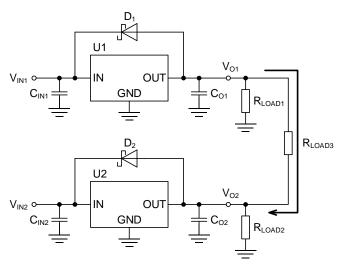

As shown in Figure 12-11, when a load exists between disparate power sources, the timing for rises and drops are different, so current will flow to another power output terminal through the load. Reverse voltage will occur between IC inputs and outputs at this time, so a reverse current bypass diode is needed.

Figure 12-11. Current path and diode insertion between disparate power sources

#### 6. Positive-negative power source (both power sources)

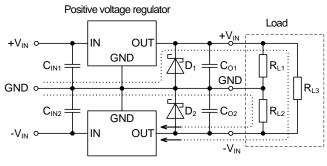

For positive-negative power supplies as shown in Figure 12-12, the speeds at which the power supplies rise are different. For this reason, when there is a load between positive and negative, the power source that started first pulls current from the other output througl  $_{\mbox{Positive voltage regulator}}$  s negative voltage to the output. Be sure to connect a Schottky barrier diode with a low  $V_{\mbox{F}}$  between the output and GND, to prevent damage to the IC and to prevent the output voltage from failing to rise.

Negative voltage regulator

Figure 12-12. Inserting a diode between positive-negative power supplies; current path when negative power supply regulator starts first

#### 13. Soft start

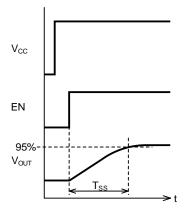

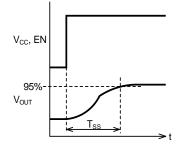

By starting the output voltage for a fixed interval when the power is turned on, the maximum value of inrush current that charges the output capacitor can be reduced. The rise time during soft start is fixed within the IC at 150  $\mu s$  (typ). For this reason, the time cannot be adjusted externally. As shown in figure 13-1, the soft start time is defined as the time until the output voltage reaches the default value of 95%, with the origin as the point at which EN turns on from Low to High. For reference, the variations in time are as follows: 50  $\mu s$  min, 150  $\mu s$  standard, 375  $\mu s$  max. The soft start time is not dependent on the output voltage. Note that the start time may differ depending on the rise times for  $V_{CC}$  and EN, as well as the capacitance of the output capacitor. Refer to "Sequence for turning power supply on" for more details.

Figure 13-1. Definition of soft start time

## 14. Sequence for turning power on

There are no restrictions on the start sequence for Vcc and EN. The starting time depends on the rising time for V<sub>CC</sub> and EN, as well as the capacitance of the output capacitor. These differences are shown below.

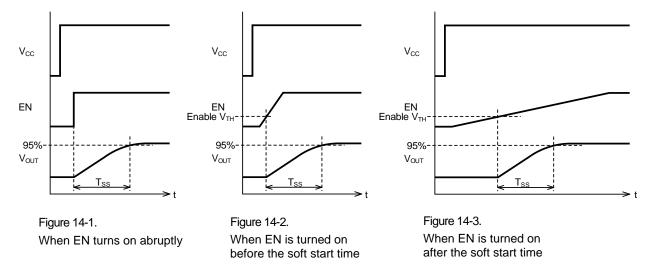

#### 1. When the circuit turns on in order of $V_{CC} \rightarrow EN$

Figure 14-1 shows the startup characteristics for when EN abruptly turns on after  $V_{CC}$  rises. At the same time, this shows the soft start time definition. The soft start time is the time until the output voltage reaches the default value of 95%, with the origin as the point at which EN turns on from Low to High.

Figure 14-2 shows the startup characteristics for when EN is turned on before the soft start time. The soft start circuit begins operating from the time that the voltage of EN exceeds the threshold value, and the output voltage rises in accordance with the soft start time.

Figure 14-3 shows the startup characteristics for when EN is turned on after the soft start time. The soft start circuit begins operating from the time that the voltage of EN exceeds the threshold value, and the output voltage rises in accordance with the soft start time.

## 14. Sequence for turning power on (continued)

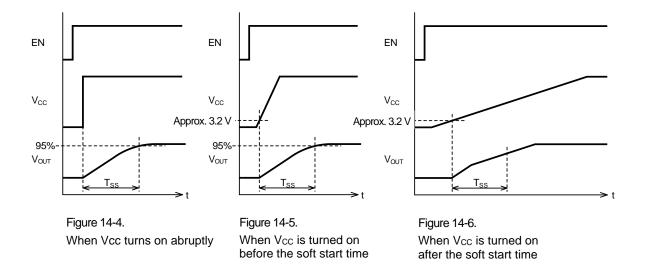

#### 2. When the circuit turns on in order of EN $\rightarrow$ VCC

Figure 14-4 shows the startup characteristics when V<sub>CC</sub> abruptly turns on after the EN rises. The soft start circuit begins operating from the time that the voltage of V<sub>CC</sub> rises, and the output voltage rises in accordance with the soft start time.

Figure 14-5 shows the startup characteristics for when  $V_{CC}$  is turned on before the soft start time. The soft start circuit begins operating from the time that  $V_{CC}$  exceeds 3.2 V, and the output voltage rises in accordance with the soft start time.

Figure 14-6 shows the startup characteristics for when  $V_{CC}$  is turned on after the soft start time. The soft start circuit begins operating and the output rises from the time when the voltage of  $V_{CC}$  exceeds approximately 3.2 V. However, since the speed at which the voltage of  $V_{CC}$  rises is slower than the speed at which the voltage rises during soft start, the output voltage rise is restricted by the voltage of  $V_{CC}$ . For this reason, the start time will be longer and will exceed the soft start time.

## 14. Sequence for turning power on (continued)

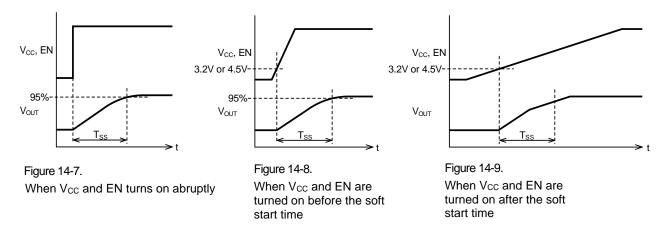

#### 3. When V<sub>CC</sub> and EN turn on at the same time or there is no EN pin

Figure 14-7 shows the startup characteristics when  $V_{CC}$  and EN are abruptly turned on at the same time. The soft start circuit begins operating from the time that  $V_{CC}$  and EN rise, and the output voltage rises in accordance with the soft start time.

Figure 14-8 shows the startup characteristics for when  $V_{CC}$  and EN are turned on before the soft start time. The soft start circuit begins operating from the time that  $V_{CC}$  exceeds 3.2 V (4.5 V for BDxxFA1FP3), and the output voltage rises in accordance with the soft start time.

Figure 14-9 shows the startup characteristics for when  $V_{CC}$  and EN are turned on after the soft start time. The soft start circuit begins operating and the output begins to rise from the time that  $V_{CC}$  exceeds 3.2 V (4.5 V for BDxxFA1FP3). However, since the speed at which the voltage of  $V_{CC}$  rises is slower than the speed at which the voltage rises during soft start, the output voltage rise is restricted by the voltage of  $V_{CC}$ . For this reason, the start time will be longer and will exceed the soft start time.

## 14. Sequence for turning power on (continued)

#### 4. When the output capacitor's capacitance is large

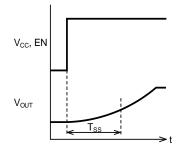

When the capacitance of the output capacitor increases, the charging current at start time also increases. Although this changes depending on the output voltage and over current protection circuit limits, the charging current generally changes when the output capacitance is around 10  $\mu$ F or less, but the soft start time remains the same when starting. When the output capacitance equals or is greater than around 10  $\mu$ F or more, the over current protection circuit activates according to the increase in charging current. Due to this, the charging current value is limited by the over current protection circuit. For this reason, the start time will be longer and will exceed the soft start time, as shown in Figure 14-10. In this condition, the start time will grow longer along with the increase in output capacitance. Figure 14-11 shows the condition in which the current limit affects the start partway through due to the over current protection circuit. In this case, the charging current decreases when the charging of the capacitor is completed to a certain extent. Due to this, the over current protection is released, and the circuit returns to normal operations. This condition occurs when the capacitance of the output capacitor is between the ranges shown in Figure 14-7 and Figure 14-10. When the output capacitor's capacitance is large, check the start time with the actual operating conditions. Typical values are shown below.

Figure 14-10.

When starting while the current limit is applied by the over current protection circuit

Figure 14-11.

When starting while the current limit is applied partway through by the over current protection circuit

| Соит | T <sub>SS</sub>        |                        |                       |

|------|------------------------|------------------------|-----------------------|

| (µF) | V <sub>OUT</sub> =3.3V | V <sub>OUT</sub> =5.4V | V <sub>OUT</sub> =12V |

| 1    | 150 µs                 | 150 µs                 | 150 µs                |

| 2.2  | 150 µs                 | 150 µs                 | 150 µs                |

| 4.7  | 150 µs                 | 150 µs                 | 150 µs                |

| 10   | 150 µs                 | 150 µs                 | 320 µs                |

| 22   | 190 µs                 | 310 µs                 | 700 µs                |

| 47   | 410 µs                 | 670 µs                 | 1.5 ms                |

| 100  | 870 µs                 | 1.4 ms                 | 3.2 ms                |

| 220  | 1.9 ms                 | 3.1 ms                 | 6.9 ms                |

| 470  | 4.1 ms                 | 6.7 ms                 | 15 ms                 |

| 1000 | 8.7 ms                 | 14 ms                  | 32 ms                 |

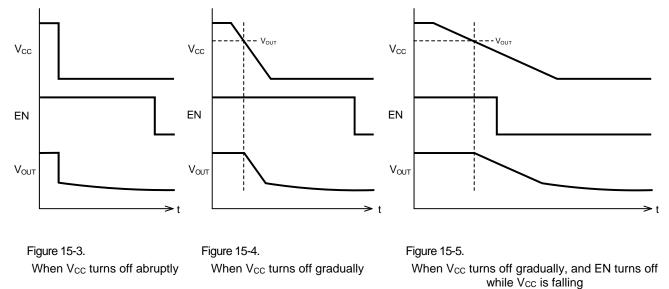

## 15. Sequence for turning power off

The output voltage fall times differ, depending on the order in which Vcc and EN are turned off. These differences are shown below.

1. When the circuit turns off in order of EN  $\rightarrow$  V<sub>CC</sub>

Figure 15-1.

When EN turns off abruptly

Figure 15-2.

When EN turns off gradually

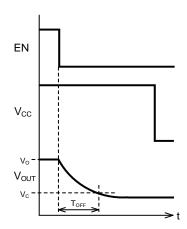

Figure 15-1 shows the startup characteristics when EN abruptly turns off at the same time. When EN goes off, the output transistor will turn off, and the supply of electrical charge from input to output will be gone. The electrical charge in the output capacitor is discharged due to the load, and the output voltage will fall. Another discharge path besides the load is the feedback resistor (output voltage setting resistor). Vcc turns off when the output voltage fully drops. For resistance with a simple load, the output voltage falling time can be calculated with the following equation.

$$T_{OFF} = -C_{OUT} \times R_L \times \ln\left(\frac{V_C}{V_O}\right) \quad [sec]$$

(15-1)

$C_{OUT}$ : Output capacitor [F]  $R_L$ : Load resistance  $[\Omega]$   $V_O$ : Output voltage [V]

$V_C$ : Final dropped voltage [V]

Figure 15-2 shows the power off characteristics when EN gradually turns off. The output transistor turns off when the voltage of EN falls below the threshold value. The output voltage will fall. The fall time for the output voltage is the same as that shown on Figure 15-1.

## 15. Sequence for turning power off (continued)

#### 2. When the circuit turns off in order of $V_{CC} \rightarrow EN$

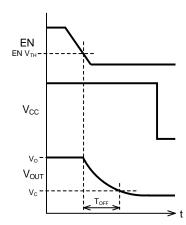

Figure 15-3 shows the power off characteristics when  $V_{CC}$  abruptly turns off. When  $V_{CC}$  abruptly turns off, the electrical charge of the output capacitor is shunted to the input side through the output transistor body diode (parasitic diode), in order to invert the input/output voltage. As a result, the output voltage abruptly falls following the input voltage; and when  $V_{CC}$  reaches 0 V, the body diode voltage (approximately 0.5 V) is left and falls gradually. Then, the voltage falls in time constant with the load resistance.

Figure 15-4 shows the power off characteristics when  $V_{CC}$  gradually turns off. When the voltage of  $V_{CC}$  falls, the electrical charge of the output capacitor is shunted to the input side through the output transistor body diode (parasitic diode), when the input/output voltage reaches the inversion point. As a result, the output voltage falls following the input voltage; and when  $V_{CC}$  reaches 0 V, the body diode voltage (approximately 0.5 V) is left and falls even more gradually. Then, the voltage falls in time constant with the load resistance.

Figure 15-5 shows the power off characteristics when EN abruptly turns off while  $V_{CC}$  gradually turns off. When the voltage of  $V_{CC}$  falls, the electrical charge of the output capacitor is shunted to the input side through the output transistor body diode (parasitic diode), when the input/output voltage reaches the inversion point. Thus, the output voltage falls following the input voltage. When EN is abruptly turned off while the  $V_{CC}$  voltage is falling, the transistor will turn off. However, as the input/output voltage will be inverted, the output voltage continues to fall following the input voltage. Note that when the load current is large, the output voltage will fall faster according to as the current value increases. When the  $V_{CC}$  reaches 0 V, the body diode voltage (approximately 0.5 V) is left and falls even more gradually. Then, the voltage falls in time constant with the load resistance.

## 15. Sequence for turning power off (continued)

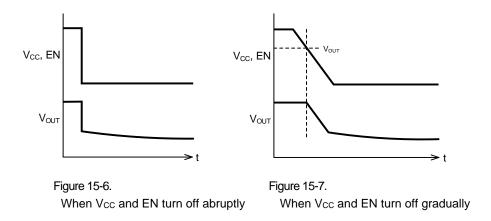

3. When Vcc and EN turn off at the same time or there is no EN pin

Figure 15-6 shows the power off characteristics when  $V_{CC}$  and EN abruptly turn off. When  $V_{CC}$  abruptly turns off, the electrical charge of the output capacitor is shunted to the input side through the output transistor body diode (parasitic diode), in order to invert the input/output voltage. As a result, the output voltage abruptly falls following the input voltage; and when  $V_{CC}$  reaches 0 V, the body diode voltage (approximately 0.5 V) is left and falls gradually. Then, the voltage falls in time constant with the load resistance.

Figure 15-7 shows the power off characteristics when  $V_{CC}$  and EN gradually turn off. When the voltage of  $V_{CC}$  falls and the input/output voltage reaches the inversion point, the electrical charge of the output capacitor is shunted to the input side through the output transistor body diode (parasitic diode). As a result, the output voltage falls following the input voltage; and when  $V_{CC}$  reaches 0 V, the body diode voltage (approximately 0.5 V) is left and falls even more gradually. Then, the voltage falls in time constant with the load resistance.

## 16. Inrush current

An inrush current flows to electrically charge the output capacitor of the IC during startup. Even if the output current value exceeds the maximum value of the recommended operating range, the over current protection (OCP) circuit limits the current, so there are no problems in operation.

## 17. Over current protection (OCP)

An over current protection circuit is included, in order to prevent IC breakdown due to overcurrent when the IC output shorts out the GND. This protective function prevents the IC from breaking down; thus, when used for the purpose of protection as per the original set, we consider that it will be used on a fuse or other current limit device.

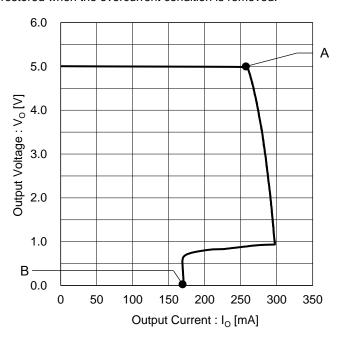

The over current protection characteristics are as shown in Figure 17-1, and the characteristics look like a number "7" (or a "fold back characteristic" in English). The reference value for point A at over current protection detected current is approximately 260 mA. The lower limit value for variations in the detected current will not fall below the maximum value of the recommended output current. When overcurrent is detected, the current fold back circuit operates, and the output voltage drops. Along with the drop in output voltage, the circuit repeatedly works to limit the current, reaching point B. Point B is the output short circuit current. As for the power loss at point B, we can say that this is a safe protection circuit that protects the IC from breaking down, due to small power loss and a smaller degree of heat. Note that this condition will continue until the cause of the overcurrent is eliminated. The output voltage is automatically restored when the overcurrent condition is removed.

Figure 17-1. Characteristics of over current protection

The region between the maximum value of the recommended output current and the over current protection detected value operates as a linear regulator. However, the electrical characteristics are not guaranteed. When continuing to operate beyond the power dissipation, the thermal shutdown circuit will activate and shut off the output.

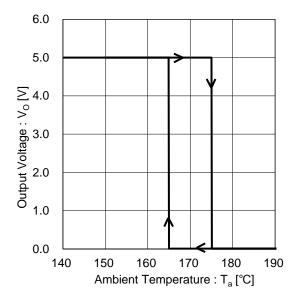

## 18. Thermal shutdown (TSD)

Thermal shutdown protects the IC from damage due to overheating, which occurs when the IC chip temperature exceeds the junction temperature due to an output short or increased power loss. This is not intended to supplant the original thermal shutdown feature of the set.

When the thermal shutdown circuit exceeds the reference value of approximately 175°C, the regulator output turns off, shutting off the output current and lowering the chip temperature. Although there are variations in the detected temperature, this will never fall below the junction temperature (150°C). If the chip temperature falls to approximately 165°C, the output turns on again, and the output current supply begins. The output will turn on and off repeatedly until the cause of the rise in chip temperature is eliminated. If this condition continues, the IC will not break down right away, but continued operation should be avoided, as it will lead to degradation or breakdown.

Figure 18-1. Thermal shutdown characteristics

## 19. Input-output equivalent circuit

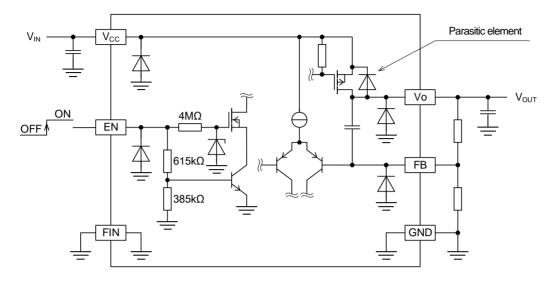

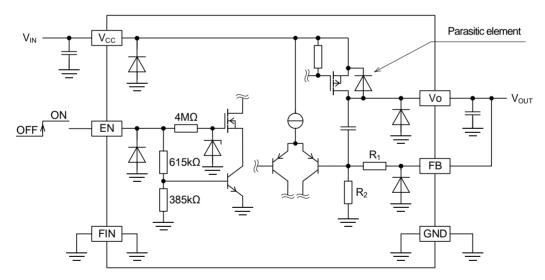

## Adjustable output type

Figure 19-1. Adjustable output type equivalent circuit

## Fixed output type

| 品名      | $R_1(k\Omega)$ | $R_2(k\Omega)$ |

|---------|----------------|----------------|

| BD33FA1 | 53.75          | 17.2           |

| BD50FA1 | 45.15          | 8.6            |

| BD54FA1 | 49.45          | 8.6            |

| BDJ2FA1 | 120.4          | 8.6            |

Figure 19-2. Fixed output type equivalent circuit