#### **Linear Regulator Series**

# **Thermal Resistance Data: SSOP5**

#### BUxxJA2DG-C, BUxxJA2VG-C Series

This application note provides the thermal resistance data of the SSOP5 package used for the thermal design of the BUxxJA2DG-C and BUxxJA2VG-C series linear regulator IC.

#### **Product Summary**

Model name: BUxxJA2DG-C series

BUxxJA2VG-C series

Package name: SSOP5

Function: Linear regulator (LDO) IC

See Datasheet for more details.

<u>Datasheet: BUxxJA2DG-C series</u> <u>Datasheet: BUxxJA2VG-C series</u>

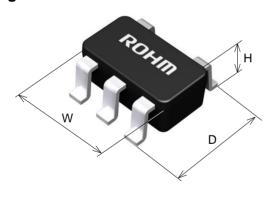

#### **Package**

SSOP5

W (typ) D (typ) H (max)

2.9 mm × 2.8 mm × 1.25 mm

#### Measurement environment

| Content                    | Standard                                |

|----------------------------|-----------------------------------------|

| Measurement environment    | JEDEC STANDARD<br>JESD51-2A (Still Air) |

| Measurement board standard | JEDEC STANDARD<br>JESD51-3<br>JESD51-5  |

#### Thermal resistance

| Configuration | θ <sub>JA</sub> (°C/W) | Ψ <sub>JT</sub> (°C/W) |

|---------------|------------------------|------------------------|

| 1 layer       | 260.7                  | 44                     |

| 2 layers      | 178.8                  | 32                     |

| 4 layers      | 135.1                  | 30                     |

$\theta_{JA}$ : Thermal resistance between junction temperature  $T_J$  - ambient temperature  $T_A$

$\Psi_{JT}$ : Thermal characteristics parameter between junction temperature  $T_J$  - package surface center temperature  $T_T$

Note: The thermal resistances and thermal characteristics parameters in this application note are based on measurement under a JEDEC environment and may not always be consistent with the values for actual equipment. It is necessary to consider variations in the values due to the PCB characteristics, PCB layout, parts layout, chassis shape, surrounding environment, and so on.

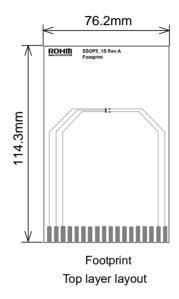

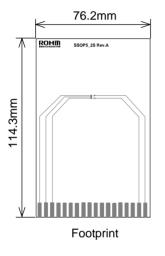

### PCB specifications, 1 layer (1s)

Conforms to JEDEC standard JESD51-3

| Item                                    | Value                             |  |

|-----------------------------------------|-----------------------------------|--|

| Board thickness                         | 1.57 mm                           |  |

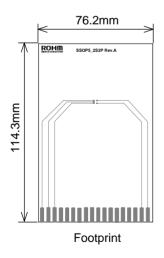

| Board outline dimensions                | 76.2 mm × 114.3 mm                |  |

| Board material                          | FR-4                              |  |

| Trace thickness<br>(Finished thickness) | 70 μm (2 oz)                      |  |

| Lead width                              | 0.254 mm                          |  |

| Copper foil area                        | Footprint<br>[ 50 mm² to 600 mm²] |  |

1-layer board sectional view

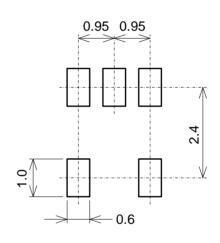

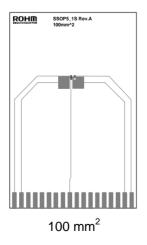

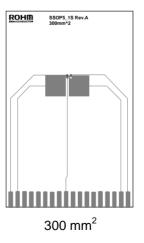

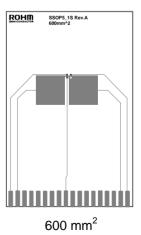

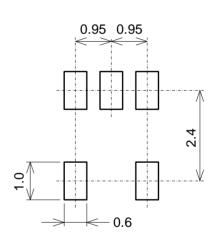

Footprint dimensions

Top layer layout

## PCB specifications, 2 layers

Conforms to JEDEC standard JESD51-7

| Item                                 |               | Value                                                                                                   |

|--------------------------------------|---------------|---------------------------------------------------------------------------------------------------------|

| Board thickness                      |               | 1.60 mm                                                                                                 |

| Board outline dimensions             |               | 76.2 mm × 114.3 mm                                                                                      |

| Board material                       |               | FR-4                                                                                                    |

| Trace thickness (Finished thickness) | Top<br>Bottom | 70 μm (2 oz)<br>70 μm (2 oz)                                                                            |

| Lead width                           |               | 0.254 mm                                                                                                |

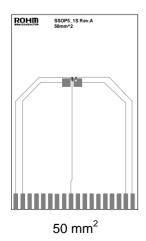

| Copper foil area                     | Top<br>Bottom | Footprint<br>5505 mm <sup>2</sup> (74.2 mm × 74.2 mm)<br>[ 50 mm <sup>2</sup> to 3000 mm <sup>2</sup> ] |

Bottom layer layout

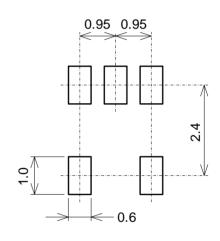

Footprint dimensions

50 mm<sup>2</sup>  $(7.1 \text{ mm} \times 7.1 \text{ mm})$

$(10 \text{ mm} \times 10 \text{ mm})$

300 mm<sup>2</sup>  $(17.3 \text{ mm} \times 17.3 \text{ mm})$

$600 \text{ mm}^2$  $(24.5 \text{ mm} \times 24.5 \text{ mm})$

1200 mm<sup>2</sup>  $(34.6 \text{ mm} \times 34.6 \text{ mm})$

3000 mm<sup>2</sup>  $(54.8 \text{ mm} \times 54.8 \text{ mm})$

Bottom layer layout

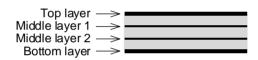

### PCB specifications, 4 layers (2s2p)

Conforms to JEDEC standard JESD51-7

| Item                                    |                                       | Value                                                                                                                                         |

|-----------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Board thickness                         |                                       | 1.60 mm                                                                                                                                       |

| Board outline dimensions                |                                       | 76.2 mm × 114.3 mm                                                                                                                            |

| Board material                          |                                       | FR-4                                                                                                                                          |

| Trace thickness<br>(Finished thickness) | Top<br>Middle 1<br>Middle 2<br>Bottom | 70 µm (2 oz)<br>35 µm (1 oz)<br>35 µm (1 oz)<br>70 µm (2 oz)                                                                                  |

| Lead width                              |                                       | 0.254 mm                                                                                                                                      |

| Copper foil area                        | Top<br>Middle 1<br>Middle 2<br>Bottom | Footprint<br>5505 mm <sup>2</sup> (74.2 mm × 74.2 mm)<br>5505 mm <sup>2</sup> (74.2 mm × 74.2 mm)<br>5505 mm <sup>2</sup> (74.2 mm × 74.2 mm) |

4-layer board sectional view

Footprint dimensions

Top layer layout

$5505 \text{ mm}^2$  (74.2 mm × 74.2 mm)

Middle 1 layer layout

$5505 \text{ mm}^2$  (74.2 mm × 74.2 mm)

Middle 2 layer layout

5505 mm<sup>2</sup> (74.2 mm × 74.2 mm)

Bottom layer layout

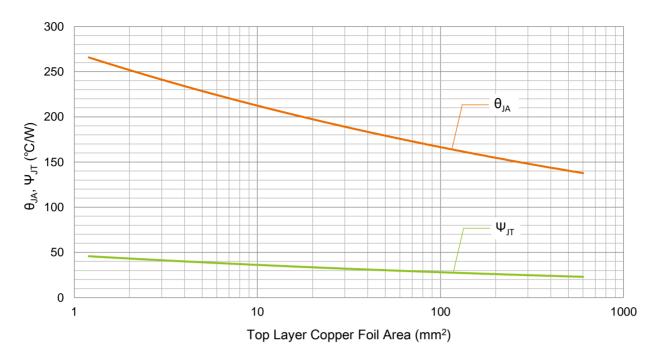

### Thermal resistance data, 1 layer (1s)

Figure 1.  $\theta_{JA}$ ,  $\Psi_{JT}$  vs. copper foil surface area

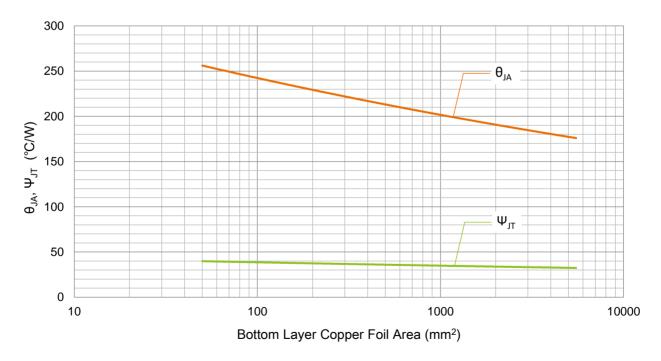

### Thermal resistance data, 2 layers

Figure 2.  $\theta_{JA},~\Psi_{JT}$  vs. Bottom layer copper foil area

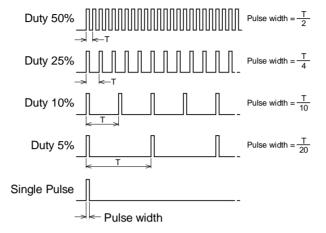

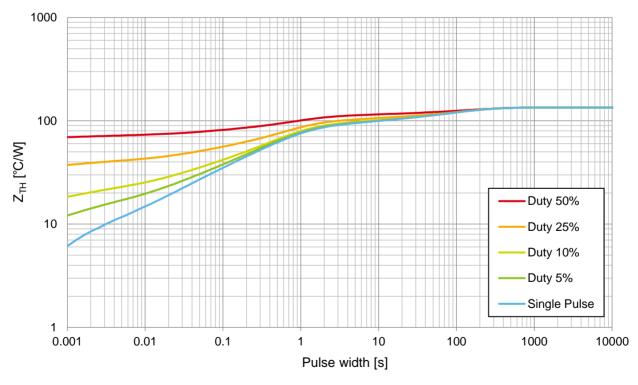

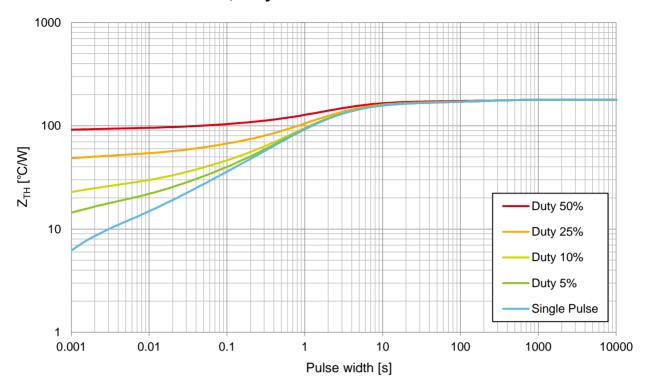

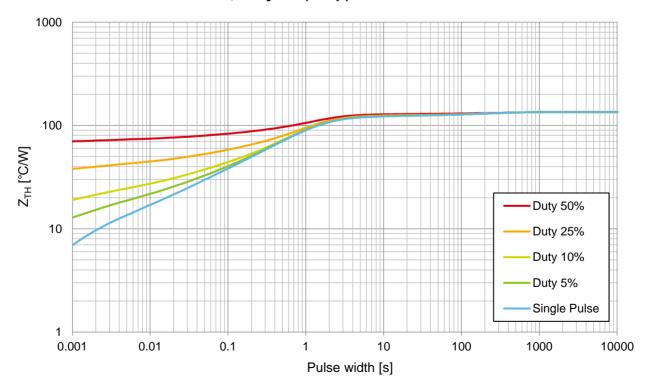

#### Transient thermal resistance

Conforms to JEDEC standard JESD51

X axis: Pulse width is the time to apply power to the device

Y axis: Transient thermal resistance

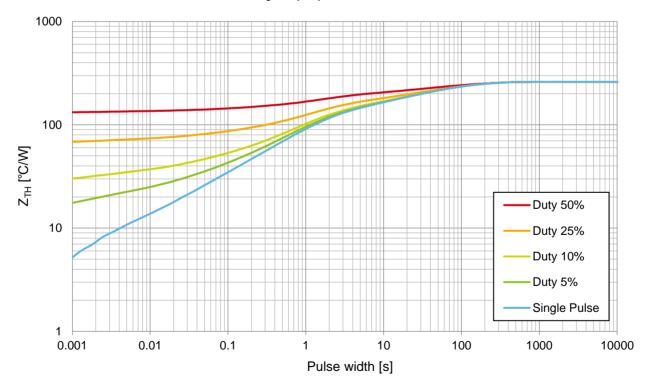

### Transient thermal resistance data, 1 layer (1s)

Figure 3. Transient thermal resistance, 1 layer, Copper foil surface area 1.2 mm<sup>2</sup> (Footprint)

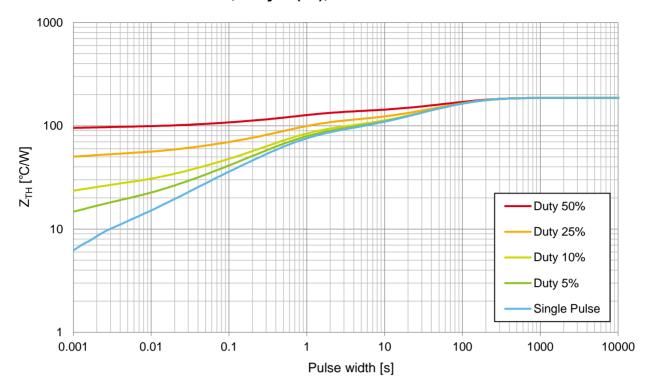

### Transient thermal resistance data, 1 layer (1s), continued

Figure 4. Transient thermal resistance, 1 layer, Copper foil surface area 50 mm<sup>2</sup>

Figure 5. Transient thermal resistance, 1 layer, Copper foil surface area 100 mm<sup>2</sup>

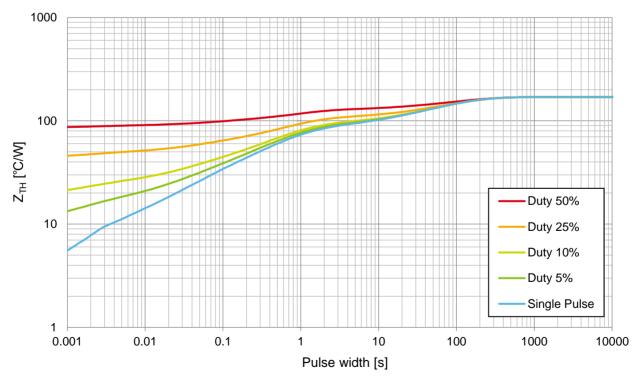

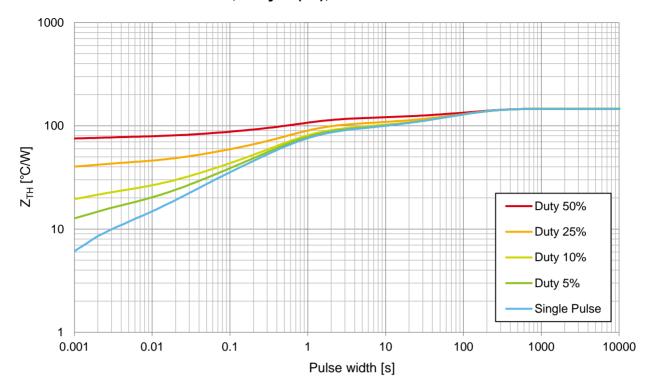

### Transient thermal resistance data, 1 layer (1s), continued

Figure 6. Transient thermal resistance, 1 layer, Copper foil surface area 300 mm<sup>2</sup>

Figure 7. Transient thermal resistance, 1 layer, Copper foil surface area 600 mm<sup>2</sup>

### Transient thermal resistance data, 2 layers

Figure 8. Transient thermal resistance, 2 layers, Copper foil bottom area 5505 mm<sup>2</sup>

### Transient thermal resistance data, 4 layers (2s2p)

Figure 9. Transient thermal resistance, 4 layers

#### Notes

- 1) The information contained herein is subject to change without notice.

- Before you use our Products, please contact our sales representative and verify the latest specifications:

- 3) Although ROHM is continuously working to improve product reliability and quality, semiconductors can break down and malfunction due to various factors. Therefore, in order to prevent personal injury or fire arising from failure, please take safety measures such as complying with the derating characteristics, implementing redundant and fire prevention designs, and utilizing backups and fail-safe procedures. ROHM shall have no responsibility for any damages arising out of the use of our Poducts beyond the rating specified by ROHM.

- 4) Examples of application circuits, circuit constants and any other information contained herein are provided only to illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

- 5) The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. ROHM does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by ROHM or any other parties. ROHM shall have no responsibility whatsoever for any dispute arising out of the use of such technical information.

- 6) The Products specified in this document are not designed to be radiation tolerant.

- 7) For use of our Products in applications requiring a high degree of reliability (as exemplified below), please contact and consult with a ROHM representative: transportation equipment (i.e. cars, ships, trains), primary communication equipment, traffic lights, fire/crime prevention, safety equipment, medical systems, servers, solar cells, and power transmission systems.

- 8) Do not use our Products in applications requiring extremely high reliability, such as aerospace equipment, nuclear power control systems, and submarine repeaters.

- 9) ROHM shall have no responsibility for any damages or injury arising from non-compliance with the recommended usage conditions and specifications contained herein.

- 10) ROHM has used reasonable care to ensure the accuracy of the information contained in this document. However, ROHM does not warrants that such information is error-free, and ROHM shall have no responsibility for any damages arising from any inaccuracy or misprint of such information.

- 11) Please use the Products in accordance with any applicable environmental laws and regulations, such as the RoHS Directive. For more details, including RoHS compatibility, please contact a ROHM sales office. ROHM shall have no responsibility for any damages or losses resulting non-compliance with any applicable laws or regulations.

- 12) When providing our Products and technologies contained in this document to other countries, you must abide by the procedures and provisions stipulated in all applicable export laws and regulations, including without limitation the US Export Administration Regulations and the Foreign Exchange and Foreign Trade Act.

- 13) This document, in part or in whole, may not be reprinted or reproduced without prior consent of ROHM.

Thank you for your accessing to ROHM product informations. More detail product informations and catalogs are available, please contact us.

### **ROHM Customer Support System**

http://www.rohm.com/contact/