# **BD71837MWV** Functional Errata

### 1. Functional Errata History

| Date        | Errata<br>Number |                             | Silicon Revision |                |  |

|-------------|------------------|-----------------------------|------------------|----------------|--|

|             |                  | Title                       | BD71837MWV       | BD71837AMWV    |  |

|             |                  |                             | (REV[00h]=A2h)   | (REV[00h]=A3h) |  |

| 05.Feb.2019 | BD71837_001      | PMIC Hung in OTP Load State | Yes              | No             |  |

A "Yes" entry indicates the erratum applies to a particular revision level, and "No" entry means it does not apply.

## 2. PMIC Hung in OTP Load State

### 2.1. Summary

When PMIC is in shutdown state **EMG** and VSYS voltage is below 2.7V, a 100  $\mu$ s - 390  $\mu$ s surge on VSYS causes PMIC to transition to and remains in OTP loading state **READY** until power is removed.

One possible workaround is to disable the reloading of OTP settings on resets. Since this is likely to be undesirable for many use cases, new silicon stepping is being planned. The fix is a simple, low-risk metal layer change.

New silicon samples: Middle of April 2019 New qualified samples: Begin of June 2019.

New PN: BD71837AMWV

BD71837MWV will be obsoleted once BD71837AMWV will be launched by October 2019.

#### 2.2. Conditions That Leads to Failure

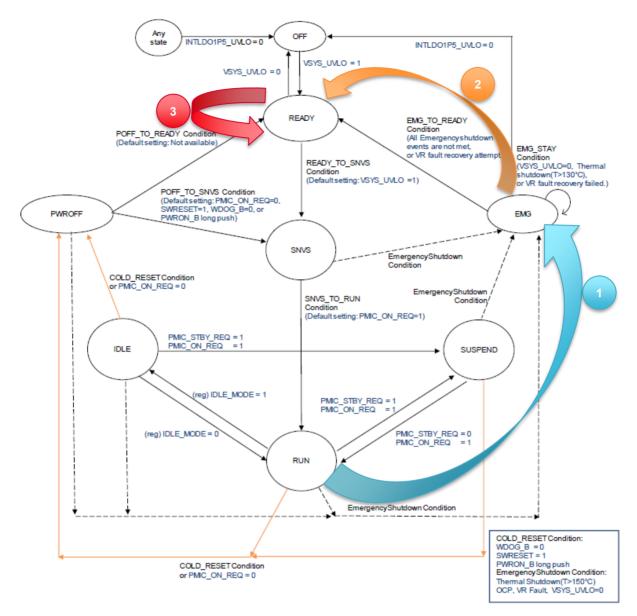

Figure 1 shows the power state transition diagram annotated with arrows showing how the problem could develop and manifest itself. The test sequence below corresponds to the matching labeled arrows in the diagram.

- 1. Input supply VSYS is lowered below VSYS\_UVLO level (2.7V) => PMIC enters **EMG** state in which all power rails are turned off.

- VSYS\_UVLO is 2.7V (sweeping down) 3.0V (sweeping up)

- 2. VSYS is raised above VSYS\_UVLO (3.0v) for a 'short' time to simulate noise spike => PMIC enters **READY** state in which OTP settings are loaded.

- $_{\odot}$  Here, short means 100 μs 390 μs. Anything shorter is filtered out by the debounce circuit. Longer duration doesn't cause problem. The reason is OTP loading takes approximately 390 μs.

- If the noise spike lasts less than 390 μs, VSYS drops back to below VSYS\_UVLO (2.7V) before OTP loading is completed.

PMIC remains in READY state until power is removed, or, more precisely, until VSYS is below 1.35V. At that point, PMIC goes to OFF state the same starting point as first time power-on.

With one exception, the above behavior holds regardless of how PMIC enters EMG state. Therefore, in addition to VSYS being less than VSYS\_UVLO, other events that may lead to failure is thermal shutdown and power fault detected on a power rail. If the conditions in Steps 2 and 3 hold, these events result in PMIC hang as well.

Exception: this problem doesn't occur when PMIC enters EMG via OFF state (as in first time power-on)

Reason: OTP loading actually takes place in OFF state in this case. The deadlock condition described in 2.3 does not arise because

neither the detection logic nor the state machine is operational in OFF state.

Figure 1: Power State Diagram

### 2.3. Root Cause - Design Details

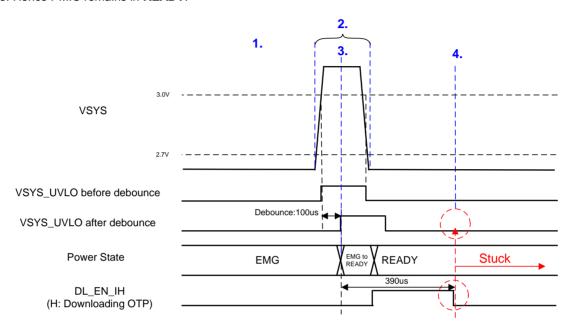

PMIC is stuck in **READY** state because of a deadlock situation between the logic that detects state of VSYS (being below or above VSYS UVLO) and the power state transition state machine that takes detection result as one of its input.

Internally a pulse is generated upon detection of VSYS\_UVLO event. During OTP download while in **READY** state, such pulse is ignored. Since the event is not registered, the power state machine receives no trigger after OTP loading is completed to transition to another state. Hence PMIC remains in **READY**.

Figure 2: Power State Transition Diagram

#### 2.4. Workaround

Register Name

RW

One possible work around is to disable the reloading of OTP while in **READY** state. This would eliminate the cause of deadlock described in 2.3 by reducing the OTP loading time – the time window deadlock may arise – to zero.

The drawback is the PMIC can't be re-initialized to a clean, known state after cold reset.

To disable OTP loading while in **READY**, OTP must be changed. Specifically, Bit [5] in PWRCTRL0 register at 0x03 is to be changed to '0'.

| PWRCTRL0 | R/W                                                                                                                                                                               | DEBUG_STATE[1:0] | REG                                                                                                                                                                             | -  | -       | - | WDOGB_SEL[1:0] | 0xA2 | 0x03 |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------|---|----------------|------|------|

| Bit      | Name Function                                                                                                                                                                     |                  |                                                                                                                                                                                 |    | Initial |   |                |      |      |

| D[7:6]   | Select Cold reset, Warm reset or No reset action when PWRON_B long push is detected.  DEBUG_STATE[1:0]  00 = No reset action 01 = No reset action 10 = Cold reset 11 = Warm reset |                  |                                                                                                                                                                                 | 10 |         |   |                |      |      |

| D[5]     |                                                                                                                                                                                   | RELOAD_REG       | Select OTP configurable registers initialization when the power state goes through<br>READY state.<br>0 = No initialization<br>1= Reload OTP registers and set to initial value |    |         | , | 1              |      |      |

| D[1:0]   |                                                                                                                                                                                   | WDOGB_SEL[1:0]   | Select Cold reset, Warm reset or No reset action when WDOG_B is asserted to 0.<br>00 = No reset action<br>01 = No reset action<br>10 = Cold reset<br>11 = Warm reset            |    |         | 1 | 0              |      |      |

Address

# 2.5. Hardware Fix - New Silicon Stepping

A silicon revision will fix the issue; no work around would be needed.

Avaibility:

Samples: Middle of April 2019

Qualified samples: Begin of June 2019

New PN: BD71837AMWV

# 3. Revision History

| Date        | Revision<br>Number | Description   |

|-------------|--------------------|---------------|

| 05.Feb.2019 | 001                | First Release |

#### Notes

- 1) The information contained herein is subject to change without notice.

- Before you use our Products, please contact our sales representative and verify the latest specifications:

- 3) Although ROHM is continuously working to improve product reliability and quality, semiconductors can break down and malfunction due to various factors. Therefore, in order to prevent personal injury or fire arising from failure, please take safety measures such as complying with the derating characteristics, implementing redundant and fire prevention designs, and utilizing backups and fail-safe procedures. ROHM shall have no responsibility for any damages arising out of the use of our Poducts beyond the rating specified by ROHM.

- 4) Examples of application circuits, circuit constants and any other information contained herein are provided only to illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

- 5) The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. ROHM does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by ROHM or any other parties. ROHM shall have no responsibility whatsoever for any dispute arising out of the use of such technical information.

- 6) The Products specified in this document are not designed to be radiation tolerant.

- 7) For use of our Products in applications requiring a high degree of reliability (as exemplified below), please contact and consult with a ROHM representative: transportation equipment (i.e. cars, ships, trains), primary communication equipment, traffic lights, fire/crime prevention, safety equipment, medical systems, servers, solar cells, and power transmission systems.

- 8) Do not use our Products in applications requiring extremely high reliability, such as aerospace equipment, nuclear power control systems, and submarine repeaters.

- 9) ROHM shall have no responsibility for any damages or injury arising from non-compliance with the recommended usage conditions and specifications contained herein.

- 10) ROHM has used reasonable care to ensure the accuracy of the information contained in this document. However, ROHM does not warrants that such information is error-free, and ROHM shall have no responsibility for any damages arising from any inaccuracy or misprint of such information.

- 11) Please use the Products in accordance with any applicable environmental laws and regulations, such as the RoHS Directive. For more details, including RoHS compatibility, please contact a ROHM sales office. ROHM shall have no responsibility for any damages or losses resulting non-compliance with any applicable laws or regulations.

- 12) When providing our Products and technologies contained in this document to other countries, you must abide by the procedures and provisions stipulated in all applicable export laws and regulations, including without limitation the US Export Administration Regulations and the Foreign Exchange and Foreign Trade Act.

- 13) This document, in part or in whole, may not be reprinted or reproduced without prior consent of ROHM.

Thank you for your accessing to ROHM product informations. More detail product informations and catalogs are available, please contact us.

# ROHM Customer Support System

http://www.rohm.com/contact/