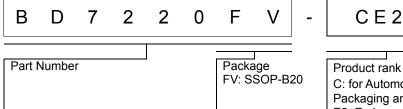

# BD7220FV-C

ROHM

#### **General Description**

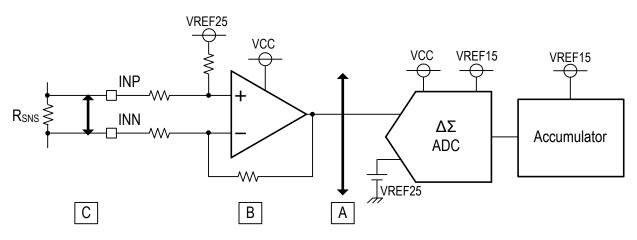

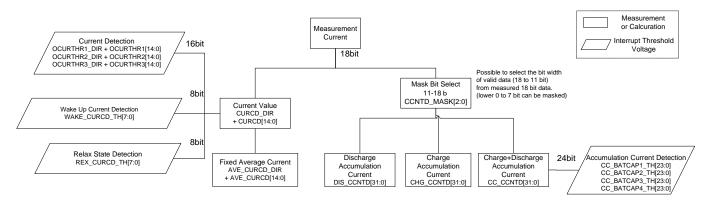

BD7220FV-C is a coulomb counter IC for high-current applications. The product integrates a high-accuracy operational amp, a current accumulation logic circuit and a 16-bit  $\Delta\Sigma ADC$  to perform current accumulation with high precision. The current sense input supports shunt resistors and output current sensors, and uses the SPI communication interface. BD7220FV-C only requires SPI commands to carry out the calibration necessary for high-precision measurement, so it can also get current accumulation information for battery state-of-charge estimation.

#### **Features**

- AEC-Q100 Qualified (Note 1)

- 16-bit ΔΣADC

- Flexible Noise Filter (4 settings)

- Automatic Calibration via SPI

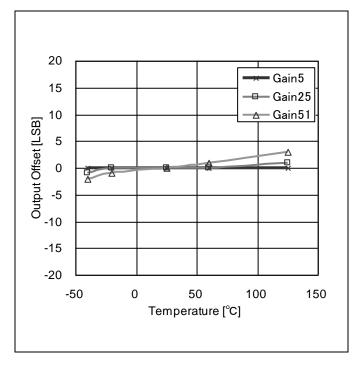

- High-accuracy Op-amp with 3 Gain Settings (5 V/V, 25 V/V, 51 V/V)

- Supports Current Sensing Using Shunt Resistors

- Supports Current Sensing Using Current Output Type **Current Sensors**

- SPI I/F (Optional CRC)

- Coulomb Counter Function with SPI External Communication

- Accumulation Current Counter which Counts Charge and Discharge Independently

- Adjustable Current Detection Interruption (3 settings)

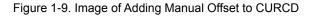

- 4 Operation Modes

- (NORMAL, SLEEP, SSHDN, OFF)

- Wake Up Current Detection Function

- UVLO

- (Note 1) Grade 1

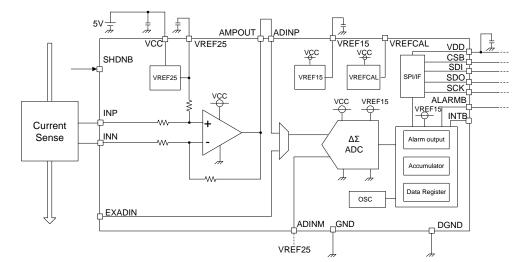

## **Typical Application Circuit**

#### **Key Specifications**

- Input Voltage Range

- VCC Input Voltage Range 4.5 V to 5.5 V

- VDD Input Voltage Range 2.5 V to 5.5 V

- Operating Temperature

- -40 °C to +125 °C

#### Applications

- Battery Current Sense for EV

- Electricity Storage Systems

- Automated Guided Vehicle (AGV)

- Robot

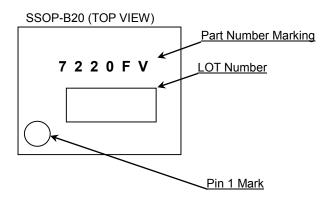

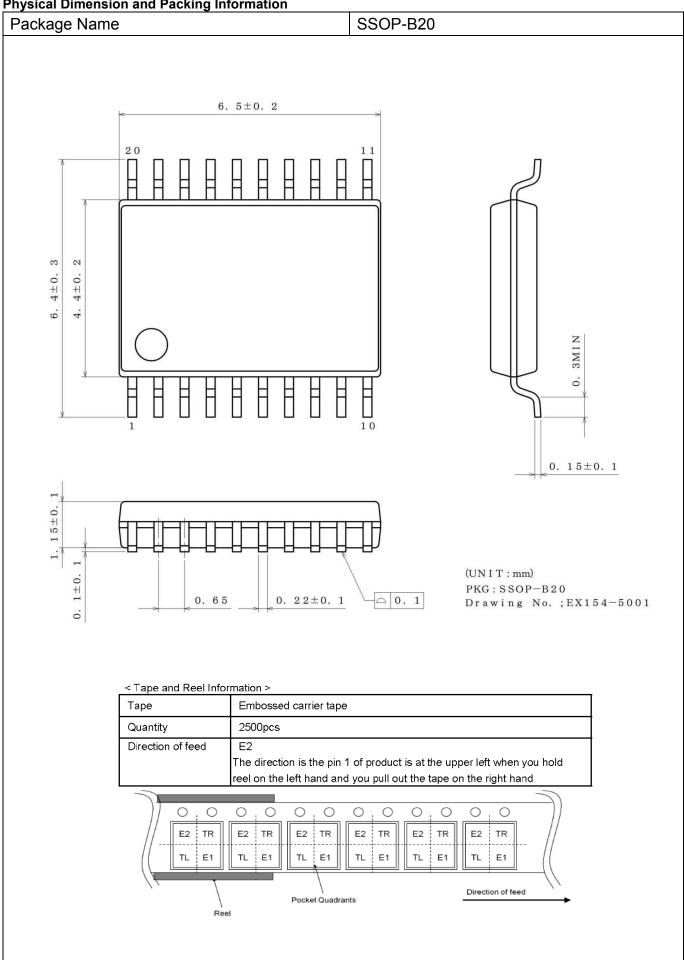

#### Package

SSOP-B20

W (Typ) x D (Typ) x H (Max) 6.5 mm x 6.4 mm x 1.45 mm

SSOP-B20

OProduct structure : Silicon integrated circuit OThis product has no designed protection against radioactive rays.

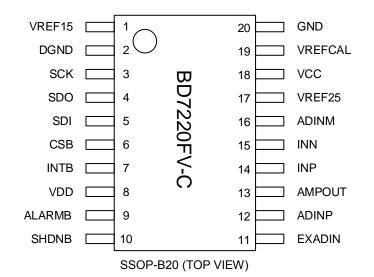

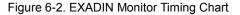

# **Pin Configuration**

# **Pin Description**

| Pin No. | Pin Name | I/O | Function                                                        |  |  |  |  |  |

|---------|----------|-----|-----------------------------------------------------------------|--|--|--|--|--|

| 1       | VREF15   | 0   | LDO output for internal power                                   |  |  |  |  |  |

| 2       | DGND     | -   | Digital ground                                                  |  |  |  |  |  |

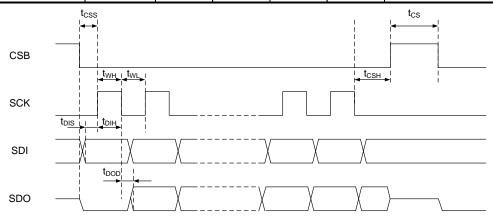

| 3       | SCK      | I   | SPI clock input                                                 |  |  |  |  |  |

| 4       | SDO      | 0   | SPI data output                                                 |  |  |  |  |  |

| 5       | SDI      | I   | SPI data input                                                  |  |  |  |  |  |

| 6       | CSB      | I   | SPI chip select input                                           |  |  |  |  |  |

| 7       | INTB     | 0   | Event interrupt output open drain                               |  |  |  |  |  |

| 8       | VDD      | -   | Power supply for SPI I/F                                        |  |  |  |  |  |

| 9       | ALARMB   | 0   | Alarm output open drain                                         |  |  |  |  |  |

| 10      | SHDNB    | I   | Shutdown Input (H: operating, L: shutdown)                      |  |  |  |  |  |

| 11      | EXADIN   | I   | Delta sigma ADC select input                                    |  |  |  |  |  |

| 12      | ADINP    | I   | Delta sigma ADC monitor input                                   |  |  |  |  |  |

| 13      | AMPOUT   | 0   | Internal amp output                                             |  |  |  |  |  |

| 14      | INP      | I   | Internal amp non-inverting input                                |  |  |  |  |  |

| 15      | INN      | I   | Internal amp inverting input                                    |  |  |  |  |  |

| 16      | ADINM    | I   | Delta sigma ADC reference input                                 |  |  |  |  |  |

| 17      | VREF25   | 0   | Internal reference output                                       |  |  |  |  |  |

| 18      | VCC      | -   | Power supply                                                    |  |  |  |  |  |

| 19      | VREFCAL  | 0   | Reference output for calibration in BD7220FV-C shipment process |  |  |  |  |  |

| 20      | GND      | -   | Analog ground                                                   |  |  |  |  |  |

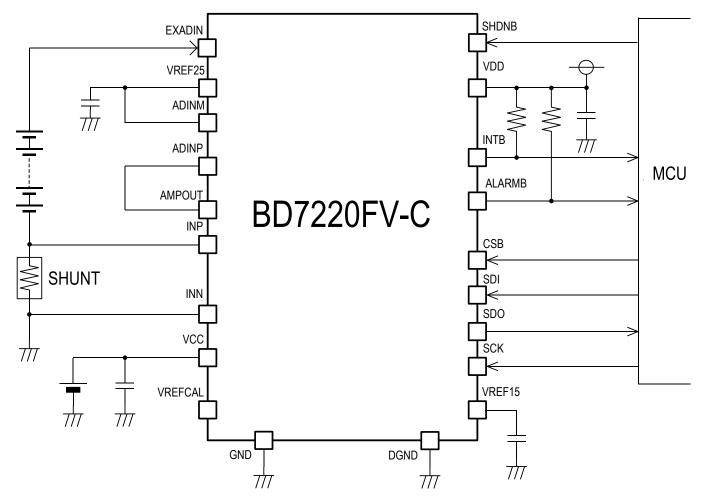

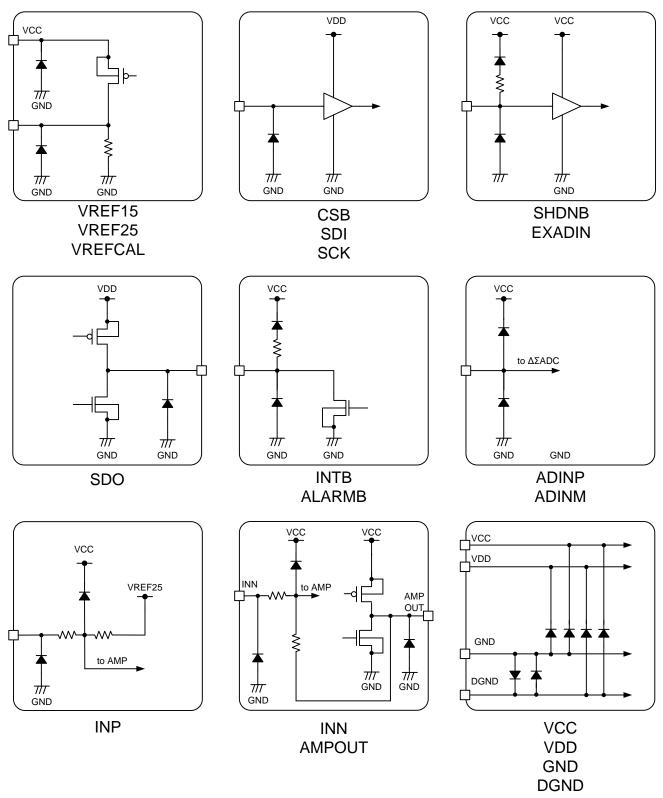

# **Application Example**

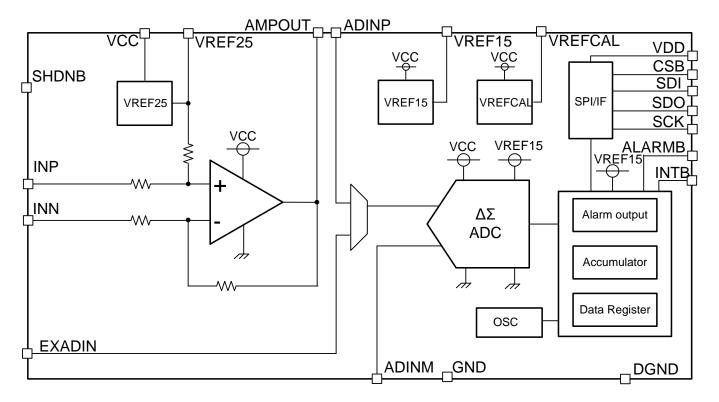

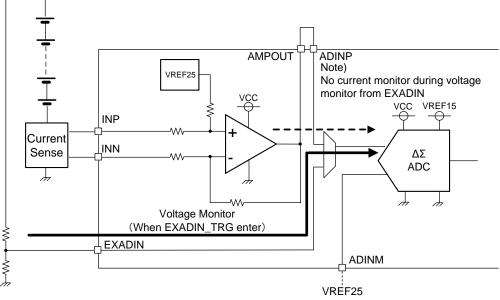

# **Block Diagram**

# Absolute Maximum Ratings (Ta = 25 °C)

| Item                                                                                                                       | Symbol             | Limit        | Unit |

|----------------------------------------------------------------------------------------------------------------------------|--------------------|--------------|------|

| Voltage Range1 (VCC, VDD)                                                                                                  | V <sub>AMR_1</sub> | -0.3 to +7.0 | V    |

| Voltage Range2 (VREF15)                                                                                                    | VAMR_2             | -0.3 to +2.1 | V    |

| Voltage Range3<br>(VREF25, VREFCAL, INP, INN, EXADIN,<br>SHDNB, INTB, ALARMB, AMPOUT, ADINP,<br>ADINM, CSB, SDI, SDO, SCK) | V <sub>AMR_3</sub> | -0.3 to +7.0 | V    |

| Maximum Junction Temperature                                                                                               | Tjmax              | 150          | °C   |

| Storage Temperature Range                                                                                                  | Tstg               | -55 to +150  | °C   |

Caution 1: Operating the IC over the absolute maximum ratings may damage the IC. The damage can either be a short circuit between pins or an open circuit between pins and the internal circuitry. Therefore, it is important to consider circuit protection measures, such as adding a fuse, in case the IC is operated over the absolute maximum ratings.

Caution 2: Should by any chance the maximum junction temperature rating be exceeded the rise in temperature of the chip may result in deterioration of the properties of the chip. In case of exceeding this absolute maximum rating, design a PCB with thermal resistance taken into consideration by increasing board size and copper area so as not to exceed the maximum junction temperature rating.

#### Thermal Resistance (Note 2)

| Baramatar                                           | Symbol             | Thermal Res | Unit                                            |      |

|-----------------------------------------------------|--------------------|-------------|-------------------------------------------------|------|

| Parameter                                           |                    | 1s (Note 4) | 1s <sup>(Note 4)</sup> 2s2p <sup>(Note 5)</sup> |      |

| SSOP-B20                                            |                    |             |                                                 |      |

| Junction to Ambient                                 | θյΑ                | 115.4       | 57.3                                            | °C/W |

| Junction to Top Characterization Parameter (Note 3) | $\Psi_{\text{JT}}$ | 10          | 8                                               | °C/W |

(Note 2) Based on JESD51-2A (Still-Air)

(Note 3) The thermal characterization parameter to report the difference between junction temperature and the temperature at the top center of the outside surface of the component package. (Note 4) Using a PCB board based on JESD51-3 (Note 5) Using a PCB board based on JESD51-7.

| (Note 5) Using a FCB board bas       | based off JESD51-7. |                    |                          |        |           |  |  |  |

|--------------------------------------|---------------------|--------------------|--------------------------|--------|-----------|--|--|--|

| Layer Number of<br>Measurement Board | Materia             | I Board S          | Size                     |        |           |  |  |  |

| Single                               | FR-4                | 114.3 mm x 76.2 r  | nm x 1.57 m              | mt     |           |  |  |  |

| Тор                                  |                     |                    |                          |        |           |  |  |  |

| Copper Pattern                       | Thickness           |                    |                          |        |           |  |  |  |

| Footprints and Traces                | 70 µm               |                    |                          |        |           |  |  |  |

| Layer Number of<br>Measurement Board | Material            | Board Siz          | e                        |        |           |  |  |  |

| 4 Layers                             | FR-4                | 114.3 mm x 76.2 mm | n x 1.6 mmt              |        |           |  |  |  |

| Тор                                  |                     | 2 Internal Layers  |                          | Botton | ı         |  |  |  |

| Copper Pattern                       | Thickness           | Copper Pattern     | Copper Pattern Thickness |        | Thickness |  |  |  |

| Footprints and Traces                | 70 µm               | 74.2 mm x 74.2 mm  | 74.2 mm x 74.2 mm 35 µm  |        | 70 µm     |  |  |  |

# **Recommended Operating Condition**

| Item                  | Sumbol |     | Limit |      | Unit | Condition |

|-----------------------|--------|-----|-------|------|------|-----------|

|                       | Symbol | Min | Тур   | Max  | Unit | Condition |

| Voltage Range1 (VCC)  | VOPR_1 | 4.5 | 5.0   | 5.5  | V    |           |

| Voltage Range2 (VDD)  | VOPR_2 | 2.5 | 3.3   | 5.5  | V    |           |

| Operating Temperature | Topr   | -40 | +25   | +125 | °C   |           |

# **Electrical Characteristics**

(Unless otherwise specified, Ta = -40 °C to +125 °C, VCC = 5.0 V, VDD = 3.3 V)

| Parameter                    | Symbol               |       | Limit |       | Unit | Condition                          |  |  |  |  |

|------------------------------|----------------------|-------|-------|-------|------|------------------------------------|--|--|--|--|

| Falameter                    | Symbol               | Min   | Тур   | Max   | Onit | Condition                          |  |  |  |  |

| REF15                        |                      |       |       |       |      |                                    |  |  |  |  |

| Output Voltage1              | V <sub>015_1</sub>   | 1.470 | 1.500 | 1.530 | V    | lo = 0 mA, Ta= +25 °C              |  |  |  |  |

| Output Voltage2              | V <sub>015_2</sub>   | 1.450 | 1.500 | 1.550 | V    | lo = 0 mA, Ta= -40 °C to +125 °C   |  |  |  |  |

| Effective Output Capacitance | C <sub>VO15</sub>    | 0.4   | -     | 2.0   | μF   | Recommended Nominal Capacitor:1 µF |  |  |  |  |

| VREF25                       | REF25                |       |       |       |      |                                    |  |  |  |  |

| Output Voltage1              | V <sub>025_1</sub>   | 2.450 | 2.500 | 2.550 | V    | lo = 0 mA, Ta= +25 °C              |  |  |  |  |

| Output Voltage2              | V <sub>025_2</sub>   | 2.400 | 2.500 | 2.600 | V    | lo = 0 mA, Ta= -40 °C to +125 °C   |  |  |  |  |

| Effective Output Capacitance | C <sub>VO25</sub>    | 0.4   | -     | 2.0   | μF   | Recommended Nominal Capacitor:1 µF |  |  |  |  |

| osc                          |                      |       |       |       |      |                                    |  |  |  |  |

| Frequency1                   | f <sub>OSC_1</sub>   | 8110  | 8192  | 8274  | kHz  | Ta= +25 °C                         |  |  |  |  |

| Frequency2                   | f <sub>OSC_2</sub>   | 8028  | 8192  | 8356  | kHz  | Ta= -40 °C to +125 °C              |  |  |  |  |

| Start up Time                | t <sub>wakeosc</sub> | -     | 50    | 200   | μs   |                                    |  |  |  |  |

| Parameter                                            | Simple              |     | Limit |      | Unit | Condition                                                                                                                                  |  |  |  |  |  |

|------------------------------------------------------|---------------------|-----|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Parameter                                            | Symbol              | Min | Тур   | Max  | Unit | Condition                                                                                                                                  |  |  |  |  |  |

| urrent Consumption                                   |                     |     |       |      |      |                                                                                                                                            |  |  |  |  |  |

| Shutdown Current 1_1<br>(OFF) = HSHDN                | I <sub>QVB1_1</sub> | -   | 0     | 5    | μA   | SHDNB = L, MODE_SEL [1:0] = 2'bXX<br>VREF15 = OFF, VREF25 = OFF<br>AMP = OFF, $\Delta\Sigma$ ADC = OFF<br>OSC = OFF, Ta= +25 °C            |  |  |  |  |  |

| Shutdown Current 1_2<br>(OFF) = HSHDN                | I <sub>QVB1_2</sub> | -   | 0     | 10   | μA   | SHDNB = L, MODE_SEL [1:0] = 2'bXX<br>VREF15 = OFF, VREF25 = OFF<br>AMP = OFF, $\Delta\Sigma$ ADC = OFF<br>OSC = OFF, Ta= -40 °C to +125 °C |  |  |  |  |  |

| Shutdown Current 2_1<br>(Soft Shutdown Mode) = SSHDN | I <sub>QVB2_1</sub> | -   | 20    | 40   | μA   | SHDNB = H, MODE_SEL [1:0] = 2'b11<br>VREF15 = ON, VREF25 = OFF<br>AMP = OFF, $\Delta\Sigma$ ADC = OFF<br>OSC = OFF, Ta= +25 °C             |  |  |  |  |  |

| Shutdown Current 2_2<br>(Soft Shutdown Mode) = SSHDN | I <sub>QVB2_2</sub> | -   | 20    | 200  | μA   | SHDNB = H, MODE_SEL [1:0] = 2'b11<br>VREF15 = ON, VREF25 = OFF<br>AMP = OFF, $\Delta\Sigma$ ADC = OFF<br>OSC = OFF, Ta= -40 °C to +125 °C  |  |  |  |  |  |

| Operating Current 1_1<br>(NORMAL Mode)               | I <sub>QVB3_1</sub> | -   | 2.50  | 3.75 | mA   | SHDNB = H, MODE_SEL [1:0] = 2'b01<br>VREF15 = ON, VREF25 = ON<br>AMP = ON, ΔΣADC = ON<br>OSC = ON, Ta= +25 °C                              |  |  |  |  |  |

| Operating Current 1_2<br>(NORMAL Mode)               | I <sub>QVB3_2</sub> | -   | 2.50  | 7.50 | mA   | SHDNB = H, MODE_SEL [1:0] = 2'b01<br>VREF15 = ON, VREF25 = ON<br>AMP = ON, ΔΣADC = ON<br>OSC = ON, Ta= -40 °C to +125 °C                   |  |  |  |  |  |

# **Electrical Characteristics – continued**

| Descenter                             | Cirrente al           |     | Limit |      | 1.1-14 | Condition                                                                                                                                                                                                                                                                      |

|---------------------------------------|-----------------------|-----|-------|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                             | Symbol                | Min | Тур   | Max  | Unit   | Condition                                                                                                                                                                                                                                                                      |

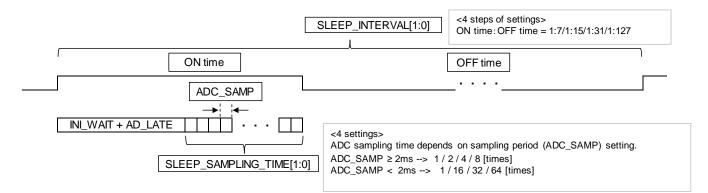

| Operating Current 2_1<br>(SLEEP Mode) | I <sub>QVB4_1_1</sub> | -   | 700   | 1050 | μA     | SHDNB = H, MODE_SEL [1:0] = 2'b10,<br>SLEEP_INTERVAL [1:0] = 2'b00,<br>SLEEP_SAMPLING_TIME [1:0] = 2'b00,<br>VREF15 = ON, VREF25 = Intermittent Operation<br>AMP = Intermittent Operation,<br>$\Delta\Sigma$ ADC = Intermittent Operation, OSC = ON,<br>Ta = +25 °C            |

| Operating Current 2_2<br>(SLEEP Mode) | I <sub>QVB4_1_2</sub> | -   | 700   | 1250 | μA     | SHDNB = H, MODE_SEL [1:0] = 2'b10,<br>SLEEP_INTERVAL [1:0] = 2'b00,<br>SLEEP_SAMPLING_TIME [1:0] = 2'b00,<br>VREF15 = ON, VREF25 = Intermittent Operation<br>AMP = Intermittent Operation,<br>$\Delta\Sigma$ ADC = Intermittent Operation, OSC = ON,<br>Ta = -40 °C to +125 °C |

| Operating Current 3_1<br>(SLEEP Mode) | I <sub>OVB4_2_1</sub> | -   | 600   | 900  | μΑ     | SHDNB = H, MODE_SEL [1:0] = 2'b10,<br>SLEEP_INTERVAL [1:0] = 2'b01,<br>SLEEP_SAMPLING_TIME [1:0] = 2'b00,<br>VREF15 = ON, VREF25 = Intermittent Operation<br>AMP = Intermittent Operation,<br>$\Delta\Sigma$ ADC = Intermittent Operation, OSC = ON,<br>Ta= +25 °C             |

| Operating Current 3_2<br>(SLEEP Mode) | I <sub>OVB4_2_2</sub> | -   | 600   | 1100 | μΑ     | SHDNB = H, MODE_SEL [1:0] = 2'b10,<br>SLEEP_INTERVAL [1:0] = 2'b01,<br>SLEEP_SAMPLING_TIME [1:0] = 2'b00,<br>VREF15 = ON, VREF25 = Intermittent Operation<br>AMP = Intermittent Operation,<br>$\Delta\Sigma$ ADC = Intermittent Operation, OSC = ON,<br>Ta = -40 °C to +125 °C |

| Operating Current 4_1<br>(SLEEP Mode) | I <sub>QVB4_3_1</sub> | -   | 540   | 810  | μΑ     | SHDNB = H, MODE_SEL [1:0] = 2'b10,<br>SLEEP_INTERVAL [1:0] = 2'b10,<br>SLEEP_SAMPLING_TIME [1:0] = 2'b00,<br>VREF15 = ON, VREF25 = Intermittent Operation<br>AMP = Intermittent Operation,<br>$\Delta\Sigma$ ADC = Intermittent Operation, OSC = ON,<br>Ta= +25 °C             |

| Operating Current 4_2<br>(SLEEP Mode) | I <sub>QVB4_3_2</sub> | -   | 540   | 1010 | μΑ     | SHDNB = H, MODE_SEL [1:0] = 2'b10,<br>SLEEP_INTERVAL [1:0] = 2'b10,<br>SLEEP_SAMPLING_TIME [1:0] = 2'b00,<br>VREF15 = ON, VREF25 = Intermittent Operation<br>AMP = Intermittent Operation,<br>$\Delta\Sigma$ ADC = Intermittent Operation, OSC = ON,<br>Ta = -40 °C to +125 °C |

| Operating Current 5_1<br>(SLEEP Mode) | I <sub>OVB4_4_1</sub> | -   | 500   | 750  | μΑ     | SHDNB=H, MODE_SEL[1:0]=2'b10,<br>SLEEP_INTERVAL[1:0]=2'b11,<br>SLEEP_SAMPLING_TIME[1:0]=2'b00,<br>VREF15=ON, VREF25=Intermittent Operation<br>AMP=Intermittent Operation,<br>$\Delta\Sigma$ ADC=Intermittent Operation, OSC = ON,<br>Ta= +25 °C                                |

| Operating Current 5_2<br>(SLEEP Mode) | I <sub>QVB4_4_2</sub> | -   | 500   | 950  | μΑ     | SHDNB=H, MODE_SEL[1:0]=2'b10,<br>SLEEP_INTERVAL[1:0]=2'b11,<br>SLEEP_SAMPLING_TIME[1:0]=2'b00,<br>VREF15=ON, VREF25=Intermittent Operation<br>AMP=Intermittent Operation,<br>$\Delta\Sigma$ ADC=Intermittent Operation, OSC = ON,<br>Ta= -40 °C to +125 °C                     |

# **Electrical Characteristics – continued**

(Unless otherwise specified, Ta = -40 °C to +125 °C, VCC = 5.0 V, VDD = 3.3 V)

| Parameter                    | Symbol               |      | Limit   |      | Unit | Condition                                                                      |

|------------------------------|----------------------|------|---------|------|------|--------------------------------------------------------------------------------|

| Falameter                    | Symbol               | Min  | Min Typ |      | Unit | Condition                                                                      |

| AMP Block                    |                      |      |         |      |      |                                                                                |

| Analog Input Valtage Range 1 | V <sub>AIN1</sub>    | -200 | -       | +400 | mV   | AMP_GAIN [1:0] = 2'b00(Gain = 5 V/V)                                           |

| Analog Input Valtage Range 2 | V <sub>AIN2</sub>    | -80  | -       | +80  | mV   | AMP_GAIN [1:0] = 2'b01(Gain = 25 V/V)<br>AMP_GAIN [1:0] = 2'b10(Gain = 25 V/V) |

| Analog Input Valtage Range 3 | V <sub>AIN3</sub>    | -40  | -       | +40  | mV   | AMP_GAIN [1:0] = 2'b11(Gain = 51 V/V)                                          |

| Gain Setting Time            | t <sub>GAINSET</sub> | -    | -       | 1.5  | ms   |                                                                                |

| ADC Block                    |                      |      | •       | 1    |      |                                                                                |

| Resolution                   | -                    | -    | -       | 16   | bit  |                                                                                |

| ADC Conversion Time 1        | t <sub>CONV1</sub>   | 0.20 | 0.25    | 0.30 | ms   | MCIC_R [1:0] = 2'b00<br>(Down sampling value = 32)                             |

| ADC Conversion Time 2        | t <sub>CONV2</sub>   | 0.80 | 1.00    | 1.20 | ms   | MCIC_R [1:0] = 2'b01<br>(Down sampling value = 128)                            |

| ADC Conversion Time 3        | t <sub>CONV3</sub>   | 1.60 | 2.00    | 2.40 | ms   | MCIC_R [1:0] = 2'b10<br>(Down sampling value = 256)                            |

| ADC Conversion Time 4        | t <sub>CONV4</sub>   | 6.40 | 8.00    | 9.60 | ms   | MCIC_R [1:0] = 2'b11<br>(Down sampling value = 1024)                           |

| EXADIN Valtage Range         | V <sub>EXADIN</sub>  | 0.5  | -       | 4.5  | V    |                                                                                |

| Parameter                  | Symbol                   |       | Limit |       | Unit | Condition           |  |  |  |

|----------------------------|--------------------------|-------|-------|-------|------|---------------------|--|--|--|

| Falameter                  | Symbol                   | Min   | Тур   | Max   | Unit | Condition           |  |  |  |

| UVLO (VCC)                 | UVLO (VCC)               |       |       |       |      |                     |  |  |  |

| VCC UVLO Detect Voltage    | V <sub>CC_UVLOD</sub>    | 2.700 | 2.800 | 2.900 | V    | VCC = Sweep down    |  |  |  |

| VCC UVLO Release           | V <sub>CC_UVLOR</sub>    | 2.717 | 3.000 | 3.283 | V    | VCC = Sweep up      |  |  |  |

| UVLO (VREF15)              |                          |       |       |       |      |                     |  |  |  |

| VREF15 UVLO Detect Voltage | V <sub>REF15_UVLOD</sub> | 1.352 | 1.380 | 1.408 | V    | VREF15 = Sweep down |  |  |  |

| UVLO (VDD)                 |                          |       |       |       |      |                     |  |  |  |

| VDD UVLO Detect Voltage    | V <sub>DD_UVLOD</sub>    | 1.550 | 1.700 | 1.850 | V    | VDD = Sweep down    |  |  |  |

| VDD UVLO Release           | V <sub>DD_UVLOR</sub>    | 1.650 | 1.800 | 1.950 | V    | VDD = Sweep up      |  |  |  |

# **Electrical Characteristics - continued**

| Symbol                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                  | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Тур                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| V <sub>IH_SHDNB</sub>   | VCCx0.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | VCC+0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $V_{\text{IL\_SHDNB}}$  | -0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | +VCCx0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| I <sub>OFF_SHDNB</sub>  | -1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | +1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| V <sub>OL_INTB1</sub>   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I <sub>O</sub> = 1 mA, Ta= +25 °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| V <sub>OL_INTB2</sub>   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I <sub>O</sub> = 1 mA, Ta= -40 °C to +125 °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| I <sub>OLK_INTB</sub>   | -1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | +1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | INTB = 5.5 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>OL_ALARMB1</sub> | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | l <sub>o</sub> = 1 mA, Ta= +25 °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

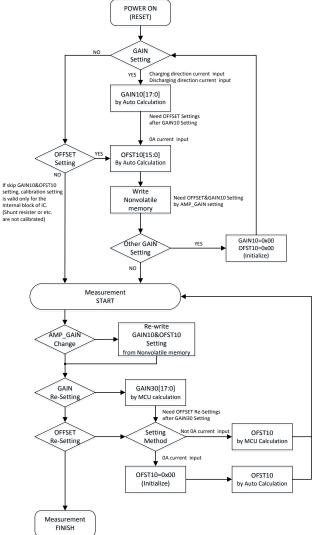

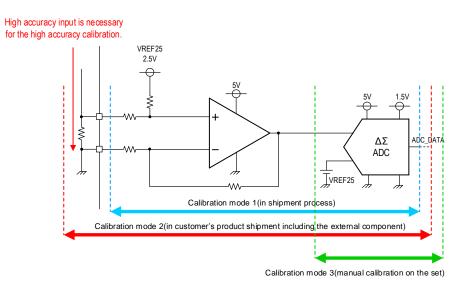

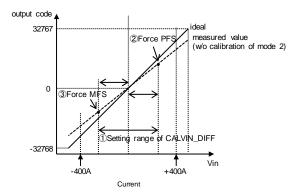

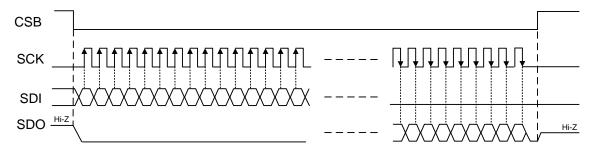

| V <sub>OL_ALARMB2</sub> | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I <sub>O</sub> = 1 mA, Ta= -40 °C to +125 °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |