# Automotive Intelligent Power Device Single Channel 20 mΩ High Side Switch

# BV1HB020EFJ-C

### **General Description**

The BV1HB020EFJ-C single channel 20 mΩ Intelligent High Side Power Device integrates an Overcurrent load protection, a dual Temperature Shutdown mechanism which limits the internal thermal transients and reduces the mechanical stress of the IC, and a smart Active-Clamp circuit to dissipate the magnetic energy while switching off inductive loads and to protect internal circuits from overvoltage surges. Embedded Current Sense and Diagnostic features provide real time load current information and open or short circuit feedback in both on and off state. A 3 V and 5 V CMOS compatible input pin offers direct microcontroller connection without special interfaces or level shifters. These in conjunction with a wide input voltage range make the High Side IPD a highperformance component suitable for 12 V battery connected automotive applications.

### **Features**

- AEC-Q100 Qualified<sup>(Note 1)</sup>

- Short Circuit Load Protection

- Overcurrent Limitation

- Active Clamp and Overvoltage Protection

- Dual Temperature Shutdown

- Undervoltage Lock Out

- Integrated Current SENSE Circuit

- Loss of Ground Protection

- Open Load and Short to Battery Diagnostics (Note 1) Grade 1

# **Applications**

- Driver for Resistive, Inductive and Capacitive Loads

- MOSFET, Relay and Fuse Replacement

- Intelligent Power Device for 12 V Automotive Applications

### **Key Specifications**

Supply Nominal Voltage Range:

Low Operating Voltage (cranking):

Overvoltage Protection:

ON Resistance:

Overcurrent Limit:

Sleep Current:

Operating Current:

Junction Temperature Range (Tj):

6 V to 28 V

4 V (Max)

41 V (Min)

20 mΩ (Typ)

51 A (Typ)

51 A (Typ)

-40 °C to +150 °C

### **Package**

W (Typ) x D (Typ) x H (Max) HTSOP-J8 4.9 mm x 6.0 mm x 1.0 mm

- Thermally Enhanced Thin Small-Outline 8 pin package with 1.27 mm Pin Pitch

- Exposed Pad for improved thermal performance

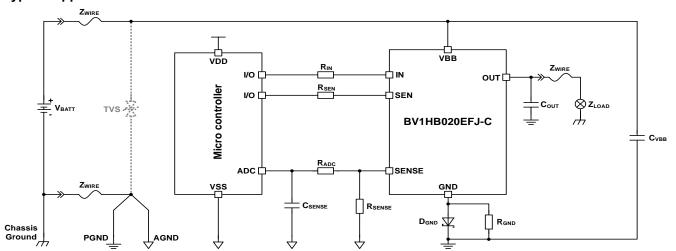

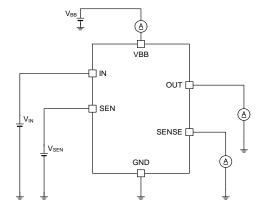

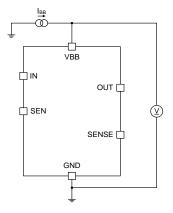

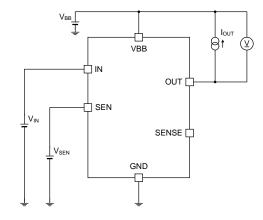

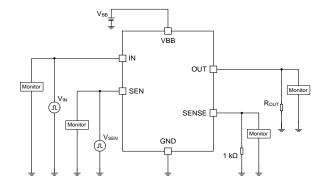

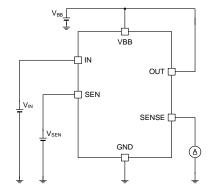

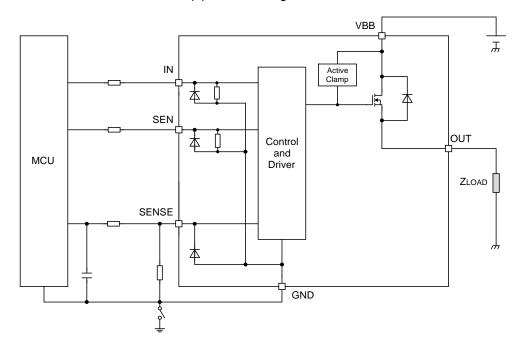

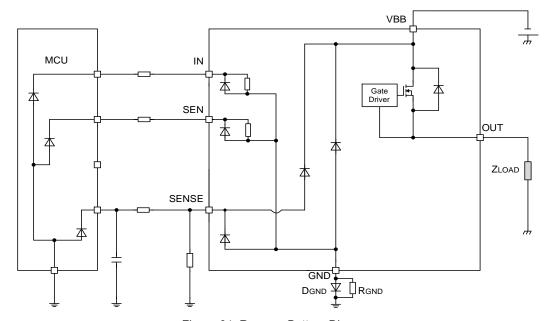

### **Typical Application Circuit**

Figure 1. Typical Application Diagram

OProduct structure: Silicon integrated circuit OThis product has no designed protection against radioactive rays.

# **Table of Contents**

| General Description                          | 1  |

|----------------------------------------------|----|

| Features                                     | 1  |

| Applications                                 | 1  |

| Key Specifications                           | 1  |

| Package                                      | 1  |

| Typical Application Circuit                  | 1  |

| Table of Contents                            | 2  |

| Pin Configuration                            | 3  |

| Pin Description                              | 3  |

| Definitions                                  | 4  |

| Absolute Maximum Ratings                     | 5  |

| Recommended Operating Conditions             | 6  |

| Thermal Resistance                           | 7  |

| Electrical Characteristics                   | 11 |

| Typical Performance Curves                   | 13 |

| Measurement Circuit Diagram                  | 22 |

| Block Diagram                                | 24 |

| Features Description                         | 25 |

| Application Circuit Example                  | 34 |

| Recommended External Components Example      | 34 |

| I/O Equivalence Circuits                     | 35 |

| Operational Notes                            | 36 |

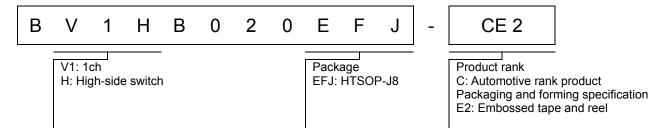

| Ordering Information                         | 38 |

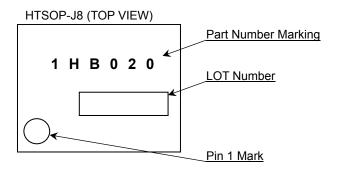

| Marking Diagram                              | 38 |

| Physical Dimension and Packaging Information | 39 |

| Revision History                             | 40 |

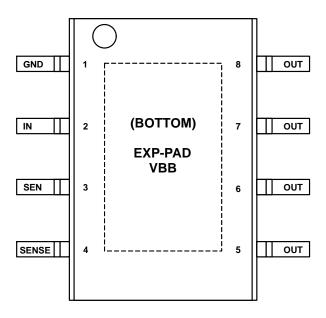

# **Pin Configuration**

HTSOP-J8 (Top View)

Figure 2. Pin Configuration

# **Pin Description**

| Pin No. | Pin Name | Function                                           |

|---------|----------|----------------------------------------------------|

| 1       | GND      | Device Ground pin                                  |

| 2       | IN       | Input Pin. Turns on the Switch. Active "High"      |

| 3       | SEN      | Current Sense and diagnostic enable. Active "High" |

| 4       | SENSE    | Current Sense analog output pin                    |

| 5 to 8  | OUT      | High Side Switch Power Output(Note 1)              |

| EXP-PAD | VBB      | Exposed-Pad. Power Supply Voltage Line Input       |

(Note 1) Output pins are internally shorted. Please connect the respective pins together on the PCB such as the metal traces can withstand the desired maximum current.

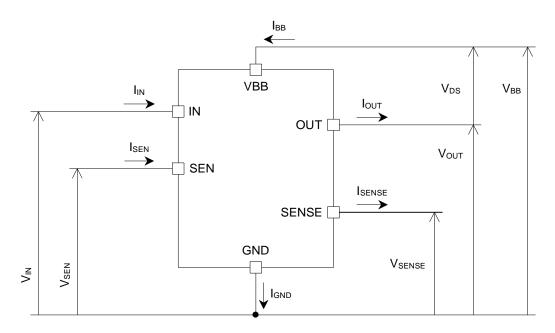

# **Definitions**

Figure 3. Voltage and Current Definitions

# **Absolute Maximum Ratings**

| Parameters                                                            | Symbol                       | Ratings                                         | Unit     | Conditions                                                                                                         |

|-----------------------------------------------------------------------|------------------------------|-------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------|

| [Power Supply / GND pin]                                              | L                            |                                                 | 1        |                                                                                                                    |

| DC Supply Voltage                                                     | $V_{BB}$                     | -0.3 to +36                                     | V        |                                                                                                                    |

| Supply Voltage at load dump                                           | $V_{BB\_LD}$                 | 40                                              | V        | ISO16750-2, Ri = 2 Ω                                                                                               |

| Supply Voltage<br>(Output to GND short) (Note 4)                      | V <sub>BB_SC</sub>           | -0.3 to +24                                     | V        | AEC-Q100-012                                                                                                       |

| Supply Voltage<br>(When battery is connected in<br>reverse direction) | V <sub>BB_REV</sub>          | -16                                             | V        | less than 2 minutes,<br>Tj = 25 °C, R <sub>L</sub> > 4 $\Omega$ ,<br>D <sub>GND</sub> , R <sub>GND</sub> connected |

| GND Pin Current                                                       | IGND                         | -50 to +30                                      | mA       | less than 2 minutes,<br>Tj = 25 °C,<br>D <sub>GND</sub> , R <sub>GND</sub> connected                               |

| [Input Pin]                                                           |                              |                                                 |          |                                                                                                                    |

| Input Voltage                                                         | VIN, VSEN                    | -0.3 to +7                                      | V        |                                                                                                                    |

| Input Current                                                         | lin, Isen                    | -2 to +2                                        | mA       |                                                                                                                    |

| Input Current<br>(When battery is connected in<br>reverse direction)  | lin_rev, Isen_rev            | -5                                              | mA       | less than 2 minutes,<br>Tj = 25 °C,<br>$R_{IN}$ , $R_{SEN} \ge 4.7$ kΩ                                             |

| [SENSE pin]                                                           |                              |                                                 |          |                                                                                                                    |

| SENSE Voltage                                                         | $V_{SENSE}$                  | -0.3 to +7                                      | V        |                                                                                                                    |

| SENSE Current                                                         | I <sub>SENSE</sub>           | -20 to internal limitation <sup>(Note 1)</sup>  | mA       | $R_{SENSE} = 1 k\Omega$                                                                                            |

| [OUT pin]                                                             |                              |                                                 |          |                                                                                                                    |

| Power Supply to Output Voltage                                        | V <sub>DS</sub>              | -0.3 to internal limitation <sup>(Note 2)</sup> | V        |                                                                                                                    |

| Maximum Output Current                                                | Іоит                         | internal<br>limitation <sup>(Note 3)</sup>      | Α        | Maximum V <sub>BB</sub> = 28 V                                                                                     |

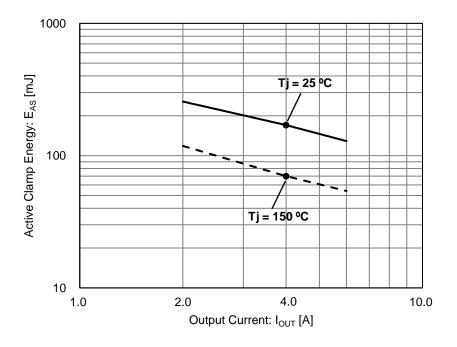

| Single Pulse Energy Rating <sup>(Note 4)</sup>                        | Eas_25°C                     | 170                                             | mJ       | Tj = 25 °C, V <sub>BB</sub> = 14 V,<br>I <sub>OUT(START)</sub> = 4 A<br>Tj = 150 °C, V <sub>BB</sub> = 14 V,       |

| omigio i dioo Enorgy i tating                                         | E <sub>AS_150°</sub> C       | 70                                              | mJ       | Tj = 150 °C, V <sub>BB</sub> = 14 V,<br>I <sub>OUT(START)</sub> = 4 A                                              |

| [Temperature]                                                         |                              |                                                 |          |                                                                                                                    |

| Storage Temperature Range                                             | Tstg                         | -55 to +150                                     | °C       |                                                                                                                    |

| Junction Temperature Range                                            | Tj                           | -40 to +150                                     | °C       |                                                                                                                    |

| Maximum Junction Temperature                                          | Tjmax                        | 150                                             | °C       |                                                                                                                    |

| [ESD] (Note 5)                                                        |                              |                                                 |          |                                                                                                                    |

| Electrostatic-Discharge Capability<br>Human Body Model - HBM          | VBB, OUT pins IN, SEN, SENSE | ±3<br>±2                                        | kV<br>kV |                                                                                                                    |

| Electrostatic-Discharge Capability Charged Device Model - CDM         | pins<br>All pins             | ±750                                            | V        |                                                                                                                    |

<sup>(</sup>Note 1) Internal limitation by SENSE voltage clamp and current-limitation protection. Please see the "Electrical Characteristics" section for more details. (Note 2) Internal limitation by output active-clamp overvoltage protection. Please see the "Electrical Characteristics" section for more details.

- Caution 1: Exposure to the absolute maximum ratings may cause permanent damage to the IC, may affect the device reliability and lifetime. Therefore, operation at or above the absolute maximum ratings is not recommended. The above-described values represent stress ratings and functional operation is not implied. In addition, no destructive conditions such as short or open can be assumed.

- Caution 2: If the IC is used in a manner that exceeds the maximum junction temperature the original characteristics of the IC will be degraded. If the junction temperature exceeds the maximum specified temperature, increase the board size, increase the area of copper foil for heat dissipation, or use a heat sink. Consider reducing the thermal resistance so that the maximum junction temperature is not exceeded.

- Caution 3: When an inductive load is turned off, the Vout voltage drops below ground level. An integrated active-clamp (overvoltage) protection limits the maximum V<sub>DS</sub> across the power transistor and the inductive energy is dissipated internally. The energy can be calculated using the following simplified

<sup>(</sup>Note 3) Internal limitation by output overcurrent protection. Please see the "Electrical Characteristics" section for more details.

<sup>(</sup>Note 4) Specified by design and/or statistical analysis of correlated parameters tested in production.

(Note 5) Measured as per EIA/JEDEC and AEC-Q100 Standard. HMB-Measured as per JESD22-A114D and AEC-Q100-002.

CDM-Measured as per JESD22-C101C and AEC-Q100-011.

# **Absolute Maximum Ratings - continued**

$$E_L = V_{DSCLP} \times \left[ \frac{V_{BB} - V_{DSCLP}}{R_L} \times \ln \left( 1 - \frac{R_L \times I_{OUT(START)}}{V_{BB} - V_{DSCLP}} \right) + I_{OUT(START)} \right] \times \frac{L}{R_L}$$

Where:

${\it L\,}$  is the inductance value of the inductive load.

$R_L$  is the resistance value of the load.

$V_{BB}$  is the supply voltage.

*V*<sub>DSCLP</sub> is the clamping voltage.

$I_{\mathrm{OUT}(\mathrm{START})}$  is the current flowing through the inductive load at the instance the inductive load is turned off.

In simplified form, if  $R_L$  is neglected.

$$E_L = \frac{1}{2} \times L \times I_{OUT(START)}^2 \times \left(1 - \frac{V_{BB}}{V_{BB} - V_{DSCLP}}\right)$$

Caution 4: The maximum  $E_L$  energy the device can dissipate for a given  $I_{OUT(START)}$  is limited by the maximum thermal transient the power transistor can handle, hence the maximum inductance L must be selected with respect to the maximum given  $I_{OUT(START)}$ .

Figure 4. Active Clamp Energy vs Output Current

**Recommended Operating Conditions**

| Parameters                            | Symbol          | MIN | TYP | MAX  | Unit |

|---------------------------------------|-----------------|-----|-----|------|------|

| Supply Nominal Voltage Range (Note 1) | V <sub>BB</sub> | 6   | 14  | 28   | V    |

| Input Voltage                         | VIN, VSEN       | 0   | -   | 5.5  | V    |

| Operating Junction Temperature        | Tj              | -40 | +25 | +150 | °C   |

| Input Frequency                       | fin             | -   | -   | 1    | kHz  |

(Note 1) An extended supply operating voltage range from 4.0 V up to 28 V is possible after start-up; protections are operational. The device is functional up to 36 V and protections are active, however parameter deviations are possible. Please refer to the "Electrical Characteristics" section and the "Features Description" section.

# Thermal Resistance (Note 1)

| ciliai Resistance                                           |             |       | ı    |      |          |

|-------------------------------------------------------------|-------------|-------|------|------|----------|

| Parameters                                                  | Symbol      | TYP   | Unit | Cond | itions   |

| HTSOP-J8                                                    |             |       |      |      |          |

| Thermal Resistance between junction and ambient temperature |             | 127.6 | °C/W | 1s   | (Note 2) |

|                                                             | θμα         | 39.3  | °C/W | 2s   | (Note 3) |

|                                                             |             | 26.5  | °C/W | 2s2p | (Note 4) |

| Thermal characterization parameter between                  |             | 12    | °C/W | 1s   | (Note 2) |

| junction and top center of the outside surface of the       | $\Psi_{JT}$ | 4     | °C/W | 2s   | (Note 3) |

| component package                                           |             | 3     | °C/W | 2s2p | (Note 4) |

(Note 1) Based on JESD51-2A(Still-Air). Specified by design.

(Note 2) Using a PCB board based on JESD51-3.

(Note 3) Using a PCB board based on JESD51-5.

(Note 4) Using a PCB board based on JESD51-5, 7.

Caution: The values presented here were measured/simulated under a specific set of conditions and should be regarded only as a guideline on how to estimate the thermal behavior of the application and should not be used as design parameters. A careful evaluation of the actual application values should be done to confirm the estimated results

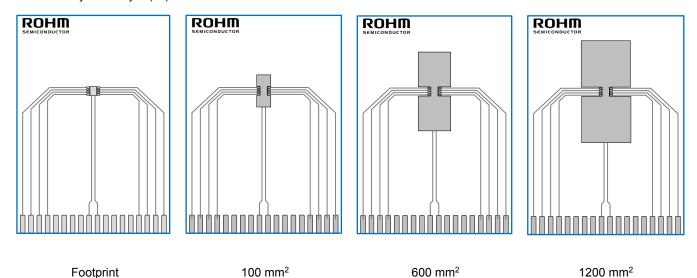

# ■ PCB Layout 1 Layer (1s)

Figure 5. PCB Layout 1 Layer (1s)

| Dimension              | Value                                                                        |

|------------------------|------------------------------------------------------------------------------|

| Board Finish Thickness | 1.57 mm                                                                      |

| Board Dimension        | 76.2 mm x 114.3 mm                                                           |

| Board Material         | FR4                                                                          |

| Copper Thickness       | 0.070 mm (Cu: 2 oz)                                                          |

| Copper Foil Area       | Footprint / 100 mm <sup>2</sup> / 600 mm <sup>2</sup> / 1200 mm <sup>2</sup> |

# Thermal Resistance - continued

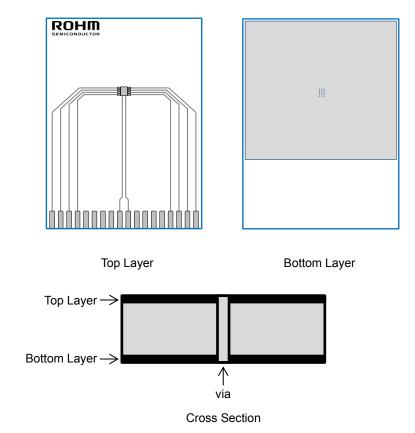

■ PCB Layout 2 Layers (2s)

Figure 6. PCB Layout 2 Layers (2s)

| Dimension                              | Value                         |

|----------------------------------------|-------------------------------|

| Board Finish Thickness                 | 1.60 mm                       |

| Board Dimension                        | 76.2 mm x 114.3 mm            |

| Board Material                         | FR4                           |

| Copper Thickness (Top / Bottom Layers) | 0.070 mm (Cu: 1 oz + plating) |

| Thermal Vias Separation / Diameter     | 1.2 mm / 0.3 mm               |

# Thermal Resistance - continued

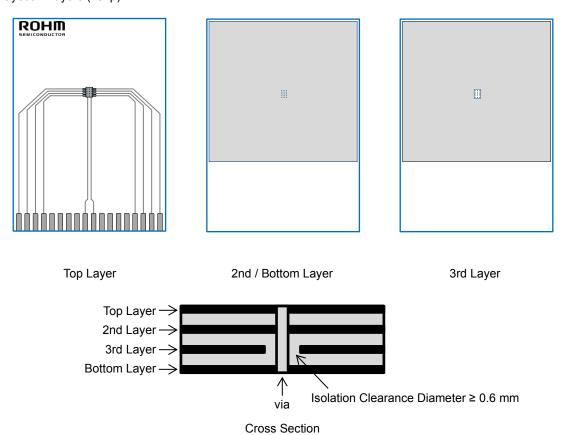

■ PCB Layout 4 Layers (2s2p)

Figure 7. PCB Layout 4 Layers (2s2p)

| Dimension                              | Value                         |

|----------------------------------------|-------------------------------|

| Board Finish Thickness                 | 1.60 mm                       |

| Board Dimension                        | 76.2 mm x 114.3 mm            |

| Board Material                         | FR4                           |

| Copper Thickness (Top / Bottom Layers) | 0.070 mm (Cu: 1 oz + plating) |

| Copper Thickness (Inner Layers)        | 0.035 mm                      |

| Thermal Vias Separation / Diameter     | 1.2 mm / 0.3 mm               |

# Thermal Resistance - continued

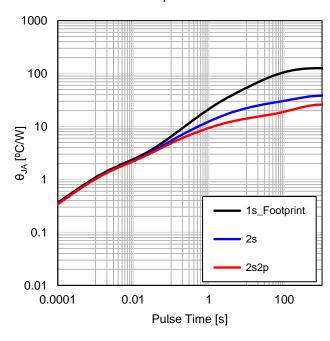

# ■ Thermal Resistance Graphs

140

120

100

80

60

40

20

0 200 400 600 800 1000 1200

Copper Foil Area (1s) [mm²]

Figure 8. Transient Thermal Resistance

Figure 9. Thermal Resistance

**Electrical Characteristics** (Unless otherwise specified  $V_{BB}$  = 6 V to 28 V, Tj = -40 °C to +150 °C)

| Parameters                                     | Symbol                     | Ratings |      | Unit | Conditions |                                                                                                                             |

|------------------------------------------------|----------------------------|---------|------|------|------------|-----------------------------------------------------------------------------------------------------------------------------|

|                                                |                            | MIN     | TYP  | MAX  |            |                                                                                                                             |

| [Power Supply Section]                         |                            |         |      |      |            |                                                                                                                             |

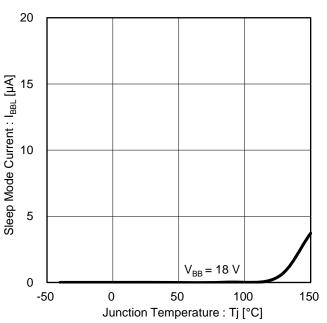

|                                                | I <sub>BBL1</sub>          | -       | -    | 0.5  | μΑ         | V <sub>BB</sub> = 18 V, V <sub>IN</sub> = 0 V, V <sub>SEN</sub> = 0 V,<br>V <sub>OUT</sub> = 0 V, Tj = 25 °C                |

| Sleep Mode Current                             | I <sub>BBL2</sub> (Note 1) | -       | -    | 1.0  | μΑ         | $V_{BB} = 18 \text{ V}, V_{IN} = 0 \text{ V}, V_{SEN} = 0 \text{ V}, V_{OUT} = 0 \text{ V}, T_j = 85 ^{\circ}\text{C}$      |

|                                                | I <sub>BBL3</sub>          | -       | -    | 20   | μΑ         | $V_{BB} = 18 \text{ V}, V_{IN} = 0 \text{ V}, V_{SEN} = 0 \text{ V},$<br>$V_{OUT} = 0 \text{ V}, T_j = 150 \text{ °C}$      |

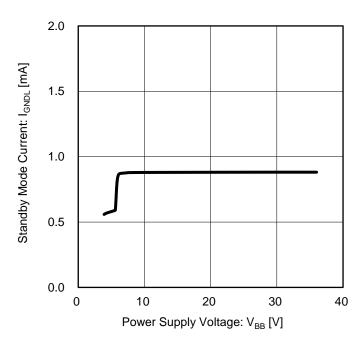

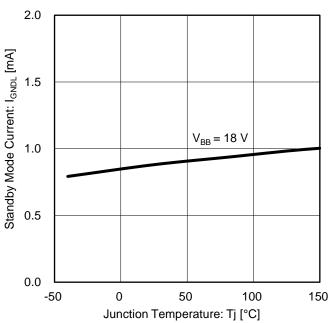

| Standby Mode Current (Diagnostic Function ON)  | I <sub>GNDL</sub>          | -       | 1.0  | 2.0  | mA         | V <sub>BB</sub> = 18 V, V <sub>IN</sub> = 0 V, V <sub>SEN</sub> = 5 V                                                       |

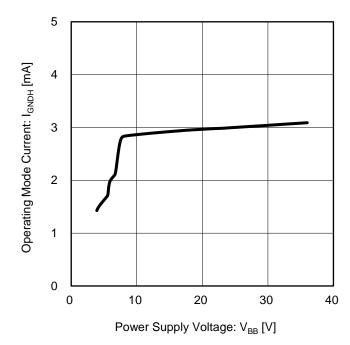

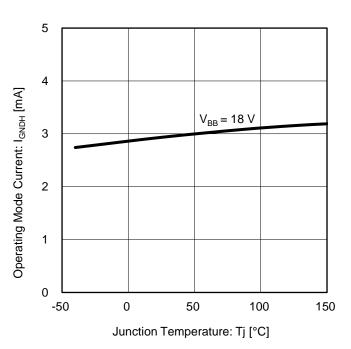

| Operating Mode Current                         | Igndh                      | -       | 3.0  | 5.0  | mA         | V <sub>BB</sub> = 18 V, V <sub>IN</sub> = 5 V                                                                               |

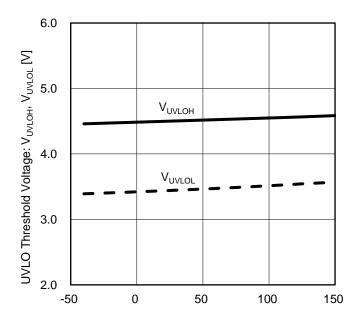

| UVLO Threshold Voltage                         | Vuvloh                     | 4.2     | 4.6  | 5.0  | V          | $V_{BB}$ : sweep-up, $V_{IN}$ = 5 V, $V_{OUT}$ reaches more than $V_{BB}$ - 1 V                                             |

|                                                | V <sub>UVLOL</sub>         | 3.0     | 3.5  | 4.0  | V          | V <sub>BB</sub> : sweep-down, V <sub>IN</sub> = 5 V,<br>V <sub>OUT</sub> reaches less than 1 V                              |

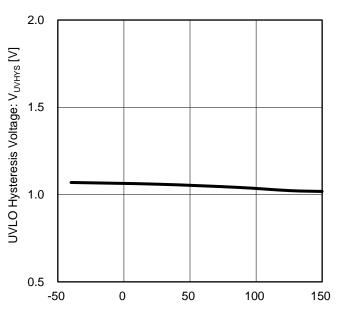

| UVLO Hysteresis Voltage                        | V <sub>UVHYS</sub>         | -       | 1.1  | -    | V          | Vuvhys = Vuvloh - Vuvlol                                                                                                    |

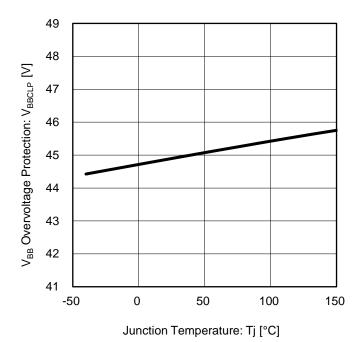

| V <sub>BB</sub> Overvoltage Protection         | VBBCLP                     | 41      | 45   | 49   | V          | I <sub>BB</sub> = 10 mA                                                                                                     |

| [Input Section (IN / SEN pin)]                 | <del>, ,</del>             |         |      |      | 1          | ,                                                                                                                           |

| High Level Input Voltage                       | VIH                        | 2.1     | -    | -    | V          |                                                                                                                             |

| Low Level Input Voltage                        | VIL                        | -       | -    | 0.9  | V          |                                                                                                                             |

| Input Hysteresis Voltage                       | V <sub>IHYS</sub>          | -       | 0.25 | -    | V          |                                                                                                                             |

| High Level Input Current                       | Iн                         | -       | 50   | 100  | μΑ         | V <sub>IN</sub> , V <sub>SEN</sub> = 5 V                                                                                    |

| Low Level Input Current                        | lı∟                        | -       | 5    | 10   | μΑ         | V <sub>IN</sub> , V <sub>SEN</sub> = 0.5 V                                                                                  |

| [Output Section]                               |                            |         |      |      |            |                                                                                                                             |

|                                                | R <sub>ON1</sub>           | -       | 20   | 25   | mΩ         | $V_{BB} \ge 8 \text{ V}, \text{ Tj} = 25 \text{ °C}, I_{OUT} = 4 \text{ A}$                                                 |

| Output ON Resistance                           | R <sub>ON2</sub>           | -       | -    | 44   | mΩ         | V <sub>BB</sub> ≥ 8 V, Tj = 150 °C, I <sub>OUT</sub> = 4 A                                                                  |

|                                                | R <sub>ON3</sub>           | -       | -    | 30   | mΩ         | V <sub>BB</sub> = 6 V, Tj = 25 °C, I <sub>OUT</sub> = 4 A                                                                   |

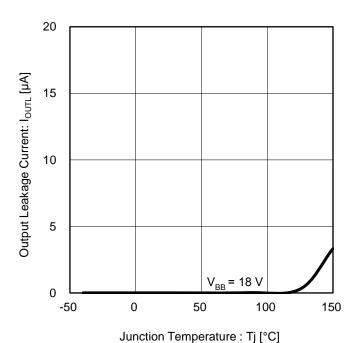

|                                                | loutl1                     | -       | -    | 0.5  | μΑ         | V <sub>BB</sub> = 18 V, V <sub>IN</sub> = 0 V, V <sub>SEN</sub> = 0 V,<br>V <sub>OUT</sub> = 0 V, Tj = 25 °C                |

| Output Leakage Current                         | IOUTL2 (Note 1)            | -       | -    | 1.0  | μΑ         | $V_{BB} = 18 \text{ V}, V_{IN} = 0 \text{ V}, V_{SEN} = 0 \text{ V}, V_{OUT} = 0 \text{ V}, T_j = 85 ^{\circ}\text{C}$      |

|                                                | <b>Г</b> ОИТL3             | -       | -    | 20   | μΑ         | $V_{BB} = 18 \text{ V}, V_{IN} = 0 \text{ V}, V_{SEN} = 0 \text{ V}, V_{OUT} = 0 \text{ V}, T_j = 150 °C$                   |

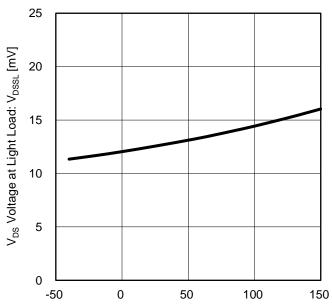

| V <sub>DS</sub> Voltage at Light Load          | VDSSL                      | -       | 13   | 27   | mV         | V <sub>IN</sub> = 5 V, I <sub>OUT</sub> = 100 mA                                                                            |

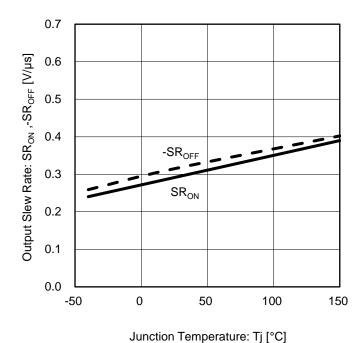

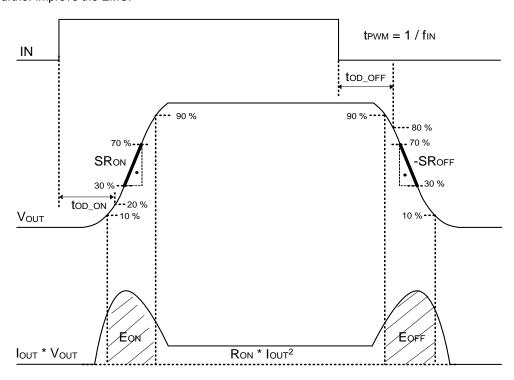

| Output Slew Rate when ON                       | SRon                       | -       | 0.3  | 0.7  | V/µs       | $V_{BB} = 14 \text{ V}, R_L = 4 \Omega, T_J = 25 \text{ °C}, V_{OUT} = 30 \% \text{ to } 70 \% \text{ of } V_{BB}$          |

| Output Slew Rate when OFF                      | -SR <sub>OFF</sub>         | -       | 0.3  | 0.7  | V/µs       | $V_{BB} = 14 \text{ V}, R_L = 4 \Omega, Tj = 25 ^{\circ}\text{C}, V_{OUT} = 70 \% \text{ to } 30 \% \text{ of } V_{BB}$     |

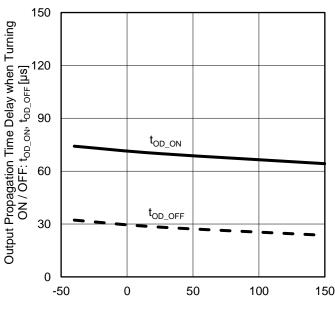

| Output Propagation Time Delay when Turning ON  | t <sub>OD_ON</sub>         | -       | 70   | 150  | μs         | $V_{BB}$ = 14 V, $R_L$ = 4 $\Omega$ , $T_J$ = 25 °C, $V_{OUT}$ rises at 20 % of $V_{BB}$                                    |

| Output Propagation Time Delay when Turning OFF | t <sub>OD_OFF</sub>        | -       | 30   | 100  | μs         | $V_{BB} = 14 \text{ V}, \text{ R}_{L} = 4 \Omega, \text{ Tj} = 25 ^{\circ}\text{C},$<br>$V_{OUT}$ drops at 80 % of $V_{BB}$ |

| Switch ON Energy                               | Eon                        | -       | 0.38 | -    | mJ         | $V_{BB} = 14 \text{ V}, R_L = 4 \Omega, Tj = 25 ^{\circ}\text{C}$                                                           |

| Switch OFF Energy                              | Eoff                       | -       | 0.38 | -    | mJ         | $V_{BB} = 14 \text{ V}, R_L = 4 \Omega, Tj = 25 ^{\circ}\text{C}$                                                           |

| Reverse Current <sup>(Note 1)</sup>            | IREVC                      | -       | -4   | -    | Α          | V <sub>IN</sub> = 5 V, Tj = 25 °C                                                                                           |

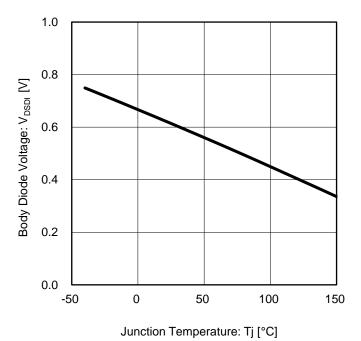

| Body Diode Voltage                             | V <sub>DSDI</sub>          | -       | 0.35 | 0.70 | V          | I <sub>OUT</sub> = -10 mA, Tj = 150 °C                                                                                      |

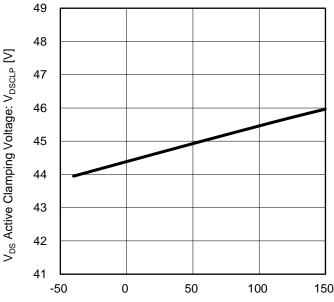

| V <sub>DS</sub> Active Clamping Voltage        | V <sub>DSCLP</sub>         | 41      | 45   | 49   | V          | I <sub>OUT</sub> = 10 mA                                                                                                    |

# **Electrical Characteristics – continued**

(Unless otherwise specified  $V_{BB}$  = 6 V to 28 V, Tj = -40 °C to +150 °C)

| Parameters                                                               | Symbol                | Ratings |      | Unit  | Conditions |                                                                                                               |  |

|--------------------------------------------------------------------------|-----------------------|---------|------|-------|------------|---------------------------------------------------------------------------------------------------------------|--|

|                                                                          |                       | MIN     | TYP  | MAX   | =          |                                                                                                               |  |

| [Output Protection Section]                                              |                       |         |      |       |            |                                                                                                               |  |

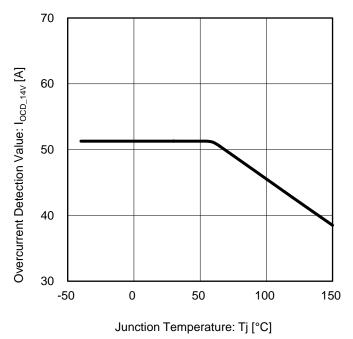

|                                                                          | I <sub>OCD_14V</sub>  | 34      | 51   | 70    | Α          | V <sub>BB</sub> = 14 V, Tj = 25 °C                                                                            |  |

| Overcurrent Detection Value                                              | I <sub>OCD_28V</sub>  | -       | 35   | -     | Α          | V <sub>BB</sub> = 28 V, Tj = 25 °C                                                                            |  |

| (Note 1) (Note 2)                                                        | IOCD_14VH             | -       | 35   | -     | Α          | V <sub>BB</sub> = 14 V, Tj = 150 °C                                                                           |  |

|                                                                          | locd_tsd              | -       | 28   | -     | Α          | V <sub>BB</sub> = 14 V, after TSD Detection                                                                   |  |

| Temperature Shutdown<br>Detection Threshold <sup>(Note 1)</sup> (Note 2) | $T_{TSD}$             | 150     | 175  | 200   | °C         |                                                                                                               |  |

| Temperature Shutdown<br>Detection Hysteresis <sup>(Note 1)</sup>         | T <sub>TSDHYS</sub>   | -       | 15   | -     | °C         |                                                                                                               |  |

| Dynamic Temperature<br>Protection Threshold <sup>(Note 1)</sup> (Note 2) | $T_{DT j}$            | -       | 90   | -     | К          | Differential temperature                                                                                      |  |

| [Diagnostic / SENSE Section]                                             |                       |         |      |       |            |                                                                                                               |  |

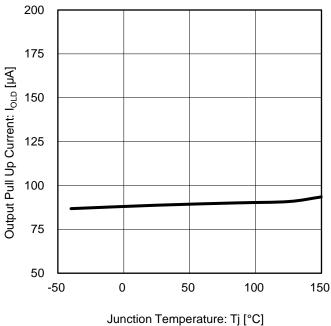

| Output Pull Up Current                                                   | lold                  | 50      | 100  | 200   | μA         | V <sub>BB</sub> = 14 V, V <sub>IN</sub> = 0 V, V <sub>SEN</sub> = 5 V, V <sub>OUT</sub> = 5 V                 |  |

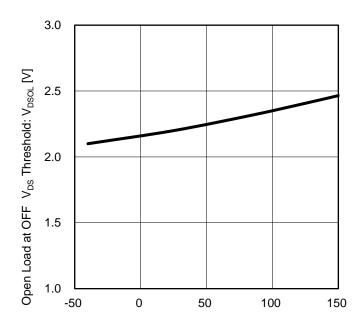

| Open Load at OFF V <sub>DS</sub><br>Threshold                            | VDSOL                 | 1.0     | 2.0  | 3.0   | V          | V <sub>IN</sub> = 0 V, V <sub>SEN</sub> = 5 V                                                                 |  |

| Output Pull Down Resistor                                                | R <sub>PD</sub>       | -       | 500  | -     | kΩ         |                                                                                                               |  |

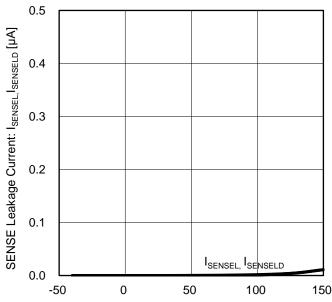

| SENSE Leakage Current                                                    | ISENSEL               | -       | -    | 0.5   | μA         | V <sub>IN</sub> = 0 V, V <sub>SEN</sub> = 0 V, V <sub>SENSE</sub> = 0 V                                       |  |

| OLIVOL Leakage Ourient                                                   | ISENSELD              | -       | -    | 0.5   | μA         | $V_{IN} = 0 \text{ V}, V_{SEN} = 5 \text{ V}, V_{SENSE} = 0 \text{ V}, V_{OUT} = 0 \text{ V}$                 |  |

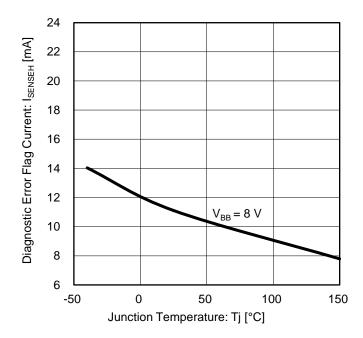

| Diagnostic Error Flag Current                                            | I <sub>SENSEH</sub>   | 6       | 13   | 23    | mA         | V <sub>BB</sub> ≥ 8 V, V <sub>SENSE</sub> = 0 V                                                               |  |

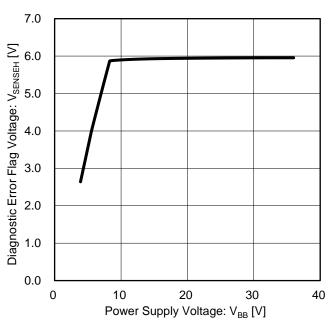

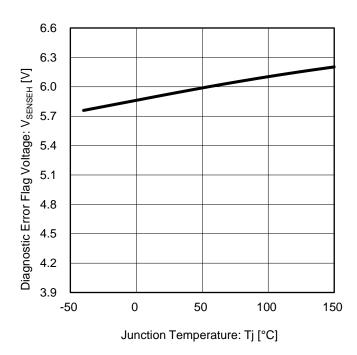

| Diagnostic Error Flag Voltage                                            | Vsenseh               | 4.0     | 5.8  | 6.9   | V          | $V_{BB} \ge 8 \text{ V}, R_{SENSE} = 1 \text{ k}\Omega$                                                       |  |

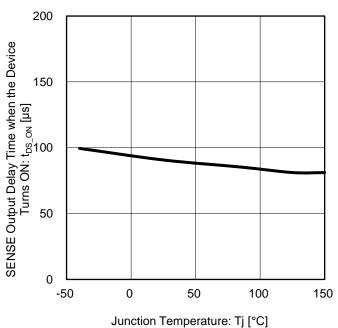

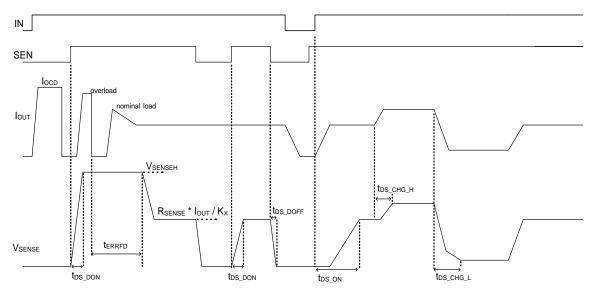

| SENSE Output Delay Time when the Device Turns ON                         | tds_on                | -       | 90   | 200   | μs         | $R_L = 4 \Omega$ , $V_{SEN} = V_{IN} = 0 V$ to 5 V, $R_{SENSE} = 1 k\Omega$                                   |  |

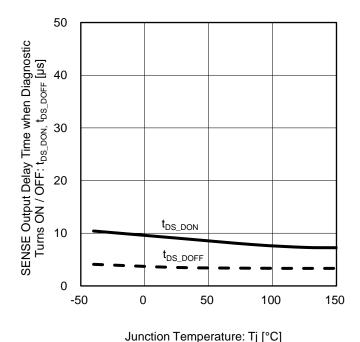

| SENSE Output Delay Time<br>when Diagnostic Turns ON                      | tds_don               | -       | 10   | 50    | μs         | $R_L = 4 \Omega$ , $V_{IN} = 5 V$ ,<br>$V_{SEN} = 0 V to 5 V$ , $R_{SENSE} = 1 k\Omega$                       |  |

| SENSE Output Delay Time when Diagnostic Turns OFF                        | t <sub>DS_DOFF</sub>  | -       | 10   | 50    | μs         | $R_L = 4 \Omega$ , $V_{IN} = 5 V$ ,<br>$V_{SEN} = 5 V$ to 0 V, $R_{SENSE} = 1 k\Omega$                        |  |

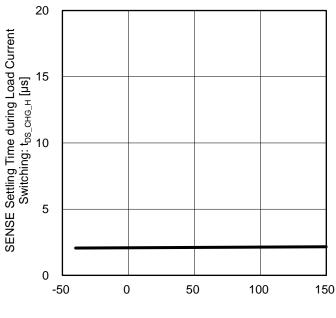

| SENSE Settling Time during                                               | tos_chg_h             | -       | -    | 20    | μs         | $V_{IN} = V_{SEN} = 5 V$ ,<br>$I_{OUT} = 2 A to 4 A$ , $R_{SENSE} = 1 k\Omega$                                |  |

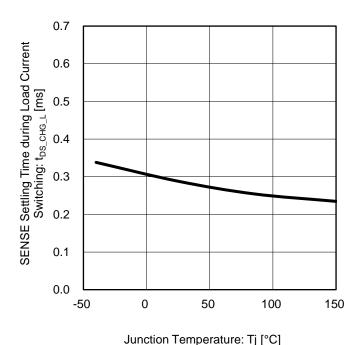

| Load Current Switching                                                   | t <sub>DS_CHG_L</sub> | -       | 0.3  | 0.7   | ms         | $V_{IN} = V_{SEN} = 5 \text{ V},$<br>$I_{OUT} = 2 \text{ A to } 0.1 \text{ A, R}_{SENSE} = 1 \text{ k}\Omega$ |  |

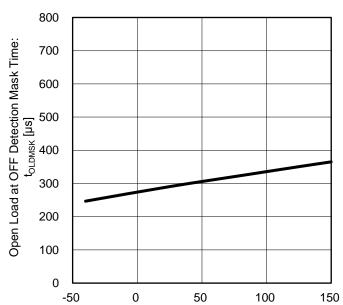

| Open Load at OFF Detection<br>Mask Time <sup>(Note 1)</sup> (Note 2)     | toldmsk               | -       | 300  | 800   | μs         | $V_{DS} = 0 \text{ V}, V_{SEN} = 5 \text{ V},$<br>$V_{IN} = 5 \text{ V to } 0 \text{ V}$                      |  |

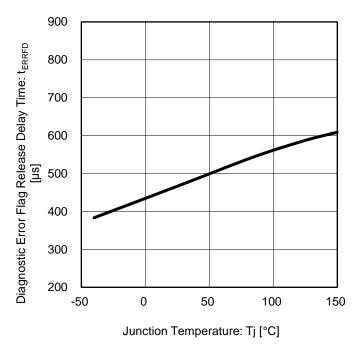

| Diagnostic Error Flag Release<br>Delay Time <sup>(Note 1)</sup> (Note 2) | t <sub>ERRFD</sub>    | -       | 500  | 1100  | μs         | V <sub>IN</sub> = 0 V, V <sub>SEN</sub> = 5 V,<br>V <sub>DS</sub> = 0 V to 5 V                                |  |

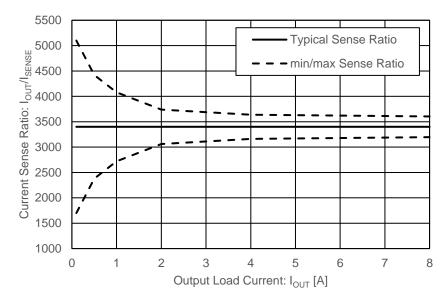

| Current Sense Ratio 1                                                    | K <sub>1</sub>        | -50 %   | 3450 | +50 % | -          | V <sub>BB</sub> = 14 V, I <sub>OUT</sub> = 0.1 A,<br>V <sub>IN</sub> = V <sub>SEN</sub> = 5 V                 |  |

| Current Sense Ratio 2                                                    | K <sub>2</sub>        | -30 %   | 3450 | +30 % | -          | V <sub>BB</sub> = 14 V, I <sub>OUT</sub> = 0.5 A,<br>V <sub>IN</sub> = V <sub>SEN</sub> = 5 V                 |  |

| Current Sense Ratio 3                                                    | <b>K</b> <sub>3</sub> | -20 %   | 3450 | +20 % | -          | $V_{BB} = 14 \text{ V}, I_{OUT} = 1 \text{ A},$<br>$V_{IN} = V_{SEN} = 5 \text{ V}$                           |  |

| Current Sense Ratio 4                                                    | K <sub>4</sub>        | -10 %   | 3450 | +10 % | -          | $V_{BB} = 14 \text{ V}, I_{OUT} = 2 \text{ A},$<br>$V_{IN} = V_{SEN} = 5 \text{ V}$                           |  |

| Current Sense Ratio 5                                                    | <b>K</b> 5            | -7 %    | 3450 | +7 %  | -          | V <sub>BB</sub> = 14 V, I <sub>OUT</sub> = 4 A,<br>V <sub>IN</sub> = V <sub>SEN</sub> = 5 V                   |  |

| Current Sense Ratio 6                                                    | <b>K</b> <sub>6</sub> | -6 %    | 3450 | +6 %  | -          | V <sub>BB</sub> = 14 V, I <sub>OUT</sub> = 8 A,<br>V <sub>IN</sub> = V <sub>SEN</sub> = 5 V                   |  |

| Current Sense Derating(Note 1)                                           | ΔK <sub>1</sub>       | -30     | -    | +30   | %          | K <sub>1</sub> vs K <sub>2</sub> , Tj = 25 °C                                                                 |  |

|                                                                          | ΔK <sub>2</sub>       | -5      | -    | +5    | %          | K <sub>4</sub> vs K <sub>5</sub> , Tj = 25 °C                                                                 |  |

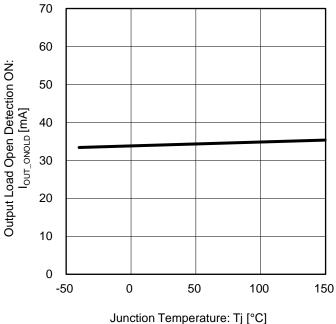

| Output Load Open Detection ON (Note 1) Specified by design and/or stati  | lout_onold            | 10.0    | 34.5 | 69.0  | mA         | Isense = 10 $\mu$ A = (34.5 mA / 3450)                                                                        |  |

(Note 1) Specified by design and/or statistical analysis of correlated parameters tested in production. (Note 2) Functional test only.

# **Typical Performance Curves**

Figure 10. Sleep Mode Current vs Power Supply Voltage

Figure 11. Sleep Mode Current vs Junction Temperature

Figure 12. Standby Mode Current vs Power Supply Voltage

Figure 13. Standby Mode Current vs Junction Temperature

Figure 14. Operating Mode Current vs Power Supply Voltage

Figure 15. Operating Mode Current vs Junction Temperature

Junction Temperature: Tj [°C]

Figure 16. UVLO Threshold Voltage vs

Junction Temperature

Junction Temperature: Tj [°C] Figure 17. UVLO Hysteresis Voltage vs Junction Temperature

Figure 18. V<sub>BB</sub> Overvoltage Protection vs Junction Temperature

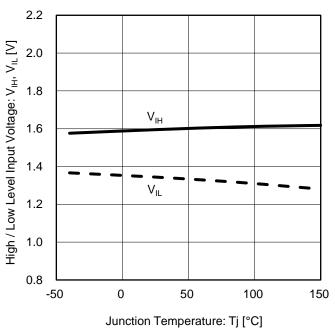

Figure 19. High / Low Level Input Voltage vs Junction Temperature

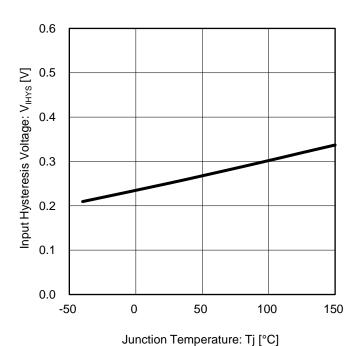

Figure 20. Input Hysteresis Voltage vs Junction Temperature

Junction Temperature: Tj [°C]

Figure 21. High / Low Level Input Current vs

Junction Temperature

(Unless otherwise specified V<sub>BB</sub> = 14 V, Tj = 25 °C)

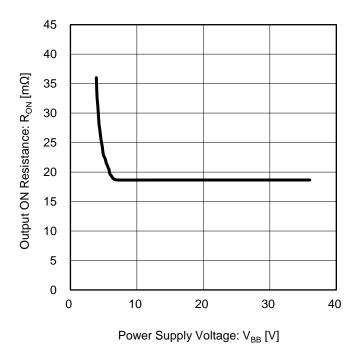

Figure 22. Output ON Resistance vs Power Supply Voltage

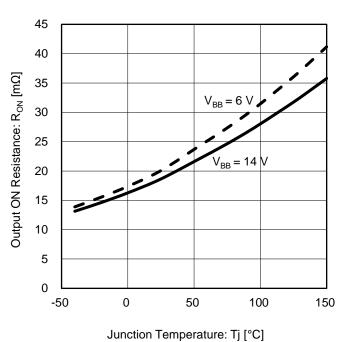

Figure 23. Output ON Resistance vs Junction Temperature

Figure 24. Output Leakage Current vs Junction Temperature

Figure 25. V<sub>DS</sub> Voltage at Light Load vs Junction Temperature

Junction Temperature: Tj [°C]

(Unless otherwise specified V<sub>BB</sub> = 14 V, Tj = 25 °C)

Figure 26. Output Slew Rate vs Junction Temperature

Junction Temperature: Tj [°C]

Figure 27. Output Propagation Time Delay when Turning

ON / OFF vs Junction Temperature

Figure 28. Body Diode Voltage vs Junction Temperature

Figure 29. V<sub>DS</sub> Active Clamping Voltage vs Junction Temperature

Junction Temperature: Tj [°C]

Figure 30. Overcurrent Detection Value vs Junction Temperature

Figure 31. Output Pull Up Current vs Junction Temperature

Junction Temperature: Tj [°C]

Figure 32. Open Load at OFF V<sub>DS</sub> Threshold vs

Junction Temperature

Junction Temperature: Tj [°C] Figure 33. SENSE Leakage Current vs Junction Temperature

Figure 34. Diagnostic Error Flag Current vs Junction Temperature

Figure 35. Diagnostic Error Flag Voltage vs Power Supply Voltage

Figure 36. Diagnostic Error Flag Voltage vs Junction Temperature

Figure 37. SENSE Output Delay Time when the Device Turns ON vs Junction Temperature

(Unless otherwise specified V<sub>BB</sub> = 14 V, Tj = 25 °C)

Figure 38. SENSE Output Delay Time when Diagnostic Turns ON / OFF vs Junction Temperature

Junction Temperature: Tj [°C]

Figure 39. SENSE Settling Time during Load Current Switching vs Junction Temperature

Figure 40. SENSE Settling Time during Load Current Switching vs Junction Temperature

Figure 41. Open Load at OFF Detection Mask Time vs Junction Temperature

Junction Temperature: Tj [°C]

Figure 42. Diagnostic Error Flag Release Delay Time vs Junction Temperature

Figure 43. Output Load Open Detection ON vs Junction Temperature

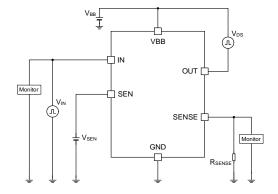

# **Measurement Circuit Diagram**

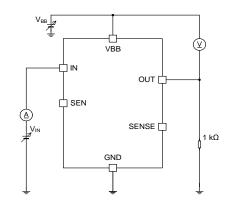

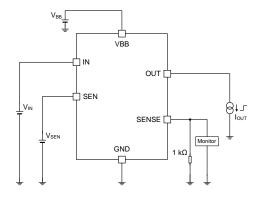

Figure 44. Sleep Mode Current OUT Leakage Current SENSE Leakage Current

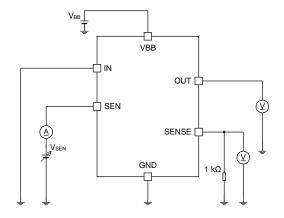

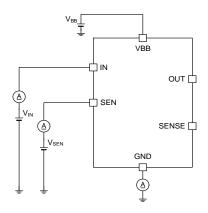

Figure 46. UVLO Threshold / Hysteresis Voltage High / Low Level Input Voltage (IN) Input Hysteresis Voltage (IN) High / Low Level Input Current (IN)

Figure 48. High / Low Level Input Voltage (SEN) Input Hysteresis Voltage (SEN) High / Low Level Input Current (SEN)

Figure 45. Standby Mode Current Operating Mode Current

Figure 47. V<sub>BB</sub> Overvoltage Protection

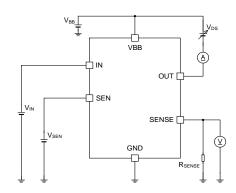

Figure 49. Output ON Resistance V<sub>DS</sub> Voltage at Light Load Body Diode Voltage V<sub>DS</sub> Active Clamping Voltage

# Measurement Circuit Diagram - continued

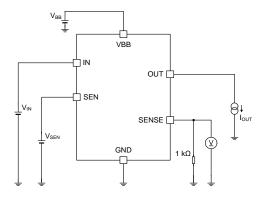

Figure 50. Output Slew Rate when ON / OFF

Output Propagation Delay Time when

Turning ON / OFF

SENSE Output Delay Time when the

Device Turns ON

SENSE Output Delay Time when

Diagnostic Turns ON / OFF

Figure 51. Open Load at OFF V<sub>DS</sub> Threshold Output Pull Up Current Diagnostic Error Flag Voltage

Figure 52. SENSE Leak Current

Diagnostic Error Flag Current

Figure 53. SENSE Settling Time During Load Current Switching

Figure 54. Open Load at OFF Detection Mask Time Diagnostic Error Flag Release Delay Time

Figure 55. Current Sense Ratio

# **Block Diagram**

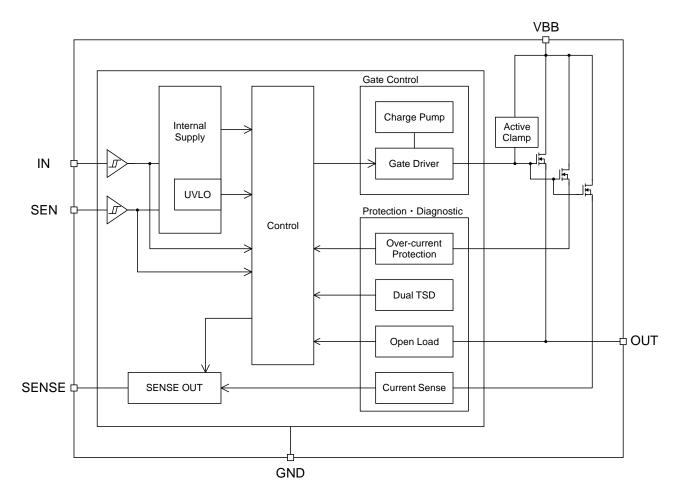

Figure 56. Block Diagram

### **Features Description**

### **Input Pins**

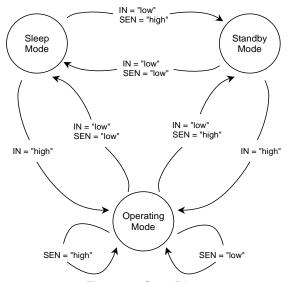

The input circuitry is compatible with 3.3 V and 5 V microcontrollers. The IN and SEN pins must be connected to the microcontroller via 4.7 k $\Omega$  resistors. In case not used, the pins shall be connected to ground via resistors; 4.7 k $\Omega$  or more is recommended

The input circuitry reacts to voltage thresholds and avoids undefined states by use of internal hysteresis. Setting the IN pin voltage above 2.1 V the High Side Power Switch output turns on. The device is in Operating mode. Setting the SEN pin voltage above 2.1 V the diagnostic functions are activated. Setting the IN pin voltage below 0.9 V the output is turned off. Setting the SEN pin voltage below 0.9 V the diagnostic functions are deactivated.

With IN and SEN input pins "low" the device enters Sleep mode; all internal circuits are switched off to prevent current consumption from the power supply, output is turned off and no protection is active. In case the IN pin is de-asserted i.e., IN is "low" and the SEN pin is kept "high" then the device enters in a Standby mode with diagnostic functions activated. In this scenario the current consumption is reduced, but not stopped.

In case the connection is interrupted, the input pins are pulled down internally; only in case all input pins are low the Sleep mode is activated. The internal pull-down is implemented with a resistance. Furthermore, internal de-bounce filters make sure the circuits are not activated or deactivated by high frequency noise or other voltage spikes at the pins.

Figure 57. State Diagram

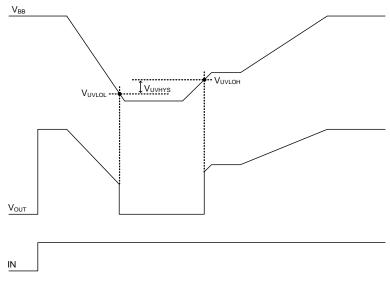

# Internal Supply and Under Voltage Lock Out (UVLO)

The Power Supply Line Input  $V_{BB}$  is used to energize and supply internal circuitry and generate internal volage references. The Intelligent High Side Power Device is designed to operate down to very low battery cranking voltages. However, as with any battery powered device it still needs a certain minimum voltage to operate. An under voltage protection circuit with hysteresis makes sure the device does nothing until the supply voltage is high enough and a predictable behavior can be maintained. The UVLO circuit prevents an undefined output state and/or unintended diagnostic functions turn on when the  $V_{BB}$  voltage is below the specified threshold.

Figure 58. UVLO Functionality

### **Control Circuitry**

The device integrates logic circuits that control the operation of the Intelligent High Side Power Switch. Based on the state of the protection circuits and given inputs the control logic performs state transitions and produces outputs as such.

### **Gate Control Circuitry**

The device integrates a gate driving circuit that acts as interface between the control logic and the N-channel power transistor. A charge pump acts as internal supply allowing to turn on the MOSFET and drive it in the deep triode operation region. The integrated charge pump operates at a fixed frequency improving the EMI performance of the IC. Moreover, the switching behavior of the power transistor is regulated via the gate-driver hence the on and off switching times and slew rates are current-controlled to further improve the EMC.

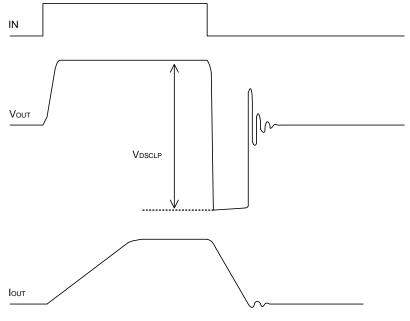

Figure 59. Switching Resistive Loads

# **Active Clamp Protection**

An intelligent integrated active clamp protection limits the maximum  $V_{DS}$  across the power transistor when switching inductive loads at the output pin and the inductive energy is dissipated internally. Moreover, a VBB to GND internal clamp circuit protects the internal circuits from overvoltage surges.

Figure 60. Switching Inductive Loads

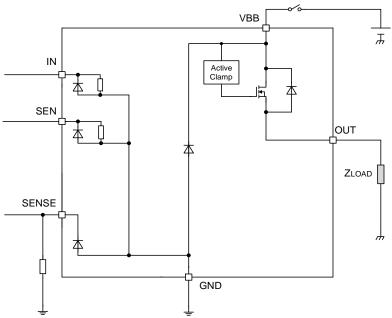

### **Loss of Ground Protection**

When the module's ground becomes open, the outputs switch off. However, it is recommended to add resistors connected between the input pins and the microcontroller. Furthermore, it is recommended to keep all the digital inputs pulled either all high or all low to avoid creating parasitic ground paths that could prevent the outputs from switching off. If the GND pin is open when an inductive load is driven, the active clamp protection safeguards the IC.

Figure 61. Loss of Ground Protection Diagram

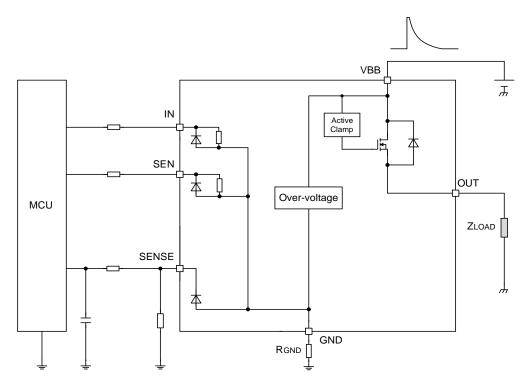

# **Load Dump and Overvoltage Protection**

The integrated VBB to GND overvoltage protection will safeguard the internal circuits from overvoltage transients. In order for the overvoltage protection to work a ground resistance  $R_{GND}$  is necessary. However, a ground shift needs to be considered versus the microcontroller ground when looking at the input voltage threshold levels while in normal operation. Furthermore, the active clamp protection limits the maximum  $V_{DS}$  across the power transistor. Moreover, in case the  $V_{BB}$  voltage exceeds the  $V_{BBCLP}$  level the input pins can start to conduct as well, hence input resistors are mandatory as per the above explanations.

Figure 62. Load Dump Protection Diagram

# **Loss of Battery Protection**

When the connection to the battery becomes open the device can dissipate the energy of the wire harness for inductivities up to 10 µH without degrading its robustness. The integrated VBB to GND overvoltage protection will act as a freewheeling path and the active clamp at the output will close the path for the current to flow safeguarding the IC. In applications where the nominal load currents are exceeded, and more load inductivity is expected, an external load freewheeling diode is necessary and/or a transient voltage suppressor must be present on the battery line.

Figure 63. Loss of Battery Diagram

# **Reverse Battery Protection**

Figure 64. Reverse Battery Diagram

To limit the current through the input pins and the SENSE pin in case of reverse battery connection and negative or positive ISO transients on the battery line, the device's interface pins must be protected with resistors connected between the micro controller and the IC. Furthermore, a ground protection Schottky diode D<sub>GND</sub> is recommended to help improve the robustness of the IC in such scenarios.

A ground resistor at the IC GND pin will protect the IC in reverse battery and in case of negative or positive ISO transients on the battery line. Moreover, the ground resistor safeguards the IC during load dump or over voltage. However, a ground shift needs to be considered versus the micro controller ground when looking at the input voltage threshold levels due to the chip's current consumption in normal operation. Resistor power dissipation needs to be considered during reverse battery conditions.

A diode at the IC GND pin will increase the protection level in both reverse battery and negative ISO pulse transients, however it will reduce the positive ISO pulse robustness of the IC and it will diminish the load dump and over voltage protection ability of the IC. Furthermore, it will lessen the loss of battery protection in case of wire harness inductivity; a parallel resistor to the diode is recommended in this case. If a diode is used the load dump, over voltage and loss of battery scenarios need careful examination and external transient voltage suppressors or/and load freewheeling diodes need to be considered. Moreover, a ground shift will be present versus the microcontroller ground. However, the diode could be shared between multiple devices.

During reverse battery the device allows the load current to flow through the body diode of the power MOSFET; the current must be limited by the resistance of the load. However, in case the load is inductive, special care must be taken to ensure safe operation. A reverse polarity diode on the battery line would be a possible solution.

A compromise between the above options must be found depending on the specific application requirements and the targeted loads.

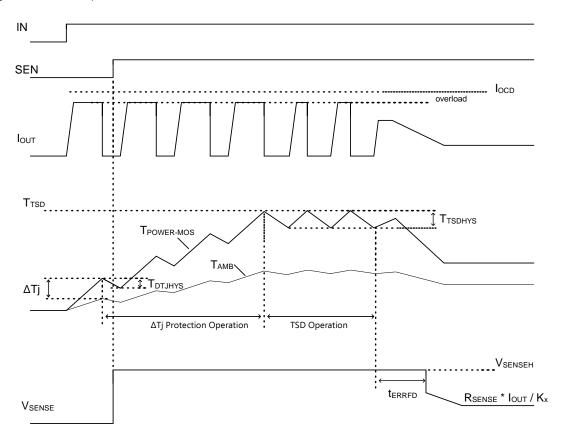

### **Dual Temperature Shutdown Protection**

A dual temperature shutdown (Dual TSD) mechanism limits the internal thermal transients and reduces the mechanical stress of the IC increasing its cyclic short-circuit robustness. The device integrates an absolute and dynamic overtemperature protection circuit. When the chip's junction temperature rises above either the  $T_{DTj}$  or the  $T_{TSD}$  threshold, the output turns off. A thermal hysteresis restart mechanism is implemented. When the chip's temperature falls below a predefined threshold, the output automatically restarts, and operation is resumed accordingly. Moreover, the TSD circuits safeguard the IC in case of overload operation (high inrush current) with the output current below the  $I_{OCD}$  thresholds i.e., before the overcurrent protection activates. When the TSD protection is triggered, the SENSE pin acts as an error flag and signals the fault to the microcontroller. The voltage at the SENSE pin is forced to be  $V_{SENSEH}$ .

Figure 65. Overtemperature Protection

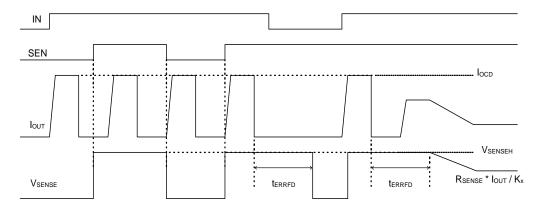

### **Over Current Protection**

The IC has a built-in overcurrent protection feature. If an excessive current flows at the output of the High Side Power Switch, a current limitation aims to protect the IC and peripheral components. Given that a fault is present (short-circuit to ground), or high inrush current at start-up occurs, then the output current is limited to safe operating levels. Moreover, the output current limit is designed to have VBB voltage dependency in favor of an increased robustness of the device. When the load current is above the locd threshold the SENSE pin acts as an error flag and signals the fault to the microcontroller. The voltage at the SENSE pin is forced to be VSENSEH. Furthermore, the overtemperature - dual temperature shutdown (TSD) protection - circuits complement the overcurrent protection. In case the overtemperature protection is triggered during current limitation the power MOSFET is turned off, hence the output current will toggle accordingly - a restart happens when the chip has cooled down sufficiently.

Figure 66. Overcurrent Protection

### **Reverse Current Protection**

The IC allows reverse current to flow through the power MOSFET when the  $V_{\text{OUT}}$  voltage level is higher than  $V_{\text{BB}}$ . Furthermore, as long as the current is maintained within the nominal range and the package's thermal limitations are not exceeded the IC can maintain its operating state or can switch from off to on and vice versa.

# **Diagnostic / SENSE Functions**

Diagnosis / SENSE Output(Note 1)

| IN   | SEN                                                             | SENSE                                                                                                                                                                                                                                                                                | OUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low  | High                                                            | Hi-Z                                                                                                                                                                                                                                                                                 | Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Low  | High                                                            | Hi-Z                                                                                                                                                                                                                                                                                 | < V <sub>BB</sub> - V <sub>DSOL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Low  | High                                                            | Vsenseh                                                                                                                                                                                                                                                                              | ≥ V <sub>BB</sub> - V <sub>DSOL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Low  | High                                                            | V <sub>SENSEH</sub>                                                                                                                                                                                                                                                                  | High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Low  | High                                                            | Hi-Z                                                                                                                                                                                                                                                                                 | Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Low  | High                                                            | Hi-Z                                                                                                                                                                                                                                                                                 | Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Low  | High                                                            | Vsenseh                                                                                                                                                                                                                                                                              | High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| High | High                                                            | I <sub>OUT</sub> / K <sub>x</sub>                                                                                                                                                                                                                                                    | High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| High | High                                                            | I <sub>OUT_ONOLD</sub> / K <sub>x</sub>                                                                                                                                                                                                                                              | High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| High | High                                                            | < I <sub>OUT</sub> / K <sub>x</sub>                                                                                                                                                                                                                                                  | High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| High | High                                                            | Vsenseh                                                                                                                                                                                                                                                                              | Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| High | High                                                            | V <sub>SENSEH</sub>                                                                                                                                                                                                                                                                  | Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| High | High                                                            | Hi-Z                                                                                                                                                                                                                                                                                 | High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| -    | Low                                                             | Hi-Z                                                                                                                                                                                                                                                                                 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | Low Low Low Low Low Low High High High High High High High High | Low High  High  High High  High High  High High  High High  High High  High High  High High  High High  High High  High High  High High  High High  Low High  High High  High High  High High  High High  High High  Low | Low         High         Hi-Z           Low         High         Hi-Z           Low         High         Vsenseh           Low         High         Hi-Z           Low         High         Hi-Z           Low         High         Vsenseh           High         High         Iout / Kx           High         High         Iout / Kx           High         High         Vsenseh           High         High         Vsenseh           High         High         Vsenseh           High         High         Hi-Z |

(Note 1) All values in the above table are Typ values and SENSE is considered Hi-Z looking into the pin i.e., R<sub>SENSE</sub> is ignored.

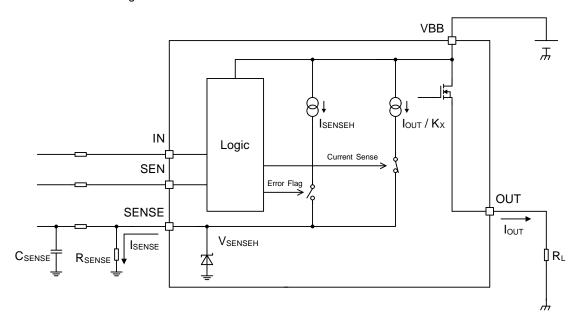

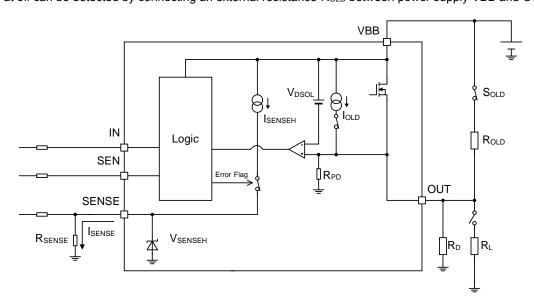

The current sense and diagnostic functions are enabled by setting the voltage  $V_{\text{SEN}}$  = High. The operation is as per the above table. However, an external resistor  $R_{\text{SENSE}}$  must be connected between SENSE and GND pins. The simplified implementation is described in the below diagram.

Figure 67. Diagnostic Output Block Diagram

### **Current Sense**

When the diagnostic is enabled, and the high side power switch is turned on, a current proportional to the load current is flowing through the SENSE pin. The current  $I_{SENSE}$  becomes equal to  $I_{OUT}$  /  $K_x$ , ( $K_x$ : Current sense ratio). An external resistor  $R_{SENSE}$  is recommended, hence for example the voltage at the SENSE pin is equal to:

$$V_{SENSE} = \frac{R_{SENSE} \times I_{OUT}}{K_X}$$

### **Current Sense Ratio Accuracy**

The below diagram shows the load current sense ration dependency vs. the output current through the power MOSFET. The accuracy of the current sense ratio depends on the load current, technological process, voltage and temperature. A higher-precision current sense ratio could be obtained with additional calibration on the application side. The device allows derating at a specific point ( $\Delta K_x$ , Tj = 25 °C). Moreover, to reduce signal ripple at the microcontroller side, it is recommended to insert an external RC filter between the SENSE pin and the ADC input pin.

Figure 68. Current Sense Ratio vs Output Load Current

Furthermore, an open load at ON condition can be recognized via the sense ratio if the load current falls below a certain threshold. This is given by the IOUT\_ONOLD parameter.

# **Open Load Detection**

Open load at off can be detected by connecting an external resistance Rold between power supply VBB and OUT.

Figure 69. Open Load Detection Block Diagram

When the output load is disconnected, input pin IN is low and SEN is high, and open load will be flagged at the SENSE pin by the  $V_{\text{SENSEH}}$  voltage if the load is missing or the output is shorted to the VBB battery line. To reduce the standby current of the system, an open load switch  $S_{\text{OLD}}$  is recommended.  $R_{\text{D}}$  represents the minimum parasitic resistance at the output pin. In case  $R_{\text{D}}$  is not considered the device integrates a 500 k $\Omega$   $R_{\text{PD}}$  resistance.

The value of external resistance  $R_{\text{OLD}}$  is decided based on the minimum power supply voltage (V<sub>BB</sub>), parasitic resistance R<sub>PD</sub> and open detection threshold V<sub>DSOL</sub>. The equation for calculating the R<sub>OLD</sub> value is shown below.

$$R_{OLD} < \frac{R_D \times R_{PD}}{R_D + R_{PD}} \times \left( \frac{V_{DSOL}}{V_{BB(min)} - V_{DSOL}} \right)$$

Moreover, in case a high ohmic open load can be considered, an integrated 100 μA I<sub>OLD</sub> pull up current could help detect an open load at off without the need for any external components.

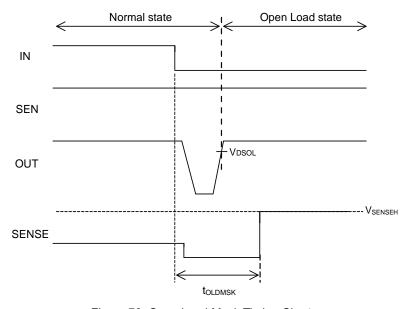

# **Open Load Masking Time**

The IC diagnoses open load detection after the mask tine t<sub>OLDMSK</sub> after the IN pin is de-asserted to allow for the output voltage to drop while in normal operation (load connected).

Figure 70. Open Load Mask Timing Chart

# **Diagnostic Timings**

Figure 71. Diagnostics Timing Diagram

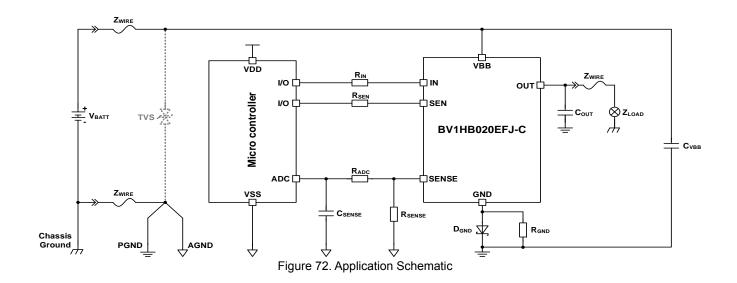

# **Application Circuit Example**

# **Recommended External Components Example**

| Item                                                            | Syr                | nbol                    | Standard Value | Unit |

|-----------------------------------------------------------------|--------------------|-------------------------|----------------|------|

| Input Pin Resistance                                            | R                  | Rin                     | 4.7            | kΩ   |

| Diagnostic Input Pin Resistance                                 | R                  | SEN                     | 4.7            | kΩ   |

| Microcontroller SENSE Pin Resistance                            | R                  | ADC                     | 4.7            | kΩ   |

| SENSE Pin Resistance                                            | Rsi                | ENSE                    | 1              | kΩ   |

| SENSE Filter Capacitance                                        | C <sub>SENSE</sub> |                         | 100            | pF   |

| Output EMC Capacitance                                          | Co                 | OUT                     | 10             | nF   |

| Battery Line Filter Capacitance                                 | C                  | VBB                     | 100            | nF   |

|                                                                 | Ro                 | GND                     | 1              | kΩ   |

| Chip Ground Protection Impedance<br>Network <sup>(Note 1)</sup> | Б                  | V <sub>F</sub> (Note 2) | 0.3            | V    |

|                                                                 | D <sub>GND</sub>   | V <sub>R</sub>          | 40             | V    |

| Transient Voltage Suppressor Diode                              | T                  | VS                      | 36             | V    |

<sup>(</sup>Note 1) R<sub>GND</sub> in parallel with the Ground protection diode is optional. R<sub>GND</sub> is needed in case of loss of V<sub>BB</sub> with wire harness inductivity or inductive load. V<sub>F</sub> of D<sub>GND</sub> is forward bias voltage, V<sub>R</sub> of D<sub>GND</sub> is reverse bias voltage.

(Note 2) V<sub>F</sub> depends on forward current of D<sub>GND</sub>. When decide forward current value, please refer to Operating Mode Current (I<sub>GNDH</sub>) of the "Electrical Characteristics" section.

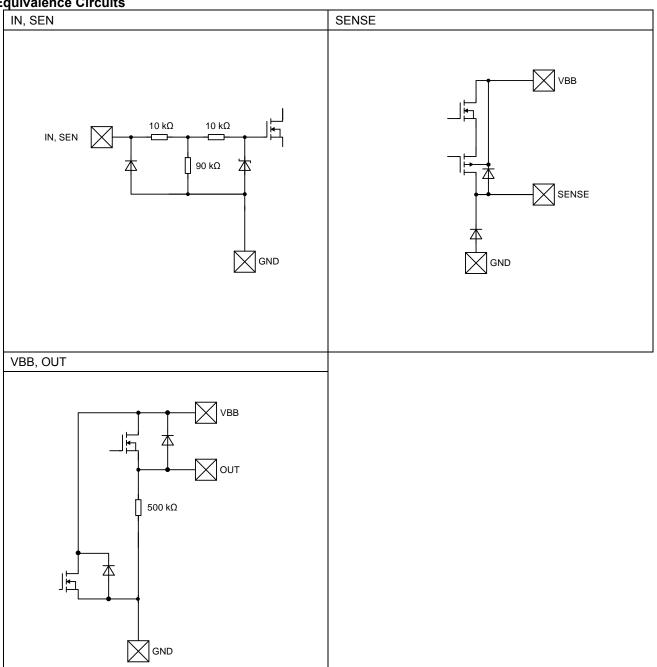

I/O Equivalence Circuits

### **Operational Notes**

### 1. Recommended Operating Conditions

The IC is designed to operate in 12 V automotive boar net applications. The functions and operation of the IC are guaranteed within the range specified by the recommended operating conditions. The characteristic values are guaranteed only under the conditions specified by the electrical characteristics. The IC can withstand transient voltages beyond the recommended operating conditions; however, parameter deviations are possible when used outside of the supply nominal voltage range. Exposure to the absolute maximum ratings may cause permanent damage to the IC.

### 2 Inrush Current

When a load is being activated by the IC inrush currents may flow. The IC is designed to drive high inrush current loads; however, careful consideration must be completed when pairing the IC with the load. In case special recommendations are not available in the Datasheet the minimum overcurrent protection level of the IC should be higher than the maximum expected inrush current for proper load driving.

### 3. Testing on Application Boards

When testing the IC on an application board, it is recommended to always discharge capacitors completely after each evaluation step. The IC's power supply should always be turned off completely before connecting or removing it from the test setup during the inspection process. To prevent damage from static discharge, ground the IC during assembly and use similar precautions during transport and storage.

### 4. Inter-pin Short and Mounting Errors

Ensure that the direction and position are correct when mounting the IC on the PCB. Incorrect mounting may result in damaging the IC. Avoid nearby pins being shorted to each other especially to ground, power supply and output pin. Inter-pin shorts could be due to many reasons such as metal particles, water droplets (in very humid environment) and unintentional solder bridge deposited in between pins during assembly to name a few.

## 5. Ceramic Capacitor

When using a ceramic capacitor, determine a capacitance value considering the change of capacitance with temperature and the decrease in nominal capacitance due to DC bias and others.

### 6. Thermal Shutdown Function (TSD)

This IC has a built-in thermal shutdown function that prevents heat damage to the IC. Normal operation should always be within the IC's maximum junction temperature rating. If however the rating is exceeded for a continued period, the junction temperature (Tj) will rise which will activate the TSD function that will turn OFF power output pins. When the Tj falls below the TSD threshold, the circuits are automatically restored to normal operation.

Note that the TSD function operates in a situation that exceeds the absolute maximum ratings and therefore, under no circumstances, should the TSD function be used in a set design or for any purpose other than protecting the IC from heat damage.

# 7. Over Current Protection Function (OCP)

This IC integrates an overcurrent limitation protection function that is activated when the load is shorted towards ground. This protection function is effective in preventing damage due to sudden and unexpected fault events. However, the IC should not be used in applications characterized by continuous operation of the protection function.

### 8. Active Clamp Operation

The IC integrates the active clamp function to internally absorb the reverse energy  $E_L$  which is generated when the inductive load is turned off. When the active clamp operates, the thermal shutdown function does not work. Decide a load so that the reverse energy  $E_L$  is active clamp energy (Single Pulse)  $E_{AS}$  (refer to Figure 4. Active Clamp Energy vs Output Current) or under when inductive load is used.

### 9. Reverse Battery Connection

Connecting the power supply i.e., the battery with a reversed polarity can damage the IC. Precautions must be taken against reverse polarity when connecting the power supply, such as mounting an external diode between the battery feed and the IC's power supply, blocking all current paths. Alternatively, inserting a blocking diode or resistance in series with the IC's GND pin will prevent or limit the current from flowing into the control circuits of the high side switch respectively. However, current thorough the body diode of the integrated power FET must be limited by the resistive component of the load. The current through the Digital inputs and SENSE pins must be limited too with protection resistors.

# 10. Power Supply and PCB Layout