第4世代 SiC MOSFET ディスクリートパッケージ 諸特性と回路設計の注意点 アプリケーションノート Rev.001

#### 【ご注意】

このアプリケーションノートに記載されている評価データ等は、 ロームにおける同一条件下で評価した結果をご参考として示したものです。 この中で示された特性を弊社が保証するものではありません。

# 第4世代 SiC MOSFET ディスクリートパッケージ 諸特性と回路設計の注意点 Application Note

# 目次

| 1. | はじめに                                       | 3  |

|----|--------------------------------------------|----|

|    | 1.1本アプリケーションノートについて                        | 3  |

|    | 1.2第 4 世代 SiC MOSFET の開発目標                 | 3  |

| 2. | 第 4 世代 SiC MOSFET の諸特性                     | 4  |

|    | 2.1 規格化オン抵抗(RonA)                          | 4  |

|    | 2.2 <i>V<sub>DS</sub>-I<sub>D</sub></i> 特性 | 5  |

|    | 2.3 ゲート駆動電圧とオン抵抗                           | 6  |

|    | 2.4 オン抵抗の温度係数                              | 7  |

|    | 2.5 V <sub>GS</sub> -I <sub>D</sub> 特性     | 7  |

|    | 2.6 ターンオン/ターンオフ 特性                         | 8  |

|    | 2.7 容量特性                                   | 10 |

|    | 2.8 内部ゲート抵抗                                | 11 |

|    | 2.9 スイッチング特性の温度依存性                         | 12 |

|    | 2.10 ボディダイオードのリカバリ特性                       | 12 |

|    | 2.11 スイッチング損失のゲート電圧依存性                     | 13 |

|    | 2.12 短絡耐量                                  | 14 |

| 3. | ゲートドライブ                                    | 15 |

|    | 3.1 SiC MOSFET 用ゲートドライバ IC                 | 15 |

|    | 3.2 推奨ゲート電圧(V <sub>G(ON)</sub> )           | 16 |

|    | 3.3 外付けゲート抵抗(R <sub>G_EXT</sub> )の選定       | 18 |

|    | 3.4 デッドタイム(t <sub>DT</sub> )設計             | 22 |

|    | 3.5 セルフターンオン対策                             | 23 |

|    | 3.6 負サージ対策                                 | 24 |

|    | 3.7 推奨レイアウト                                | 25 |

| 4. | 第 4 世代 SiC MOSFET の信頼性                     | 27 |

| 5. | ディスクリート用評価基板                               | 28 |

|    | 5.1 第4世代 SiC MOSFET ディスクリート用評価基板           | 28 |

| 6. | 第 4 世代 SiC MOSFET ラインナップ                   | 32 |

| 7. | まとめ                                        | 33 |

#### 1. はじめに

### 1.1 本アプリケーションノートについて

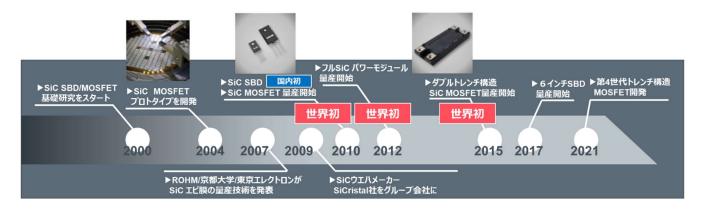

近年、SiC MOSFET はパワーエレクトロニクス分野において急速に普及が進んでおり、高耐圧かつ高速スイッチングのメリットを活かして、その適用範囲が飛躍的に拡大しております。ロームは 2010 年に世界で初めて SiC MOSFET の量産化(プレーナ構造)に成功し、2015 年にトレンチ構造採用による大幅な微細化(第3世代)の達成など、SiC のリーディングカンパニーとして技術革新を続けてきました。この度、ローム独自のトレンチ構造をさらに進化させた「第4世代」SiC MOSFET を量産するに至りました(Figure 1-1)。

本アプリケーションノートでは、第4世代 SiC MOSFET の特長について説明し、その性能を最大限に引き出すための使い方を詳しく解説します。なお、旧世代品の詳細情報については「SiC パワーデバイス・モジュール アプリケーションノート Rev.003」(\*1)にまとめております。本アプリケーションノート以外にも、SiC MOSFET を使いこなす上で役立つ技術資料を多数ご用意しております。 (\*1~\*21) また、ROHM ホームページ上では第4世代 SiC MOSFET に対応した Web シミュレーションツール「ROHM Solution Simulator」を公開しております。 こちらも併せてぜひご活用ください。

Figure 1-1. ROHM SiC MOSFET 開発の歴史

#### 1.2 第4世代 SiC MOSFET の開発目標

第4世代 SiC MOSFET の開発に当たり、注力したのは以下の3点になります。

- 低損失:業界トップクラスの規格化オン抵抗(RonA)と高速スイッチングの実現

- 使い易さの向上:ゲート駆動電圧(15V~18V)と負バイアスレスの実現

- 高信頼性:高短絡耐量の実現

まず「低損失」については、MOSFET のセル微細化などにより重要指標の一つである「規格化オン抵抗:RonA」を第3世代品と比較して40%低減したことや、デバイス構造の最適化による寄生容量の削減により、導通損失・スイッチング損失を従来品と比べ大幅に低減しました。

次に「使い易さの向上」については、第 3 世代品の  $V_{G(ON)}$ =18V 駆動に対して、シリコン(Si)MOSFET と同等の  $V_{G(ON)}$ =15V でも駆動できるようになりました。これにより Si-MOSFET から SiC への置き換えが容易になるため、お客さまにおける回路設計の自由度向上に大きく貢献できます。 また、セルフターンオンを抑制するようデバイスの容量特性を最適化や、ゲート閾値電圧を高く設計しておりますので、ターンオフ時の負バイアス設計が不要です。 この点は駆動回路を簡略化するとともに、回路規模を極小化することで、コスト削減にも繋がります。

そして「高信頼性」については、RonA を低減しているにも関わらず第3世代品と同等以上の短絡耐量実力\*を確保しております(一般的にRonA の低減に伴って短絡耐量は低下します)。この点は単位面積当たりの電流密度が大きいSiC MOSFET を安心して使って頂く上で、非常に重要な特長と言えます。 (※保証はしておりませんのでご注意下さい)

以上のように、第4世代品は従来品と比べ、飛躍的に性能・使い易さ・信頼性が向上しておりますので、お客さまの設計課題の解決に貢献することができると考えます。なお、この第4世代品はディスクリート品やモジュール品での提供だけでなく、ウエハやチップ単体での供給も可能ですので、ラインナップ等詳細につきましては、弊社営業窓口までお気軽にお問い合わせ下さい。

次の章から、第4世代 SiC MOSFET の優れたデバイス特性について詳しく解説していきます。

### 2. 第4世代 SiC MOSFET の諸特性

# 2.1 規格化オン抵抗(RonA)

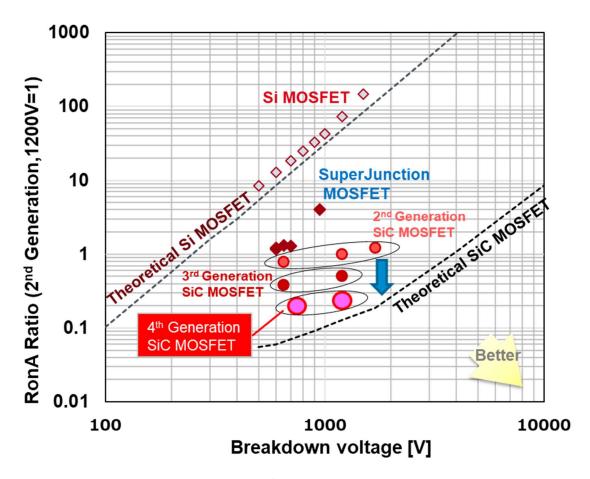

SiC は Si に比べて絶縁破壊電界強度が 10 倍高いことから低い比抵抗、薄い膜厚のドリフト層で高い耐圧を実現できます。このため同じ耐圧 同士で比較すると規格化オン抵抗(RonA: 単位面積当たりオン抵抗)の小さなデバイスが実現可能です。Figure 2-1 に示すとおり、例えばブレイクダウン電圧 650V クラスで比較した場合、SiC MOSFET は Si-MOSFET の約 100 分の 1、スーパージャンクション(Super Junction: SJ) MOSFET の約 10 分の 1 のチップサイズで同じオン抵抗を実現できます。これにより従来よりも小型パッケージかつ低オン抵抗な製品を実現できるほか、ゲート電荷量 Qg や容量なども小さくなりますのでスイッチング特性においても非常に有利になります。

現在、スーパージャンクション MOSFET は一般的に 900V 程度までの製品しか存在していませんが、SiC MOSFET では 1700V 以上の耐圧 についても、低いオン抵抗で実現することができます。これまでは 1700V 以上の耐圧に対応するためには IGBT のようなバイポーラデバイス構造(オン抵抗は低くなる一方スイッチングが遅い)を採用する必要がありましたが、SiC であれば低オン抵抗、高耐圧、高速スイッチングの全てを兼ね備えた優れたデバイスとしてご利用いただけます。

Figure 2-1. 規格化オン抵抗 RonA の比較

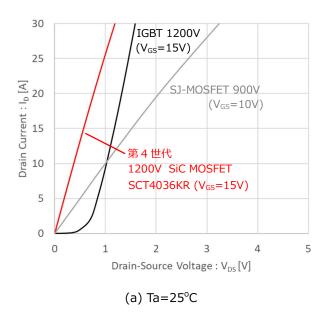

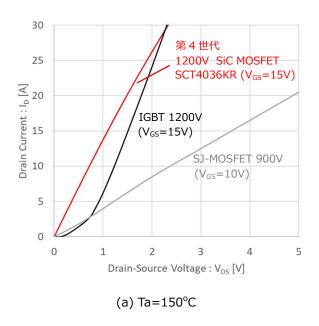

## 2.2 V<sub>DS</sub>-I<sub>D</sub>特性

一般的に MOSFET は飽和領域に達するまでは抵抗性領域のため、ドレイン電流  $I_D$  に比例したドレイン-ソース間電圧  $V_{DS}$  が発生するのに対して、IGBT は PN 接合を有しているため、コレクタ-エミッタ間電圧  $V_{CE}$  が PN 接合電位以上にならないとコレクタ電流 Ic は流れ始めません。そのため、図 2.2 に示します  $V_{DS}(V_{CE})$  -  $I_D(I_C)$  特性からも、 $I_D$  ( $I_C$ ) が小さいほど MOSFET の方が導通損失は小さいことがわかります。また、SiC MOSFET と SJ-MOS を比較すると、オン抵抗が低いだけでなく温度上昇に対するオン抵抗の上昇率が小さいため、高温でもオン抵抗を低く抑えることができます。SiC MOSFET のこの特長は、回路の熱設計を容易にします。Figure 2-2 に常温と高温時における、第 4世代 SiC MOSFET (1200V 36m $\Omega$ : SCT4036KR) と IGBT、SJ-MOSFET の  $V_{DS}$ - $I_D$  特性を示します。

Figure 2-2. 各デバイスの  $V_{DS} - I_D$  特性 (常温および高温)

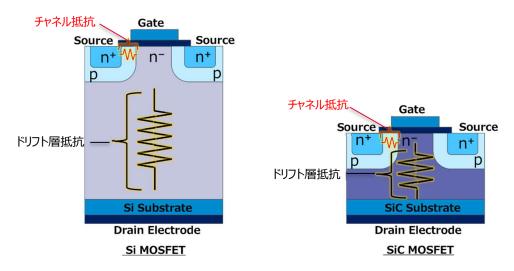

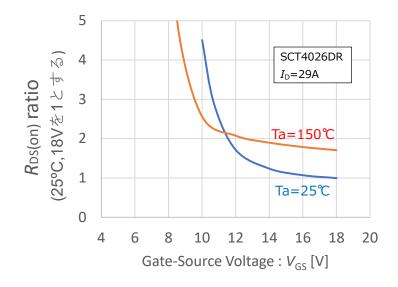

### 2.3 ゲート駆動電圧とオン抵抗

SiC MOSFET はドリフト層抵抗が Si-MOSFET よりも低い一方で、現在の技術レベルでは MOSFET チャネル部のキャリア移動度が低いため、チャネル抵抗が Si-MOSFET と比較して高くなります。このため、ゲート電圧  $V_{GS}$  が高いほどオン抵抗を下げることができます( $V_{GS}$ =18V 以上で徐々に飽和します)。

Figure 2-3(b)に、第 4 世代 SiC MOSFET SCT4026DR の  $V_{GS}$ - $R_{DS(on)}$ 特性を示します。これを見て分かるように、SiC MOSFET は一般的な SJ-MOSFET と異なり、チャネル ON の状態でも  $V_{GS}$ の値によってオン抵抗が大きく変動します。このためオン抵抗を下げて SiC MOSFET の性能を十分に発揮するためには、 $V_{GS}$ の値を上げることが効果的です。

また  $V_{\rm GS}$  が低い場合、動作温度が高いほどオン抵抗が下がる傾向にあります。よって、高温かつ低  $V_{\rm GS}$  で並列接続して使用する場合などは、一つの素子に電流が集中し熱暴走しないよう注意して下さい。

Figure 2-3(a). MOSFET 構造図

Figure 2-3(b). V<sub>GS</sub>-R<sub>DS(on)</sub> 特性

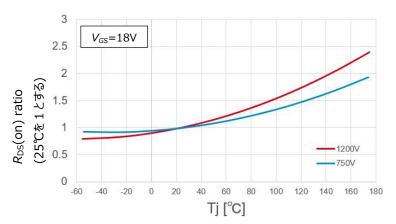

### 2.4 オン抵抗の温度係数

一般的な SJ-MOSFET は高温でオン抵抗が大きく上昇します。これはデバイスのオン抵抗のうち 9 割以上を占めるドリフト層の抵抗成分 (R<sub>EPI</sub>)が 100℃上昇すると約 2 倍に上昇するためです。SiC のドリフト層抵抗も Si と同様の温度依存性を示しますが、デバイス全体のオン抵抗上昇率は一般的な SJ-MOSFET と比べて低いです。これは SiC MOSFET 全体のオン抵抗のうち、ドリフト層抵抗(温度上昇によって抵抗が上昇する部分)の占める割合が小さいためです。

また、他の半導体デバイスと同様に SiC MOSFET においても、耐圧やデバイス設計によってオン抵抗の温度係数は異なります。例えば 750V 品ではドリフト層の抵抗成分が小さいため温度係数は比較的小さいです。しかし 1200V 品ではドリフト層が厚く(抵抗成分が大きく)なるため、750V 品に比べて温度係数が大きくなります。 Figure 2-4 は X 軸にジャンクション温度(Tj)を置き、Y 軸に 25℃時を 1 とするオン抵抗比を置いた、オン抵抗の温度特性を示すグラフです。 Tj 上昇に伴って、温度係数の差から 1200V 品のオン抵抗比が 750V 品よりも大きくなることが分かります。

Figure 2-4. 第4世代 SiC MOSFET 規格化 RDS(on) の温度特性

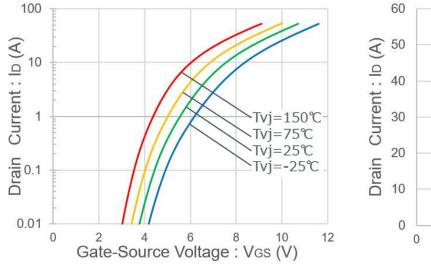

### 2.5 V<sub>GS</sub>-I<sub>D</sub>特性

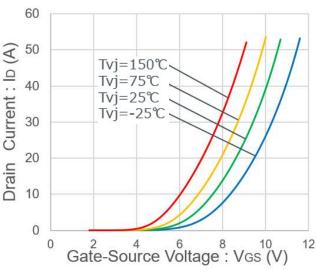

Figure 2-5 に SCT4036KR(1200V 36m $\Omega$ )の  $V_{GS}$ - $I_D$  特性を示します。左右のグラフは同じデータですが、左側は縦軸を Log スケール、右側は Linear スケールで表示しています。これから分かるように第 4 世代 SiC MOSFET の閾値電圧は、 $I_D$ =10mA で見た場合室温で約 4V(ノーマリ・オフ)です。また、5A 以上の電流を流すためには、室温で約 7V 以上のゲート電圧が必要です。一般的に閾値電圧は温度が上昇するほど低下します。

(Tvj: Virtual junction temperature)

Figure 2-5. V<sub>GS</sub>-I<sub>D</sub> 特性 (SCT4036KR)

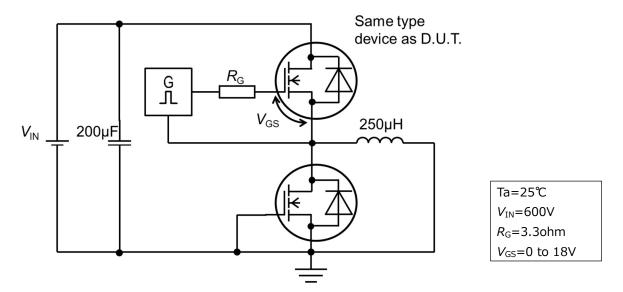

### 2.6 ターンオン/ターンオフ 特性

第4世代 SiC MOSFET SCT4036KR と、同オン抵抗クラスの第3世代品 SCT3040KR をそれぞれ用いてハーフブリッジ回路を構成し、 誘導負荷ダブルパルス試験(DPT)によりスイッチング特性を比較しました。Figure 2-6 にその試験回路を示します。

Figure 2-6. ダブルパルス試験回路

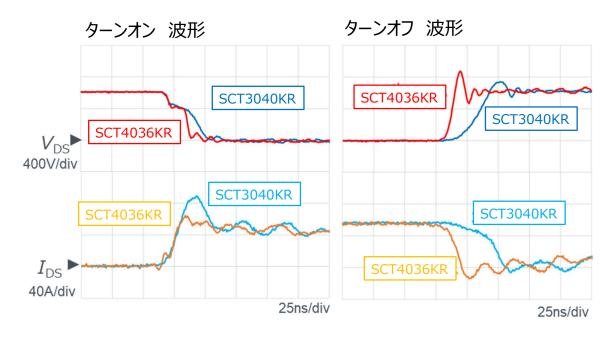

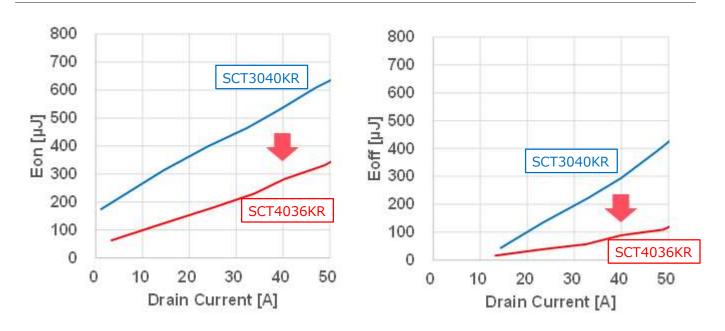

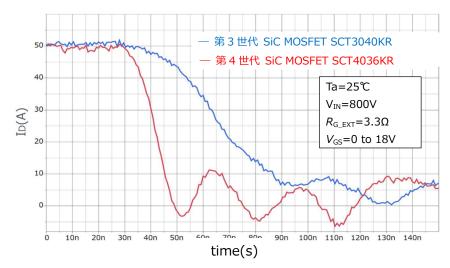

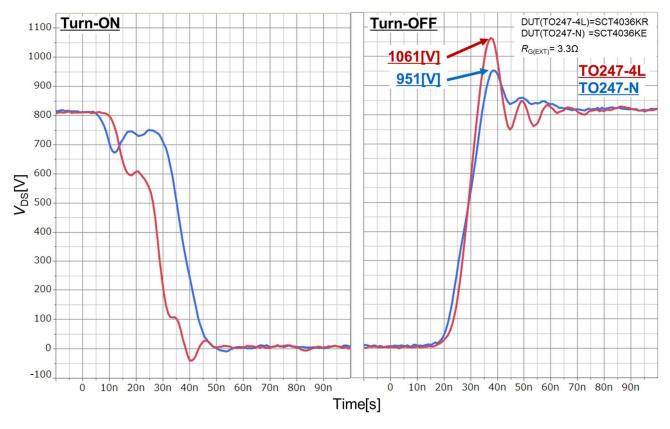

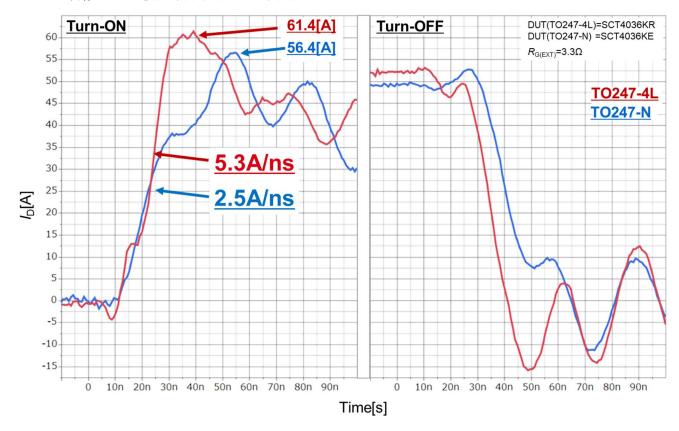

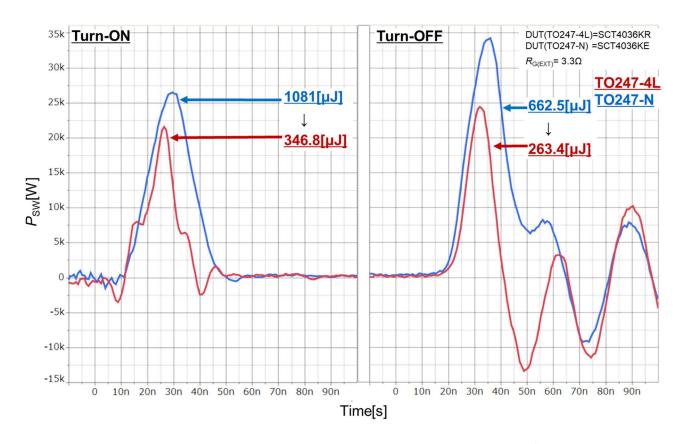

Figure 2-7 と Figure 2-8 に、ダブルパルス試験のスイッチング波形と損失の比較(Low-side 側)を示します。下図より第 4 世代品のスイッチング速度は第 3 世代品よりも高速で、かつスイッチング損失も低減していることが分かります。この結果は第 4 世代品の方が、スイッチング速度に影響を与える内部ゲート抵抗値、および  $C_{oss}$ ・ $C_{rss}$  の各容量値を低減したことに起因します。

なお容量と内部ゲート抵抗については、2-7節および2-8節で詳しく説明します。

Figure 2-7. ターンオン/ターンオフ 波形比較

Figure 2-8. スイッチング損失比較

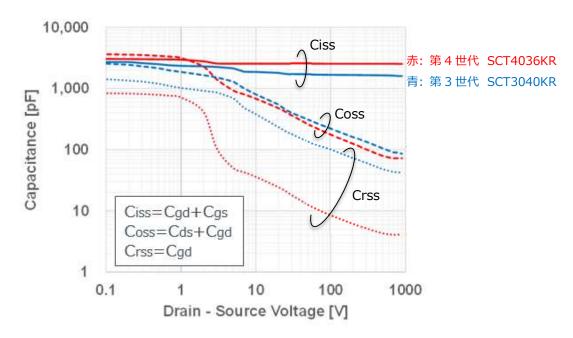

#### 2.7 容量特性

2.1 節で説明した通り、第4世代品は第3世代品と比べて、規格化オン抵抗RonAを大幅に低減しています。これにより、オン抵抗が同等の製品でも、第4世代品の方が素子サイズを小さくすることが可能です。一般的にSiC MOSFET の素子サイズが小さくなれば寄生容量  $C_{\rm rss}$  は小さくなり(Figure 2-9)、その結果 2.6 節で説明した通りスイッチング速度の向上につながります。

Figure 2-9. 第4世代、第3世代 容量比較

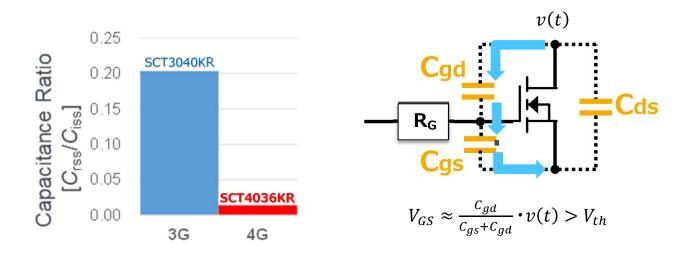

また第 4 世代品は  $C_{oss}$  と  $C_{rss}$  の容量値を単に低減しただけでなく、 $C_{rss}/C_{iss}$  の容量比も大幅に低減(Figure 2-10)することで、高速スイッチング時に問題となるセルフターンオンの発生リスクも低減しています。

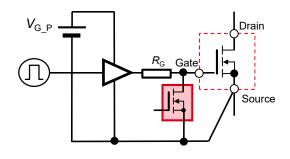

セルフターンオンの概念図を Figure 2-11 に示します。オフ状態における MOSFET のドレイン-ソース間に、スイッチング過程などにおいて急峻な dv/dt が発生すると、寄生容量  $C_{gd}$   $extit{ }$   $extit{ }$

Figure 2-10. Crss/Ciss 容量比の低減

Figure 2-11. セルフターンオン現象

### 2.8 内部ゲート抵抗

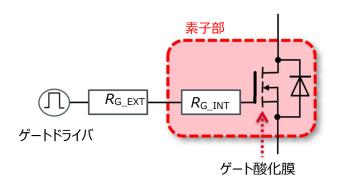

一般的に同一構造の素子同士であれば、素子サイズが小さいほど内部ゲート抵抗は大きくなります。しかし、第4世代品は第3世代品と比べて素子を小型化しているにも関わらず、ウエハプロセスや素子パターンを最適化することにより、この内部ゲート抵抗を大幅に(約1/6に)低減することができました。

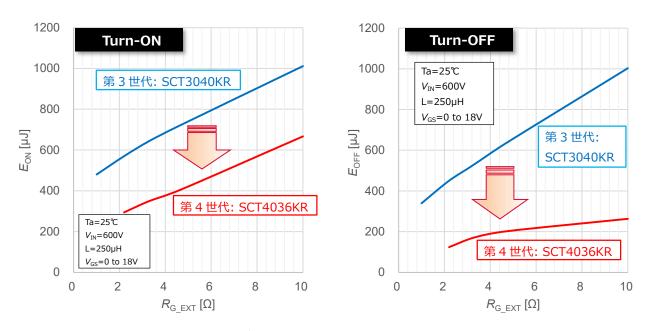

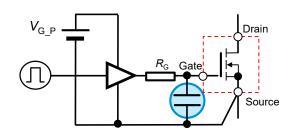

MOSFET のゲートを駆動する場合 Figure2-12 に示すように、ゲートドライバとゲート酸化膜の間には外付けゲート抵抗( $R_{G_EXT}$ : サージなど 調整用)と内部ゲート抵抗( $R_{G_INT}$ : 素子上のゲート配線抵抗などに固有)が直列に入ります。そのため、スイッチング速度は、この  $R_{G_EXT}$ と  $R_{G_INT}$ の「和」が小さいほど速くなりスイッチング損失も小さくなります。

Figure 2-12. 外付けゲート抵抗「RG EXT」と内部ゲート抵抗「RG INT」

続いて Figure 2-13 に、外付けゲート抵抗  $R_{G_EXT}$ を変化させた場合の第 4 世代品と第 3 世代品のスイッチング損失の比較を示します。評価方法は 2.6 節と同様のダブルパルス試験です。これを見ると、同じ  $R_{G_EXT}$ で駆動した場合でも、第 4 世代品の方が大幅にスイッチング損失を低減できることが分かります。これは 2.7 節で説明したように第 4 世代品は、寄生容量と内部ゲート抵抗  $R_{G_EXT}$  が小さく、ゲート抵抗の総和  $(R_{G_EXT})$ も小さくなり、スイッチング速度が上昇したためです。

またスイッチング速度は  $R_{\rm G}$  の総和( $R_{\rm G_LNT}+R_{\rm G_EXT}$ )で決定されるため  $R_{\rm G_LNT}$  が小さくなり、 $R_{\rm G_EXT}$  の調整範囲も広がることで、ゲートサージ の抑制やスイッチング特性の改善などに対して柔軟に対応することができます。この点も第 4 世代品の大きな特長と言えます。

Figure 2-13. スイッチング損失の R<sub>G\_EXT</sub> 依存性比較 (第4世代品 vs. 第3世代品)

### 2.9 スイッチング特性の温度依存性

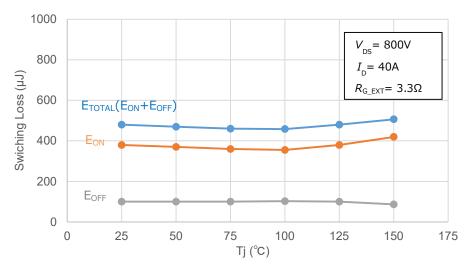

一般的に半導体デバイスのスイッチング速度は寄生容量に大きく依存しますが、SiC MOSFET の寄生容量は温度に対してほとんど変化しないため、スイッチング損失の温度特性も極めて安定しています。Figure 2-14 に第 4 世代 SiC MOSFET SCT4036KR のスイッチング損失の温度依存性を示します。下記グラフからも分かるように、スイッチング損失は温度変化に対してほぼフラットな特性となっています。

Figure 2-14. スイッチング損失の温度依存性 (SCT4036KR)

### 2.10 ボディダイオードのリカバリ特性

Figure 2-15 に第 4 世代品と第 3 世代品におけるボディダイオードのリカバリ特性比較を示します。第 4 世代品は、「2.8 内部ゲート抵抗」の項で述べた通り、第 3 世代品と比較して内部ゲート抵抗を低減したことで、スイッチング速度が速くなっています。一般的には、その背反としてサージ増大によるリカバリ特性の悪化があげられますが、これを見ると、第 4 世代品はスイッチング速度が速くなった上で、リカバリ電流もほとんど流れていないことが分かります。このことは Totem-pole PFC やインバータなど、リカバリ電流が発生する各種ブリッジ回路においてスイッチング損失の大幅な低減に貢献できるとともに、リカバリ電流に起因する故障リスクやノイズ低減にも期待できることを表しています。

Figure 2-15. ボディダイオードのリカバリ特性比較

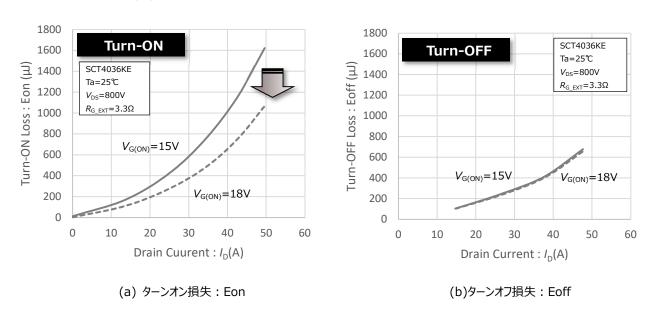

### 2.11 スイッチング損失のゲート電圧依存性

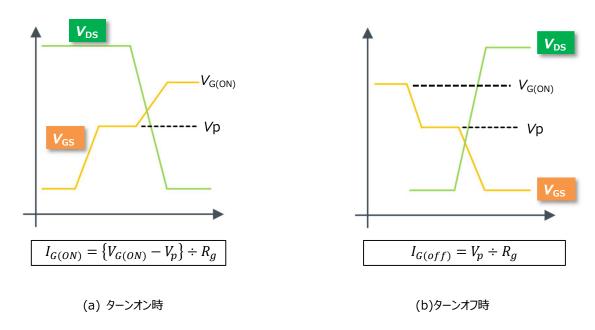

ゲート駆動電圧によるスイッチン損失の違いを Figure 2-16 に示します。ターンオン時スイッチング損失  $E_{ON}$  は駆動電源  $V_{G(ON)}$ が高いほど低減され、18V では 15V に比べ  $I_D$ =50A 時に 1.6 倍程度小さくなります。これは  $V_{G(ON)}$ とプラトー電圧(スイッチング時において、ミラー容量の充放電が始まるゲート電圧値)の電位差が大きいほど、ゲート電流  $I_{G(ON)}$ が大きくなり、 $C_{rss}$  の放電、すなわちドレイン電圧  $V_{DS}$  の下降速度を速めるためです(Figure 2-17(a))。

一方で、ターンオフ時スイッチング損失 Eoff は  $V_{G(ON)}$ による変化はほとんどありません。ターンオフ時はプラトー電圧  $V_P$  とゲートオフ電圧(この場合は OV)の電位差で Crss を充電するゲート電流  $I_{G(off)}$ が決まるため、 $V_{G(ON)}$ の影響を受けません (Figure 2-17(b)参照:この  $I_{G(off)}$ の式から明らかなよう、式中に  $V_{G(ON)}$ が含まれないため)。

Figure 2-16. スイッチング損失の  $V_{G(ON)}$ 依存性

Figure 2-17. ターンオン/オフ時におけるゲート電流  $I_G$

# 2.12 短絡耐量

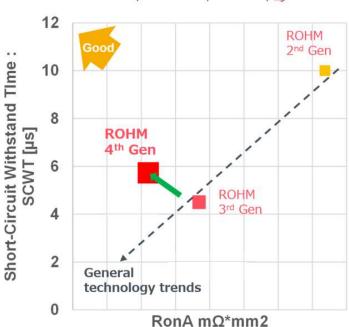

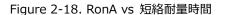

第4世代 SiC MOSFET では独自のデバイス構造を採用することで、本来トレードオフとなる RonA と短絡耐量時間の関係を解消し、低 RonA と高短絡耐量の両立を実現しました(Figure2-18)。一般的に RonA を下げると飽和電流が上昇するため、短絡耐量時間が短くなります。しかし、第4世代 SiC MOSFET は第3世代 SiC MOSFET と比較して、ドレイン・ソース間電流  $I_D$  の飽和電流を下げることで短絡時のピーク電流を抑えています。よって、RonA と短絡耐量時間のトレードオフを解消することができ、短絡耐量時間の確保に成功しています(Figure2-19)。(図で示した短絡耐量については一条件での測定値となります。この数値を保証するものでないことをご留意ください)

VDSS:1200V, Ron:40m $\Omega$ , VIN:800V, Tj=25°C

Figure 2-19 飽和電流比較(第 4 世代 vs 第 3 世代)

### ・3. ゲートドライブ

第4世代 SiC MOSFET の駆動時のスルーレート(dv/dt)は、第3世代 SiC MOSFET と比較しても格段に上昇しています。この特性は、スイッチング損失を減少させ効率改善を望める一方、リンギングやサージの発生を誘発するため、ゲートドライブ回路設計には、より一層の注意と慎重な検討が必要となります。本章ではゲート駆動に関する設計時の注意点や、推奨駆動条件などについて説明します。

### 3.1 SiC MOSFET 用ゲートドライバ IC

SiC MOSFET 用ゲートドライバ IC を選定する上で、特に考慮しなければならないところは次の点です。

- 駆動電圧(最大定格など)

- 駆動能力(出力ピーク電流、スイッチング周波数など)

- 伝播遅延時間(一次-二次間など)

- 保護機能(Miller Clamp、DESAT、OCP、UVLO など)

- 同相過渡電圧耐性(CMTI: Common Mode Transient Immunity)

また、ドライバ IC は備えている機能によって、単機能タイプ(Simple タイプ)と多機能タイプ(Complex タイプ)の大きく二つのカテゴリに分けられます。単機能タイプは、駆動信号によるゲートドライブ機能のみを備え SOP-8 や SSOP-10 などの小型パッケージで製品化されています。一方、多機能タイプは負バイアス対応、各種保護機能や温度モニタ機能、絶縁電源などを備え、SOP-20 以上の大型パッケージで製品化されているものが多くなっています。

必要な機能に応じて多数ラインナップしておりますので、ロームホームページ(<a href="https://www.rohm.co.jp/products/power-management/gate-drivers">https://www.rohm.co.jp/products/power-management/gate-drivers</a>)をご覧になるか、営業担当までご連絡下さい。

# 3.2 推奨ゲート電圧(V<sub>G(on)</sub>)

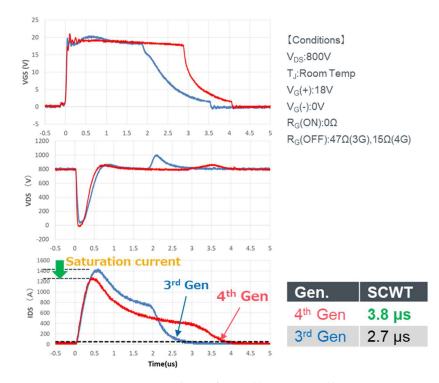

第 4 世代 SiC MOSFET では 18V のみでなく、第 3 世代品では使用できなかった 15V 駆動に対応しており、従来の Si 系デバイスの回路を流用することができます。 また、デバイスは 18V 駆動時に最適化するよう設計されていますが、条件によっては 18V 駆動と同等の効率を実現することができます。 Figure 3-1 は表記の条件で  $V_{G(ON)}$ をそれぞれ 15V,18V に設定した際の効率を比較した結果です。 高負荷時に若干の差が見られますが、ほぼ同等の効率となっています。 そのため、 15V 駆動の Si MOSFET からの置き換えが容易になります。

Figure 3-1. V<sub>G(ON)</sub>電圧違いの効率比較(Buck コンバータ動作時)

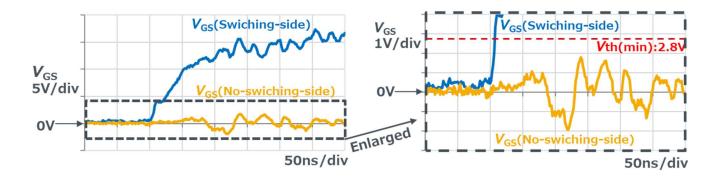

また、第4世代 SiC MOSFET のターンオフ時の推奨駆動電圧は 0V となっております。一般的な MOSFET ではターンオフ時のゲート・ソース電圧を負バイアスまで印加することでセルフターンオンを対策することができ、負バイアス駆動を推奨する製品もあります。ただし、第4世代 SiC MOSFET は閾値電圧( $V_{th}$ )を高く設計しており、セルフターンオンの発生を抑制し、負バイアスの印加を不要としています。(Figure.3-2)

Figure 3-2. スイッチングターンオン時波形

なお、 $\Box$  –  $\Delta$  SiC MOSFET のゲート定格電圧については、世代毎により異なりますので、Table 3-1 に比較表を示します。 SiC MOSFET のゲート定格電圧については、4 章「第 4 世代 SiC MOSFET の信頼性」を参照下さい。

| Parameter                 |          | 3 <sup>rd</sup> Generation<br>SCT3xxxx | 4 <sup>th</sup> Generation<br>SCT4xxxx |

|---------------------------|----------|----------------------------------------|----------------------------------------|

| Gate-Source Voltage       |          | -4 V ~ +22 V                           | -4 V ~ +21 V                           |

| Gate-Source Surge Voltage |          | -4 V ~ +26 V                           | -4 V ~ +23 V                           |

| Recommended               | Positive | +18 V ~ +20 V                          | +15 V ~ +18 V                          |

| Drive voltage             | Negative | 0 V                                    | 0 V                                    |

Table 3-1. ゲート-ソース電圧比較

# 3.3 外付けゲート抵抗(R<sub>G EXT</sub>)の選定

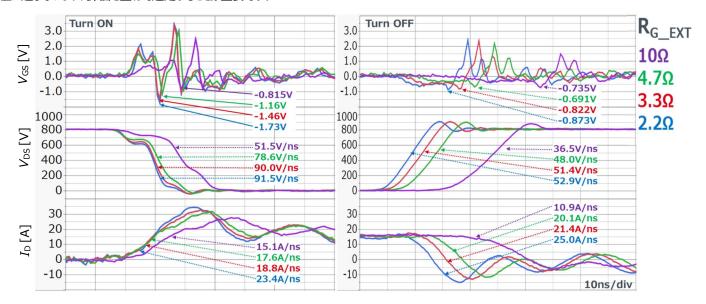

MOSFET のスイッチング性能を決定する重要な要素の一つに外付けゲート抵抗( $R_{G_EXT}$ )の選定があります。スイッチング速度は外付けゲート抵抗( $R_{G_EXT}$ )とデバイス内部ゲート抵抗( $R_{G_INT}$ )の合計値によって変化し、この値が小さいほどスイッチング速度は速くなります。2.8 節で説明したとおり、第4世代 SiC MOSFET は、第3世代 SiC MOSFET と比較して内部ゲート抵抗が大幅に減少しています。このため外付けゲート抵抗を変更せずに置き換えを行った場合は、スイッチング速度が上昇し、スイッチング損失を減少させることができます(2.6 ターンオン/ターンオフ特性参照)。ただし一方で、スイッチング速度が上昇するとゲート・ソース間のサージ電圧が大きくなる傾向があります。

Figure 3-3 は第 4 世代 SiC MOSFET 「SCT4062KR」(1200V, $R_{DS(on)}$ =62m $\Omega$ ) をスイッチングさせた時の非スイッチング側  $V_{GS}$  波形 と、スイッチング側  $V_{DS}$ 、 $I_D$  波形です。ゲート抵抗値が小さいほど、 $V_{DS}$ 、 $I_D$  のスイッチング速度は速くなりますが、非スイッチング側  $V_{GS}$  のサージが大きくなることが分かります。

これらの要素から、外付けゲート抵抗の値は、スイッチング損失を抑えることで要求の動作効率を満たしつつ、かつサージ電圧がデバイス定格値に達しないよう、評価を重ねて選定することが重要です。

Figure 3-3. スイッチングターンオン/オフ時 VGS 波形(SCT4062KR) RG\_EXT 依存性

# 3.3.1 V<sub>GS</sub>サージ測定時の注意点

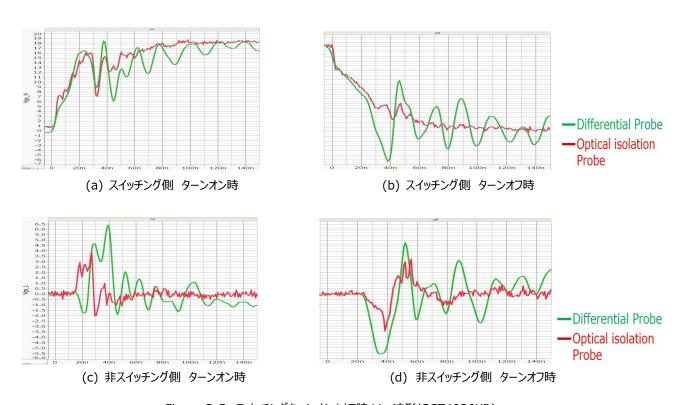

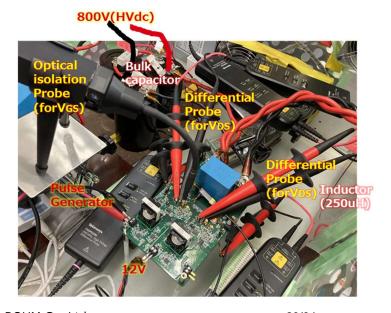

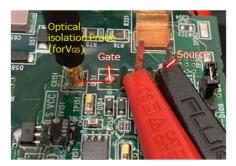

SiC MOSFET は Si MOSFET と比較してスイッチング時のスルーレートが格段に上昇していることで、従来の受動プローブ・差動プローブによる測定では、プローブ起因によるノイズなどの影響で正確な波形を取得することが困難です。そのため、SiC MOSFET のような高速スイッチング波形の測定にはノイズの影響をカットすることができる光絶縁プローブでの測定が推奨されます。光絶縁プローブを用いてダブルパルス試験を行った際の様子を Figure 3-4 に示します。本試験内容と使用した基板についての詳細は「5.ディスクリート用評価基板」をご確認ください。

Figure 3-5 は差動プローブ (Differential Probe)と光絶縁プローブ (Optical isolation Probe)を使用して、同条件でスイッチング波形を取得した際の比較結果です。差動プローブを用いた測定波形に、大きなサージが発生していることが分かります。

Figure 3-5. スイッチングターンオン/オフ時 V<sub>GS</sub> 波形(SCT4036KR)

SiC デバイス測定時の注意点についての詳細はアプリケーションノート「ゲート-ソース電圧測定時の注意点」\*6 もご参照ください。

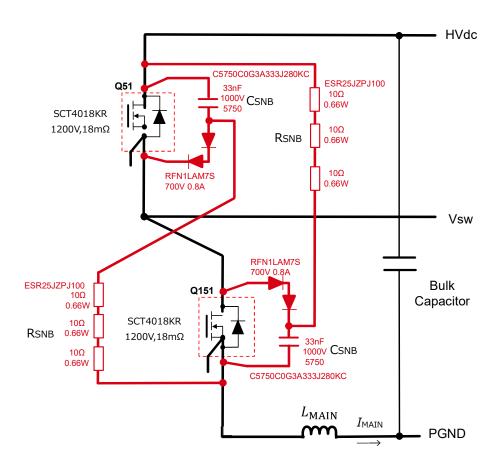

### 3.3.2 V<sub>DS</sub>サージの対策

SiC MOSFET は高速スイッチングという特長を有する一方で、ドレイン-ソース間に発生するサージ電圧が大きくなります。このため、 $V_{GS}$ サージ電圧と同様にドレイン-ソース間電圧も定格電圧内に収まるように  $R_{G_EXT}$ を選定する必要があります。また、スナバ回路のようなサージ吸収回路を追加するといった対策も有効となります。 Figure 3-6 にスナバ回路例を示します

Figure 3-6. スナバ回路例 (SCT4018KR)

非放電型スナバ回路は、高圧入力電圧 HVdc を超えたサージ分のみをスナバ回路内の抵抗で消費するため、高周波スイッチング回路に最適な回路方式となっています。しかし、パターンレイアウトが複雑になるため、4 層以上の基板をご使用下さい。

スナバ回路内の抵抗により消費される電力  $P_{SNB}$  は、すべてスナバ回路内の抵抗  $R_{SNB}$  で消費されます。そのため、 $R_{SNB}$  を設定するためにまず式(1)から  $P_{SNB}$  を導きます。

$$P_{\rm SNB} = \frac{L_{\rm MAIN} \times I_{\rm MAIN}^2 \times f_{\rm SW}}{2} \quad [W] \cdots (1)$$

この数式における  $L_{MAIN}$  は主回路の配線インダクタンスであり、バルクキャパシタ(Bulk Capacitor)の等価直列のインダクタンスを含めた配線インダクタンスです。  $I_{MAIN}$  は MOSFET のターンオフ時のドレイン電流を、 $f_{SW}$  は SiC MOSFET を駆動するスイッチング周波数を表します。 一方、スナバコンデンサの静電容量  $C_{SNB}$  はインダクタンスに蓄積されたエネルギーから次の式(2)で求められます。

$$C_{\text{SNB}} = \frac{L_{\text{MAIN}} \times I_{\text{MAIN}}^{2}}{V_{\text{SURGE}}^{2} - V_{\text{HVdc}}^{2}} \qquad [\text{F}] \cdots (2)$$

© 2022 ROHM Co. Ltd. 20/34 No. 64AN118J Rev.001

$V_{\text{HVdc}}$ は高圧電源、 $V_{\text{SURGE}}$ はサージ電圧の最大値です。更に  $R_{\text{SNB}}$ の抵抗値は以下の式(3)で求められます。

$$R_{\rm SNB} < \frac{-1}{C_{\rm SNB} \times \ln[(V_{\rm SURGE} - V_{\rm SNB})/(V_{\rm SURGE})]} \times \frac{1}{f_{\rm sw}} \quad [\Omega] \cdots (3)$$

$R_{\mathsf{SNB}}$  値を適切に設定することで、SiC MOSFET が一周期の間に  $C_{\mathsf{SNB}}$  で吸収したエネルギーを全て放電させ、サージ吸収効果を最大にできます。

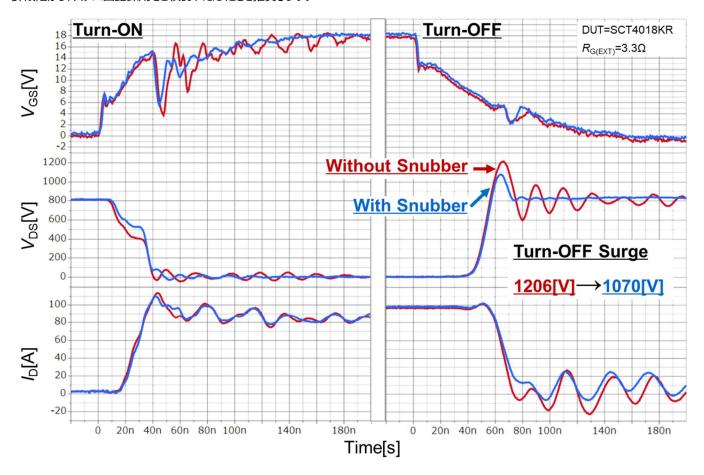

Figure 3-7 に SCT4018KR のダブルパルス試験によるスナバ回路の検証結果を示します。ターンオン時はスナバ回路の有無による違いはほぼありませんが、ターンオフ時は  $V_{DS}$  ターンオフサージが 1207V から 1070V と減少しています。その一方で、スイッチング速度にはほとんど影響がありません。

このように、スナバ回路の実装によって  $V_{\rm DS}$  ターンオフサージを抑制することが可能です。 $V_{\rm DS}$  ターンオフサージが問題となった場合に備え回路設計段階から、スナバ回路採用をご検討いただくことを推奨します。

スナバ回路の設計方法についての詳細はアプリケーションノート「スナバ回路の設計方法」\*4をご参照ください。

### 3.4 デッドタイム(t<sub>DT</sub>)設計

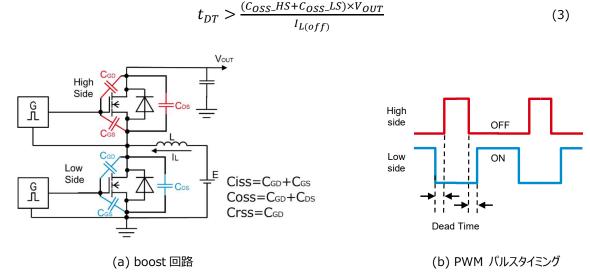

SiC MOSFET をブリッジ構成の回路で使用する場合、ハイサイド(HS)とローサイド(LS)の SiC MOSFET が同時オンしないよう通常デッドタイム期間を設けます。 Figure 3-8(a)に boost 回路でのデッドタイム制御の事例を示します。ローサイド SiC MOSFET がスイッチング用、ハイサイド SiC MOSFET は同期整流用として動作しています。同図(b)で示すとおり、HS と LS の同時オンを防止するためにデッドタイム期間を LS のターンオン前とターンオフ後に設けています。デッドタイム期間中は SiC MOSFET のボディダイオードを通してインダクタ L の電流が流れます。 SiC MOSFET のボディダイオードの順方向電圧 VFは Si デバイスよりも高いため、デッドタイムはできるだけ短時間に設定することが望ましいと言えます。しかし、ターンオフ時のインダクタ L の電流  $I_{L(OFF)}$ が小さくなると、ハイサイド・ローサイドの SiC MOSFET の出力容量( $C_{OSS}$ )への充放電電流が小さくなり、結果としてデッドタイム期間中に  $C_{OSS}$ の充放電、つまり  $V_{DS}$ の変化が完了しないことになります。この場合、本来発生しない同期整流側 SiC MOSFET にスイッチング損失が発生し、効率低下や発熱増大などの問題が生じます。そのため、 $I_{L(OFF)}$ の動作条件に従ってデッドタイム時間の最小値を見積もる必要があります。

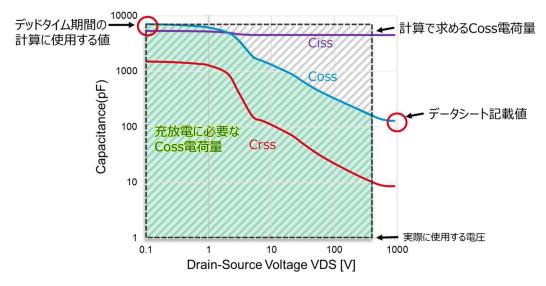

式(3)に示す最小デッドタイム期間は、簡略化するため  $C_{\rm oss}$  を一定として算出していますが、実際にはドレイン-ソース電圧  $V_{\rm DS}$ で  $C_{\rm oss}$  は変化します。一般的にデータシートに記載されている  $C_{\rm oss}$  は、ある  $V_{\rm DS}$  における代表値で記載されていることが多く、デッドタイムの算出に最適とは言えません。 Figure 3-9 に示す  $V_{\rm DS}$ -C 特性を使い、  $C_{\rm oss}$  が最大となる  $V_{\rm DS}$ <1V での値を用いて計算することで、余裕を持ったデッドタイム設計ができます(斜線部分)。 実際に充放電に必要な電荷量は、図中の着色部分の面積になりますので、式(3)の分子にこの面積部分を使用すれば、より正確に  $t_{\rm DT}$ を計算することも可能です。 Figure 3-9 のような容量グラフは、SiC MOSFET のデータシートに記載されています。

Figure 3-8. boost 回路におけるデッドタイム制御

Figure 3-9. 寄生容量の V<sub>DS</sub> 依存性(SCT4018KR)

### 3.5 セルフターンオン対策

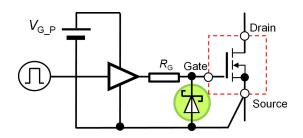

インバータやフルブリッジ回路など MOSFET をブリッジ構成で使用する場合、上下アームのうち片方あるいは両方の MOSFET が同時にオフとなっているはずですが、スイッチング側 MOSFET の動作に合わせて非スイッチング側(還流側)の  $V_{DS}$ や  $I_{D}$ が変化することで、意図としないターンオンが発生してしまうことがあります。これをセルフターンオンと呼びます。この現象が発生すると、効率の低下を招くばかりか、最悪の場合、MOSFET の破壊を招くことになります。

一般的には、オフ時の電圧に負バイアスを印加することでセルフターンオンを対策しており、負バイアス駆動を推奨する製品も多いです。 第4世代 SiC MOSFET の閾値電圧(Vth)は高く設計されているため、セルフターンオンの発生が抑制されています。このため負バイアス駆動を必要としません。5章に記載のあるローム評価基板(P04SCT4018KE-EVK-001, P05SCT4018KR-EVK-001)を用いた評価においても、セルフターンオンの発生は見られておりません。

ただし、お客様で基板設計をされる際、配線インダクタンス等の影響でセルフターンオンが発生する可能性がありますので、その際には回路上でのセルフターンオン対策が必要となります。

Figure 3-10 に対策回路例を示します。 (a)は MOSFET のゲート・ソース間に 1nF~5nF のコンデンサを接続することで、瞬間的なゲート電圧の上昇を抑えます。 (b)はゲート・ソース電圧が一定電圧以下でオンするようなアクティブミラークランプ MOSFET を使うことで、ゲート・ソース間電圧の上昇を抑えます。 これらの対策回路については寄生インダクタンスが存在すると効果が薄れてしまうため、対策部品をゲート端子、ソース端子のなるべく直近に取り付けることが重要です。 部品選定の際も寄生インダクタンスの小さい小型パッケージのものを選ぶことを推奨します。

(a) ゲート-ソース間にコンデンサを接続

(b) アクティブミラークランプ MOSFET

Figure 3-10. ブリッジ構成におけるセルフターンオン対策例

ただしセルフターンオン対策はいずれの方式にも一長一短があり、使用するゲートドライバ IC が有する機能によって適用できない場合があります。 セルフターンオンの発生メカニズムを正しく理解した上で選定するようにお願いします。

なお、セルフターンオン発生のメカニズムについては、アプリケーションノート「<u>ブリッジ構成におけるゲート-ソース電圧の振る舞い</u>」\*2 で詳しく説明しております。また、アプリケーションノート「ゲート-ソース電圧のサージ抑制方法」\*3 に各種対策回路を紹介していますので、併せてご参照下さい。

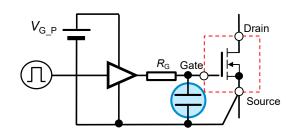

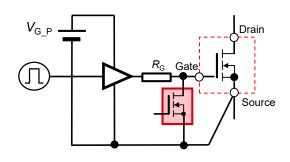

#### 3.6 負サージ対策

3.5 節で説明しましたが、SiC MOSFET のゲート定格電圧は非常に狭く、特に負バイアスに関しては、実使用電圧に対して数 V のマージンしかありません。そのため、ゲート負サージ対策を回路設計段階から盛り込むことが非常に重要です。

Figure 3-11 に負サージの対策回路を示します。(a)はゲート-ソース間に負サージをクランプするダイオードを接続します。(b)は MOSFET のゲート-ソース間に 1nF~5nF のコンデンサを接続することでゲート電圧の瞬間的な降下を抑えます。(c)はゲート-ソース電圧が一定電圧以下でオンするようなアクティブミラークランプ MOSFET を使うことで、ゲート-ソース間電圧の降下を抑えます。(b)、(c)については、3.5 節で説明したセルフターンオン対策と同じであり共用することができます。また、いずれの場合もセルフターンオン対策と同様、対策部品をゲート端子やソース端子の直近につけることや、なるべく寄生インダクタンスの小さい部品を選択することが重要です。

(a) ゲート-ソース間 SBD 接続

(b) ゲート-ソース間コンデンサ接続

(c) アクティブミラークランプ MOSFET

Figure 3-11. ブリッジ構成における負サージ対策

ただし、負サージは必ずしもひとつの要因で発生しておらず、 $V_{DS}$ や  $I_D$  の変化タイミングと密接に関連して複数の要因で発生します。負サージの発生タイミングによって効果的な対策方法は異なりますので、まずは負サージの発生要因を正確に把握する必要があります。そのうえで、負バイアスの有無や基板レイアウト条件など状況に応じた最適な対策をとることが重要です。

なお、負サージの発生メカニズムについては、アプリケーションノート「<u>ブリッジ構成におけるゲート-ソース電圧の振る舞い</u>」\*2 に詳しく説明してあります。また、アプリケーションノート「ゲート-ソース電圧のサージ抑制方法」\*3 に各種対策回路を紹介していますので、併せてご参照下さい。

#### 3.7 推奨レイアウト

これまで説明してきましたゲートドライブ回路の機能としては、

- ●駆動用電源(3.2 節)

- ●ゲート抵抗(スイッチング速度調整)(3.3 節)

- ●ゲートサージ保護(MOSFET ゲート保護)(3.6 節)

がありますが、これらすべての必要な回路部品をプリント基板上に実装しなければなりません。すべての機能を MOSFET の近傍に実装できるのが理想ですが、基板レイアウト上優先順位を決める必要があります。

また、使用するデバイスの特性や回路トポロジによってゲートに発生するサージ電圧の大小が異なるため、対策の優先順位が変わります。 MOSFET 周辺回路のレイアウト検討時には、どの機能のパターンインダクタンスを小さくするべきか、綿密な考察が必要です。

回路トポロジの分類としては、MOSFET の構成とスイッチング方式などで切り分けることができます。 つまり、MOSFET を単独使用する構成 (Single) と、MOSFET を上下直列に接続して使用する構成 (Half Bridge) に大別でき、その中で MOSFET のスイッチング方式としてハードスイッチング方式 (Hard Switching) とソフトスイッチング方式 (Soft Switching) に分類することができます。 Half Bridge 構成では、非スイッチング側がスイッチング側動作の影響を受けるのに対し、 Single 構成では単独使用のため、自身のスイッチング動作のみを考えればよいことになります。

また、デバイスの世代毎によってスイッチング特性やゲート定格電圧に違いがあり、必要とされる保護機能が異なるため注意が必要です。

Table 3-2 に回路構成別に必要な機能を示します。下記の順番に対策部品のレイアウトの優先度を決めていくことで定格内での動作と高い効率を両立することが重要になります。

| Topology    |                | 必要な保護機能               |

|-------------|----------------|-----------------------|

| Single End  | Hard Switching | 1)ゲート-ソース間 SBD 接続     |

|             | Soft Switching | 2)ゲート抵抗               |

| Half Bridge | Hard Switching | 1)アクティブミラークランプ MOSFET |

|             |                | 2)負サージクランプ SBD        |

|             |                | 3)ゲート-ソース間コンデンサ接続     |

|             |                | 4)ゲート抵抗               |

|             | Soft Switching | 1)ゲート-ソース間 SBD 接続     |

|             |                | 2)ゲート-ソース間コンデンサ接続     |

|             |                | 3)ゲート抵抗               |

Table 3-2. ゲート駆動回路における必要機能

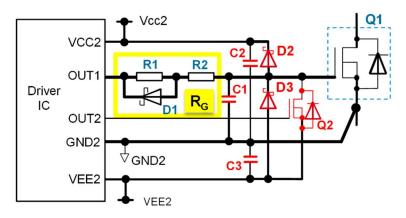

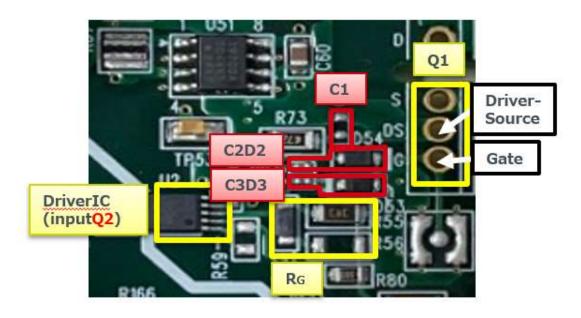

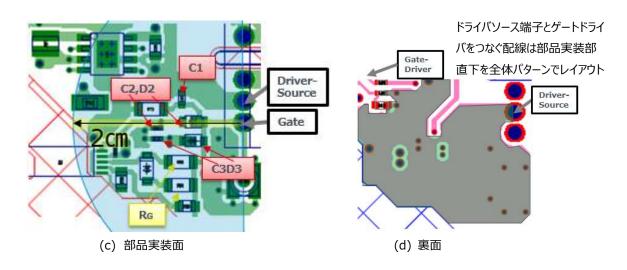

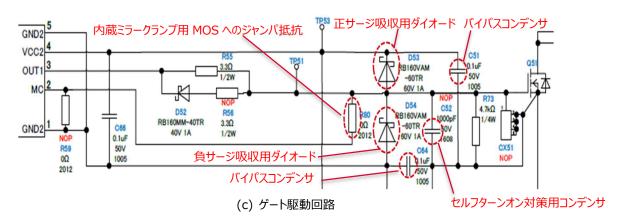

Figure 3-12 に SiC MOSFET 用ハーフブリッジ評価基板(P05SCT4018KR-EVK-001)のレイアウト事例を示します。 同図(a)が駆動回路図、(b)が基板実装写真、(c)および(d)が基板パターンレイアウトです。

この基板は第4世代 SiC MOSFET をハードスイッチング動作で評価する基板のため、ゲートサージ対策が最も重要となります。

MOSFET(Q2)を SiC MOSFET のできる限り直近に配置する必要がありますが、今回 figure 3-12(b)に図示した基板に使用しているゲートドライバ IC(BM61M41RFV-C)にアクティブクランプ MOSFET が内蔵されているため、負サージ吸収用ダイオード(D3)とそのバイパスコンデンサ(C3)を直近に配置しています。次に正サージ吸収用ダイオード(D2)とそのバイパスコンデンサ(C2)をレイアウトしていますが、ドライバ IC からMOSFET までのパターン長によるインダクタンスによって正サージは発生しますので、レイアウト状況に応じて実装可否を判断します。最後にゲートソース間にセルフターンオン対策用コンデンサ(C1)を配置しています。

サージ吸収用部品は MOSFET からの距離が遠くなるほど、その効果が薄れるので、(c)に示すように MOSFET から 2cm 以内の配置を推奨します。また、Driver Source 端子からゲートドライバ IC へのリターン線は、ドライバ回路部品全体の直下に全面パターン(d)のようにレイアウトし、駆動信号やサージ保護回路への外来ノイズの影響を可能な限り受けないようにすることが大切です。

(a) ゲートサージ保護回路例

(b) ゲートサージ保護回路の PCB 実装例 (P04SCT4018KR-EVK-001)

Figure 3-12. ゲートサージ保護回路のレイアウト例 (P05SCT4018KR-EVK-001)

#### ·4.第4世代 SiC MOSFET の信頼性

Table 4-1 に信頼性試験結果を示します。(民生・産業機器用途)

Table 4-1. スルーホールタイプ (TO-247N / TO-247-4L) の信頼性試験項目と結果

#### 1. 寿命試験

| 試験項目      | 試験方法/準拠規格                                                                                | 試験時間       | サンプル数<br>n [pcs] | 故障数<br>Pn [pcs] |

|-----------|------------------------------------------------------------------------------------------|------------|------------------|-----------------|

| 高温逆バイアス   | $T_a = T_{jmax}$ , $V_{DS} = V_{DSmax}$<br>JEITA ED-4701/100A-101A                       | 1000 h     | 22               | 0               |

| 高温ゲートバイアス | $T_a = T_{jmax}$ , $V_{GS} = V_{GSmax}$<br>JEITA ED-4701/100A-101A                       | 1000 h     | 22               | 0               |

| 高温ゲートバイアス | $T_a = T_{jmax}$ , $V_{QS} = V_{QSmin}$<br>JEITA ED-4701/100A-101A                       | 1000 h     | 22               | 0               |

| 高温高湿バイアス  | $T_a = 85^{\circ}\text{C}$ , RH = 85%, $V_{DS} = 100\text{V}$<br>JEITA ED-4701/100A-102A | 1000 h     | 22               | 0               |

| 温度サイクル    | $T_a = -55$ °C (30 min) $\sim T_a = 150$ °C (30 min)<br>JEITA ED-4701/100A-105A          | 100 cycles | 22               | 0               |

| 蒸気加圧      | T <sub>a</sub> = 121°C , 203 kPa [2 atm] , RH = 100%<br>JESD22-A102C                     | 48 h       | 22               | 0               |

| 高温保存      | T <sub>a</sub> = 175°C<br>JEITA ED-4701/200A-201A                                        | 1000 h     | 22               | 0               |

| 低温保存      | 7 <sub>a</sub> = −55°C<br>JEITA ED−4701/200A−202A                                        | 1000 h     | 22               | 0               |

#### 2. 強度試験

| 試験項目      | 試験方法/準拠規格                                                                              | 試験時間      | サンプル数<br>n [pcs] | 故障数<br>Pn [pcs] |

|-----------|----------------------------------------------------------------------------------------|-----------|------------------|-----------------|

| はんだ耐熱性1   | 260 ±5℃のはんだ槽に端子を浸漬<br>JEITA ED-4701/301-302A                                           | 10 s      | 22               | 0               |

| はんだ耐熱性2   | 350 ±10°Cのはんだ槽に端子を浸漬<br>JEITA ED-4701/301-302A                                         | 3.5 s     | 22               | 0               |

| はんだ付け性    | 245 ±5℃のはんだ槽に浸漬<br>JEITA ED-4701/301-303A                                              | 5 s       | 22               | 0               |

| 熱衝撃       | $0^{+5}_{-0}(5 \text{ min}) \sim 100^{+0}_{-5} (5 \text{ min})$ JEITA ED-4701/302-307B | 100 cycle | 22               | 0               |

| 端子強度(引張り) | 引張力 = 20 N<br>JEITA ED-4701/400A-401A                                                  | 10 s      | 22               | 0               |

| 端子強度 (曲げ) | 曲げ荷重 = 10 N<br>JEITA ED-4701/400A-401A                                                 | 2 times   | 22               | 0               |

- ※ 故障判定は仕様書に記載されている電気的特性にて行っています。 はんだ付け性試験については濡れ面積≥95%にて判定しています。

- ※ サンプル基準: 信頼度水準90%、不合格信頼性水準λ1=10%、C=0判定を採用し、 MIL-STD-19500の指数分布型計数1回抜取表に従い、サンプルを22個としています。

### 5.ディスクリート用評価基板

### 5.1 第4世代 SiC MOSFET ディスクリート用評価基板

ロームにてリリースしている第4世代 SiC MOSFET(ディスクリート)用評価基板一覧を Table 5-1 に示します。スイッチング特性を評価するためにハーフブリッジ構成となっており、ダブルパルス試験をはじめ、buck や boost トポロジの評価を最少の外付け部品で行うことができます。また、スイッチング速度の調整や、駆動電圧の変更が可能で、ゲートサージ保護回路なども備えています。

ロームホームページ内の第 4 世代 SiC MOSFET サポートコンテンツ (<a href="https://www.rohm.co.jp/products/sic-power-devices/sic-mosfet#supportInfo">https://www.rohm.co.jp/products/sic-power-devices/sic-mosfet#supportInfo</a>)に詳しい情報がありますのでご参照下さい。

Table 5-1. SiC MOSFET(ディスクリート)用評価基板一覧

| 評価対象デバイス                                  | 外観 | 品名                   |

|-------------------------------------------|----|----------------------|

| TO-247N<br>第 4 世代 SCT4xxxxxxxxEseries 用   |    | P04SCT4018KE-EVK-001 |

| TO-247-4L<br>第 4 世代 SCT4xxxxxxxR series 用 |    | P05SCT4018KR-EVK-001 |

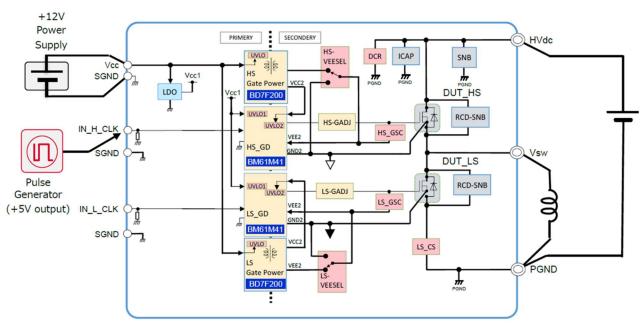

評価基板 P04SCT4018KE-EVK-001 と P05SCT4018KR-EVK-001 を使ったダブルパルス試験の実施例を説明します。 搭載製品はそれぞれ SCT4036KE,SCT4036KR (1200V、36m $\Omega$ )です。 Figure 5-1(a)に試験回路、(b)に測定風景、(c)に MOSFET のゲート駆動回路を示します。

試験の回路動作に必要な機器は、(a)に示す通り制御電源(12V)、パルスジェネレータ(PG)、負荷用インダクタ(250µH)、負荷用高圧電源 ( $V_{HVdc}$ )です。 $V_{HVdc}$ から評価基板までの距離があったため、今回の試験ではバルク用コンデンサ(Bulk capacitor)を接続しています。評価基板上にも  $10\mu$ F フィルムコンデンサが実装されているため、バルク用コンデンサは基本的には必要ありませんが、動作条件に応じて接続することをお奨めします。

(b)に測定時の  $V_{GS}$  のセンシング方法について説明します。通常 MOSFET の波形観測は絶縁プローブもしくは差動プローブを使いますが、SiC MOSFET については、スイッチング速度が高速化しており、プローブがノイズの影響を受けやすくなります。そのため、デバイス直近にコネクタを実装し、プローブからのノイズの影響を受けない光絶縁プローブにて測定を行っています。また、(c)の赤色点線で示した部品は MOSFET のゲート-ソース間に発生するサージを除去するための保護回路であり、その効果も併せて検証しました。

今回の試験ではハイサイド(HS)側 MOSFET をスイッチング用デバイスとして動作させ、ローサイド(LS)側は転流用としてボディダイオードを使用しています。  $V_{HVdc}$  は 800V、 $I_D$  が  $55A\sim60A$  程度になるようにパルス幅を調整し、ターンオンおよびターンオフ時のスイッチング動作を観測しました。 その波形を Figure 5-2、5-3 に示します。

(a) 測定回路ブロック図(P05SCT4018KR-EVK-001)

#### (b) 測定風景(P04SCT4018KE-EVK-001)

Figure 5-1. P04SCT4018KR-EVK-001 測定回路

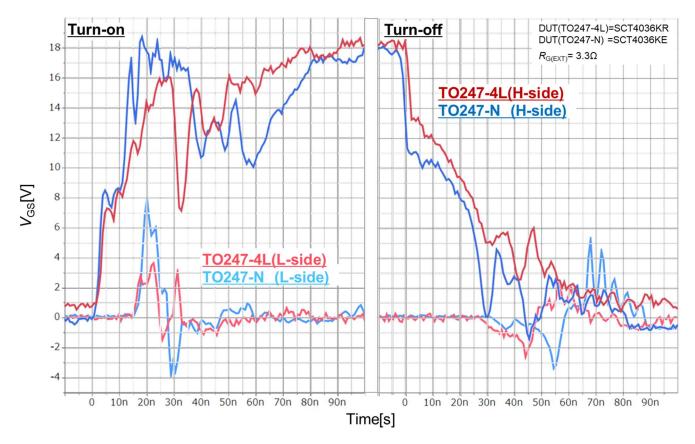

Figure 5-2(a)は  $V_{GS}$  の波形、同図(b)は  $V_{DS}$  の波形,同図(c)は  $I_D$  の波形となっており、SCT4036KE(TO-247N)と SCT4036KR (TO-247-4L)を比較しています。(a)にあるスイッチング側の  $V_{GS\_HS}$  波形はスルーレートがほぼ同等ですが、(c)における  $I_D$  波形はターンオン時も  $V_{GS\_HS}$  なっています。これは、ドライバソース端子による効果です。詳細はアプリケーションノート「ドライバソース端子によるスイッチング損失の改善」\*5 を参照下さい。

非スイッチング(LS)側 MOSFET のゲート-ソース電圧  $V_{GS\_LS}$  は、「3.6 負サージ対策」ゲート-ソースで述べた負サージを、Figure 4-1(c)で示す保護回路が除去しており、SiC MOSFET 特有の狭いゲート定格電圧の仕様を満たすことができています。

(a)ターンオン/オフ時(H-side, L-side) $V_{GS}$

Figure 5-2(b)は V<sub>DS</sub> の波形です。ターンオフ時に TO-247-4L のスルーレートが速くなりますが、サージの値が上昇しています。

(b) ターンオン/オフ時 V<sub>DS</sub>

Figure 5-2(c)は  $I_D$  の波形となっています。前頁で述べた通り、ターンオン・ターンオフ時に TO-247-4L のスルーレートが速くなっていますが、こちらも  $V_{DS}$  と同様にサージの値が上昇していることに注意してください。

(c)ターンオン/オフ時  $I_D$

Figure 5-2. TO-247-4L (SCT4036KR) と TO-247N (SCT4036KE)のスイッチング波形比較また、Figure 5-3 はスイッチング損失 Eon、Eoff の波形を示しています。

TO-247-4L はソース端子の起電によるスイッチングスピード遅延の問題を解消し、トータルスイッチング損失を約 65%低減しています。

Figure 5-3. TO-247-4L (SCT4036KR) と TO-247N (SCT4036KE)のスイッチング損失比較

これらの結果から、ドライバソース端子を備えた TO-247-4L パッケージは通常の TO-247N と比較してスイッチング損失を抑えられることが分かりました。 第 4 世代 SiC MOSFET では TO-247N パッケージでも十分に優秀な特性を持ちますが、TO-247-4L では、スイッチングサージなどに注意し本アプリノートを参考に適切な回路設計を行うことで、より低損失なデバイスとして利用できます。

### 6.第4世代 SiC MOSFET ラインアップ

第4世代 SiC MOSFET ディスクリートパッケージのラインアップについては、ロームホームページ(下記 URL)をご確認下さい。 https://www.rohm.co.jp/products/sic-power-devices/sic-mosfet#anc-02

#### 7.まとめ

第4世代 SiC MOSFET は、従来品よりも低損失・使い易さ・高信頼性のメリットがあり、システム効率等のお客様の設計課題を解決できることを述べました。また一方で、スイッチング速度の劇的な向上により、 $V_{GS}$  サージや  $V_{DS}$  ターンオフリンギングを抑制、配線インダクタンスにまで踏み込んだ回路設計をより慎重に検討する必要があります。このアプリケーションノートが第4世代 SiC MOSFET を正しくお使い頂き、性能を最大限に引き出すための一助になることを期待します。

#### 参考資料:

- \*1 「SiC パワーデバイス・モジュール アプリケーション ノート Rev.003」 アプリケーションノート (No. 63AN101JRev.003) ローム株式会社, 2020 年8 月

- \*2 「<u>ブリッジ構成におけるゲート-ソース電圧の振る舞い</u>」 アプリケーションノート(No. 60AN134JRev.002)ローム株式会社, 2020 年4 月

- \*3 「<u>ゲート-ソース電圧のサージ抑制方法</u>」 アプリケーションノート (No. 62AN009JRev.002) ローム株式会社, 2020 年4 月

- \*4 「<u>スナバ回路の設計方法</u>」 アプリケーションノート (No. 62AN036JRev.002) ローム株式会社, 2020 年4 月

- \*5 「<u>ドライバソース端子によるスイッチング損失の改善</u>」 アプリケーションノート (No. 62AN039JRev.002) ローム株式会社, 2020 年4 月

- \*6「<u>ゲート-ソース電圧測定時の注意点</u>」 アプリケーションノート(No. 62AP084JRev.002)ローム株式会社, 2020 年4 月

- \*7 「<u>測定波形から電力損失を求める</u>」 アプリケーションノート (No. 62AN133J Rev.002) ローム株式会社, 2022 年6 月

- \*8「<u>スイッチング回路の電力損失計算</u>」 アプリケーションノート(No. 62AN1311 Pey 001)ローム株式会社 2020 年7 E

- アプリケーションノート (No. 62AN131J Rev.001) ローム株式会社, 2020 年7 月 \*9「スイッチング波形のモニタ方法」

- アプリケーションノート (No. 62AN151J Rev.001) ローム株式会社, 2020 年4 月 \*10「パワー測定におけるプローブ校正の重要性 デスキュー編」

- アプリケーションノート (No. 63AN148J Rev.001) ローム株式会社, 2020 年12 月

- \*11「<u>バイパスコンデンサのインピーダンス特性</u>」 アプリケーションノート (No. 63AN090J Rev.001) ローム株式会社, 2020 年9 月

- \*12「熱設計とは」

アプリケーションノート (No. 64AN030J Rev.001) ローム株式会社, 2021 年6 月

\*13「熱抵抗と放熱の基本」

アプリケーションノート (No. 64AN042J Rev.001) ローム株式会社, 2021 年8 月

\*14「過渡熱抵抗データからジャンクション温度を求める方法」

アプリケーションノート (No. 64AN027J Rev.001) ローム株式会社, 2021 年6 月

\*15「熱電対を用いた温度測定における注意点」

アプリケーションノート (No. 62AN153J Rev.001) ローム株式会社, 2020 年4 月

\*16「熱シミュレーション用 2抵抗モデル」

アプリケーションノート (No. 62AN122J Rev.001) ローム株式会社, 2020 年3 月

\*17「pn 接合の順方向電圧を用いた温度測定の注意点」

アプリケーションノート (No. 62AN135J Rev.001) ローム株式会社, 2020 年4 月

© 2022 ROHM Co. Ltd. 33/34 No. 64AN118J Rev.001

#### \*18「熱モデルとは」

アプリケーションノート (No. 62AN098J Rev.001) ローム株式会社, 2019 年12 月

#### \*19「熱モデルの使い方」

アプリケーションノート (No. 64AN112J Rev.001) ローム株式会社, 2020 年2 月

#### \*20「熱電対でパッケージ裏面を測定するときの注意点」

アプリケーションノート (No. 63AN066J Rev.001) ローム株式会社, 2020 年10 月

### \*21「熱抵抗 RthJC の測定方法と使い方」

アプリケーションノート (No. 63AN039J Rev.001) ローム株式会社, 2020 年10 月

#### ご注意

- 1) 本資料の記載内容は改良などのため予告なく変更することがあります。

- 2) 本資料に記載されている内容は製品のご紹介資料です。ご使用に際しては、別途最新の仕様書を必ずご請求のうえ、ご確認ください。

- 3) ロームは常に品質・信頼性の向上に取り組んでおりますが、半導体製品は種々の要因で故障・誤作動する可能性があります。

- 万が一、本製品が故障・誤作動した場合であっても、その影響により人身事故、火災損害等が起こらないようご使用機器でのディレーティング、冗長設計、延焼防止、バックアップ、フェイルセーフ等の安全確保をお願いします。 定格を超えたご使用や使用上の注意書が守られていない場合、いかなる責任もロームは負うものではありません。

- 4) 本資料に記載されております応用回路例やその定数などの情報につきましては、本製品の標準的な動作や使い方を説明するものです。

- したがいまして、量産設計をされる場合には、外部諸条件を考慮していただきますようお願いいたします。

- 5) 本資料に記載されております技術情報は、製品の代表的動作および応用回路例などを示したものであり、 ロームまたは他社の知的財産権その他のあらゆる権利について明示的にも黙示的にも、その実施また は利用を許諾するものではありません。上記技術情報の使用に起因して紛争が発生した場合、ロームは その責任を負うものではありません。

- 6) 本資料に掲載されております製品は、耐放射線設計はなされておりません。

- 7) 本製品を下記のような特に高い信頼性が要求される機器等に使用される際には、ロームへ必ずご連絡の上、承諾を得てください。

- ·輸送機器(車載、船舶、鉄道など)、幹線用通信機器、交通信号機器、防災·防犯装置、安全確保のための装置、医療機器、サーバー、太陽電池、送電システム

- 8) 本製品を極めて高い信頼性を要求される下記のような機器等には、使用しないでください。 ・ 航空宇宙機器、原子力制御機器、海底中継機器

- 9) 本資料の記載に従わないために生じたいかなる事故、損害もロームはその責任を負うものではありません。

- 10) 本資料に記載されております情報は、正確を期すため慎重に作成したものですが、万が一、当該情報の誤り・誤植に起因する損害がお客様に生じた場合においても、ロームはその責任を負うものではありません。

- 11) 本製品のご使用に際しては、RoHS 指令など適用される環境関連法令を遵守の上ご使用ください。 お客様がかかる法令を順守しないことにより生じた損害に関して、ロームは一切の責任を負いません。 本製品の RoHS 適合性などの詳細につきましては、セールス・オフィスまでお問合せください。

- 12) 本製品および本資料に記載の技術を輸出又は国外へ提供する際には、「外国為替及び外国貿易法」、「米国輸出管理規則」など適用される輸出関連法令を遵守し、それらの定めにしたがって必要な手続を行ってください。

- 13) 本資料の一部または全部をロームの許可なく、転載・複写することを堅くお断りします。

ローム製品のご検討ありがとうございます。 より詳しい資料やカタログなどご用意しておりますので、お問合せください。

# ROHM Customer Support System

http://www.rohm.co.jp/contact/