## SIC MOSFET

## ゲート駆動回路の基礎とデザインガイドライン

SiC MOSFET は、ゲート-ソース間に一定の電圧を印加することで導通状態を制御できるため、スイッチングデバイスとして各種スイッチング電源に使われています。スイッチングデバイスとして重要なことは、導通損失の低減に加えスイッチング損失の低減や EMC ノイズの極小化などがあり、ゲート-ソース間電圧の印加方法を工夫することで実現しています。SiC MOSFET の特性を十分に引き出す使い方を検討するためには、まずはゲート-ソース間に電圧を印加した時に起こる基本的な動作(状態遷移)を理解しておく必要があります。そこで、本アプリケーションノートではゲート-ソース間に電圧を印加した時、SiC MOSFET で起こる状態遷移をまとめ、性能を十分に引き出すためのゲート駆動回路設計ガイドラインとして、設計の一助になることを目的としています。

## 目次

| 1. SiC MOSFET について                                             | 2  |

|----------------------------------------------------------------|----|

| 近年のスイッチングデバイスに関するニーズとパワーデバイスの適用範囲から、SiC MOSFET の重要性について説明します。  |    |

| また、SiC MOSFET の構造や容量特性について言及し、ゲートの入力容量に充電する動作を説明します。           |    |

| 2. ゲート駆動に関連するトラブル                                              | 4  |

| SiC MOSFET のスイッチング時に発生する損失やドレイン-ソース間電圧サージ、セルフターンオンなどに関して説明します。 |    |

| 3.ゲートドライバの役割                                                   | 8  |

| 駆動電圧の生成や、絶縁保護機能など、ゲートドライバの持つ能力を説明します。                          |    |

| 4.ゲート駆動回路のデザインガイドライン                                           | 9  |

| SiC MOSFET の特性を生かすためのゲートドライバ IC の選定方針や、消費電力の計算方法を紹介します。        |    |

| 5.ゲート駆動回路の設計例                                                  | 14 |

| ROHM のデバイスを用いて、具体的にゲート駆動回路の設計例を説明します。                          |    |

| 6.まとめ                                                          | 17 |

## 1. SiC MOSFET について

#### 1.1 SiC MOSFET の重要性

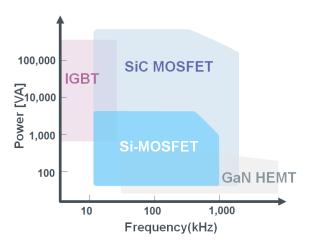

近年、自動車をはじめ身の回りの様々なモノの電動化が急速に進んでおり、より高効率な電力の制御が技術的な課題となっています。電力制御は一般的に電流をターンオン/ターンオフすることで電源から負荷への電力供給量を調節したり、直流を交流に変換したりするなど、電力の形態を変化させる事です。このターンオン/ターンオフを担うスイッチングデバイスとしてパワーデバイスが用いられています。Figure 1 はスイッチング周波数と負荷容量の適用範囲を示しています。

近年では、省エネ化や機器の小型化へのニーズが高まっています。スイッチング周波数を高周波化することで受動部品であるインダクタやキャパシタを小型化できます。高周波化すると、その分スイッチング損失は増えます。高周波化と省エネを両立させるには、スイッチング特性の良い SiC MOSFET が最も適用範囲が広く、重要性が増しています。

Figure 1. パワーデバイスの適用範囲

#### 1.2 SiC MOSFET の基本的構造

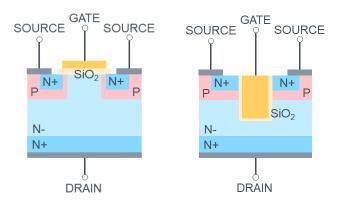

SiC MOSFET は Figure 2 の構造となっています。ドレイン-ソース間にドレインを正極性とした電圧( $V_{DS}$ )を印加、さらにゲート-ソース間にゲートを正極性とした電圧( $V_{GS}$ )を印加することで P 型半導体領域に電子が引き寄せられ、n 型のチャネル(反転層)が形成されます。このチャネルを通り、ドレインからソースへ電流が流れます。この仕組みにより、MOSFET は電圧によるスイッチング制御、n 型チャネルによる高速性、縦型構造による高耐圧を実現しています。

SiC MOSFET はゲート構造やドリフト層の構造によってプレーナ構造 (Figure 2-(a))とトレンチ構造(Figure 2-(b))に大別されます。

Figure 2-(a). プレーナ型構造 Figure 2-(b). トレンチ型構造

#### ・プレーナ構造

Figure 2-(a)に示すとおり、ゲートがウエハの表面に形成されます。 そのため、チャネルが横向きに形成されるため、一つのセルサイズが大き くなってしまいます。

## ・トレンチ構造

Figure 2-(b)に示すとおり、トレンチ構造はウエハの表面からドレイン方向に溝を掘り、ゲート電極を埋め込んでいます。この構造ではチャネルが垂直に形成されているため、セルの微細化が可能となっています。そのため、セルをプレーナ構造より多く並べることができ、オン抵抗を低減することができます。

#### 1.3 寄生容量特性

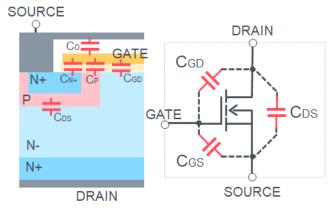

SiC MOSFET にはソース電極、ゲート電極、ドレイン電極があり、これらの電極の組み合わせで、寄生の静電容量が発生します。ソース電極とゲート電極間の容量を  $C_{GS}$ 、ドレイン電極とゲート電極間の容量を  $C_{GD}$ 、ソース電極とドレイン電極間の容量を  $C_{DS}$ とします。 $C_{GD}$ はゲート酸化膜を誘電体として形成される静電容量によって決まり、 $C_{GS}$ はゲート-ソース間で形成される静電容量  $C_{O}$ と P チャネルおよび N チャネルと酸化膜を誘電体として形成される  $C_{P}$ 、 $C_{N+}$ の合計で決まります( $C_{GS}$ = $C_{O}$ + $C_{P}$ + $C_{N+}$ )。また、 $C_{DS}$  はドレイン-ソース間の接合容量です。(Figure 3)

Figure 3. 寄生容量等価回路

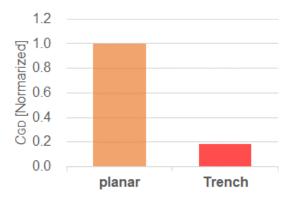

単一セル構造でゲート酸化膜が縦方向に深いトレンチ構造の方が、基本的に寄生容量が大きい傾向です。但し、ROHMの SiC MOSFET は、プロセス技術の進化によりトレンチ構造のオン抵抗を低減できる特徴を活かし、チップサイズが小さくなることでチップ全体の寄生容量を低減しています。

Figure 4 は ROHM 第 2 世代プレーナ構造 SiC MOSFET と第 4 世代トレンチ構造 SiC MOSFET のゲート容量比較です。第 4 世代ではトレンチ構造でありながらもセルの微細化によりプレーナ構造よりも小さい寄生容量を実現しております。

Figure 4-(a). C<sub>GD</sub> 比較(ROHM プレーナ vs トレンチ) 測定条件: V<sub>GS</sub>=0V, V<sub>DS</sub>=800V, T<sub>i</sub>=25℃

Figure 4-(b). C<sub>GS</sub>比較(ROHM プレーナ vs トレンチ) 測定条件:V<sub>GS</sub>=0V,V<sub>DS</sub>=800V,T<sub>j</sub>=25℃

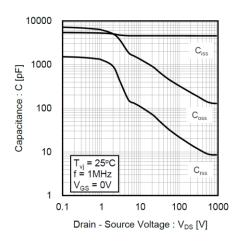

これらの寄生容量は一般的に MOSFET のデータシートに( I )/入 力容量( $C_{iss}$ ), (II )/出力容量( $C_{oss}$ ), (II )/帰還容量( $C_{rss}$ )の 3 つのパラメータで示されています。これらは、スイッチング特性に影響を与える重要なパラメータです。

## (I). 入力容量: $C_{iss} = C_{GD} + C_{GS}$

MOSFET をターンオン/ターンオフするためには、 $C_{iss}$ を充電/放電する必要があり、遅延時間に影響します。 $C_{iss}$ を充電するために必要な電荷量が $Q_{a}$ です。

#### (Ⅱ). 出力容量: Coss = CDS + CGD

$C_{\rm oss}$  はターンオフ特性に影響します。 $C_{\rm oss}$  が大きい場合は、ターンオフ時に  $C_{\rm oss}$  を充電するために要する時間が長くなるため、ターンオフ時間が長くなります。

#### (Ⅲ). 帰還容量: C<sub>rss</sub> = C<sub>GD</sub>

C<sub>rss</sub> は、スイッチング速度に影響します。 C<sub>rss</sub> が大きい場合は、ドレイン -ソース電圧のターンオン、ターンオフ時間が長くなります。

また、 $C_{oss}$ 、 $C_{rss}$ はドレイン-ソース間電圧  $V_{DS}$ に対して依存性を持っています。Figure 5 に示すとおり  $V_{DS}$ を大きくしていくと、容量値は小さくなる傾向にあります。

Figure 5. ROHM SiC MOSFET 寄生容量特性例

#### 1.4 ゲート充電特性

Figure 6 にゲート充電特性の例を示します。SiC MOSFET のゲート充電特性は、駆動電流や駆動損失を決定するパラメータです。 大きく3 つの期間に分けられます。

Figure 6. ゲート充電特性とドレイン-ソース電圧・電流

#### Period. 1

ゲート電圧が上昇し、ミラー電圧に到達するまでの期間です。ゲート ソース間容量  $C_{GS}$  へ充電されてゲート電圧が上昇します。 $V_{GS(th)}$ を 超えてからドレイン-ソース間に電流が流れ始めます。また、ドレイン電 流の増加後、ドレイン-ソース電圧( $V_{DS}$ )が下がります。

#### Period. 2

$V_{DS}$ が変化し、ゲート-ドレイン容量  $C_{GD}$ が放電されます。この期間はミラー期間と呼ばれ、ゲート-ソース電圧は上昇しません。また、この時のゲート電圧はプラトー電圧と呼ばれます。

#### Period. 3

$C_{GD}$  の電圧が  $C_{GS}$  の電圧と同じになるとスイッチング動作は完了し、ドレイン-ソース間電圧が変化しなくなり、再び  $C_{GS}$  と  $C_{GD}$  への充電が始まりゲート電圧が上昇を始めます。

ドレイン-ソース電圧の変化を速くするには、 $C_{GD}$  の小さいデバイスを選ぶか、ミラー期間を短くするため、 $C_{GD}$  へ放電する電流を大きくします。

## 2.ゲート駆動に関連するトラブル

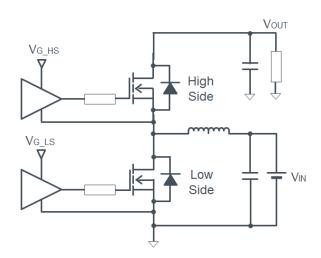

ゲート駆動回路を設計する上で、同期整流方式 BOOST 回路 (Figure 7) を用いて、SiC MOSFET をスイッチングする際に発生するトラブル事例を説明します。

Figure 7. 同期整流方式 BOOST 回路

## 2.1 デバイスの発熱/電力損失が大きい

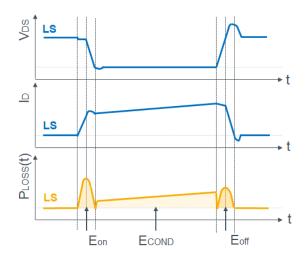

インダクタ負荷を駆動するデバイスに発生する電力損失( $P_{LOSS}$ )は、Figure 8 のようにスイッチングのターンオン/ターンオフ時に、電圧・電流の重なりによって発生するスイッチング損失( $E_{con}/E_{off}$ )とターンオン時に流れる電流とデバイスのオン抵抗で決まる導通損失( $E_{COND}$ )があります。スイッチング毎に発生するため、式(1)のようにスイッチング周波

数( $f_{SW}$ )の積がデバイスの電力損失  $P_{LOSS}$  になります。

$$P_{\text{LOSS}} = (E_{\text{on}} + E_{\text{off}} + E_{\text{COND}}) \times f_{\text{SW}} \cdots (1)$$

Figure 8. デバイスの損失波形

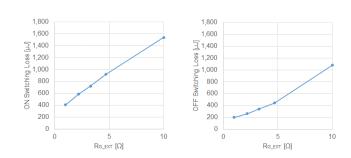

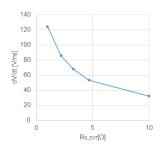

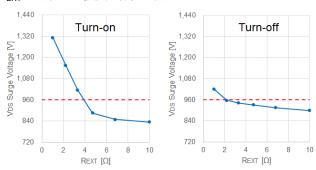

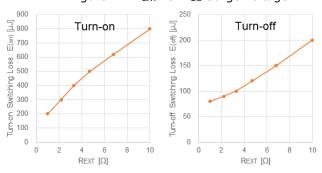

電力損失を削減するためには、スイッチング周波数を低くすることも方法のひとつですが、スイッチング周波数を高くするメリットを選択している場合、ゲート駆動回路で対策します。Figure 9 はゲート抵抗の大きさとターンオン損失( $E_{on}$ )、ターンオフ損失( $E_{of}$ )の関係を示したグラフで、Figure 10 はゲート抵抗( $R_{G_{EXT}}$ )とスイッチング速度(dV/dt)の関係を示したグラフです。Figure 9 から、 $R_{G_{EXT}}$ を小さくするとターンオン、ターンオフともに損失が低下することが分かります。これは Figure 10 に示すように  $R_{G_{EXT}}$ を下げて、スイッチング速度(dV/dt)を速くすることにより  $V_{DS}$ の変化時間を短くしたことが要因です。

Figure 9.  $R_{G}$  EXT vs.  $E_{SW}$

Figure 10.  $R_{G\_EXT}$  vs. dV/dt

#### 2.2 ドレイン-ソース電圧( $V_{DS}$ )のサージ電圧が大きい

Low Side の MOSFET をターンオフする時に出力電圧( $V_{OUT}$ )までドレイン-ソース電圧  $V_{DS}$  が上昇しますが、電流経路のインダクタンス成分が原因で、サージ電圧が発生します。

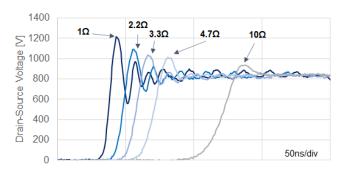

$V_{\rm DS}$  サージ電圧を低減する方法として、ドレイン-ソース間にスナバ回路を設ける方法もありますが、ゲート駆動回路ができる対策としては、外付けゲート抵抗値  $R_{\rm G_EXT}$ を大きくすることでスイッチング速度を下げる方法もあります。Figure 11 はゲート抵抗( $R_{\rm G_EXT}$ )とドレイン-ソース電圧のサージの変化を示します。

Figure 11. V<sub>DS</sub>サージ波形-R<sub>G EXT</sub>特性

# 2.3 ゲート-ソース電圧(V<sub>GS</sub>)の「正側の電圧上昇」や「負サージ電圧」が発生する

$V_{DS}$  および  $I_D$  の変化に着目しがちですが、それらが変化することによるゲート-ソース電圧( $V_{GS-HS}$ )への影響も考慮する必要があります。アプリケーションノート「ブリッジ構成におけるゲート-ソース電圧の振る舞い」 \*1 で詳しく説明していますが、本アプリケーションノートでも改めて説明します。

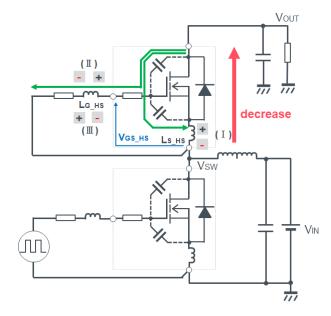

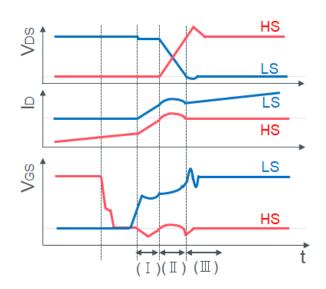

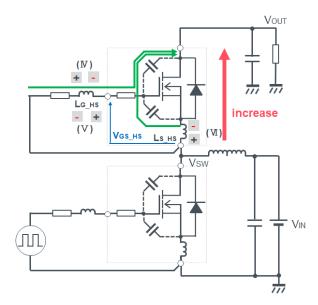

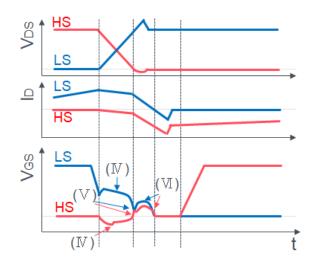

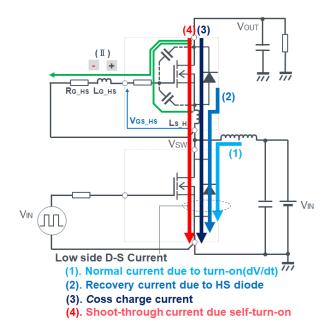

Low Side 側(以降 LS)のターンオン時の挙動を等価回路図 (Figure 12)と波形(Figure 13)で示します。LS ターンオン時はまず  $I_D$ が変化します。LS の  $I_D$ は増加傾向、High Side(以降 HS)の  $I_D$ は減少方向となるため、事象(I)により、Figure 12(I)で示す極性 で起電が発生します。この起電による電流はソース側を正として CGS-HS に充電するため、HS では  $V_{GS-HS}$  がマイナス側に引っ張られ、「負サ ージ」として見えます。 $I_D$  の変化が終了すると LS 側の  $V_{DS}$  の電位が 減少します。Figure 13(Ⅱ)のように流れ、HS、LS それぞれ「正側に 電圧上昇」が VGS-HS で起きます。そのため、本来オフしているはずの HS 側は V<sub>GS-HS</sub>の持ち上がり程度次第ではターンオン動作を始めてし まい(セルフターンオン)、LS 側のターンオン動作と重なり上下 MOSFET の同時ターンオンが発生し、貫通電流が流れます。CGS へ の充電電流はターンオン動作が完了するまで流れ続け、LG HS に蓄え られますが、 $V_{SW}$  の変化が完了した時点で消滅し、 $L_{G_{-HS}}$  が Figure 12(Ⅲ)のように起電します。この起電により、再び「負サージ」として見 えます。

Figure 12. ゲート-ソース電圧の挙動を示した等価回路図(LS 側ターンオン時)

Figure 13. ゲート-ソース電圧の挙動を示した波形 (LS 側ターンオン時)

次に LS 側ターンオフ時の動作について説明します。 LS 側のターンオフ時の挙動を等価回路図(Figure 14)と波形(Figure 15)で示します。

ターンオン時と同じく、各事象に(IV)、(V)、(VI)の附番をしています。ターンオン時と比べ、 $V_{DS}$ と  $I_{D}$ の変化順序が変わってくるのみで基本的な動作は同じとなり以下の対応になります。

ターンオフ ターンオン

事象(Ⅳ) → 事象(Ⅱ)

事象(Ⅴ) → 事象(Ⅲ)

事象(VI) → 事象(I)

HS 側の VGS「負サージ」が事象(IV)になります。

事象(VI)による VGS の持ち上がりについてはすでにターンオフ 終了寸前であり、HS 側がターンオン動作に入っていたとしても LS側はターンオフしておりほとんど問題になりません。

Figure 14. ゲートソース電圧の挙動を示した等価回路図 (LS 側ターンオフ時)

Figure 15. ゲートソース電圧の挙動を示した波形 (LS 側ターンオフ時)

## 2.4 正側の電圧上昇によるセルフターンオン (誤点弧) の発生

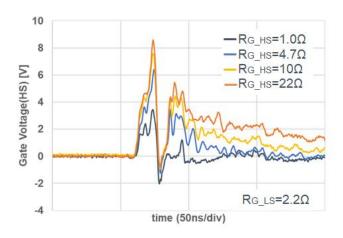

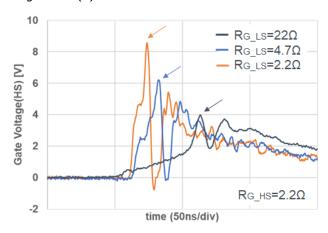

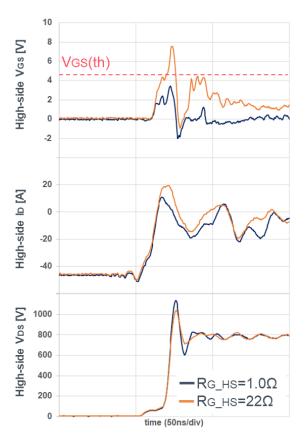

ターンオン時(事象Ⅱ)において、正側の電圧上昇によりゲート電 圧がゲートスレッショルド電圧 VGS(th)を上回ることで、意図しないターン オンをしてしまうと、セルフターンオンが発生してしまいます。正側の電圧 上昇は、LS側のスイッチング速度とゲート抵抗(RG HS)に関連があり、 LS 側のスイッチング速度が遅く、HS 側のゲート抵抗(R<sub>G\_HS</sub>)が小さい 方がセルフターンオン発生しにくくなります。Figure 16 は、駆動側 (LS)がターンオン時の、還流側(HS)のゲート-ソース間電圧波形です。 ゲート抵抗(RG HS)が大きい方ほど、ゲート電圧の電圧上昇が大きく なり(Figure 16-(a))、駆動側(LS)のゲート抵抗(R<sub>G\_LS</sub>)を小さくし、 スイッチングを速くする方が、ゲート電圧の電圧上昇が大きくなります (Figure 16-(b))。

Figure 16-(a). 還流側ゲート抵抗と還流側ゲート電圧上昇

Figure 16-(b). 駆動側ゲート抵抗と還流側ゲート電圧上昇

セルフターンオンが発生した場合、Figure 17 に示すように、LS 側 のドレイン-ソース電流には、以下の4つの電流が観測されます。

- ①通常のターンオン電流

- ②HS 側ダイオードのリカバリ電流

- ③セルフターンオンによる貫通電流

- ④Coss 充電電流

よって、セルフターンオンが発生しているかを判定することは非常に困難 です。また、評価している波形はデバイスの内部抵抗の影響も含まれ ているため、単純にゲート波形が VGS(th)を超えたかどうかで判定するこ とも良い判断基準ではありません。

Figure 17. セルフターンオン時の LS 電流

Figure 18 は、還流側のゲート抵抗( $R_{G_-HS}$ )を  $1\Omega$ と  $22\Omega$ にした場合の波形比較です。 $R_{G_-HS}$ が  $22\Omega$ の時、大きなゲート電圧の上昇が発生し、 $V_{GS(th)}$ を約 10ns 間超えています。この時、セルフターンオンにより電流が増えたことにより、還流側の  $V_{DS}$  の傾きが小さくなり、ピークが低下していることが分かります。また、駆動側のドレイン-ソース電流は増加します。

Figure 18. セルフターンオンの疑いがある波形(還流側)

Figure 19 に示すとおり、スイッチング損失で比較するとターンオン時のリカバリ損失  $E_{RR}$  (※セルフターンオンと思われる電流波形を含む)が  $R_{G_{-HS}}$ =22 $\Omega$ の方が若干増加していますが、ターンオン損失( $E_{on}$ )とターンオフ損失( $E_{off}$ )は、ほぼ増減はなく、セルフターンオンの影響は小さいと言えます。

常温でセルフターンオンの疑いがあるときは、 $V_{GS(th)}$ が低くなる高温時でのスイッチング損失で判定する方法や、負バイアスを引いた時と OV でターンオフした時の損失で大きな差がないことを比較することで確認することができます。

Figure 19. 還流側ゲート抵抗を変えたスイッチング損失比較

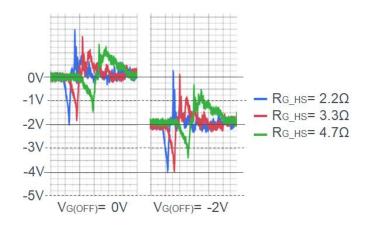

#### 2.5 負サージ電圧の発生

ゲート抵抗とゲート負電圧設定による駆動側ターンオフ時の還流側 ゲート波形を Figure 20 に示します。ゲート負電圧によるゲート負サ ージの影響はないことが確認できます。ゲート抵抗が大きい方が、負サ ージの影響が小さくなる傾向があります。

Figure 20. ゲート抵抗とゲート負サージ

## 3.ゲートドライバの役割

ゲート駆動回路を設計する上でまず、ゲートドライバの役割を理解 する必要がありますので、その主な役割を以下に示します。

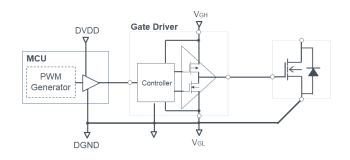

#### 3.1 パワーデバイスの駆動電圧を出力する

パワーデバイスの推奨駆動電圧は、デバイスやメーカーによって異なります。ROHMの SiC MOSFET の場合、正のゲート-ソース電圧は $15\sim18V(V_{GH})$ 、負のゲート-ソース電圧は $0V(V_{GL})$ を推奨しています。主にゲート信号の発生源であるマイコン(MCU)は、5V/3.3V(DVDD)の CMOS 出力であり、パワーデバイスを最適に駆動するには、15V以上で駆動することがゲートドライバの役割のひとつになります。Figure 21 にパワーデバイスの駆動電圧を出力することを目的としたローサイド型ゲートドライバの回路図を示します。

Figure 21. "ローサイド型"ゲートドライバの回路図概要

#### 3.2 パワーデバイスを高速にスイッチングできるように駆動する

ゲート信号の発生源であるマイコン(MCU)は、一般的に電流能力は 0.1A 以下と少なく、パワーデバイスを直接駆動することはできません。 MOSFET の入力容量を 5nF とし、マイコンがもつ I/O ポートの出力インピーダンスの一例として  $500\Omega$ とすると、時定数 t は以下の値になります。

$t = CR = 5n \times 500 = 2.5 \, [\mu s]$

ゲートのターンオン/ターンオフの速度が非常に遅くなりスイッチング損失が大きくなります。パワーデバイスを最適に駆動するためには、高速に駆動することも、ゲートドライバの役割のひとつになります。

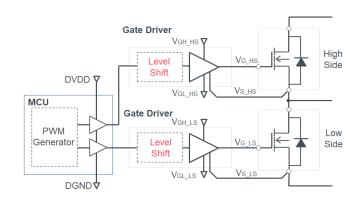

## 3.3 制御回路からレベルシフトする

Figure 22 にレベルシフトの役割をもつゲート駆動回路例を示します。ゲート信号の発生源であるマイコン(MCU)の GND 電位とパワーデバイスのソース電位(V<sub>S\_HS</sub>,V<sub>S\_LS</sub>)は異なることがほとんどであり、最適なゲート-ソース間電圧を印加するには、MCU の信号からレベルシフトする必要があり、これもゲートドライバの重要な役割のひとつになります。

Figure 22. "レベルシフト"型ゲート駆動回路図例

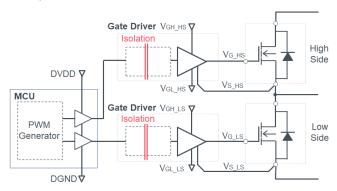

#### 3.4 制御回路とパワー回路を絶縁する

パワーデバイスを使用するアプリケーションにおいては、主回路のバス電圧は数百ボルト以上の電圧を扱い、数十 A 以上の電流がパワーデバイスのドレイン・ソース間に流れます。制御系とパワー系のシステム間が非絶縁の場合、万が一漏電し、製品自体の絶縁対策が十分では無かった場合や、システムに何らかの故障が生じ電子部品が破損した際、ユーザーが感電する恐れがあります。Figure 23に絶縁型ゲート駆動回路図の一例を示します。このように、絶縁能力があるゲートドライバ IC を使用することで、ユーザーが感電するリスクを下げます。

Figure 23. "絶縁型"ゲート駆動回路図例

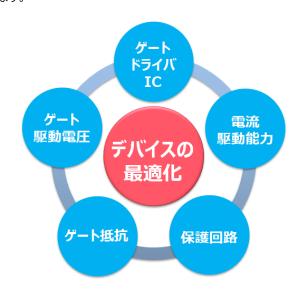

## 4.ゲート駆動回路のデザインガイドライン

ゲート駆動回路はゲートドライバやその周辺回路で構成されていますが、ゲートドライバは一般的に IC 化されています。デバイスの最適化を行うために、Figure 24 に示す、ゲートドライバ IC の選定、ゲート抵抗の選定、ゲート駆動電圧・電流駆動能力の設計、保護回路の設計が必要です。ゲートドライバ回路の基本的な設計項目を以下に示します。

Figure 24. ゲート駆動回路の設計要素

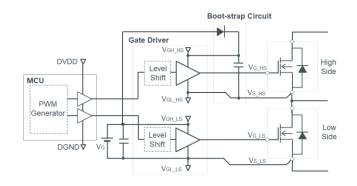

## 4.1 ゲートドライバ IC の選定

ゲートドライバ IC には 1ch(ローサイド)/2ch(ローサイド+ハイサイド)駆動タイプ、絶縁タイプ/非絶縁タイプなど使用用途に合わせた選定が必要になります。Table 1 では駆動条件におけるゲートドライバ IC の種類を紹介します。Figure25で2ch 出力ゲートドライバ IC 使用時の設計回路例を示します。

Table 1. ゲートドライバの種類と機能

| 松松台店    | ゲートドライバ IC の種類 |        |     |  |

|---------|----------------|--------|-----|--|

| 機能      | ローサイド          | レベルシフト | 絶縁型 |  |

| ローサイド駆動 | 有              | 有      | 有   |  |

| ハイサイド駆動 | 無              | 有      | 有   |  |

| 絶縁      | 無              | 無      | 有   |  |

Figure 25. "2ch"ゲートドライバ IC を用いた回路図例

また、ゲートドライバ ICの絶縁方式はフォトカプラ方式、磁気方式、容量方式の3種類あります。

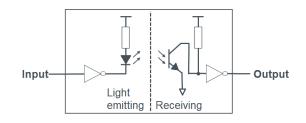

✓ フォトカプラ方式:発光素子(Light emitting)と受光素子 (Receiving)で構成されており、フォトカプラに入力された電流 信号は、内部素子により光信号に変換され、発光側から受光 側に信号を伝送することができます。(Figure 26)

Figure 26. フォトカプラ絶縁

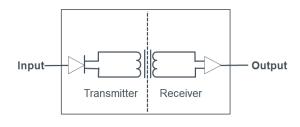

✓ 磁気方式:入力側と出力側にコイルを用い、絶縁されたコイル間で信号を受け渡す方式です。(Figure 27)

Figure 27. 磁気方式絶縁

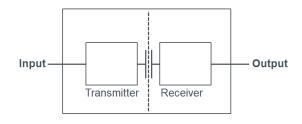

✓ 容量方式: SiO₂ キャパシタを用い、入力側(Transmitter)と 出力側(Receiver)の絶縁を実現しており、絶縁されたコンデン サ間で AC 信号を受け渡しする方式です。 (Figure 28)

Figure 28. 容量方式絶縁

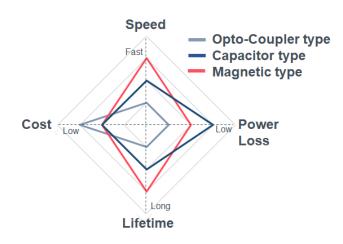

Figure 29 のようにフォトカプラ方式は安価であるものの、LEDや封

止樹脂の経年劣化により磁気方式や容量方式と比較すると寿命が 短く、通信速度が遅いデメリットがあります。磁気方式、容量方式はデ ジタルアイソレータと呼ばれ、オンチップで作成できるために高集積であ り長寿命です。製品設計においては特に高信頼性、長寿命が重要 視され、近年では磁気方式や容量方式が多く採用されています。

また、絶縁ゲートドライバを選定する要素の一つとしてコモンモード過 渡耐性(CMTI)を考慮する必要があります。これは、スイッチング時に ゲートドライバ ICの入出力間に大きな dV/dt が発生する場合でも安 定した動作ができる指標です。SiC MOSFET を駆動する場合、スイッ チング時のドレイン-ソース間電圧の dV/dt は 40~90V/ns の速さと なります。フォトカプラ方式では CMTI が 50V/ns に対し、磁気方式、 容量方式は 100V/ns であるため、SiC MOSFET などを実装する、 高速スイッチングを想定したアプリケーションでは磁気方式又は容量方 式の選択を推奨します。本アプリケーションノートでは磁気方式で、絶 縁タイプ、1ch 出力 ROHM 製ゲートドライバ IC(BM61S41RFV)を 選択しています。

Figure 29. ゲートドライバ IC の絶縁方式の特性比較

#### 4.2 ゲート駆動電圧の決定

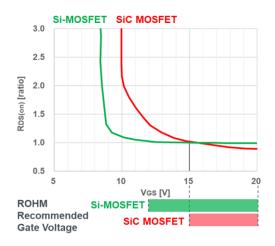

SiC MOSFET のゲート駆動電圧を設定する際はデータシートに記 載されている推奨駆動電圧を参考にしてください。推奨ゲート駆動電 圧はデバイスの構造や材質によって異なります。一般的に SiC MOSFET のゲート駆動電圧は 15V~20V なので、Si-MOSFET か ら SiC MOSFET への置き換えの際は注意が必要です。

Figure 30 に ROHM の第 4 世代 SiC MOSFET と Si-MOSFET のゲート-ソース間電圧  $V_{GS}=15V$  の時のオン抵抗を 1 としたグラフを 示します。グラフから分かるように、Si-MOSFET のゲート-ソース間電 圧は 10~15V 間であればオン抵抗はほぼ変わりません。しかし、SiC MOSFET は 15V 以下で駆動すると急激にオン抵抗が増加してしま います。よって、ROHM の第 4 世代 SiC MOSFET の駆動の際は、 十分に低いオン抵抗を得るためにゲート-ソース間電圧を 15V 以上で 駆動することが推奨されます。

また、ゲート駆動電圧はゲート-ソース間電圧の絶対最大定格を超

えないように注意する必要があります。印加されたゲート電圧が絶対 最大定格以下に保たれていても、ゲートのインダクタンスと容量によりリ ンギング電圧が発生し、これが酸化膜層の破壊につながる電圧に達す る事があります。

Figure 30. VGS とオン抵抗の関係

#### 4.3 ゲートドライバの駆動電流能力の検討

ゲート駆動回路設計を進め、使用するスイッチングデバイス、ゲート 抵抗、ゲート駆動電圧が決定すると、それらの定数で実際に所望の 時間でターンオン/ターンオフできる駆動能力になっているか検討する 必要があります。

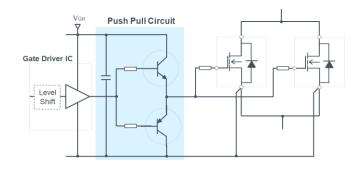

大電流のモジュールやデバイスを並列に接続した場合、入力容量 C<sub>iss</sub> が増加し、スイッチング時間が増加してしまうため、Figure 31 の ように NPN バイポーラトランジスタと PNP バイポーラトランジスタを組み 合わせてプッシュプル回路を設計します。プッシュプル回路ではゲートド ライバ ICがターンオン時は NPN バイポーラトランジスタがオンになり  $V_{GH}$ から電流が供給され、ターンオフ時は PNP バイポーラトランジスタを介 して電流をシンクします。このように、ゲートドライバ IC の駆動電流能 力が不十分な場合は、十分な電流供給能力のある電源から補いま

Figure 31. プッシュプル回路

#### 4.4 ゲート駆動回路の消費電力

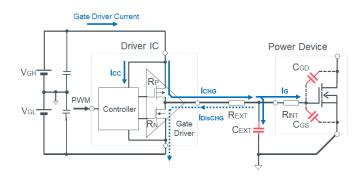

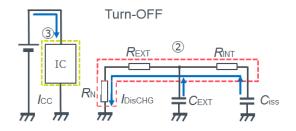

ゲート駆動回路で消費する電力について説明します。Figure 32 にゲートドライバ IC を用いたゲート駆動回路例を示します。

Figure 32. ゲート駆動回路例

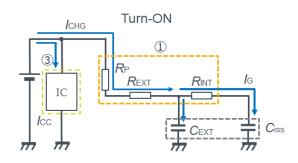

ゲートをターンオンするためには、入力容量  $C_{iss}(C_{GS}+C_{GD})$ や、ゲート-ソース間のコンデンサ( $C_{EXT}$ )に充電する必要があります。また、ターンオフするには、充電された電荷を放電する必要があります。充電する電流( $I_{CHG}$ )、放電する電流( $I_{DisCHG}$ )、ゲートドライバ IC の消費電流( $I_{CC}$ )として、Figure 33 に Figure 32 のターンオン/ターンオフ時の等価回路を示します。

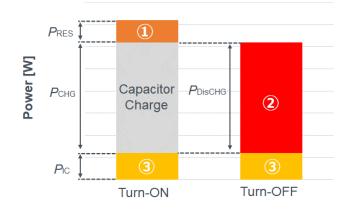

ゲート駆動回路の消費電力  $P_{GDR}$  はターンオンの際、容量成分へ充電する過程で  $R_P$ 、 $R_{EXT}$ 、 $R_{INT}$  において発生する損失  $P_{RES}$ (①)、ターンオフ時に容量成分が放電する際に  $R_{INT}$ 、 $R_{EXT}$ 、 $R_N$  において発生する消費電力  $P_{DisCHG}$ (②)、ゲートドライバ IC で消費される電力  $P_{IC}$ (③)の総和なので、式(2)で表すことができます。

$$P_{\rm GDR} = P_{\rm RES} + P_{\rm DisCHG} + P_{\rm IC} \cdots (2)$$

Figure 34 に消費電力の内訳を示します。P<sub>CHG</sub>で発生する損失は、容量成分に蓄えられるエネルギーと等しいことが分かります。

Figure 33. ゲート駆動回路ターンオン/ターンオフ等価回路

Figure 34. ゲート駆動回路の消費電力内訳

容量成分に充電される時に抵抗に消費される電力  $P_{RES}$  は式(3)に なります。

$$P_{\text{RES}} = I_{\text{CHG}}^2 \times (R_{\text{P}} + R_{\text{EXT}}) + I_{\text{G}}^2 \times R_{\text{INT}} \cdots (3)$$

ターンオン時に容量成分に充電されるエネルギーは式(4)になります。

$$P_{\text{CHG}} = \frac{1}{2} \times \left( Q_g \times V_{\text{G}} + C_{\text{EXT}} \times V_{\text{G}}^2 \right) \times f_{\text{SW}} \cdots (4)$$

Qg ゲート総電荷量

V<sub>GH</sub> ターンオンゲート電圧

V<sub>GL</sub> ターンオフゲート電圧

ターンオン/ターンオフ電圧  $V_G$ は式(5)になります。

$$V_{\rm G} = V_{\rm GH} + |V_{\rm GL}| \cdots (5)$$

P<sub>DisCHG</sub>は、ターンオン時に充電した電力 P<sub>CHG</sub>をターンオフ時に消費するため、式(6)が成り立ちます。

$P_{\text{DisCHG}} = P_{\text{CHG}} \cdots (6)$

ゲートドライバから充電される平均電流 I<sub>CHG</sub> は、式(7)となります。

$$I_{\text{CHG}} = \frac{P_{\text{CHG}}}{V_{\text{G}}} = \frac{1}{2} \times (Q_g + C_{\text{EXT}} \times V_{\text{G}}) \times f_{\text{SW}} \cdots (7)$$

また、デバイスのゲートに充電される平均電流  $I_G$  は、式(8)になります。

$$I_{\rm G} = \frac{1}{2} \times Q_g \times f_{\rm SW} \cdots (8)$$

ゲートドライバ IC へ供給される電流を  $I_{CC}$  とすると  $P_{IC}$  は式(9)になります。

$$P_{\rm IC} = V_{\rm G} \times I_{\rm CC} \cdots (9)$$

#### 4.5 ゲート駆動回路のピーク電流

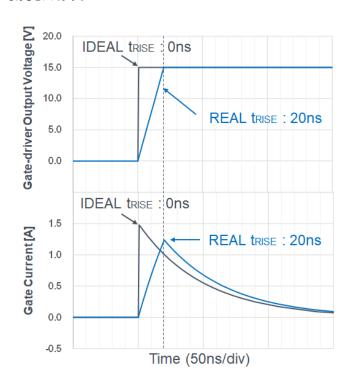

ゲート駆動回路のピーク電流  $I_{CHG\_PEAK}$  は、ゲートドライバが瞬時 に理想的にターンオンすると式(10)になります。

$$I_{\text{CHG\_PEAK}} = \frac{V_{\text{G}}}{R_{\text{P}} + R_{\text{EXT}} + R_{\text{INT}}} \cdots (10)$$

実際には、ゲートドライバにもターンオン時間が発生します。Figure 35 は、ゲート電源  $V_G$ が 15V で、全てのゲート抵抗が  $10\Omega$ の条件の ゲート電流のシミュレーション結果になります。ゲートドライバが瞬時  $(t_{RISE}=0ns)$  にターンオンした場合 (IDEAL) と、遅延が発生  $(t_{RISE}=20ns)$  した場合 (REAL)のゲート電流の波形を示します。理想的 (IDEAL) にターンオンした場合は、式(9)が成り立ちますが、遅延が発生 (REAL) した場合は、ピーク電流が低くなります。ピーク電流を正確に算出することは難しいですが、式(9)がピーク電流の最大値であるといえます。

Figure 35. ターンオン時間とゲート電流の関係

#### 4.6 ゲートドライブ IC の消費電力

ゲートドライバ IC の消費電力  $P_{DRV}$  は、ゲートドライバ IC のドライブ段の電源側のオン抵抗を  $R_p$ 、GND 側のオン抵抗を  $R_N$  とすると式(11)になります。

$$P_{\text{DRV}} = I_{\text{CHG}}^2 \times R_{\text{P}} \times Duty + I_{\text{CHG}}^2 \times R_{\text{N}} \times (1 - Duty)$$

$$+I_{\text{CC}} \times V_{\text{G}} \cdots (11)$$

#### 4.7 ゲート抵抗の選定

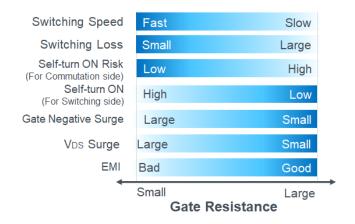

ゲート抵抗の値を決定する場合は、様々な要因から最適値を選択します。Figure 36 にゲート抵抗の大小における回路への影響を示します。

Figure 36. ゲート抵抗が回路に与える影響

ゲート抵抗の値を小さくすると、スイッチング速度の高速化により電力損失を減らすことができますが、サージ電圧の増加や EMI などのリスクが発生するため、適切なゲート抵抗に調整する必要があります。

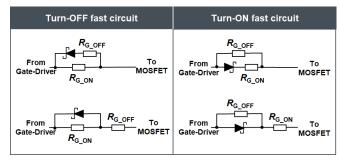

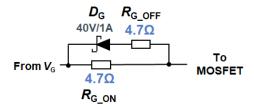

また Figure 37 のようにダイオードを用いることでターンオンとターンオフ時で異なる大きさのゲート抵抗を使うように設計することができます。 V<sub>DS</sub> サージに余裕がある場合はターンオフが速くなるようにターンオフ時のゲート抵抗の値を小さくすることができます。 しかし、 回路が複雑になることから、 信頼性や故障時のアクシデントも含めて、安全設計やフェールセーフ性も考慮して設計してください。

Figure 37. ダイオードを用いたゲート抵抗の実装例

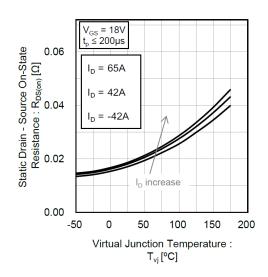

ゲート抵抗の変化でスイッチング速度が変化すると、スイッチング損失に影響します。V<sub>DS</sub> サージ対策に大きすぎるゲート抵抗を使用するとターンオン、ターンオフのスイッチング速度が低下し、スイッチング損失が増加します。損失は熱になり、デバイスの温度が増加すると Figure 38のようにドレイン-ソース間のオン抵抗も上昇します。そこから損失が増え、またオン抵抗も上昇していくサイクルに陥り、破壊につながる恐れがあります。そのため、損失にも注意しつつ最適なゲート抵抗の値を選定する必要があります。

Figure 38. ROHM SiC MOSFET のオン抵抗と温度の関係

#### 4.8 保護回路の設計

アプリケーションノート「ゲート-ソース電圧のサージ抑制方法」\*2 で詳しく説明していますが、SiC MOSFET を使用するアプリケーションではスイッチング時の電圧や電流の変化が、デバイス自身のパッケージインダクタンスや周辺回路の配線インダクタンスの影響を無視できないほど高速動作をしています。特にゲート-ソース間電圧には予期せぬ正あるいは負のサージが発生するなど、様々な問題が発生します。Figure 39 にゲート-ソース間のサージや、トラブル回避のための保護回路例を示します。

Figure 39. 保護回路設計例

## ゲート-ソース間容量(C<sub>EXT</sub>)

SiC MOSFET のスイッチング周波数が高く、スイッチング速度が速い場合、ゲート-ドレイン間容量  $C_{GD}$  に流れる電流は、ゲート-ソース間容量  $C_{GS}$ にすべて流れていると仮定すると、MOSFET のゲート-ソース間電圧  $V_{GS}$  は式(12)のようにゲート-ドレイン間容量  $C_{GD}$  とゲート-ソース間容量  $C_{GS}$  の分圧となります。

$$V_{\rm GS} \approx \frac{c_{\rm GD}}{c_{\rm GS} + c_{\rm GD}} V_{\rm DS} \cdots (12)$$

この時、ゲート-ソース間に Figure 39 のように容量  $C_{\text{EXT}}$ を追加すると、ゲート-ソース間電圧  $V_{\text{GS}}$ は式(13)になります。

$$V_{\rm GS} \approx \frac{c_{\rm GD}}{c_{\rm EXT} + c_{\rm GS} + c_{\rm GD}} V_{\rm DS} \cdots (13)$$

よって、ゲートソース間電圧  $V_{GS}$  を小さくすることができ、セルフターンオンのリスクを抑えることができます。しかし、 $C_{EXT}$  が大きいと損失も増加するので、適切な容量の選定が必要です。

#### ② 正サージクランプダイオード(D1)

$V_{\text{GH}}$ -ゲート間にダイオード D1 を実装することで電圧が  $V_{\text{GH}}$ でクランプされ、正サージが抑えられます。また、D1 は数十 ns のパルスを吸収し、できるだけ低電圧でクランプする必要があるためショットキーバリアダイオード(SBD)の使用を推奨します。

## ③ 負サージクランプダイオード(D2)

ゲート-*V*<sub>GL</sub> 間のダイオード(D2)により、負側のサージが発生した際は *V*<sub>GL</sub> にクランプされます。D2 も、D1 と同様ショットキーバリアダイオード(SBD)の使用を推奨します。

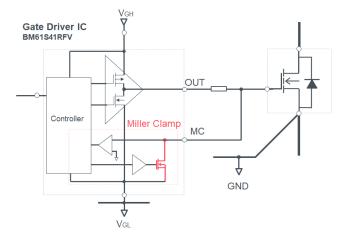

## ④ ミラークランプ(MC)回路(Q1)

デバイスがターンオフ状態でミラークランプ用 MOSFET をターンオンすることで VGsを 0V に接続し、ゲート電位の持ちあがりを抑制します。 (Figure 40)ミラークランプ回路を備えるためには、ミラークランプ用 MOSFET を駆動するための制御信号が必要となります。制御信号はターンオフ時に VGs をモニタリングしながら駆動タイミングを見出す必要があり、一般的にはゲートドライバ IC に備わっていることが多いです。本アプリケーションノートで選定したゲートドライバ IC (BM61S41RFV-C)は、ミラークランプ回路内蔵型 IC となります。

Figure 40. ミラークランプ回路内蔵型 IC の回路例

#### ⑤ 低電圧検出回路(UVLO)

ゲート駆動回路の電源電圧(V<sub>GH</sub>)が十分に電圧上昇していない 状態で、MOSFET をオンするとオン抵抗が高く、発熱や破壊につなが る場合があります。電源電圧をモニタし、低電圧を検出すると、ゲート をオンしない制御回路が搭載されているゲートドライバ IC があります。 本アプリケーションノートで例として挙げているゲートドライバ IC(BM61S41RFV)は UVLO 機能が実装されています。

#### ⑥ ゲート-ソース間抵抗(R1)

ゲート電源がオフの時にゲート電位を固定するためにゲート-ソース間に抵抗を接続します。

## 5.ゲート駆動回路の設計例

## 5.1 ROHM SiC MOSFET SCT4018KR

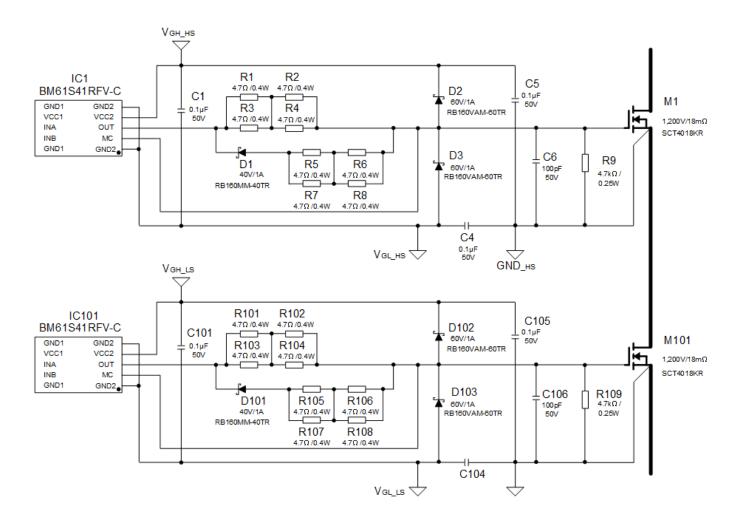

ゲート駆動回路の設計条件は以下になります。ゲートドライバ IC は、ミラークランプ機能付き 1ch 絶縁タイプで SiC MOS を高速駆動するのに適している ROHM の BM61S41RFV-C を使用します。

ゲート電圧は、ターンオン電圧( $V_{GH}$ )を 18V、ターンオフ電圧( $V_{GL}$ )を 0V とします。ゲート抵抗( $R_{\text{EXT}}$ )は、仮に 4.7 $\Omega$ とします。

Circuit Design

- VGH=18V

- V<sub>GL</sub>=0V

- CEXT=100pF

- fsw=50kHz

Power Device (SiC MOSFET: SCT4018KR)

- Ciss=4.5nF

- RINT=1Ω

Gate Driver IC (BM61S41RFV-C)

- ICC=0.7mA

- RP=0.67Ω typ.

- R<sub>P</sub>=0.30Ω min.

- R<sub>N</sub>=0.45Ω typ.

- RN=0.45Ω typ.

RN=0.15Ω min.

充放電されるゲート電圧  $V_G$ は、式(5)から計算します。

$$V_{\rm G} = V_{\rm GH} + |V_{\rm GL}| = 18 + |0| = 18[V]$$

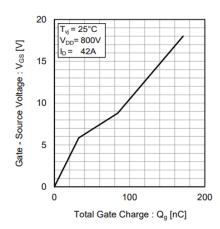

ゲート駆動範囲での Total Gate Charge( $Q_g$ )は、Figure 41 から +18V の  $Q_g$ は 170nC と読み取ることができます。

$$Q_g = +Q_g + |-Q_g| = 170n + 0 = 170n [C]$$

Figure 41. ROHM SiC MOSFET SCT4018KR  $Q_g$  vs.  $V_{\rm GS}$

スイッチング時に容量成分に充電される電力  $P_{CHG}$  は式(4)から算出します。

$$P_{\text{CHG}} = \frac{1}{2} \times (Q_g \times V_G + C_{\text{EXT}} \times {V_G}^2) \times f_{\text{SW}}$$

= 0.5 \times (170n \times 18 + 100p \times 18^2) \times 50k

= 77 [mW]

ターンオフ時に容量成分から放電されるエネルギーによる消費電力 PDisCHG は式(4)から、

$$P_{\text{DisCHG}} = P_{\text{CHG}} = 77 \ [mW]$$

ゲートに充電される平均電流 ICHG は式(7)から以下の値になります。

$$I_{\text{CHG}} = \frac{P_{\text{CHG}}}{V_{\text{G}}} = \frac{1}{2} \times (Q_g + C_{\text{EXT}} \times V_{\text{G}}) \times f_{\text{SW}}$$

$$= 0.5 \times (170n + 100p \times 18) \times 50k$$

$$= 4.3 \text{ [mA]}$$

デバイスのゲートに充電される平均電流  $I_G$  は、式(8)から以下の値になります。

$$I_{\rm G} = \frac{1}{2} \times Q_g \times f_{\rm SW} = \frac{1}{2} \times 170n \times 50k = 4.3 \ [mA]$$

実際にデバイスを動作させてみて、Figure 36 に示すゲート抵抗の要因から最適なゲート抵抗を検討します。 $V_{DS}$  のサージ波形を確認します。Figure 42 にゲート抵抗  $R_{EXT}$  と  $V_{DS}$  サージの特性を示します。Figure 42 のターンオンのグラフの  $V_{DS}$  サージは還流側のサージ、ターンオフのグラフは駆動側の  $V_{DS}$  サージです。Figure 43 にゲート抵抗  $R_{EXT}$  とスイッチング損失の特性を示します。

Figure 42.  $R_{\rm EXT}$  vs.  $V_{\rm DS}$  Surge Voltage

Figure 43. R<sub>EXT</sub> vs. Switching Loss

絶対最大定格 1,200V に対し、ディレーティング 80%とすると、ゲート抵抗の値を調整し  $V_{DS}$  サージを 960V 以下に抑える必要があります。ゲート抵抗が小さい時、スイッチング損失は小さくなりますが、 $V_{DS}$  サージを 960V 以下にするためには、ターンオン時約 4 $\Omega$ 以上、ターンオフ時約 2 $\Omega$ 以上のゲート抵抗を選択する必要があります。

ターンオフ時のゲート抵抗が小さいため、Figure 44 の回路図で、4.7  $\Omega$ の抵抗を選択しています。

Figure 44. 選択したゲート抵抗

ターンオンで容量成分が充電される際に抵抗で発生する消費電力  $P_{\text{RES}}$  は式(3)から以下の値になります。

$$P_{\text{RES}} = I_{\text{CHG}}^2 \times (R_{\text{P}} + R_{\text{EXT}}) + I_{\text{G}}^2 \times R_{\text{INT}}$$

$$= (4.3m)^2 \times (0.67 + 4.7) + (4.3m)^2 \times 1$$

$$= 0.117 [mW]$$

ゲートドライバ IC の消費電力は式(8)から

$$P_{IC} = V_{G} \times I_{CC}$$

$$= 18 \times 0.7m$$

= 12.6 [mW]

ゲート駆動回路の消費電力  $P_{GDR}$  は式(2)から以下の結果となります。

$$P_{\text{GDR}} = P_{\text{RES}} + P_{\text{DisCHG}} + P_{\text{IC}}$$

=  $0.117m + 77m + 12.6m$

=  $90 \ [mW]$

ゲート駆動回路のピーク電流  $I_{CHG\_PEAK}$  は、式(10)から計算します。 ゲートドライバ IC のデータシートから、ゲートドライバ IC の充電側トラ ンジスタの出力抵抗  $R_P$ の Min 値は  $0.3\Omega$ 、放電側トランジスタの出 力抵抗  $R_N$ の Min 値は  $0.15\Omega$ であるため、最大のピーク電流は、放 電時で計算します。

$$I_{\text{CHG\_PEAK}} = \frac{V_{\text{G}}}{R_N + R_{\text{G\_EXT}} + R_{\text{G\_INT}}}$$

$$= \frac{18}{0.15 + \frac{4.7}{2} + 1} = 5.14 [A]$$

放電時間 t<sub>DisCHG</sub>は、時定数の式から計算します。

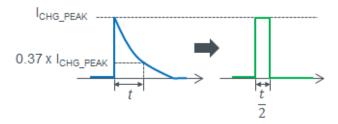

$$t_{\rm DisCHG} = \frac{Q_g + C_{\rm EXT} \times V_{\rm G}}{I_{\rm CHG\_PEAK}} = \frac{170n + 100p \times 18}{5.14} = 33.4[ns]$$

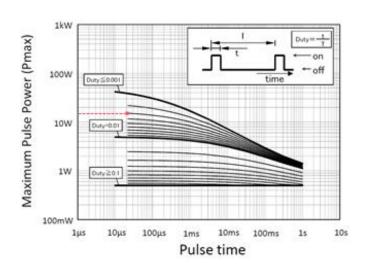

Figure 45 のように時定数をもつ矩形波をパルス換算すると、ピーク

電流 5.14A、パルス時間(t/2)16.2ns で計算します。

Figure 45. 時定数をもつ矩形波のパルス換算

$$Duty = t \times f_{SW} \times 2 = 33.4n \times 50k \times 2 = 0.0033$$

Figure 46 から抵抗器の連続パルス限界電力は、概算で 13W と読みとりました。

Figure 46. 連続パルス限界電力

抵抗器のパルス定格電圧は以下の式から計算します。

$$V_{\text{R MAX}} = \sqrt{P_{\text{max}} \times R} = \sqrt{13 \times 4.7} = 7.81 \text{ [V]}$$

ゲート抵抗に発生するピーク電圧  $V_{R\_PEAK}$  は以下になります。

$$V_{\text{R_PEAK}} = \frac{I_{\text{CHG_PEAK}}}{2} \times R = \frac{5.14}{2} \times 4.7 = 12.09 [V]$$

パルス定格電圧  $V_{R\_MAX}$ =7.81V を超えてしまっているので、ゲート抵抗を  $4.7\Omega$ の 2 直列 2 並列にすることにします。  $V_{R\_MAX}$ と  $V_{R\_PEAK}$ は以下のように計算されます。

$$V_{\text{R\_PEAK}} = \frac{I_{\text{CHG\_PEAK}}}{4} \times R = \frac{5.14}{4} \times 4.7 = 6.04 [V]$$

パルス定格電圧  $V_R$  MAX=7.81V を下回ることができました。

ゲート駆動回路の消費電力は、90mW となり、ゲート駆動回路の電源は、90 mW 以上の定格電力で、最大 5.14 A/33 ns 幅の急峻負荷変動に影響のない電源設計が必要になります。

ゲートドライバ IC の消費電力  $P_{\mathsf{DRV}}$ は、 $\mathsf{Duty}50\%$ とすると式(11)から以下の値となります。

$$P_{DRV} = I_{CHG}^{2} \times R_{P} \times Duty + I_{CHG}^{2} \times R_{N} \times (1 - Duty)$$

$$+I_{CC} \times V_{G}$$

$$= (4.3m)^{2} \times 0.67 \times 0.5 + (4.3m)^{2} \times 0.45 \times (1 - 0.5)$$

$$+ 0.7m \times 18$$

= 12 [mW]

パッケージパワー $P_d$ は熱抵抗 180°C/W より、 $P_d$ =694mW であるため、ゲートドライバ IC の発熱は問題ないことが確認できました。 ゲート抵抗( $R_{\text{EXT}}$ )の消費電力  $P_{R_{\text{EXT}}}$ は、

$$P_{\text{R\_EXT}} = I_{\text{CHG}}^2 \times R_{\text{EXT}} = (8.6m)^2 \times 4.7$$

= 0.325 [mW]

ROHM 耐サージ抵抗: ESR10 を選択した場合、定格電力は250mW であり、平均電力は問題ありません。但し、パルス電力により実際にはパルス電力により瞬間的な発熱が蓄積されているので、熱測定評価を実施し判断してください。

Figure 44 のターンオフ用ダイオード( $D_G$ )は、40V/1A 品を選定しています。

Figure 47 に設計例で検討した ROHM SiC MOSFET SCT4018KR 実装時のゲート駆動回路図の例を示します。

Figure 47. SCT4018KR ゲート回路図例

## 6.まとめ

SiC MOSFET への置き換えなどによりスイッチングが高速になり、ドレイン-ソース電圧のサージやセルフターンオンなどのトラブルが発生するリスクが高まっています。ゲート駆動回路の設計を十分に検討することでトラブルを回避し、SiC MOSFET の能力を最大限引き出すことにつながります。

このアプリケーションノートで紹介したゲート駆動回路のデザインガイドラインや保護回路の設計例が、ゲート駆動回路設計の一助になることを期待しています。

#### 参考資料

\*1「ブリッジ構成におけるゲート-ソース電圧の振る舞い」

アプリケーションノート (No. 60AN134J Rev.002)

□-ム株式会社,2020年4月

\*2「ゲート-ソース電圧のサージ抑制方法」

アプリケーションノート (No. 62AN009J Rev.002)

□-ム株式会社,2020年4月

## ご 注 意

- 1) 本資料に記載されている内容は、ロームグループ(以下「ローム」という)製品のご紹介を目的としています。ローム製品のご使用にあたりましては、別途最新のデータシートもしくは仕様書を必ずご確認ください。

- 2) ローム製品は、一般的な電子機器(AV機器、OA機器、通信機器、家電製品、アミューズメント機器等)もしくはデータシートに明示した用途への使用を意図して設計・製造されています。したがいまして、極めて高度な信頼性が要求され、その故障や誤動作が人の生命、身体への危険もしくは損害、またはその他の重大な損害の発生に関わるような機器または装置(医療機器、輸送機器、交通機器、航空宇宙機器、原子力制御装置、燃料制御、カーアクセサリーを含む車載機器、各種安全装置等)(以下「特定用途」という)にローム製品のご使用を検討される際は事前にローム営業窓口までご相談くださいますようお願いいたします。ロームの文書による事前の承諾を得ることなく、特定用途にローム製品を使用したことによりお客様または第三者に生じた損害等に関し、ロームは一切その責任を負いません。

- 3) 半導体を含む電子部品は、一定の確率で誤動作や故障が生じる場合があります。万が一、誤動作や故障が生じた場合であっても、人の生命、身体、財産への危険または損害が生じないように、お客様の責任においてフェールセーフ設計など安全対策をお願いいたします。

- 4) 本資料に記載された応用回路例やその定数などの情報は、ローム製品の標準的な動作や使い方を説明するためのもので、実際に使用する機器での動作を明示的にも黙示的にも保証するものではありません。したがいまして、お客様の機器の設計において、回路やその定数及びこれらに関連する情報を使用する場合には、外部諸条件を考慮し、お客様の判断と責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、ロームは一切その責任を負いません。

- 5) ローム製品及び本資料に記載の技術を輸出または国外へ提供する際には、「外国為替及び外国貿易法」、「米国輸出管理規則」など適用される輸出関連法令を遵守し、それらの定めにしたがって必要な手続きを行ってください。

- 6) 本資料に記載された応用回路例などの技術情報及び諸データは、あくまでも一例を示すものであり、これらに関する第 三者の知的財産権及びその他の権利について権利侵害がないことを保証するものではありません。また、ロームは、本 資料に記載された情報について、ロームもしくは第三者が所有または管理している知的財産権その他の権利の実施、 使用または利用を、明示的にも黙示的にも、お客様に許諾するものではありません。

- 7) 本資料の全部または一部をロームの文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 8) 本資料に記載の内容は、本資料発行時点のものであり、予告なく変更することがあります。ローム製品のご購入及びご使用に際しては、事前にローム営業窓口で最新の情報をご確認ください。

- 9) ロームは本資料に記載されている情報に誤りがないことを保証するものではありません。万が一、本資料に記載された情報の誤りによりお客様または第三者に損害が生じた場合においても、ロームは一切その責任を負いません。

ローム製品のご検討ありがとうございます。 より詳しい資料やカタログなどご用意しておりますので、お問い合わせください。

## ROHM Customer Support System

https://www.rohm.co.jp/contactus