# 第4世代 SiC MOSFET ハーフブリッジ評価ボード 取扱説明書

# <高電圧に関するご注意事項>

◇操作を始められる前に!

このドキュメントは、SiC MOSFET 用評価ボード(P04SCT4018KE-EVK-001, **P05SCT4018KR-EVK-001**)の取り扱い方に限定し記載しています。

回路図、BOM、レイアウト等の詳細な内容については、製品仕様書を参照してください。

# 安全に操作を行って頂く為に、評価ボードをご使用になる前に 必ずこのドキュメントの全文を読んでください!

また、使用される電圧およびボードの構造によっては、

生命に危険をおよぼす電圧が発生する場合があります。

必ず下記囲み内の注意事項を厳守してください。

### <使用前に>

- **(1**) ボードの落下などによる部品の破損、欠落がない事を確認してください。

- 導電性の物体がボードトに落ちていない状態である事を確認してください。

- モジュールと評価ボードのはんだ付けを行う際は、はんだ飛散に注意してください。

- 基板に、結露や水滴がない事を確認してください。

#### <通電中>

- 導電性の物体がボードに接触しないよう注意してください。

- 動作中は、偶発的な短時間の接触、もしくは手を近づけた場合の放電であっても、重篤に陥る 場合や牛命に関わる危険性があります。

絶対にボードに素手で触れたり、近づけ過ぎたりしないでください。

また、ピンセットやドライバなど導電性の器具を用いての作業も上記同様に注意してください。

- 定格以上の電圧が印加された場合、短絡など仕様状況によっては部品の破裂等も考えられます。部品の飛散 などによる危険についても考慮して下さい。

- 動作時は、熱等によるボード・部品の変色や液漏れ等、及び低温評価による結露に注意しながら作業を進めて ください。

#### <使用後>

- 評価ボードには、高電圧を蓄える回路が含まれる場合があります。接続している電源回路を切断しても電荷を 蓄えているため、ご使用後には必ず放電し、放電したことを確認してから取り扱うようにして下さい。

- 過熱された部品への接触による火傷等に注意してください。

この評価ボードは、研究開発施設で使用されるもので、**各施設において高電圧を取り扱う事を許可さ** れた方だけが使用出来ます。また、高電圧を使用しての作業時には、「高電圧作業中」等の明示を行 い、インターロック等を備えたカバーや保護メガネの着用等、安全な環境において作業される事を推奨し ます。なお、本文冒頭に本ボードの短絡保護に関する注意書きがありますので、併せてお読み下さい。

SiC MOSFET 評価ボード

# 第4世代 SiC MOSFET 評価ボード 取扱説明書

本ユーザガイドは、第4世代 SiC MOSFET を評価するための評価ボードの使い方について解説したものです。

SiC MOSFET は高電圧かつ大電流を扱い、EMC ノイズや電源効率を最適化するための動作条件を決定するために、様々な条件で評価を 行う必要があります。しかしながら、評価環境を適切に構築することは簡単なことではありません。そこで、スイッチング特性を評価するための様々な 条件を簡単に設定できる評価ボードを準備し、SiC MOSFET の評価を効率よく実施できるようにしました。

このユーザガイドでは、TO-247N パッケージ用および TO-247-4L 用評価ボードの取り扱い方について説明しています。製品仕様に関する詳細 な情報は、「第4世代 SiC MOSFET 評価ボード 製品仕様書」を参照して下さい。

本評価ボードには、評価デバイスに対する短絡保護機能がありません。

そのため、通常動作における評価方法であっても、お客様が選定した評価デバイスの電気的仕様(最大電流 等)を逸脱する使い方を行いますと、破裂音を伴ってデバイスの激しい破壊が生じる恐れがありますので、評価 デバイスの仕様を逸脱する使い方は決して行わないで下さい。また、万が一激しい破壊が発生した場合に備え て、破片飛散の防止及び保護具の使用等を実施のうえ、お使い下さい。

#### 1. はじめに

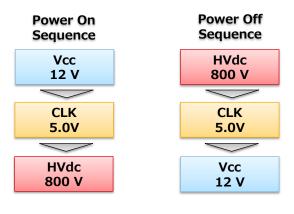

本基板は外部から供給される電圧源や信号源が複数存在するため、下記に定める投入および切断シーケンスを必ず守ることで、破壊等のトラブ ルを回避できます。

Figure 1. On/Off シーケンス

© 2022 ROHM Co., Ltd. No. 63UG059J Rev.001 3/27 2022.2

HVdc: High voltage power supply

CLK: Gate pulse signal

Vcc: Control power supply

また、本基板は「SCT4018KE」もしくは「SCT4018KR」をご使用いただくにあたり、各デバイスに最適なゲート駆動回路をデフォルトとして設計しておりますが、その他の「TO-247N」、「TO-247-4L」パッケージのデバイスを実装して評価することも可能です。その際は、各デバイスの特性に合わせて「4. ゲート駆動電圧の設定方法」「5. ゲート抵抗の設定方法」を参考にゲート駆動回路の定数変更をお願いいたします。

Table.1 に第4世代 SiC MOSFET シリーズの各ラインナップと仕様を示します。

Table 1. 第4世代 SiC MOSFET ラインナップ一覧

| <b>Product Name</b> | VDSS(V) | Ron(Typ.)<br>(mΩ) | I <sub>D</sub><br>(A) | P <sub>D</sub> (W) | Tj(Max)<br>(°C) | Package   |

|---------------------|---------|-------------------|-----------------------|--------------------|-----------------|-----------|

| SCT4045DE           |         | 45                | 34                    | 115                |                 | TO-247N   |

| SCT4026DE           | 750     | 26                | 56                    | 176                |                 | 100       |

| SCT4013DE           |         | 13                | 105                   | 312                |                 | ROHM      |

| SCT4062KE           |         | 62                | 26                    | 115                |                 |           |

| SCT4036KE           | 1200    | 36                | 43                    | 176                |                 |           |

| SCT4018KE           |         | 18                | 81                    | 312                | 175             |           |

| SCT4045DR           |         | 45                | 34                    | 115                | 175             | TO-247-4L |

| SCT4026DR           | 750     | 26                | 56                    | 176                |                 | 0.6       |

| SCT4013DR           |         | 13                | 105                   | 312                |                 | ROHM      |

| SCT4062KR           |         | 62                | 26                    | 115                |                 |           |

| SCT4036KR           | 1200    | 36                | 43                    | 176                |                 |           |

| SCT4018KR           |         | 18                | 81                    | 312                |                 |           |

#### 2. LED 表示

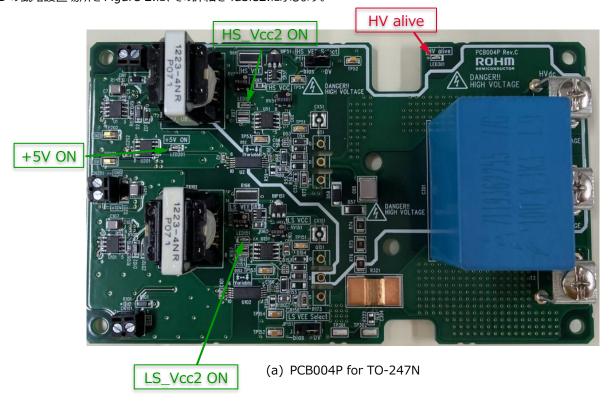

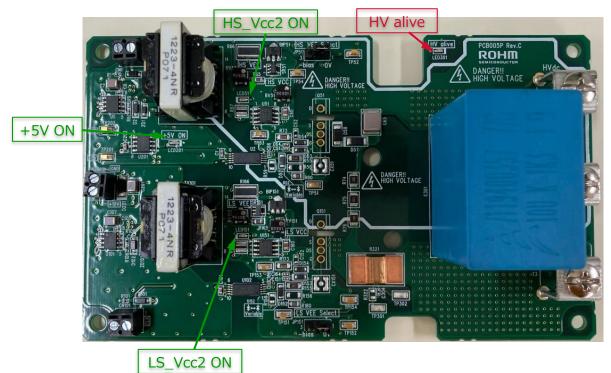

本基板には基板の動作状態を簡単に把握できるように、いくつかの LED が備えられています。 LED の概略設置場所を Figure 2.に、その詳細を Table2.に示します。

(b) PCB005P for TO-247-4L

Figure 2. LED Location

Table 2. LED 点灯とその意味

| シルク表記      | LED   | LED 点灯 | 詳細                                                                         |                 |

|------------|-------|--------|----------------------------------------------------------------------------|-----------------|

| HV alive   | 赤     | 点灯     | 高圧電源 HVdc に 20V 以上の電圧が存在すると点灯する。 高圧電源を切り離していても点灯していることがあるので、点灯時は基板に絶対触れない。 |                 |

|            |       | 消灯     | HVdc の電圧が 20V 以下。                                                          |                 |

| LEV ON     | 緑     | 点灯     | 通常動作時に点灯。点灯時は制御用電源(+12V)が出力されている。                                          |                 |

| +5V_ON     | JN 称  | 形      | 消灯                                                                         | 制御用電源が印加されていない。 |

| HS_Vcc2_ON | ON «= | 点灯     | 通常動作時に点灯。ゲート駆動用絶縁電源が正常に立ち上っている。                                            |                 |

| LS_Vcc2_ON | 緑     | 消灯     | ゲート駆動用絶縁電源が出力されていない。                                                       |                 |

### 3. コネクタ ピンアサイン

コネクタ ピンアサインを figure 3.に示します。

また、各信号および電源端子の定義をtable 3.およびtable 4.に示します。

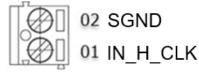

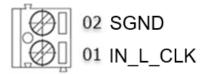

(1) CN1 (HS 側信号入力コネクタ)

(2) CN101 (LS 側信号入力コネクタ)

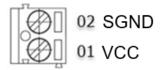

(3) CN201 (制御電源カコネクタ)

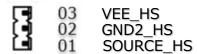

(4) JP51 (HS 側負バイアス/OV 切り替えコネクタ)

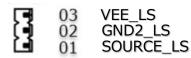

(5) JP151 (LS 側負バイアス/OV 切り替えコネクタ)

Figure 3. コネクタ ピンアサイン(Top view)

Table 3. 電源端子の定義

| 電源端子 | 信号   | 詳細                                                                       |

|------|------|--------------------------------------------------------------------------|

| T1   | HVdc | 高電圧入力端子<br>Buck あるいはインバータ動作時は入力端子となるが、Boost 動作時は出力端子となる。                 |

| T2   | Vsw  | HS 側 MOSFET のパワーソース端子および LS 側 MOSFET のドレイン端子<br>基板内で接続されており、切り離すことはできない。 |

| Т3   | PGND | Power GND 端子<br>入力信号側 SGND と接続されていない。                                    |

Table 4. 信号線の定義

| コネクタ  | ピン<br>No. | 信号        | I/O | 詳細                                                                      |

|-------|-----------|-----------|-----|-------------------------------------------------------------------------|

| CN1   | 01        | IN_H_CLK  | I   | HS 側 MOSFET を ON/OFF する信号。"H"レベルの時オンする。<br>オープン時は 2.2kΩ抵抗でプルダウンされている。   |

|       | 02        | SGND      |     | 入力信号側 GND。 DUT 側 GND とは完全に分離されている。                                      |

| CN101 | 01        | IN_L_CLK  | I   | LS 側 MOSFET を ON/OFF する信号。"H"レベルの時オンする。<br>オープン時は 2.2kΩ抵抗でプルダウンされている。   |

|       | 02        | SGND      |     | 入力信号側 GND。                                                              |

| CN201 | 01        | Vcc       |     | ドライバ IC および内部制御用電源端子。この電源からゲート駆動用電源を内部で生成する。                            |

|       | 02        | SGND      |     | 入力信号側 GND。                                                              |

| JP51  | 01        | SOURCE_HS |     | PCB004P: HS 側 DUT の SOURCE 信号。<br>PCB005P: HS 側 DUT の DRIVER SOURCE 信号。 |

|       | 02        | GND2_HS   |     | HS 側ドライバ IC の GND2 信号。                                                  |

|       | 03        | VEE_HS    |     | HS 側負バイアス電源。                                                            |

| JP151 | 01        | SOURCE_LS |     | PCB004P: LS 側 DUT の SOURCE 信号。<br>PCB005P: LS 側 DUT の DRIVER SOURCE 信号。 |

|       | 02        | GND2_LS   |     | LS 側ドライバ IC の GND2 信号。                                                  |

|       | 03        | VEE_LS    |     | LS 側負バイアス電源。                                                            |

#### 4. ゲート駆動電圧の設定方法

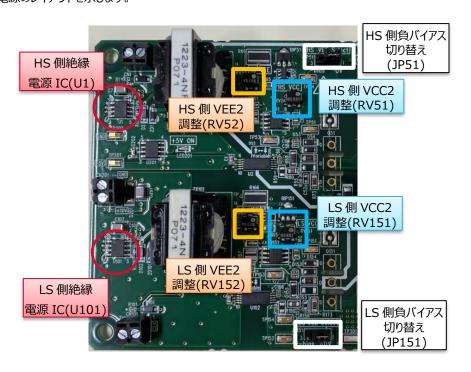

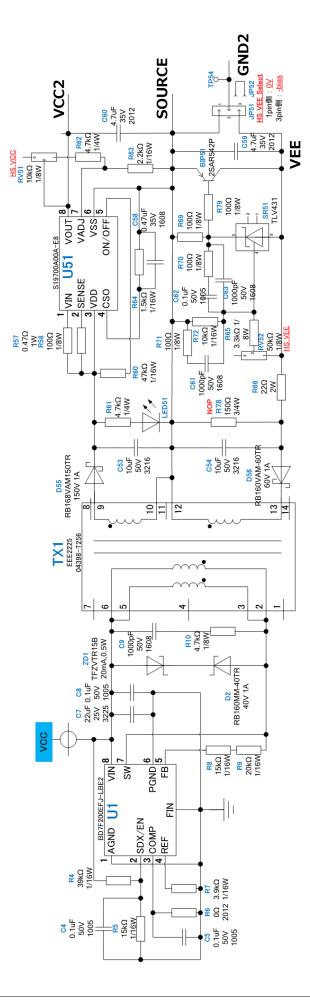

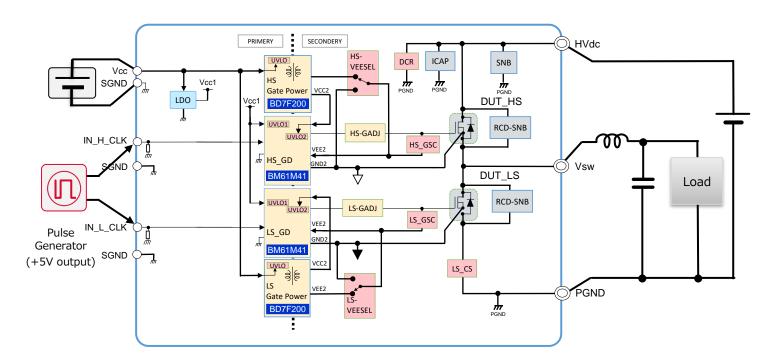

ゲート駆動電圧はオンボード実装されている絶縁型フライバック電源で供給されています。このフライバック電源はローム製フォトカプラレス制御 IC (BD7F200EFJ) を使用しており、HS 側および LS 側それぞれに正負駆動電圧を出力するトランスを備えています。 Figure 4. にオンボード電源のレイアウトを示します。

Figure 4. ゲート電源の構成 (Top View of PCB004P)

## **4.1 正バイアス(VCC2)の調整方法**

絶縁型フライバック電源のトランス(TX1, TX101)出力は正電圧と負電圧が存在します。MOSFET の駆動電圧(正バイアス)となる VCC2 は、そのトランスの正出力から LDO を通して生成されており、LDO の出力電圧を可変抵抗 RV51,RV151 により調整することができます。 可変抵抗を時計間回りに回転させると出力電圧は高くなります。

# **4.2 負バイアス(VEE2)の調整方法**

MOSFET のオフ時のバイアス電圧となる負バイアス VEE2 は、トランス TX1,TX101 の負出力からシャントレギュレータ SR1,SR101 (TI 製 TIV431) と可変抵抗 RV52,RV152 により調整され、可変抵抗を回転させることで-4.5V~-2V の範囲において設定することができます。 VEE2 は負バイアス切り替え端子 JP51,JP151 を経由して供給され、ゼロバイアスと VEE2 バイアスを選択します。その設定方法を Table 5.に 示します。

コネクタ ピン No. 信号 設定方法 JP51 01 **SOURCE** 1-2 ピン接続: 0V バイアス設定 JP151 DRIVER SOURCE 02 GND2 2-3 ピン接続: 負バイアス設定 03 VEE

Table 5. 負バイアス (VEE2) の設定方法

Figure 5. ゲート駆動電源回路(HS側)

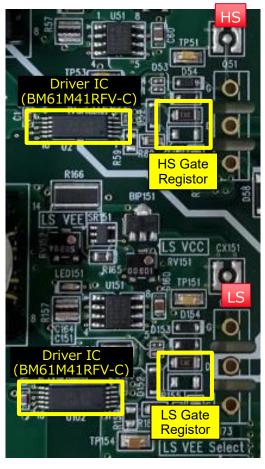

# 5. ゲート抵抗の設定方法

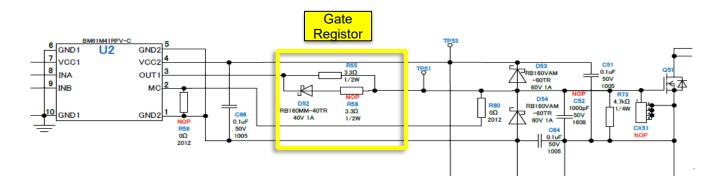

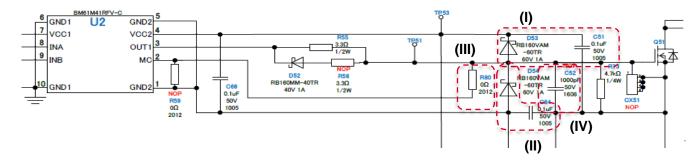

MOSFET のスイッチング速度を調整するゲート抵抗を備えており、ターンオフ側を低く設定するためのダイオード(D52,D152)が接続されて おり、ターンオンとターンオフのスイッチング速度を個別に調整することができます。

ターンオン: HS側 R55

LS 側 R155

ターンオフ: HS 側 R56, D52

LS 側 R156,D152

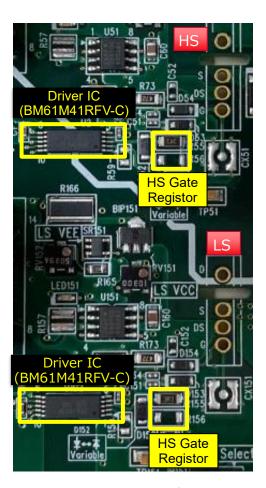

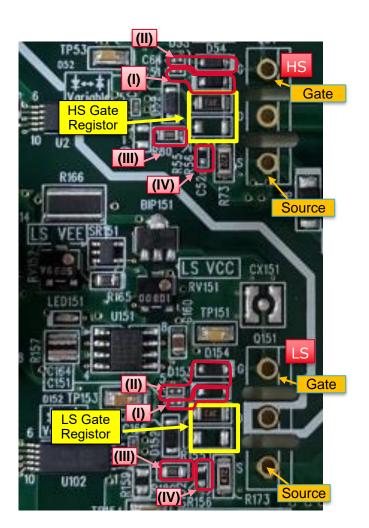

Figure 6.(a)に TO-247N、同図(b)に TO-247-4L のゲート駆動回路の実装状態をそれぞれ示し、Figure 7に TO-247N 用の回路図を示 します。

ローム製 MOSFET 駆動 IC (BM61M41RFV-C) の出力信号がゲート抵抗を介して直接 MOSFET を駆動しています。駆動回路のパタ ーンインダクタンスがゲート-ソース信号のサージ電圧特性に影響するため、極力配線長を短くしたほうがよく、最小限の調整部品で構成されていま す。

なお、TO-247N と TO-247-4L ではゲート端子のピンアサインが違っているため、それぞれのパッケージに最適な基板レイアウトとなっています。

(b) TO-247-4L 用 (PCB005P)

Figure 6. ゲート駆動回路 実装状態

初期設定はターンオンとターンオフの調整抵抗は同じ回路構成となっており、R55 で調整しますが、ターンオンとターンオフを個々のスイッチング 速度に設定したい場合、R56を実装し、ターンオン時は抵抗 R55を通し、ターンオフ時は D52 と R56を通して駆動信号を MOSFET に伝達しま す。この場合、ターンオン時はゲート抵抗 R55 のみで、ターンオフ時は R55 // R56 と並列接続となり、ターンオフが高速化されます。

なお、ダイオード D52 のフットプリントはアノードとカソードが対象となっており、逆に実装することが可能です。アノードをドライバ IC(U2)の OUT 端子に接続すればターンオンを高速化することが可能であり、使用するデバイスの特性によって使い分けることができます。

Figure 7. ゲート駆動回路 (PCB004P)

## 6. 光絶縁プローブを用いたゲート-ソース電圧測定

本評価ボードには、 HS 側および LS 側の DUT 実装位置のゲート端子直近にパターン CX51,CX151 がそれぞれあり、コネクタを実装する ことで光絶縁プローブを用いたゲート-ソース電圧測定を行うことができます。光絶縁プローブを利用することでコモンモードノイズの干渉を取り除き、よ り高確度な波形を取得することができます。

(a)コネクタ実装用パターン

(b)光絶縁プローブを用いた測定

(c)プローブ接続部

Figure 8. Coaxial 型シャント抵抗での測定方法

#### 7. デバイス電流の測定方法

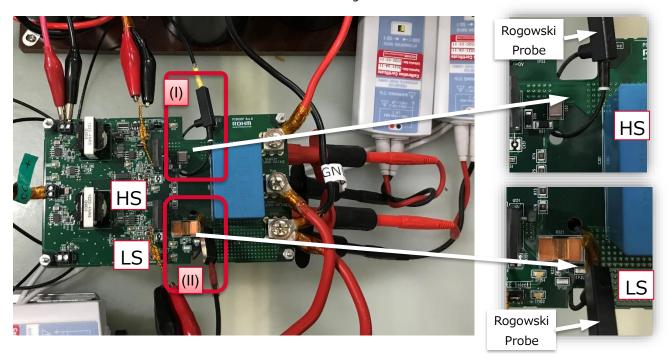

# 7.1 ロゴスキー(Rogowski)型電流プローブでの測定

本評価ボードには HS 側および LS 側にそれぞれ 1 つのスルーホール (メッキなし) と基板端面に切り欠きがあり、ロゴスキー型電流プローブを 用いて、それぞれのデバイスに流れる電流を簡単に測定することができます。 HS 側はドレイン端子の電流を測定し、LS 側はパワーソース側の電 流を測定することができます。測定時のプローブ関連の接続状況外観を Figure 9.に示し、電流プローブの取り付け状況を拡大写真で示します。

Figure 9. ロゴスキー型電流プローブによる電流測定 (PCB005P)

ロゴスキー型電流プローブのヘッド部分には種々の大きさが存在しており、適用できるヘッド部分は Figure 10.のとおりとなっていて、直径 25mm ~ 30mm、線径 3mm 以下となっています。

Figure 10. 適応可能なロゴスキー型電流プローブのヘッド部分

#### 7.2 Coaxial 型シャント抵抗での測定

ロゴスキー型電流プローブは、測定時に電流経路を分断せずに測定できるため、デバイスの使用回路を再現した状態で波形観測が可能な反 面、測定の周波数帯域があまり広くありません。

電流波形の観測には、ロゴスキー型電流プローブの他に、クランプ型電流プローブやシャント抵抗による測定方法があり、測定条件に合わせた 測定機器の選定が必要となります。クランプ型電流プローブは、プローブを取り付けるために配線を延長する必要があり、DUT のスイッチング特性に 少なからず影響を与えるためお奨めできません。また、一般的なシャント抵抗は自身のパッケージインダクタンスによるノイズが大きく、スイッチング時の 電流波形を正確に測定することができません。そこで、nsレベルの電流立ち上がりを測定可能な Coaxial 型シャント抵抗を使い、DUT のスイッチ ング特性を測定することができます。

Table 6.に一般的なロゴスキー型電流プローブと Coaxial 型シャント抵抗の特性比較一覧を示します。ロゴスキー型は測定帯域が数十 MHz なのに対し、Coaxial 型は数 GHz まで対応できるものがあります。

|                                    |                     | Rogowski          |                         |                              | Coaxial                       |                              |

|------------------------------------|---------------------|-------------------|-------------------------|------------------------------|-------------------------------|------------------------------|

| Model<br>(Manufacturer)            | SS-285A<br>(IWATSU) | CWT3<br>(PEM)     | TRCP0600<br>(Tektronix) | SDN-414-01<br>(T&M Research) | SDN-414-025<br>(T&M Research) | SDN-414-10<br>(T&M Research) |

| HF frequency                       | 30MHz               | 16MHz             | 30MHz                   | 400MHz                       | 1200MHz                       | 2000MHz                      |

| di/dt or rise time<br>(Peak Value) | 4A/ns<br>(N/A)      | 4A/ns<br>(40A/ns) | N/A                     | 1ns                          | 0.3ns                         | 0.18ns                       |

Table 6. Rogowskie 型電流プローブと Coaxial 型シャント抵抗の特性比較

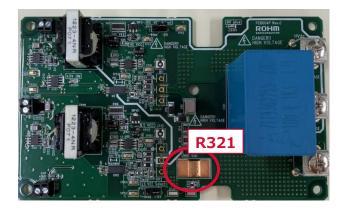

本評価ボードでは Coaxial 型シャント抵抗での測定可能なレイアウトを行っています。 Figure 11. (a)に示す抵抗 R321 (0.1mΩ) を取 り除き下アームのソースラインを切り離し、Coaxial 型シャント抵抗を(b)のようにはんだ付けし、下アーム DUT のソース電流を測定します。その際、 Coaxial 型シャント抵抗の GND 側は DUT のソース側とし、Coaxial 型シャント抵抗の GND (オシロスコープ内 GND) を DUT のソース側を 基準とします。これは、下アームの DUT のゲートーソース間電圧 V<sub>GS</sub>を一般的なパッシブプローブで測定する際、GND レベルの不一致を防止す るためです。

R321 実装位置 (a)

(b) Coaxial 型シャント抵抗に置き換え

Figure 11. Coaxial 型シャント抵抗での測定方法

#### 8. ヒートシンクの取り付け方法

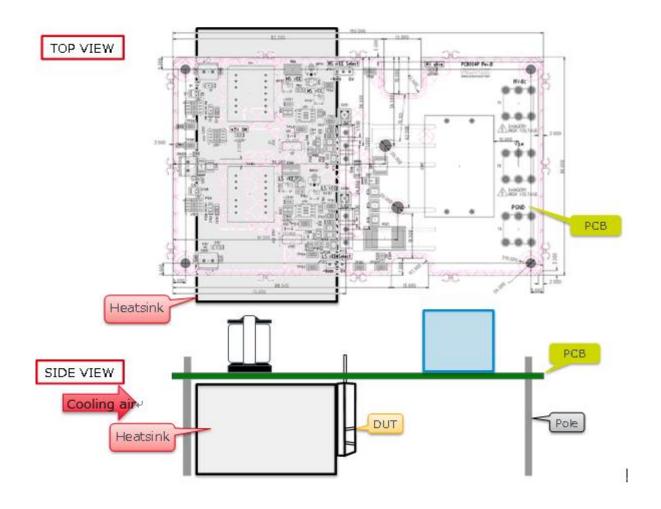

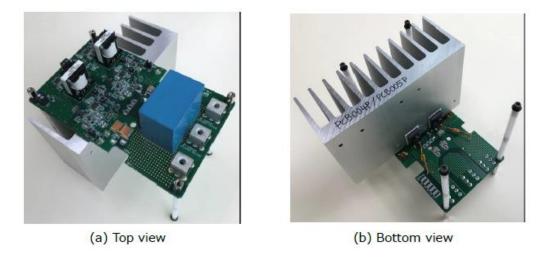

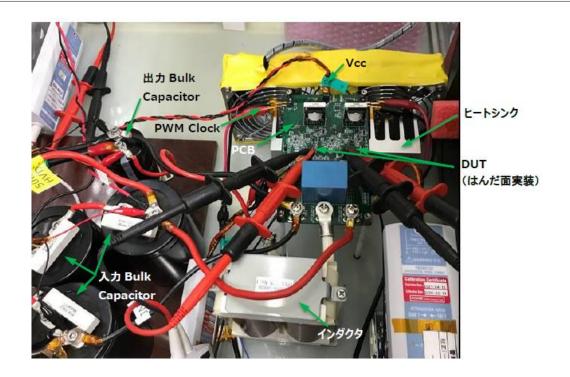

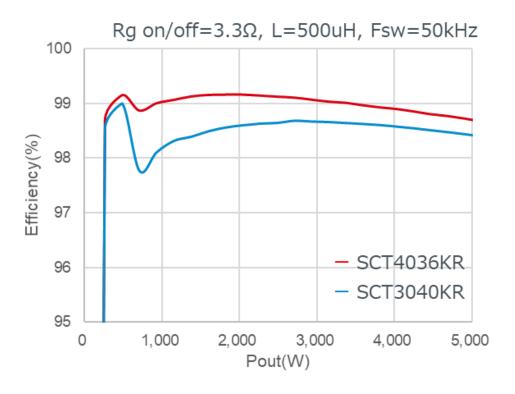

電源トポロジーによる効率測定など、本基板を使って数 kW の電力変換を行う場合、デバイス自身の消費電力が十数 W に達するためヒートシンク等による冷却が必須となります。ヒートシンクを取り付けるにはデバイスをはんだ面側に実装する必要があります。 転流用デバイスも同一ヒートシンクに取り付けられるよう DUT は同一面にレイアウトされています。 Figure 12.に取り付け例を図式化し、 Figure 13.に取り付けた状態の写真を示します。 三協サーモテック製に相当品(33BS136)があり、熱抵抗は 1.16℃/W です。

Figure 12. ヒートシンクの取り付け図

Figure 13. ヒートシンク取り付け例

Figure 14. ヒートシンクの取り付け時の測定風景

# Synch Buck (Vin=500V, Vout=250V)

Figure 15. 効率 (SCT4036KR,BUCK,Rg=3.3Ω)

#### 9. 評価ボードの接続例

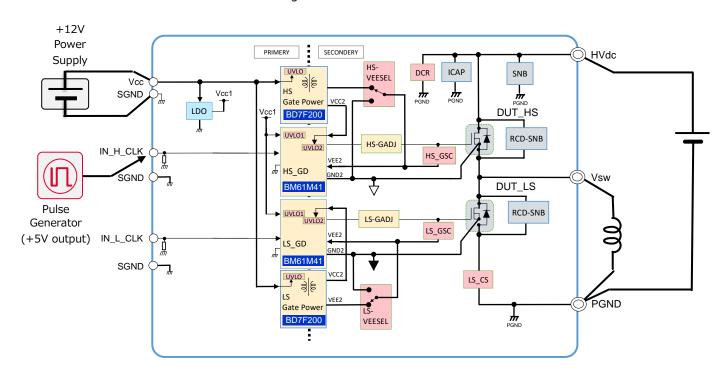

#### 9.1 HS 側 MOSFET のダブルパルス試験

HS 側の MOSFET を使ったダブルパルス試験回路を figure 16.に示します。

Figure 16. HS 側ダブルパルス回路

パルスジェネレータを準備し、CLK 信号を IN\_H\_CLK 端子(CN1 1pin)に接続します。制御用 12V 電源を Vcc 端子(CN201)に、 高圧 HVdc 電源を HVdc 端子(T1)に接続します。動作手順は以下のとおりです。

- +12V→HVdc の順番にて電源を投入します。

- ② パルスジェネレータにより、パルス信号を入力します。

インダクタ(L)に流れる最大電流 ID(peak)は下記式にて概略計算できます。

$I_{D(PEAK)} = HVdc/L*T_{DP\_TTL} [A]$

HVdc:印加電圧[V]

L:インダクタ値[µH]

T<sub>DP TTL</sub>:ダブルパルス信号のトータル時間[µs]

通常、ダブルパルス信号は単発ですが、周期的に印加する場合は、インダクタ電流 I<sub>D(PEAK)</sub>のリセット時間を充分確保する必要があります。リセット電圧はフライホイールダイオードの順方向電圧 V<sub>F</sub>分しかないため、

$T_{RST} = I_{D(PEAK)} * L/V_F [\mu s]$

で目安となる時間を把握し、その 2 倍程度のリセット時間 T<sub>RST</sub>を確保します。なお、ヒートシンクは必要ありませんが、繰り返しダブルパルス試験を 行う場合は、フライホイールダイオードの温度上昇には注意して下さい。

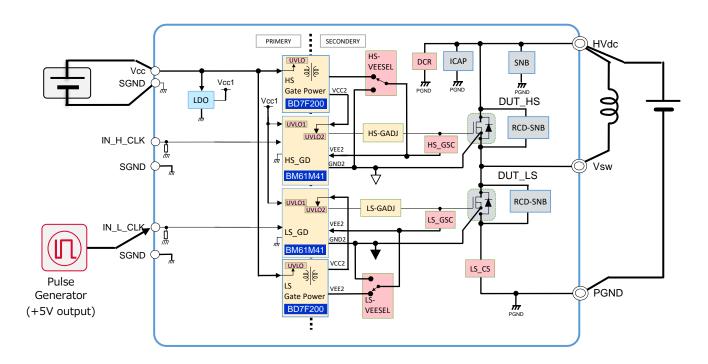

#### 9.2 LS 側 MOSFET のダブルパルス試験

LS 側の MOSFET を使ったダブルパルス試験回路を figure 17.に示します。

Figure 17. LS 側ダブルパルス回路

パルスジェネレータを準備し、外部から CLK 信号を IN\_L\_CLK 端子(CN101 1pin)に接続した後は、HS 側と同じ手順となります。

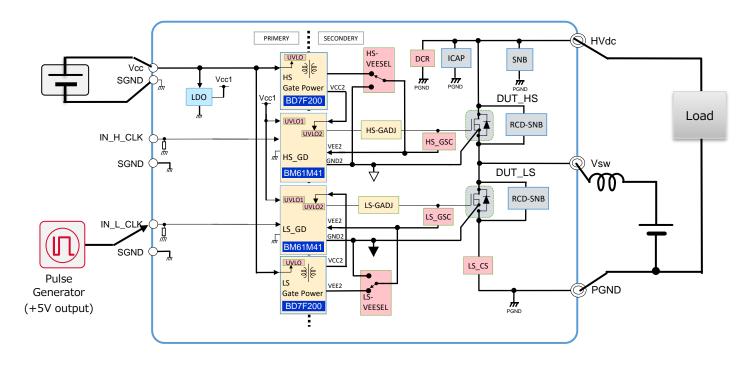

#### 9.3 Boost 電源回路

LS 側 MOSFET をスイッチング動作させた Boost 動作試験回路を figure 18 に示します。

Figure 18. Boost 回路による動作試験回路

まず、パルスジェネレータを準備し、CLK 信号を IN\_L\_CLK 端子(CN101 1pin)に接続します。制御用 12V 電源を Vcc 端子 (CN201) へ、負荷インダクタンスを Vsw 端子(T2)へ、高圧 HVdc 電源を負荷インダクタンスへ、電子負荷を HVdc 端子(T1)へ Figure 17.のように接続します。HVdc 側が出力となり、出力コンデンサは本基板上に実装されているため基本的に必要ありませんが、発振周波 数が低い場合は、適当な値を外付けすることを推奨します。その際はコンデンサの定格電圧を十分に確保して下さい。

動作手順は以下のとおりです。

- +12V 電源を投入する。

- (2) パルスジェネレータにより、スイッチング周波数とデューティ比を設定し、CLK 信号を入力する。

- (3) HVdc 電源を投入する。

- 電子負荷装置により出力電流を調整する。

インダクタ電流が連続となる CCM モードでは、出力電圧は概ね以下のようになります。

Vout=Vin/(1-Duty)

インダクタ電流が不連続(出力電流が小さい)の場合は、出力電圧はデューティ比に比例せず大きくなります(負荷電流により出力電圧は変化 する)。これはオープンループ制御のためパルスを間引いていないためですが、出力電圧は入力電圧の数十倍に達するため、必ず出力電圧値を把 握しながら入力電圧を徐々に上昇させる等の注意が必要となります。なお、負荷電流を大きくする場合は、評価デバイスの発熱に注意し、必要な らば充分冷却できるヒートシンクを取り付けるか、周囲温度に配慮して下さい。

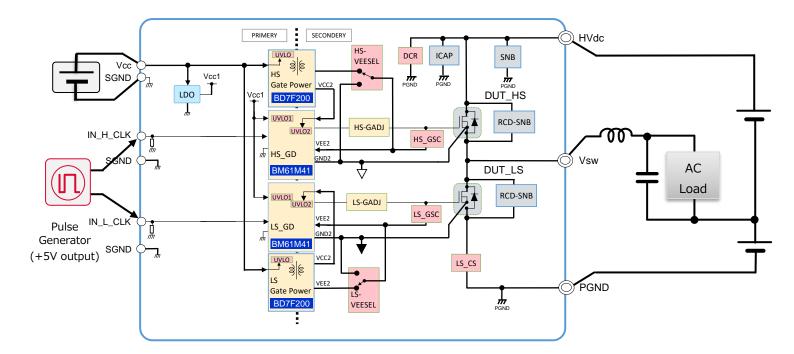

#### 9.4 2レベル インバータ回路

ハーフブリッジ構成による2レベルインバータの動作試験回路をfigure 19.に示します。

Figure 19. 2レベル インバータ回路による動作試験回路

まず、パルスジェネレータを準備し、CLK 信号を IN\_H\_CLK 端子および IN\_L\_CLK 端子(CN1, CN101 1pin)に接続します。制御用 12V 電源を Vcc 端子(CN201)へ、負荷インダクタンスを Vsw 端子(T2)へ接続します。 同じ電圧を有する高圧 HVdc 電源を 2 台準 備し、直列接続し、上側を HVdc 端子(T1)へ、下側を PGND 端子(T3)へ接続します。負荷インダクタンスの片側に平滑用コンデンサと AC 負荷を接続し、そのリターン線を直列接続した高圧 HVdc 電源の中点へ接続します。

AC 出力が+側の時は HS 側、- 側の時は LS 側がスイッチング動作し、CLK 信号を Duty 制御することにより正弦波電圧を出力します。

#### 動作手順は以下のとおりです。

- ① +12V 電源を投入する。

- ② パルスジェネレータ等により、スイッチング周波数とデューティ比を設定し、CLK 信号を入力する。

- ③ HVdc 電源を投入する。

- ④ AC 負荷装置により出力電流を調整する。

なお、負荷電流を大きくする場合は、評価デバイスの発熱に注意し、必要ならば充分冷却できるヒートシンクを取り付けるか、周囲温度に配慮 して下さい。

#### 9.5 同期整流型 Buck 電源回路

HS 側の MOSFET を使った Buck 動作試験回路を figure 20.に示します。

Figure 20. 同期整流型 Buck 電源回路による動作試験回路

パルスジェネレータを準備し、外部から CLK 信号を IN\_H\_CLK 端子(CN1 1pin)および IN\_L\_CLK 端子(CN101,1pin)に接続します。制御用 12V 電源を Vcc 端子(CN201)へ、高圧 HVdc 電源を HVdc 端子(T1)へ、負荷インダクタンスを Vsw 端子(T2)へ接続します。 平滑コンデンサと負荷を負荷インダクタンスの片側に接続します。 HVdc 側が入力となるため入力コンデンサは本基板上に実装されており基本的に必要ありませんが、発振周波数が低い場合は、適当な値を外付けすることを推奨します。その際はコンデンサの定格電圧を十分に確保して下さい。

動作手順は以下のとおりです。

- ① +12V 電源を投入する。

- ② パルスジェネレータにより、スイッチング周波数とデューティ比を設定し、CLK 信号を入力する。

- ③ HVdc 電源を投入する。

- ④ 電子負荷装置により出力電流を調整する。

インダクタ電流が連続となる CCM モードでは、出力電圧は概ね以下のようになります。

Vout=Dutv\*Vin

一方、インダクタ電流が不連続となる DCM モード時は、出力電圧は入力電圧と等しくなりますが、これはオープンループ制御のためパルスを間引かないためです。出力電圧は入力電圧と等しいので、電子負荷装置の耐圧等に注意して下さい。

HS 側と LS 側 MOSFET の同時オンを防止するために、IN\_H\_CLK 信号と IN\_L\_CLK 信号のデッドタイム時間を十分確保して下さい。なお、負荷電流を大きくする場合は、評価デバイスの発熱に注意し、必要ならば充分冷却できるヒートシンクを取り付けるか、周囲温度に配慮して下さい。

#### 10. スナバ回路

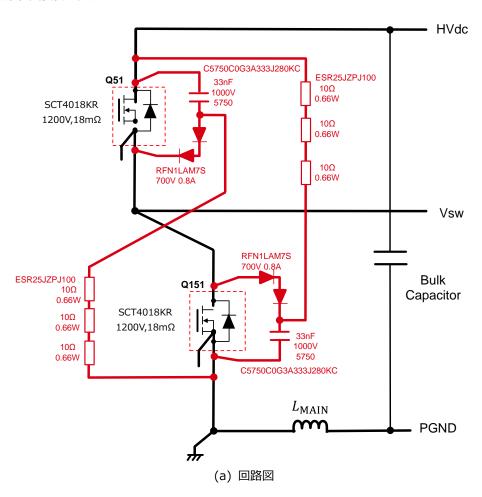

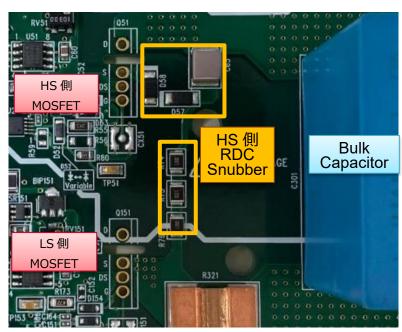

本基板には MOSFET のターン・オフサージを抑えるためにドレイン・ソース間に非放電型 RCD スナバ回路(\*3)のレイアウトが含まれています。 Figure 21.にその回路図と実装例を示します。

(b) 実装例(PCB005P, HS 側)

Figure 21. RCD 非放電スナバ回路

非放電型スナバ回路は、高圧入力電圧 HVdc を超えたサージ分のみをスナバ回路内の抵抗で消費するため、高周波スイッチング回路に最適 な回路方式となっていますが、パターンレイアウトが複雑になるため、4層以上の基板において使用して下さい。

スナバ回路内の抵抗により消費される電力  $P_{SNB}$  は、すべてスナバ回路内の抵抗  $R_{SNB}$  で消費されますが、

$$P_{\rm SNB} = \frac{L_{\rm MAIN} \times I_{\rm MAIN}^2 \times f_{\rm SW}}{2}$$

となっています。ここで、LMAINは主回路の配線インダクタンスであり、バルクキャパシタ(Bulk Capacitor)までの配線インダクタンス、IMAINは MOSFET のターンオフ時のドレイン電流、 $f_{SW}$ は MOSFET のスイッチング周波数です。

一方、スナバコンデンサの静電容量 C<sub>SNB</sub> はインダクタンスに蓄積されたエネルギーから次の式で求められます。

$$C_{\text{SNB}} = \frac{L_{\text{MAIN}} \times I_{\text{MAIN}}^2}{V_{\text{SURGE}}^2 - V_{\text{HVdc}}^2}$$

ここで、V<sub>HVdc</sub>は高圧電源、V<sub>SURGE</sub>はサージ電圧の最大値です。

更に R<sub>SNB</sub> の抵抗値は以下の式で求められます。

$$R_{\rm SNB} < \frac{-1}{C_{\rm SNB} \times \ln[(V_{\rm SURGE} - V_{\rm SNB})/(V_{\rm SURGE})]} \times \frac{1}{f_{\rm sw}}$$

これは、MOSFET の一周期の間に  $C_{SNB}$  で吸収したエネルギーを全て放電させて、サージ吸収効果を最大限にしています。

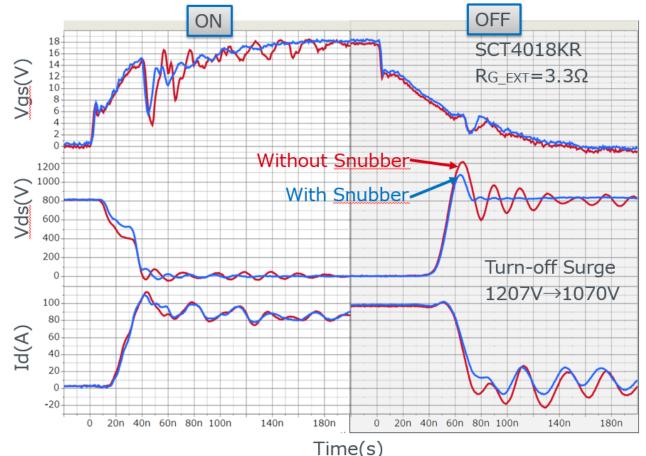

Figure 22.に SCT4018KR のダブルパルス試験によるスナバ回路の検証結果を示します。ターン・オン時はスナバ回路の有無による違いはあり ませんが、ターンオフ時は V<sub>DS</sub>ターン・オフサージが 1207V から 1070V と減少しています。その一方で、スイッチング速度にはほとんど影響がありま せん。

Figure 22. スナバ回路の効果 (SCT4018KR)

#### 11. ゲート-ソース信号の保護回路

#### 11.1 保護回路の種類

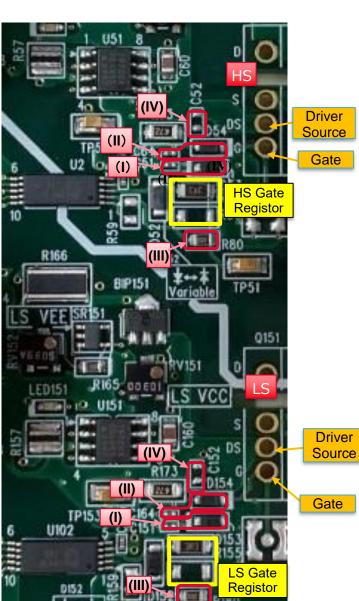

本基板には MOSFET のゲート-ソース端子に発生するサージ電圧を吸収する保護回路が内蔵されています。保護回路には Table 7.に示す 3つの機能(クランプ回路)と4つの対策回路を有しています。 ゲート-ソース電圧は、スイッチング動作時の V<sub>DS</sub>や I<sub>D</sub>の変化に大きく影響され るため、これらの保護回路により適切にサージ電圧を抑える必要があります。なお、ゲート-ソース電圧の振る舞いおよびサージの抑制方法について は、別途アプリケーションノート(\*1)、(\*2)が発行されていますので、併せて参照して下さい。

Figure 23.に回路図示します。

Table 7. 保護回路と動作詳細

| 項     | 機能(クランプ回路)    | 対象部品     | 動作詳細                                                           | 初期設定 |

|-------|---------------|----------|----------------------------------------------------------------|------|

| (I)   | 正サージ抑制        | D53, C51 | MOSFET の V <sub>DS</sub> 変化が完了した時点で発生するプラス側サージ。                | 実装   |

|       |               | D153,    | ターンオン時は V <sub>DS</sub> 最大定格を越えることがあるため、D53(D153)              |      |

|       |               | C151     | で Vcc2 にクランプさせる。 C51(C151)はパスコンであり、                            |      |

|       |               |          | D53(D153)の近傍にレイアウトする。                                          |      |

| (II)  | 負サージ抑制        | D54, C64 | ブリッジ構成における MOSFET のターン・オフ動作時に、非スイッチン                           | 実装   |

|       |               | D154,    | グ側 MOSFET の VGS に負サージが発生し、最大定格を超えること                           |      |

|       |               | C164     | があるため、ターン・オフ駆動電圧(VEE2)にクランプさせる。                                |      |

|       |               |          | C64(C164)はパスコンであり、D54(D154)の近傍にレイアウトす                          |      |

|       |               |          | る。                                                             |      |

| (III) | セルフターンオン防止    | R80      | ブリッジ構成における MOSFET のターン・オン動作時に、非スイッチ                            | 実装   |

|       | セルフターンオンサージ抑制 | R180     | ング側 MOSFET の V <sub>GS</sub> の持ち上がりが発生(V <sub>DS</sub> 立ち上がりに連 |      |

|       |               |          | 動)し、ゲート閾値 V <sub>GS(th)</sub> を越えるとオンする(いわゆるセルフター              |      |

|       |               |          | ンオン) ことがある。そのため、ドライバ IC(BM61M41RFV-C)の                         |      |

|       |               |          | MC 信号でターン・オフ駆動電圧にクランプすることにより、V <sub>GS</sub> の持ち               |      |

|       |               |          | 上がりを抑制する。                                                      |      |

| (IV)  |               | C52      | MOSFET の Crss/Ciss 比が大きくなると、V <sub>GS</sub> は持ち上がりやすく          | 未実装  |

|       |               | C152     | なる。 (充電電流は Crss に比例するため)                                       |      |

|       |               |          | Ciss に並列に容量を追加し、Crss/Ciss 比を小さくすることで、                          |      |

|       |               |          | V <sub>GS(th)</sub> 以上の持ち上がりを防止する。追加する静電容量値が大き                 |      |

|       |               |          | いほど、持ち上がり量は小さくなるが、駆動能力が必要になるばかり                                |      |

|       |               |          | か、スイッチング損失の増加を伴うため、発熱を考慮しながら追加容                                |      |

|       |               |          | 量を決定する。                                                        |      |

Figure 23. ゲート-ソース信号の保護回路(PCB004P)

V<sub>GS</sub>のサージ電圧は数十 ns の短い時間で発生するため、これらのクランプ回路のパターンインダクタンスは極力小さくするため、MOSFET の直 近にレイアウトする必要があります。

SiC MOSFET は一般的に Si 系 MOSFET よりもゲート-ソース電圧の定格が狭く、これらのクランプ回路を設置することを推奨しています。これ らの対策回路を複数用いることで、より効果的に VGS のサージ電圧を抑えることができますが、MOSFET に近付ける優先順位は以下の通りとな り、ミラークランプ(MC)信号を内蔵しているドライバ IC を用いる場合は、できる限り駆動する MOSFET の近傍にレイアウトし、MC 端子と MOSFET 間のパターン線長を短くして寄生インダクタンスを小さくする必要があります。

#### (II)負サージクランプ回路 → (I)正サージクランプ回路 → (IV)GS 間容量(C<sub>GS</sub>)追加

Figure 24.に保護回路の実装例を示します。(a)が TO-247N 用基板(PCB004P)、(b)が TO-247-4L 用基板(PCB005P)です。 ゲート端子のピンアサインは TO-247N と TO247-4L では対極にあるため、保護回路はそれぞれのパッケージに最適な実装レイアウトとなっていま

なお、Figure 25.に保護回路の有無による波形の違いについて、いくつかの事例を示していますが、実際の動作はデバイス自身の特性のみなら ず、実装されている基板の影響も大きいため、必ず実機での確認が必要です。

(a) PCB004P (b) PCB005P

Figure 24. ゲート-ソース電圧 保護回路の実装位置

#### 11.2 保護回路によるサージ抑制効果

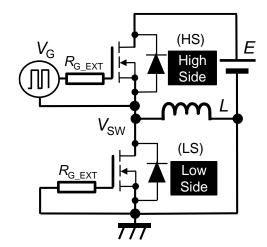

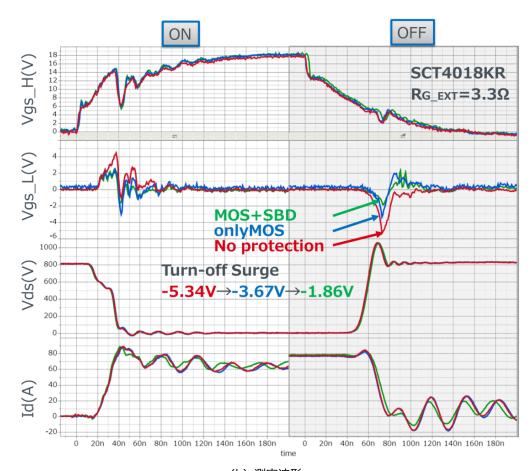

SCT4018 をブリッジ構成に接続しハイサイド(HS)側をスイッチングしたダブルパルス試験を実施し、保護回路による V<sub>GS</sub> サージ電圧の低減効果事例を示します。Figure 25.(a)は測定回路、(b)は測定波形です。

外付けゲート抵抗  $R_{G_-EXT}$ は  $3.3\Omega$ です。一番上の波形は HS 側  $V_{GS}$ 、二番目は LS 側  $V_{GS}$ 、三番目は HS 側  $V_{DS}$ 、一番下の波形は HS 側  $I_D$ となっています。ゲート-ソース端子のサージは、ターンオン時には HS 側に正サージ、ターンオフ時には LS 側に負サージが発生しています。サージの発生原因については、別途アプリケーションノートを準備(\*1),(\*4)していますので、ここでは詳しく述べませんが、保護回路が全く実装されていない(No Protection)場合、MOSFET のゲート定格電圧を越えるサージが発生する場合があります。

#### ■測定条件

DUT: SCT4018KR

E: 800V L: 250µH

ドレイン電流: 約80A パルス幅: 2.5μs R<sub>G EXT</sub>: 3.3Ω

評価ボード: PCB005P Rev.C

(a) 測定回路

(b) 測定波形

Figure 25. 保護回路の効果 (SCT4018KR)

一方、保護回路のひとつであるドライバ IC(BM61M41RFV-C)のミラークランプ信号(MC 信号)を接続することにより、ターンオフ時のサー ジを抑制することができます。しかしながら、MC 信号は高速に応答する必要があるため、できる限り MOSFET との配線長を短くする必要がありま すが、速度調整用ゲート抵抗 RG EXTなどの実装位置が優先され、MOSFET の近くに実装できない場合もあり、レイアウト次第ではクランプ効果 が十分でない場合もあります。経験的に20mm以上離れるとクランプ効果が極端に低くなります。

そこで、クランプ SBD を MOSFET の直下に配置し、負サージを抑制する回路を付加する(MC 信号 + Clamp SBD)ことで、サージ抑制効 果をより高めることができ、今回の測定においてもゲートサージ電圧を定格内に抑制していることがわかります。

このように、ゲート端子には MOSFET の過渡動作に連動したサージが、正方向および負方向に発生しますので、設計段階から保護回路を MOSFET の近傍に配置することが大切です。

#### 12. 注意事項

本評価ボードは数百 Vの電圧を取り扱うため、不具合によって危険な状態にならないよう配慮が常に必要です。不具合には、本基板で 発生する場合のみならず、配線の誤接続や規定外電圧の印加など、間違った取り扱いにより発生する不具合もあります。

Table 8.に特に注意する点について示しますが、これ以外に関しましてもあらゆる不具合防止の措置を施した上でお使い下さい。

Table 8. 代表的な不具合一覧

| Function             | Items          | Details                                                                                                                                               |

|----------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| DCR                  | LED 不点灯        | HVdc-PGND 端子に電圧を印加した時に、LED301(赤色)が点灯していることを確認すること。 点灯していない場合は印加電圧源や配線等の確認を行うこと。 入出力電圧が約 20V 以上になると点灯する。                                               |

| HVdc<br>Vsw          | 誤配線<br>規定外電圧印加 | 規定値(1200V)以上の電圧印加は厳禁であり、配線等の接続間違いなどが発生しないようにすること。また、稼働中は絶対に触らないこと。                                                                                    |

| Vcc                  | 誤配線<br>規定外電圧印加 | Vcc は正負逆電圧の印加をしないよう、使用前に配線の確認を行うこと。ただし、逆接続用ダイオードが入っているので、Vcc 電源の OPC 設定を 1A~3A に設定すること。 (逆接続用ダイオードを保護するため) また、規定の電圧以外を印加すると故障の原因となるので、充分な確認の上、操作すること。 |

| SNB<br>RDC_SNB       | MLCC 焼損        | 機械的ストレスによりクラック等の短絡故障が発生しやすい MLCC を使用しているため、基板には過度の衝撃を与えないよう、取り扱いには注意すること。<br>もし電圧を印加した時に少しでも気になる点があれば印加電圧を切断する等、危険回<br>避処置を直ちに行うこと。                   |

| IN_H_CLK<br>IN_L_CLK | 連続パルス印加        | DUT を駆動する CLK 信号を連続的に印加すると、規定を越える電流が流れ DUTが破損することがあるため、必ず DUT の電気的特性を満足する範囲内で使用すること。                                                                  |

| DUT                  | ドライバ IC 破損     | DUT のゲート-ソース間が短絡状態で、駆動する CLK 信号をオンにすると、Vcc2 から OUT 端子を通り、GND2 へ短絡電流が流れるため、外付け抵抗値が小さい場合、ドライバ IC の OUT 端子を破壊することがある。そのため、動作前に必ずゲート-ソース間の短絡状態を確認すること。    |

#### 参考資料:

\*1「ブリッジ構成におけるゲートーソース電圧の振る舞い」

アプリケーションノート (No. 60AN134JRev.001)

□-ム株式会社, 2018年5月

https://fscdn.rohm.com/jp/products/databook/applinote/discrete/sic/mosfet/sic-mosfet\_gate-

source\_voltage\_an-j.pdf

\*2「ゲートーソース電圧のサージ抑制方法」

アプリケーションノート (No. 62AN009JRev.001)

ローム株式会社, 2019年5月

https://fscdn.rohm.com/jp/products/databook/applinote/discrete/sic/mosfet/sicmosfet-

surge%20suppression\_an\_j.pdf

\*3「スナバ回路の設計方法」

アプリケーションノート (No. 62AN0036JRev.001)

□-ム株式会社, 2019年6月

https://fscdn.rohm.com/jp/products/databook/applinote/discrete/sic/mosfet/sic-

mos\_snubber\_circuit\_design\_an-j.pdf

\*4 「ドライバソース端子によるスイッチング損失の改善」

アプリケーションノート (No. 62AN0039JRev.001)

□-ム株式会社, 2019年8月

https://fscdn.rohm.com/jp/products/databook/applinote/discrete/sic/mosfet/sicmosfet\_swloss\_an-j.pdf

\*5 日本オートマティック・コントロール株式会社 ホームページ

https://naccjp.com/nacc/lp/cwt/

\*6 T&M Research Products, Inc. ホームページ

https://www.tandmresearch.com/index.php?mact=ListIt2Products,cntnt01,detail,0&cntnt01item=series-sdn-414&cntnt01template\_summary=Side&cntnt01returnid=19

\*7 [How to Select the Right Current Probe]

アプリケーションノート (No. 5992-2656EN)

KEYSIGHT TECHNOLOGIES, 2018年9月

#### ご注意

- 1) 本資料の記載内容は改良などのため予告なく変更することがあります。

- 2) 本資料に記載されている内容は製品のご紹介資料です。ご使用に際しては、別途最新の仕様書を必ず ご請求のうえ、ご確認ください。

- 3) ロームは常に品質・信頼性の向上に取り組んでおりますが、半導体製品は種々の要因で故障・誤作動する可能性があります。

- 万が一、本製品が故障・誤作動した場合であっても、その影響により人身事故、火災損害等が起こらないようご使用機器でのディレーティング、冗長設計、延焼防止、バックアップ、フェイルセーフ等の安全確保をお願いします。 定格を超えたご使用や使用上の注意書が守られていない場合、いかなる責任もロームは負うものではありません。

- 4) 本資料に記載されております応用回路例やその定数などの情報につきましては、本製品の標準的な動作や使い方を説明するものです。

- したがいまして、量産設計をされる場合には、外部諸条件を考慮していただきますようお願いいたします。

- 5) 本資料に記載されております技術情報は、製品の代表的動作および応用回路例などを示したものであり、 ロームまたは他社の知的財産権その他のあらゆる権利について明示的にも黙示的にも、その実施また は利用を許諾するものではありません。上記技術情報の使用に起因して紛争が発生した場合、ロームは その責任を負うものではありません。

- 6) 本資料に掲載されております製品は、耐放射線設計はなされておりません。

- 7) 本製品を下記のような特に高い信頼性が要求される機器等に使用される際には、ロームへ必ずご連絡の上、承諾を得てください。

- ·輸送機器(車載、船舶、鉄道など)、幹線用通信機器、交通信号機器、防災·防犯装置、安全確保のための装置、医療機器、サーバー、太陽電池、送電システム

- 8) 本製品を極めて高い信頼性を要求される下記のような機器等には、使用しないでください。 ・航空宇宙機器、原子力制御機器、海底中継機器

- 9) 本資料の記載に従わないために生じたいかなる事故、損害もロームはその責任を負うものではありません。

- 10) 本資料に記載されております情報は、正確を期すため慎重に作成したものですが、万が一、当該情報の誤り・誤植に起因する損害がお客様に生じた場合においても、ロームはその責任を負うものではありません。

- 11) 本製品のご使用に際しては、RoHS 指令など適用される環境関連法令を遵守の上ご使用ください。 お客様がかかる法令を順守しないことにより生じた損害に関して、ロームは一切の責任を負いません。 本製品の RoHS 適合性などの詳細につきましては、セールス・オフィスまでお問合せください。

- 12) 本製品および本資料に記載の技術を輸出又は国外へ提供する際には、「外国為替及び外国貿易法」、「米国輸出管理規則」など適用される輸出関連法令を遵守し、それらの定めにしたがって必要な手続を行ってください。

- 13) 本資料の一部または全部をロームの許可なく、転載・複写することを堅くお断りします。

ローム製品のご検討ありがとうございます。 より詳しい資料やカタログなどご用意しておりますので、お問合せください。

# ROHM Customer Support System

http://www.rohm.co.jp/contact/