#### スイッチングレギュレータシリーズ

# 昇圧コンバータの PCB レイアウト手法

スイッチング電源の設計において、PCBレイアウト設計は、回路設計同様に重要です。適切なレイアウトでなければ、電源 IC の本来の性能を引き出すことはおろか、IC 破壊など、致命的なトラブルを引き起こします。このアプリケーションノートでは、昇圧コンバータにフォーカスして、解説していますので、適正な PCB レイアウト設計の一助となれば幸いです。また、降圧コンバータについてフォーカスしたノートは、"降圧コンバータの PCB レイアウト手法"としてリリース済ですので、昇降圧コンバータなどの PCB レイアウト設計時には、合わせて参照ください。なお、本アプリケーションノートは、"降圧コンバータの PCB レイアウト手法"の回路素子番号(Q2,D2 など欠番あり)と整合しています。

#### 昇圧コンバータの電流経路

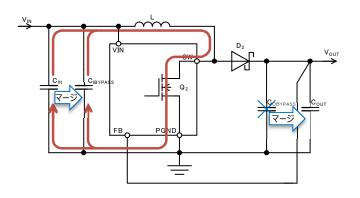

Figure 1-a から 1-c は、昇圧コンバータの電流経路を示した図です。 Figure 1-a の赤色の線は、スイッチング FET  $Q_2$ がオン時にコンバータに流れる主な電流を表しています。 $C_{IBYPASS}$ は、高周波用のデカップリングコンデンサで、 $C_{IN}$ は、大容量コンデンサ $^{(\pm 1)}$ です。スイッチングFET  $Q_2$ がオンした瞬間、電流波形の急峻な部分の大部分は $C_{IBYPASS}$ から供給され、次に  $C_{IN}$ から供給されます(電流により  $C_{IN}$ は、 $C_{IBYPASS}$ にマージが可能です。)。緩やかな変化の電流は、入力電源から供給されます。この期間に、インダクタ L に電流エネルギーを蓄えます。

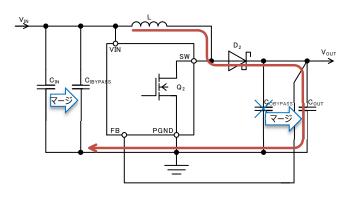

Figure 1-b の赤色の線は、スイッチング FET  $Q_2$  がオフした時の電流の状態を表しています。インダクタ L は、スイッチング FET  $Q_2$  がオフしても、直前の電流値をキープしようと働きます。インダクタ L の左端は、 $V_{IN}$  に固定されるので、 $V_{OUT}$  に電圧を継ぎ足すように電流を供給し続けるので、昇圧動作になります。したがって、スイッチング FET  $Q_2$  のオン時間が長く、インダクタ L に蓄積された電流エネルギーが大きいほど、大電力を取り出せます。しかし、むやみにスイッチング FET  $Q_2$  のオン時間を長くすると、出力側に電力を供給する時間が少なくなり、効率が悪化します。そのため、オン/オフ時間比(デューティ)の最大値を制限しています。

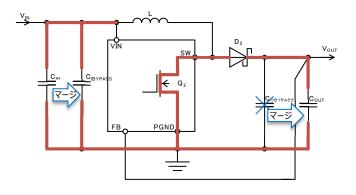

Figure1-c の赤色の太線部分は、Figure1-a と 1-b の差分を表しています。スイッチング FET  $Q_2$  がオフからオンへ、オンからオフへ変化する度に、赤線部分は、激しく変化します。この系は、変化が急峻なため高調波を多く含んだ波形が現れます。この差分の系は、重要箇所として PCB レイアウトで最大限の注意を払う必要があります。

注1:一般に、コンデンサは種類によらず容量が大きくなると周波数特性は悪化します。ここでは、周波 数特性の観点から、その特性が良くないコンデンサとして、大容量コンデンサと言う表現をしていま す。

Figure 1-a. スイッチング FET Q2のオン時の電流経路

Figure 1-b. スイッチング FET Q2のオフ時の電流経路

Figure 1-c. 電流の差分、レイアウト上での重要箇所

#### PCB レイアウト手順

PCB レイアウト手順は、おおまかに以下の様になります。

- 1. 入力コンデンサ CIN, CIBYPASS を、IC の近くに配置する。

- 2. 出力コンデンサ Cour とスイッチング FET Q2のグラウンドル-プを可能な限り小さくする。

- 3. 出力コンデンサ Cour、フリーホイールダイオード<sup>(注 2)</sup>D<sub>2</sub>とインダクタ Lを可能な限り近くに、かつ同一面に配置する。

- 4. 特にインダクタ L の銅箔パターン面積は、スイッチングノードからの 輻射ノイズを最小限にするため、必要以上に大きくしない。

- 5. 必要に応じてサーマルビアを配置する。

- 6. 帰還経路は、出力コンデンサ Cout の近傍から分離し、出力コ ンデンサ Cout やフリーホイールダイオード D2 などのノイズ源から離 して配線する。

- 7. 一部の機器では、外部補償部品 Rc,Cc が必要となります。 これらの部品は、IC のグラウンド近くに配置する。

- 8. 帰還分圧器が必要な場合は、ICのグラウンド近くに配置する。

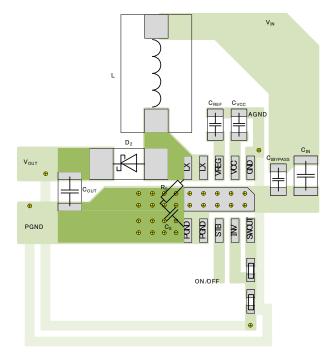

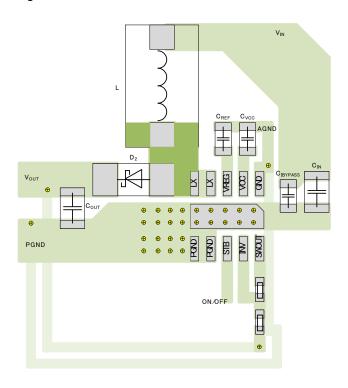

Figure 2. 望ましい入力コンデンサの配置

#### 入力コンデンサを IC の近くに配置

入力コンデンサは、DCDC コンバータのトポロジ(昇圧、降圧)にかかわ らず、最も重要な部品です。昇圧コンバータの場合、入力コンデンサは、 昇圧負荷に対して、出力電圧/入力電圧比分の大電流が流れるば かりでなく、高周波数スイッチング電流に対する高速応答性を担保す るために、大容量の CIN と高周波用デカップリング CIBYPASS を想定して います。降圧 DCDC の入力コンデンサ同様、電流容量と高速応答性 がコンデンサ1個で担保可能な場合は、CINとCIBYPASSを1個のセラ ミックコンデンサにマージ可能です。この場合は、高周波スパイクノイズ に対する配慮をメインに配置してください。

ここでは、CIBYPASS と CIN がマージできないとこを前提に、説明します。 CIBYPASS は、必ず IC と同じ面の直近に配置します。特に、GND ルー プは、小さくなるように配置・配線してください。CIBYPASSは、前述の"昇 圧コンバータの電流経路"でも述べたように、電流波形の急峻な部分 の供給源(この部分に高周波のスパイクノイズが発生する)となるの で特に重要です。望ましい入力コンデンサの配置例を、Figure 2に示 します。CIN が大電流担保のみの場合は、CIBYPASS が望ましく配置さ れていることを前提に、IC から 2cm 程度なら離れても構いません。ま た、ビアを介して裏面へ配置することも許容できます。

#### 出力コンデンサとフリーホイールダイオードの配置

次に重要な部品として、出力コンデンサとフリーホイールダイオードを配 置します。出力コンデンサは、本ドキュメントが対象としている(Table 1参照)製品では、電流容量が小さい(Io≤1A)ので、容量値が 小さくなり、セラミックコンデンサ1個で、高周波用デカップリングコンデン サ Cobypass を兼ねています。これは、セラミックコンデンサは、容量値が 小さくなるにつれ周波数特性がよくなるためです。しかし、セラミックコン デンサによって周波数特性が異なるため実際に使用する部品の周波 数特性を確認してください。

フリーホイールダイオード D2は、ICや Coutと同じ面の直近に配置しま す。ダイオードとスイッチング FET  $Q_2$  がつながるポイントは、スイッチング ノードで、高周波のノイズの発生源です。このノードが長くなると、配線 インダクタンスにより誘起された高周波にスパイクノイズが、Vourに重畳 されてしまします。さらに、スイッチング FET Q2からフリーホイールダイオ ード D<sub>2</sub>、高周波デカップリング兼用出力コンデンサ Cout のループは、 可能な限り小さくし、高周波ノイズの輻射を最小限にします。このトレ -スは、必ず同一面で完結する必要があります。ビアを介して裏面に 配置・配線すると、ビアコンダクタンスの影響により、ノイズが悪化します ので、絶対にビアを介さないでください。これらを考慮した望ましいレイア ウトを、Figure 3-a (説明対象部は、濃い色で表示) に示します。

スイッチングノードが長くなったレイアウトになると、配線インダクタンスが 増加し、高周波スパイクノイズの発生が大きくなります。この様なレイア

注 2: スイッチング FET がオフしている期間に、インダクタ電流を流すためのダイオード。このダイオードの電 流経路により、インダクタによる電圧の発生を抑えられます。

ウトでは、大抵の場合、高周波スパイクノイズを発生します。発生した 高周波スパイクノイズを改善するため、RC スナバ回路を応急処置とし て追加する場合があります。このスナバ回路の位置は、スイッチング FET Q2とICのGND端子の直近に配置する必要があります(Figure

Figure 3-a. 望ましいスイッチングノードの配置

#### インダクタの配置

インダクタ L は、スイッチングノードからの輻射ノイズを最小限にするため、 スイッチング FET Q2 の近くに配置し、必要以上に大きくしてはいけま せん。配線抵抗の改善とデバイスの冷却を目的に、銅箔面積を大きく

3-b)ので、あらかじめ Rs と Cs のランドを準備することをお勧めします。 ただし、スナバ回路は、スイッチング動作をしていると常に損失が発生 するため、効率を低下させる要因になります。

Figure 3-b. 望ましいスナバ回路の配置

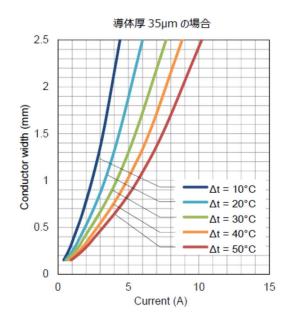

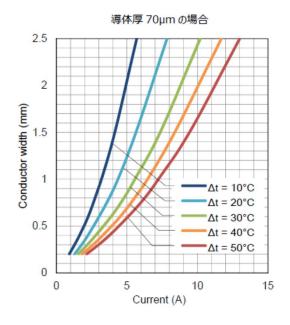

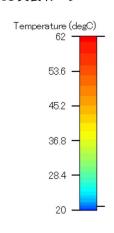

する方向で考えがちですが、面積が広くなるとアンテナとして、働くことが あり、EMI の増大を招いてしまいます。配線幅を決定する指針の一つ に電流耐量があります。Figure 4 にある電流を流したときの導体幅と 自己発熱による温度上昇のグラフを示します。例えば、2A の電流を 導体厚 35µmの配線に流した場合、20℃の温度上昇に抑えるため には、0.53mmの導体幅でよいことになります。

Figure 4. 導体厚さ・導体幅・電流による温度上昇

しかし、配線は周辺部品の発熱や周囲温度の影響を受けるため、十 分なマージンを持った導体幅を使用することを推奨します。例えば、1 オンス(35µm)基板では、1A あたり 1mm 幅以上、2 オンス(70µ m)基板では、1A あたり 0.7mm 幅以上の導体幅で配線します。

EMI の観点から配線面積を考慮したレイアウトを、Figure 5-a (説 明対象部は、濃い色で表示。以下全 Figure 5 同様)に示します。 また、必要以上に広い銅箔配線を配置した良くないレイアウトを、 Figure 5-b に示します。

Figure 5-a. 望ましいインダクタへの配線

VIN PGND

Figure 5-c. 良くないインダクタ直下の配線

Figure 5-b. 良くないインダクタへの広大配線

Figure 5-d. 良くないインダクタ端子間の配線

インダクタ配置に関して、その他に注意することは、インダクタ直下にグラ ウンド層を置かない事です(Figure 5-c)。グラウンド層に発生する渦 電流による磁力線の打ち消し効果で、インダクタ値の低下や損失の増 加(Q の低下)が発生します。グラウンド以外の信号線でも、渦電流に より、信号線にスイッチングノイズが伝搬する可能性があります。インダ クタ直下の配線は、避けてください。やむを得ず配線する場合は、磁 力線の漏れが小さい閉磁路構造のインダクタを使用してください。

インダクタ端子間のスペースにも注意が必要です、Figure 5-d の様に、 端子間に距離が近いと、スイッチングノードの高周波信号が、浮遊容 量を介して、入力へ容量誘導されます。

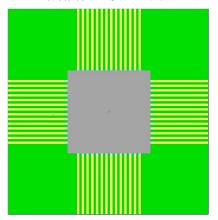

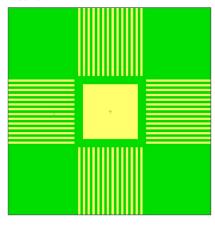

#### サーマルビアの配置

PCB の銅箔面積は、放熱に寄与しますが、厚さが十分でないため、あ

る面積以上では面積に見合った放熱効果が得られません。熱は、基 板の基材を放熱器として放熱されます。熱を基板の反対側へ効果的 に伝えて、熱抵抗を大幅に小さくするためにサーマルビアを使用します。

サーマルビアは、熱伝導性を高めるために、メッキ充填できる内径 0. 3 mm程度の小径ビアを推奨します。穴の直径が大きすぎると、リフロ ーハンダ処理工程で、ハンダ吸い上げ問題が発生します。サーマルビア の間隔は、1.2mm 程度とし、ICの裏面放熱板の直下に配置します。

裏面放熱板の直下だけでは不足する場合は、IC 周辺にサーマルビア を配置します。裏面放熱板が、グラウンド電位の場合は、広い銅箔パ ターンを設けても、EMI に悪影響を及ぼしません。

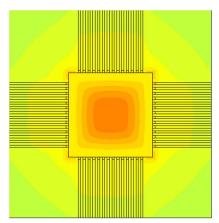

サーマルビアの効果を、Figure 6-a から 6-e に熱シミュレーションの例 を示します。サーマルビアの効果として、15℃程度の温度低下を確認 いただけます。

Figure 6-a. IC 実装イメージ

Figure 6-b. IC 直下のサーマルビアなし

Figure 6-c. IC 直下にサーマルビアあり

Figure 6-d. IC 直下ビアなし熱分布

Figure 6-e. IC 直下ビアあり熱分布

#### 帰還経路の配線

信号配線で、特に注意が必要なのは帰還信号です。この配線は、回路的にハイインピーダンスになる傾向が強く、ノイズを拾いやすくなります。この配線でノイズを拾うと出力電圧に誤差を生じ、動作が不安定になる場合があります。

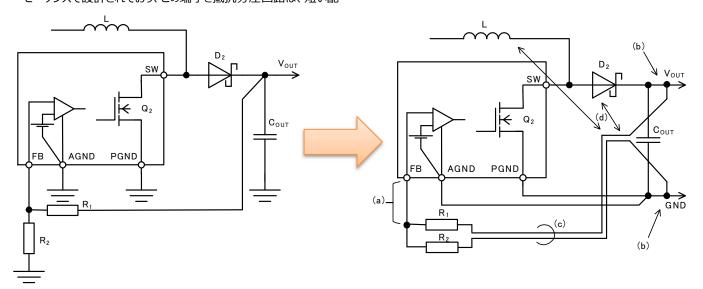

帰還経路の配線の注意点を、Figure 7 に示します。

(a). 帰還信号を入力する IC のフィードバック端子は、通常ハイイン ピーダンスで設計されており、この端子と抵抗分圧回路は、短い配 線で結びます。

- (b). 出力電圧を検出する箇所は、出力コンデンサ Cout の両端か、 出力コンデンサより後ろに接続します。

- (c). 抵抗分圧回路の配線は、平行かつ近接された方が、ノイズ耐性がよい。

- (d). インダクタ L やダイオード  $D_2$  から遠ざけて配線を引く。インダクタ やダイオードの直下、電力系の配線と並行して配線しないように注意が必要です。多層基板においても同じです。

Figure 7. 帰還経路配線の注意点

#### グラウンド

アナログ小信号グラウンドとパワーグラウンドは、分離しなければなりません。パワーグラウンドは、比較的配線抵抗が低く、放熱性の良いトップレイヤに分離することなく、レイアウトする事が基本です。パワーグラウンドを分離してビアを介して裏面で接続すると、ビアの抵抗やインダクタの影響で損失やノイズの悪化を招きます。内層や裏面にグラウンドプレーンを設けることは、DC損失の軽減やシールド、放熱が目的で、あくまで補助的なグラウンドです。

多層基板で内層や裏面にグラウンドプレーンを配置する場合は、高周波スイッチングノイズが多いパワーグラウンドに注意を払う必要があります。2層目に DC 損失軽減のためのパワーグラウンドプレーンがある場合、トップレイヤと2層目を多数のビアで接続し、パワーグラウンドのインピーダンスを小さくします。さらに、3層目にコモングラウンド、4層目に信号グラウンドがある場合、パワーグラウンドと 3,4 層目グラウンドの接続は、高周波スイッチングノイズが少ない入力コンデンサ付近のパワーグラウンドのみを接続します。決してノイズが多い出力やフリーホイールダイオードのパワーグラウンドを接続しないでください。

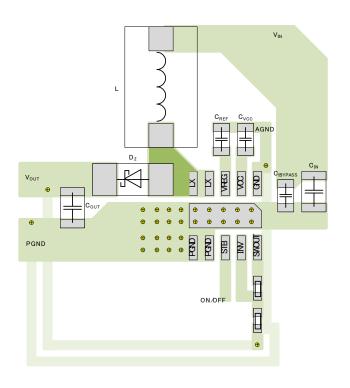

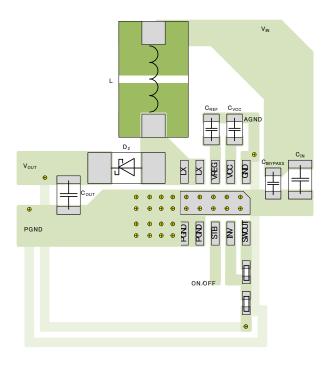

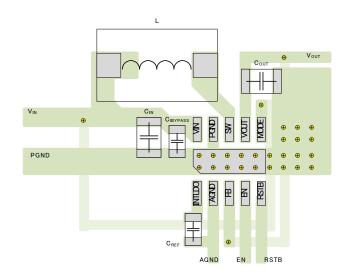

#### 同期整流の場合の例

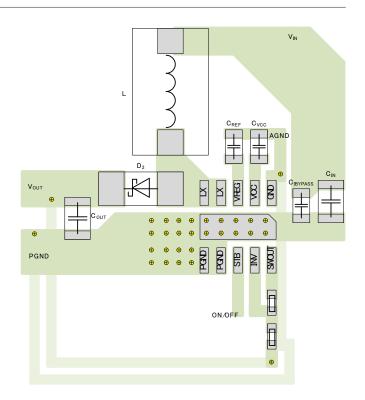

同期整流の場合、フリーホイールダイオード D<sub>2</sub> が、スイッチング FET Q2Hとして、IC 内部に集積されることが多いので、望ましいレイアウトは、 Figure 8 の様になります。 入出力コンデンサ、インダクタやインダクタ を含むスイッチングノード、サーマルビア、帰還経路、グラウンドに対する 配慮ポイントは、Figure 1 から7と同様です。もちろん、高周波スパ イクノイズ対策のスナバ回路に関しても、配慮ポイントは、同様です。

Figure 8. 同期整流の望ましい配置

#### PCB パターンの物理

銅箔の抵抗とインダクタンス、ビアの抵抗とインダクタおよびコーナー配線については、"降圧コンバータの PCB レイアウト手法"の P9,10 を参照くださ い。

#### 対象製品

Table 1. 本ドキュメントが対象としているスイッチング電源 IC('19/7 現在)

| 製品名          | パッケージ名  | トポロジー   | 反転有 | 出力電力(mA·V) | 作図例        |

|--------------|---------|---------|-----|------------|------------|

| BU33DV5G     | SSOP5   | 同期昇圧    |     | 10 x 3.3   |            |

| BU33DV7NUX   | VSON10  | 同期昇圧    |     | 300 x 3.3  |            |

| BU34DV7NUX   | VSON10  | 同期昇圧    |     | 300 x 3.4  |            |

| BU33UV7NUX   | VSON10  | 同期昇圧    |     | 500 x 3.3  | Figure 8   |

| BD8316GWL    | WLCSP11 | 非同期昇圧   | 0   | 200 x 5.6  |            |

| BD8317GWL    | WLCSP11 | 非同期昇圧   | 0   | 100 x 5.0  |            |

| BD83854GWL   | WLCSP12 | 同期昇圧    | 0   | 50 x 5.4   |            |

| BD83854MUV   | VQFN20  | 同期昇圧    | 0   | 50 x 5.4   |            |

| BD8152FVM    | MSOP8   | 非同期昇圧   |     | 1400 x 8.5 |            |

| BD8158FVM    | MSOP8   | 非同期昇圧   |     | 1400 x 8.5 |            |

| BD8306MUV    | VQFN16  | 同期昇降圧   |     | 1000 x 3.3 |            |

| BD8311NUV    | VSOP11  | 非同期昇圧   |     | 800 x 8    | Figure 2,5 |

| BD8314NUV    | VSOP11  | 非同期昇圧   |     | 600 x 8    |            |

| BD83070GWL   | WLCSP12 | 同期昇降圧   |     | 1000 x 3.3 |            |

| BD90302NUF-C | VSON10  | 同期PwMOS |     |            |            |

## 変更履歴

| Date      | Revision | Changes     |

|-----------|----------|-------------|

| 2019.7.17 | 001      | New Release |

#### ご注意

- 1) 本資料の記載内容は改良などのため予告なく変更することがあります。

- 2) 本資料に記載されている内容は製品のご紹介資料です。ご使用に際しては、別途最新の仕様書を必ずご請求のうえ、ご確認ください。

- 3) ロームは常に品質・信頼性の向上に取り組んでおりますが、半導体製品は種々の要因で故障・誤作動する可能性があります。

- 万が一、本製品が故障・誤作動した場合であっても、その影響により人身事故、火災損害等が起こらないようご使用機器でのディレーティング、冗長設計、延焼防止、バックアップ、フェイルセーフ等の安全確保をお願いします。 定格を超えたご使用や使用上の注意書が守られていない場合、いかなる責任もロームは負うものではありません。

- 4) 本資料に記載されております応用回路例やその定数などの情報につきましては、本製品の標準的な動作や使い方を説明するものです。

- したがいまして、量産設計をされる場合には、外部諸条件を考慮していただきますようお願いいたします。

- 5) 本資料に記載されております技術情報は、製品の代表的動作および応用回路例などを示したものであり、 ロームまたは他社の知的財産権その他のあらゆる権利について明示的にも黙示的にも、その実施また は利用を許諾するものではありません。上記技術情報の使用に起因して紛争が発生した場合、ロームは その責任を負うものではありません。

- 6) 本資料に掲載されております製品は、耐放射線設計はなされておりません。

- 7) 本製品を下記のような特に高い信頼性が要求される機器等に使用される際には、ロームへ必ずご連絡の上、承諾を得てください。

- ·輸送機器(車載、船舶、鉄道など)、幹線用通信機器、交通信号機器、防災·防犯装置、安全確保のための装置、医療機器、サーバー、太陽電池、送電システム

- 8) 本製品を極めて高い信頼性を要求される下記のような機器等には、使用しないでください。 ・航空宇宙機器、原子力制御機器、海底中継機器

- 9) 本資料の記載に従わないために生じたいかなる事故、損害もロームはその責任を負うものではありません。

- 10) 本資料に記載されております情報は、正確を期すため慎重に作成したものですが、万が一、当該情報の誤り・誤植に起因する損害がお客様に生じた場合においても、ロームはその責任を負うものではありません。

- 11) 本製品のご使用に際しては、RoHS 指令など適用される環境関連法令を遵守の上ご使用ください。 お客様がかかる法令を順守しないことにより生じた損害に関して、ロームは一切の責任を負いません。 本製品の RoHS 適合性などの詳細につきましては、セールス・オフィスまでお問合せください。

- 12) 本製品および本資料に記載の技術を輸出又は国外へ提供する際には、「外国為替及び外国貿易法」、「米国輸出管理規則」など適用される輸出関連法令を遵守し、それらの定めにしたがって必要な手続を行ってください。

- 13) 本資料の一部または全部をロームの許可なく、転載・複写することを堅くお断りします。

ローム製品のご検討ありがとうございます。 より詳しい資料やカタログなどご用意しておりますので、お問合せください。

### ROHM Customer Support System

http://www.rohm.co.jp/contact/