# カップリングコンデンサレス ラインアンプ

# **BD8876FV, BD8878FV**

#### 概要

BD8876FV、BD8878FV は出力カップリングコンデンサレスラインアンプです。負電源発生回路を内蔵しており、正電圧と負電圧の両電圧を用いてラインアンプを駆動することで、グラウンドレベルを基準にして出力を行います。そのため、広い出力ダイナミックレンジを持ち、単一電源5Vで2Vrmsの信号を出力することが可能です。これにより高電圧出力のレギュレータを削減することが出来ます。また、グラウンドを基準として出力を行うため、出力カップリングコンデンサなしに他デバイスとの接続が可能です。

### 特長

- 単一電源 5V で 2 Vrms の信号を出力可能

- 出力カップリングコンデンサ不要

- 可変利得(+6.0dB / +9.0dB Typ) [BD8876FV]

- 固定利得(+6.7dB Typ) [BD8878FV]

- 負電源発生回路内蔵

- グラウンド基準出力

- 減電圧保護回路/短絡保護回路内蔵

# 用途

ゲーム機、プロジェクタ、ブルーレイ・プレーヤ、 セット・トップ・ボックス、TV など。

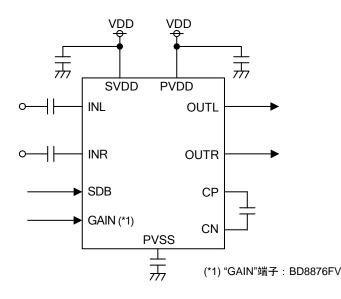

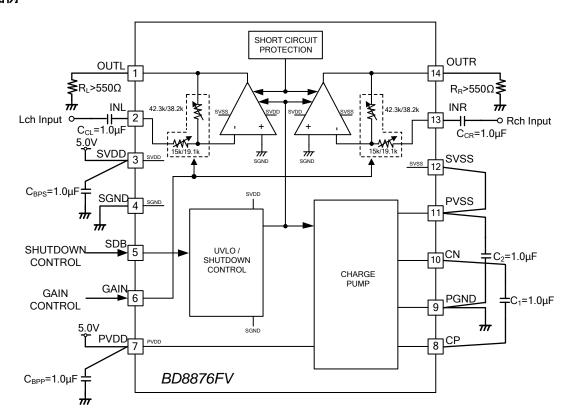

# 基本アプリケーション回路

Figure 1. 基本アプリケーション回路

# 重要特性

パッケージ SSOP-B14 W(Typ) x D(Typ) x H(Max) 5.00mm x 6.40mm x 1.35mm

|       | BD8876FV                          | BD8878FV |  |  |

|-------|-----------------------------------|----------|--|--|

| アンプ方式 | 反転アンプ                             | 非反転アンプ   |  |  |

| ゲイン   | +6.0dB / +9.0dB<br>(GAIN ピンによる切替) | +6.7dB   |  |  |

| パッケージ | SSOP-B14                          |          |  |  |

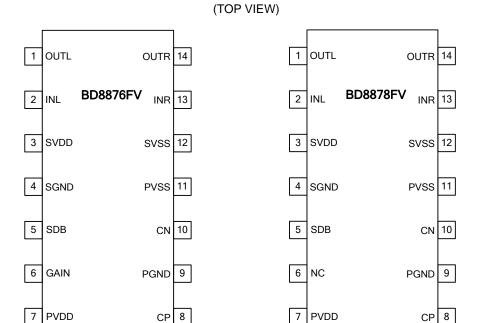

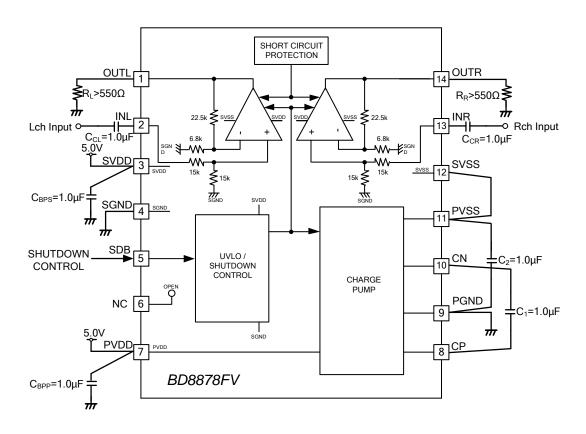

# 端子配置図

Figure 2. 端子配置図

# 端子名と機能

| PIN<br>No. | 端子名                | 機能                                    | 等価<br>回路図                            |

|------------|--------------------|---------------------------------------|--------------------------------------|

| 1          | OUTL               | ラインアンプ Lch 出力                         | D                                    |

| 2          | INL                | ラインアンプ Lch 入力                         | C1<br>(BD8876FV)<br>C2<br>(BD8878FV) |

| 3          | SVDD               | ラインアンプ電源                              | -                                    |

| 4          | SGND               | ラインアンプグラウンド                           | -                                    |

| 5          | SDB                | シャットダウン制御<br>(H: active, L: shutdown) | E                                    |

| 6          | GAIN<br>(BD8876FV) | ゲイン切り替え制御<br>(H: 9.0dB, L:6.0dB)      | Е                                    |

| 6          | NC<br>(BD8878FV)   | NC(未接続)                               | -                                    |

| 7          | PVDD               | チャージポンプ電源                             | -                                    |

| 8          | СР                 | フライングコンデンサ正極                          | А                                    |

| 9          | PGND               | チャージポンプグラウンド                          | -                                    |

| 10         | CN                 | フライングコンデンサ負極                          | В                                    |

| 11         | PVSS               | チャージポンプ負電圧出力                          | F                                    |

| 12         | SVSS               | ラインアンプ負電圧入力                           | F                                    |

| 13         | INR                | ラインアンプ Rch 入力                         | C1<br>(BD8876FV)<br>C2<br>(BD8878FV) |

| 14         | OUTR               | ラインアンプ Rch 出力                         | D                                    |

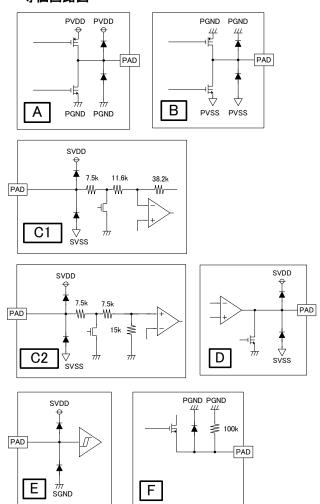

# 等価回路図

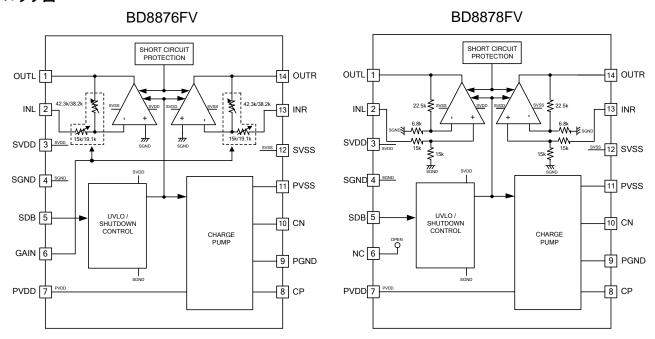

### ブロック図

Figure 3. ブロック図

# 絶対最大定格(Ta = 25°C)

| 項目                          | 記号               | 定格                    | 単位                      |

|-----------------------------|------------------|-----------------------|-------------------------|

| SVDD-PVDD 間電圧               | $V_{DD}$         | 0                     | V                       |

| SGND-PGND 間電圧               | V <sub>G</sub> G | 0                     | V                       |

| SVSS-PVSS 間電圧               | Vss              | 0                     | V                       |

| SVDD, PVDD-SGND or PGND 間電圧 | $V_{DG}$         | -0.3~6.0              | V                       |

| SVSS, PVSS-SGND or PGND 間電圧 | Vsg              | -6.0~0.3              | V                       |

| INSGND 間電圧                  | VIN              | (SVSS-0.3)~(SVDD+0.3) | V                       |

| OUTSGND 間電圧                 | Vout             | (SVSS-0.3)∼(SVDD+0.3) | V                       |

| CP-PGND 間電圧                 | V <sub>CP</sub>  | (PGND-0.3)∼(PVDD+0.3) | V                       |

| CN-PGND 間電圧                 | Vcn              | (PVSS-0.3)∼(PGND+0.3) | V                       |

| SDB-SGND 間電圧                | VsH              | (SGND-0.3)~(SVDD+0.3) | V                       |

| GAIN-SGND 間電圧               | $V_{GA}$         | (SGND-0.3)~(SVDD+0.3) | V                       |

| 入力電流                        | I <sub>IN</sub>  | -10~10                | mA                      |

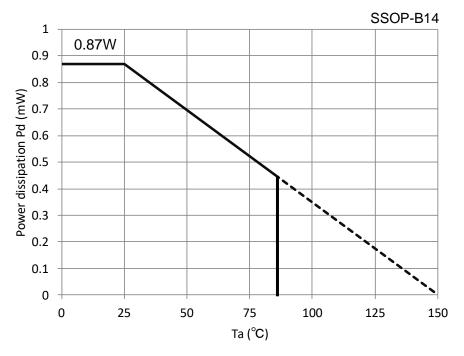

| 許容損失 <sup>(Note 1)</sup>    | P <sub>D</sub>   | 0.87                  | W                       |

| 保存温度範囲                      | T <sub>STG</sub> | -55 <b>~</b> +150     | $^{\circ}\! \mathbb{C}$ |

(Note 1) SSOP-B14:70mm x 70mm x 1.6mm ガラスエポキシ基板実装時 Ta ≥ 25℃の場合は、6.96mW/℃で軽減。 注意:印加電圧及び動作温度範囲などの絶対最大定格を超えた場合は、劣化または破壊に至る可能性があります。また、ショートモードもしくはオープンモードなど、破壊状態を想定できません。絶対最大定格を超えるような特殊モードが想定される場合、ヒューズなど物理的な安全対策を施して頂けるようご検討お願いします。

# 推奨動作範囲

|           | <del>=</del> 7 □                      |     | 規格値 | ** \r |            |

|-----------|---------------------------------------|-----|-----|-------|------------|

| 項目        | 記号                                    | 最小  | 標準  | 最大    | 単位         |

| 電源電圧      | V <sub>SVDD</sub> , V <sub>PVDD</sub> | 3.0 | -   | 5.5   | <b>V</b>   |

| 動作温度範囲    | $T_{OPR}$                             | -40 | -   | +85   | $^{\circ}$ |

| 負荷インピーダンス | ZL                                    | 550 | -   | -     | Ω          |

# 電気的特性

(特に指定のない限り Ta=25 $^{\circ}$ C, SVDD=PVDD=5V, SGND=PGND=0V, SDB=H, GAIN=L [BD8876FV], C<sub>1</sub>=C<sub>2</sub>=1 $\mu$ F, R<sub>L</sub>=10k $\Omega$ , Input coupling capacitor = 1 $\mu$ F)

|                    |                                          | 規格            |            |               |               |         |               |        |                                                                     |

|--------------------|------------------------------------------|---------------|------------|---------------|---------------|---------|---------------|--------|---------------------------------------------------------------------|

| 項目                 | 記号                                       | В             | D8876F     | V             | Е             | 3D8878F | V             | 単位     | 備考                                                                  |

|                    |                                          | 最小            | 標準         | 最大            | 最小            | 標準      | 最大            |        |                                                                     |

| 消費電流               |                                          |               |            | 1             |               |         |               |        |                                                                     |

| 回路電流<br>(シャットダウン時) | Ist                                      | -             | 0.1        | 2             | -             | 0.1     | 2             | μA     | SDB=L                                                               |

| 回路電流<br>(動作時)      | I <sub>DD</sub>                          | -             | 3.2        | 8.2           | -             | 3.2     | 10.5          | mA     | SDB=H<br>無信号入力, R <sub>L</sub> =無負荷                                 |

| SDB 端子 / GAIN 端子   |                                          |               |            |               |               |         |               |        |                                                                     |

| H レベル入力電圧          | V <sub>IH</sub>                          | 0.7 x<br>SVDD | -          | -             | 0.7 x<br>SVDD | -       | -             | V      |                                                                     |

| L レベル入力電圧          | VIL                                      | -             | 1          | 0.3 x<br>SVDD | -             | -       | 0.3 x<br>SVDD | V      |                                                                     |

| 入カリーク電流            | ILEAK                                    | -             | -          | ±1            | -             | -       | ±1            | μA     |                                                                     |

| ラインアンプ             |                                          |               |            |               |               |         |               |        |                                                                     |

| 起動時間               | t <sub>SON</sub>                         | -             | 470        | -             | -             | 470     | -             | µsec   | SDB=L→H                                                             |

| 入力オフセット電圧          | V <sub>IS</sub>                          | -             | ±0.5       | ±5            | -             | ±1      | ±10           | mV     |                                                                     |

| 最大出力電圧             | Vouт                                     | 2.5           | 3.5        | -             | 2.05          | 3.0     | -             | Vrms   | f=1kHz , THD+N≦-40dB,<br>20kHz LPF                                  |

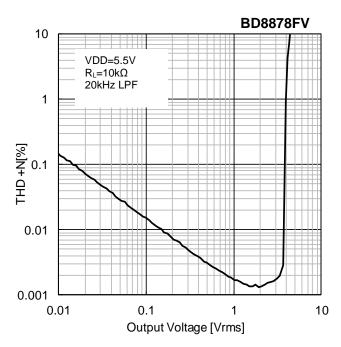

| 全高調波歪率+ノイズ         | THD+N                                    | -             | 0.003      | 0.032         | -             | 0.003   | 0.032         | %      | f=1kHz, VOUT=2Vrms,<br>20kHz LPF                                    |

| 入力インピーダンス          | Z <sub>IN1</sub> *1                      | 12            | 19         | 26            | 20            | 30      | 40            | kΩ     | *1 GAIN=L (6dB mode)                                                |

| 7,3122 727         | Z <sub>IN2</sub> *2                      | 10            | 15         | 20            | 20            | 00      | 10            | 1132   | *2 GAIN=H (9dB mode)                                                |

| ゲイン                | A <sub>V1</sub> *1<br>A <sub>V2</sub> *2 | 5.0<br>8.0    | 6.0<br>9.0 | 7.0<br>10.0   | 5.7           | 6.7     | 7.7           | dB     | *1 GAIN=L (6dB mode)<br>*2 GAIN=H (9dB mode)                        |

| ゲインミスマッチング         | ΔΑν                                      | -             | 1          | -             | -             | 1       | -             | %      |                                                                     |

| 出力雑音電圧             | VN                                       | -             | 8          | -             | -             | 10      | -             | μVrms  | 20kHz LPF<br>+A-Weight フィルタ                                         |

| スルーレート             | SR                                       | -             | 3.0        | -             | -             | 3.0     | -             | V/µsec |                                                                     |

| 最大負荷容量             | CL                                       | -             | -          | 250           | -             | -       | 250           | pF     |                                                                     |

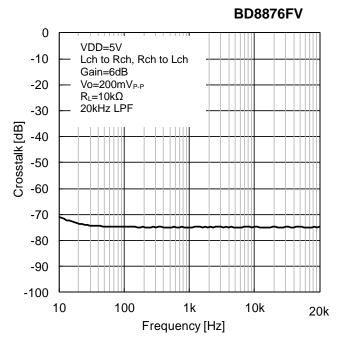

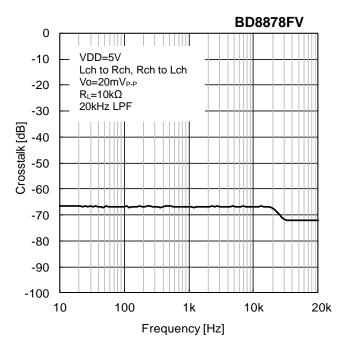

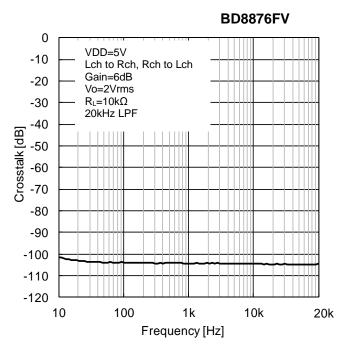

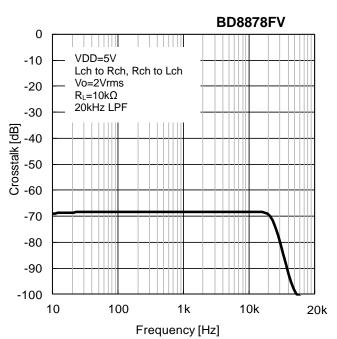

| チャネル間クロストーク        | СТ                                       | -             | -80        | -             | -             | -65     | -             | dB     | f=1kHz, V <sub>OUT</sub> =200mV <sub>P-P</sub> ,<br>1kHz BPF を使用    |

| 電源電圧変動除去比          | PSRR                                     | -             | -65        | -             | -             | -65     | -             | dB     | f=1kHz, V <sub>ripple</sub> =100mV <sub>P-P</sub> ,<br>1kHz BPF を使用 |

| チャージポンプ<br>発振周波数   | fosc                                     | 150           | 300        | 450           | 150           | 300     | 450           | kHz    |                                                                     |

# 特性データ(参考データ)

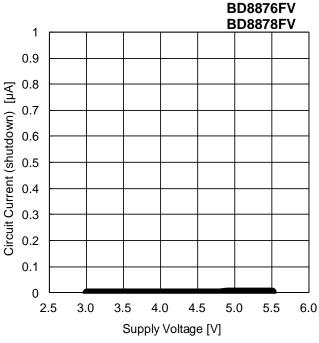

Figure 4.

Circuit Current (Shutdown)

vs. Supply Voltage

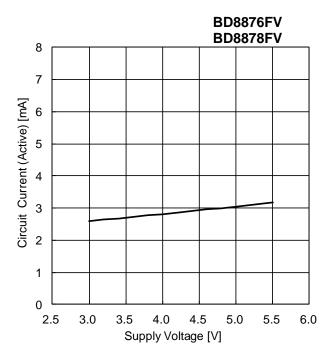

Figure 5.

Circuit Current (Active)

vs. Supply Voltage

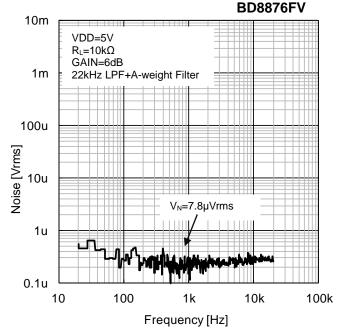

Figure 6. Noise Level (BD8876FV)

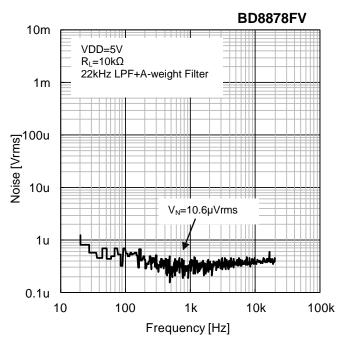

Figure 7. Noise Level (BDD8878FV)

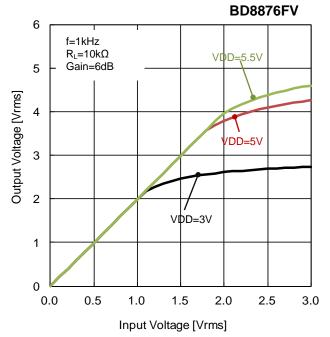

Figure 8.

Output Voltage vs. Input Voltage (BD8876FV, 6dB)

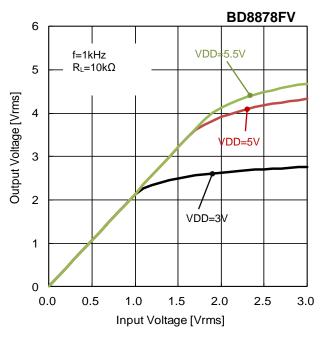

Figure 10.

Output Voltage vs. Input Voltage (BD8878FV)

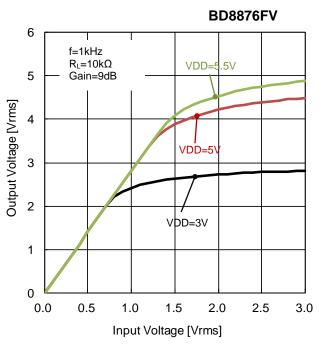

Figure 9. Output Voltage vs. Input Voltage (BD8876FV, 9dB)

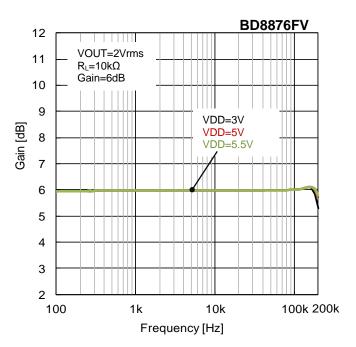

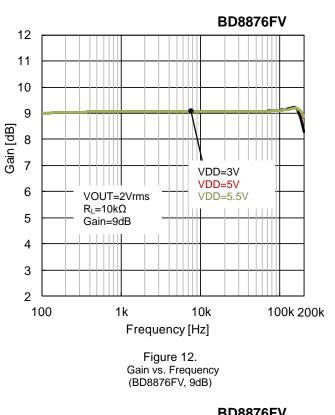

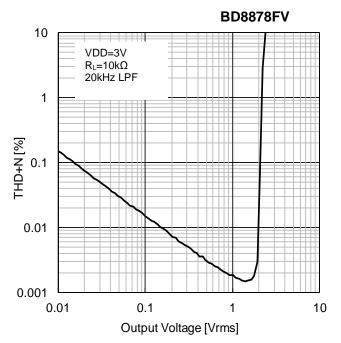

Figure 11. Gain vs. Frequency (BD8876FV, 6dB)

**BD8878FV** 12 11 10 VDD=3V VDD=5V 9 VDD=5.5V Gain [dB] 7 6 VOUT=2Vrms 5  $R_L=10k\Omega$ 4 3 2 100k 200k 10k 100 Frequency [Hz]

Figure 13. Gain vs. Frequency (BD8878FV)

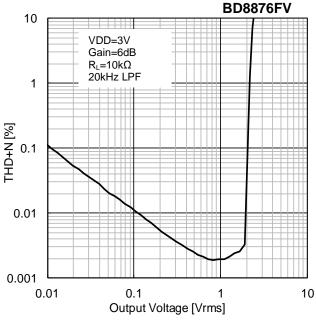

Figure 14. THD+N vs. Output Voltage (BD8876FV, 3V)

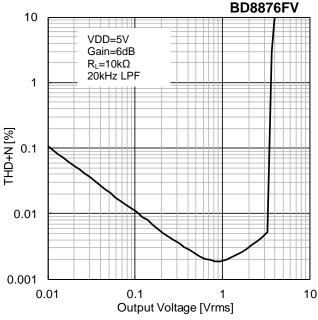

Figure 15. THD+N vs. Output Voltage (BD8876FV, 5V)

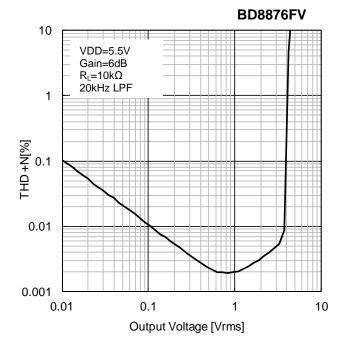

Figure 16. THD+N vs. Output Voltage (BD8876FV, 5.5V)

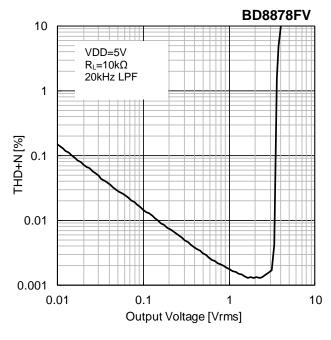

Figure 18. THD+N vs. Output Voltage (BD8878FV, 5V)

Figure 17. THD+N vs. Output Voltage (BD8878FV, 3V)

Figure 19. THD+N vs. Output Voltage (BD8878FV, 5.5V)

(特に指定のない限り Ta=25℃, SVDD=PVDD=5V, SGND=PGND=0V, SDB=H, GAIN=L [BD8876FV], C₁=C₂=1μF, R∟=10kΩ, Input coupling capacitor = 1μF) ※以下の特性データでは、SVDD=PVDD= "VDD" と表します。

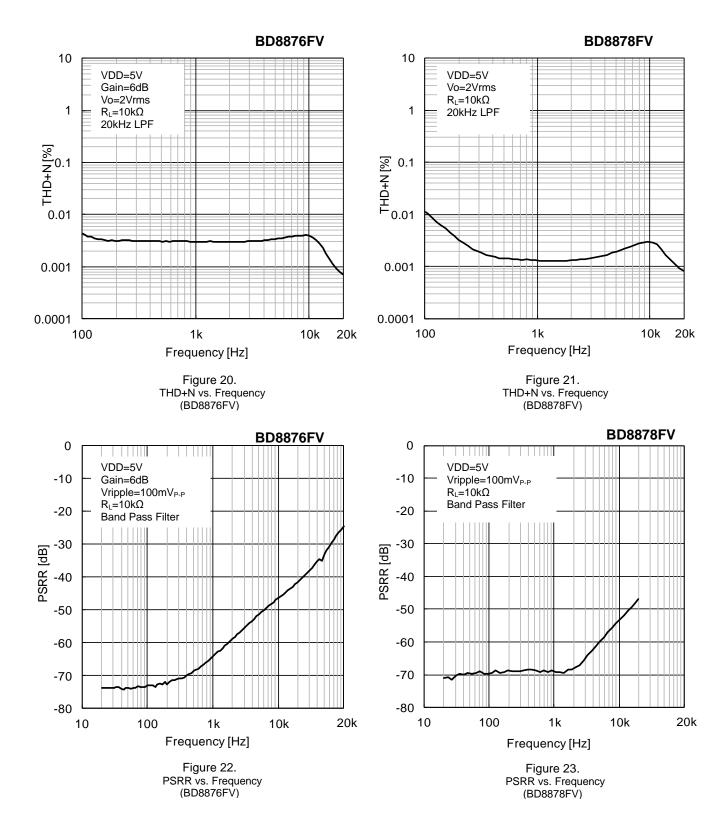

Figure 24. Crosstalk vs. Frequency (BD8876FV, 200mV<sub>P-P</sub>)

Figure 26. Crosstalk vs. Frequency (BD8878FV, 200mV<sub>P-P</sub>)

Figure 25. Crosstalk vs. Frequency (BD8876FV, 2Vrms)

Figure 27. Crosstalk vs. Frequency (BD8878FV, 2Vrms)

#### 応用回路例

Figure 28. BD8876FV 応用回路例

Figure 29. BD8878FV 応用回路例

※PVSS と SVSS は IC 内部で接続されていますが、外部で必ず短絡してご使用ください。

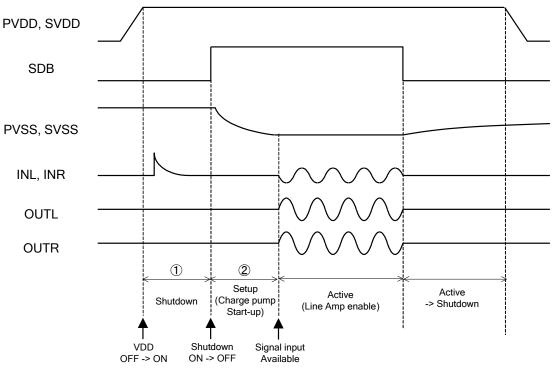

### タイミングチャート

<電源立ち上げ/立ち下げシーケンス>

Figure 30. 電源立ち上げシーケンス図

# ① VDD(PVDD, SVDD): ON~シャットダウンを解除するまでの時間

電源(PVDD, SVDD)を投入すると入力カップリングコンデンサが充電され、下図 Figure.31 のように IC 入力端子の電圧 Vin は変動します。入力カップリングコンデンサを充電する時定数(以下、充電時定数)  $\tau$  は入力カップリングコンデンサ Cin と IC 内部の入力インピーダンス Rin によって以下の式(1)で表せます。充電時定数  $\tau$  を小さくするためにシャットダウン時の入力インピーダンス Rin は通常動作時よりも低い  $\tau$ .5k $\tau$  (Typ)になっています。この入力電圧が変動している期間にシャットダウンを解除するとポップ音の原因になります。入力電圧変動中はシャットダウンを解除せず、少なくとも  $\tau$  6  $\tau$  後にシャットダウン解除(SDB = "L"  $\tau$ " H")することを推奨します。

Figure 31. 入力カップリングコンデンサによる入力端子電圧変動

$$\tau = R_{in}C_{in} \quad \cdots (1)$$

(計算例) Cin=1.0 $\mu$ F の場合、 Rin=7.5 $k\Omega$  (typ)であるから  $\tau$  =7.5 $k\Omega$  × 1.0 $\mu$ F = 7.5 msec(typ) 6  $\tau$  =6 × 7.5msec = 45 msec(typ)

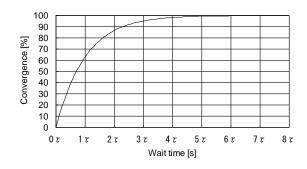

Figure 32. Wait time と収束率(参考データ:計算値)

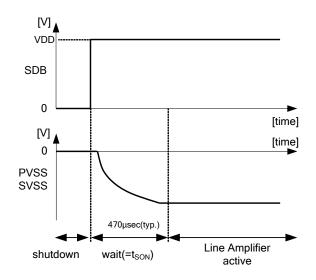

#### ② シャットダウン解除からラインアンプ起動までの時間

シャットダウンを解除すると、チャージポンプ回路が動作開始します。チャージポンプ回路を立上げている途中の不正な出力を防止するため、シャットダウン解除から"tson(起動時間=470μsec typ)"の間、ラインアンプはパワーオンしません。ラインアンプの起動は tson (470μsec) 後になりますので、オーディオ信号も tson 後に入力してください。

Figure 33. ラインアンプ動作可能領域

# 機能ブロック動作説明/アプリケーション情報

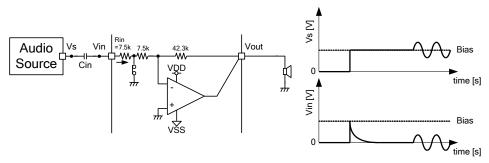

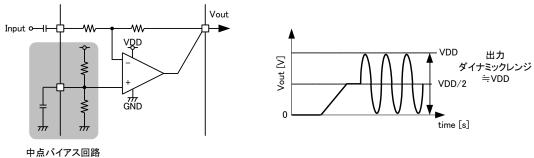

従来のラインアンプ構成を Figure 34 に示します。この構成では中点バイアス(VDD/2)を基準に信号出力を行います。 そのため、アンプの出力ダイナミックレンジは最大で VDD に制限されます。

Figure 34. 従来のラインアンプ構成

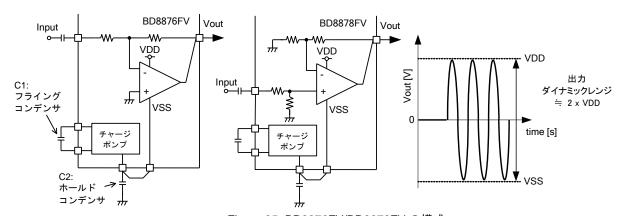

BD8876FV/BD8878FVの構成を Figure 35 に示します。この構成ではチャージポンプ回路により負電圧を発生させることで、グラウンドレベルを基準に信号出力を行います。そのため、アンプの出力ダイナミックレンジはおよそ VDD の 2 倍となります。これにより、従来 5V 単一電源で出力することができなかった 2Vrms (5.657V<sub>P-P</sub>)出力が可能になります。

Figure 35. BD8876FV/BD8878FV の構成

#### ■チャージポンプ回路

負電圧発生回路はチャージポンプ回路で構成しており、電源電圧(PVDD)から負電圧(PVSS)を出力します。 チャージポンプのパワー制御は Table1.に示すとおり SDB の論理に従います。

Table 1. チャージポンプ回路の制御表

| SDB | チャージポンプ制御 |

|-----|-----------|

| L   | パワーダウン    |

| Η   | パワーオン     |

# 【フライングコンデンサ / ホールドコンデンサについて】

フライングコンデンサ(Figure 35. C1)及びホールドコンデンサ(Figure 35. C2)はチャージポンプの特性に大きく影響します。C1,C2 には低 ESR で温度や印加電圧による変動が小さいコンデンサを使用してください。また、出来るだけIC の近傍で接続してください。

#### 【過電流保護機能】

本チャージポンプには過電流保護機能が搭載されています。この機能により、チャージポンプの端子(CP, CN, PVSS, SVSS)が地絡等の異常接続状態にあるときに、IC に発生する電流を制限することができます。

#### ■ラインアンプ

ラインアンプは電源電圧(SVDD)と負電圧(SVSS)によってグラウンド(SGND)を基準として動作し、5V の単一電源で負荷  $10k\Omega$ に対して 2Vrms の出力が可能です。また BD8876FV は GAIN 端子によって利得を 6dB または 9dB に設定することができます。 BD8878FV は 6.7dB で固定です。 ラインアンプは Table 2.に示すとおり SDB の論理によって L チャネルと R チャネルが同時制御されます。またラインアンプには過電流保護回路を内蔵しており、出力短絡等による過電流発生時には出力電流を制限し、IC の破壊を防止します。

Table 2. ラインアンプ回路の制御表

| SDB | ラインアンプ制御 |

|-----|----------|

| L   | パワーダウン   |

| Н   | パワーオン    |

# 【入力カップリングコンデンサ】

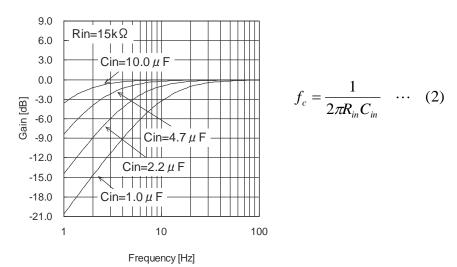

BD8876FV/BD8878FV の入力 DC レベルは 0V(SGND)です。そのため通常、信号源デバイスとの接続には入力カップリングコンデンサが必要です。この入力カップリングコンデンサ Cin と IC の入力インピーダンス Rin によってハイパスフィルタ特性を構成するため、低周波で信号減衰が起こります。BD8876FV の入力インピーダンス Rin は 15k $\Omega$  (Typ, Gain=+9.0dB)で、BD8878FV の Rin は 30 k $\Omega$  (Typ)です。

このハイパスフィルタのカットオフ周波数は以下の式(2)で決まります。

Figure 36. 入力カップリングコンデンサと周波数特性(参考データ:計算値)

また、入力カップリングコンデンサによって全高調波歪率の劣化が起こります。そのため、部品の選定にはコンデンサの印加電圧依存性や温度特性をご確認ください。

#### ■低電圧保護機能 (UVLO)

BD8876FV, BD8878FV は、推奨動作電圧範囲外の低い電源電圧領域における IC の異常動作を防止するため、低電圧保護(UVLO: <u>Under Voltage Lock Out</u>) 機能を内蔵しています。低電圧検出電圧は 2.8V (Typ)です。 またこの低電圧検出によるパワー制御は IC 全体を対象として働き、チャージポンプとラインアンプの両方をパワーダウンします。低電源電圧を検出して UVLO 機能が動作したのちに、電源電圧が推奨動作範囲(3.0V~)まで上がれば自動復帰します。

#### 熱損失について

Figure 37. 熱軽減率曲線

測定状態: ローム標準 ガラスエポキシ基板実装 基板サイズ: 74.2mm×74.2mm×1.6mm (片面基板)

材質:FR4

#### 使用上の注意

#### 1. 電源の逆接続について

電源コネクタの逆接続により LSI が破壊する恐れがあります。逆接続破壊保護用として外部に電源と LSI の電源端子間にダイオードを入れるなどの対策を施してください。

#### 2. 電源ラインについて

基板パターンの設計においては、電源ラインの配線は、低インピーダンスになるようにしてください。グラウンドラインについても、同様のパターン設計を考慮してください。また、LSIのすべての電源端子について電源ーグラウンド端子間にコンデンサを挿入するとともに、電解コンデンサ使用の際は、低温で容量ぬけが起こることなど使用するコンデンサの諸特性に問題ないことを十分ご確認のうえ、定数を決定してください。

#### 3. グラウンド電位について

機能的に負電位を入出力する端子を除き、グラウンド端子の電位はいかなる動作状態においても、最低電位になるようにしてください。また実際に過渡現象を含め、グラウンド端子、負電位入出力端子以外の端子がグラウンド以下の電圧にならないようにしてください。

#### 4. グラウンド配線パターンについて

小信号グラウンドと大電流グラウンドがある場合、大電流グラウンドパターンと小信号グラウンドパターンは分離し、パターン配線の抵抗分と大電流による電圧変化が小信号グラウンドの電圧を変化させないように、セットの基準点で 1 点アースすることを推奨します。外付け部品のグラウンドの配線パターンも変動しないよう注意してください。グラウンドラインの配線は、低インピーダンスになるようにしてください。

#### 5. 熱設計について

万一、許容損失を超えるようなご使用をされますと、チップ温度上昇により、IC 本来の性質を悪化させることにつながります。本仕様書の絶対最大定格に記載しています許容損失を超える場合は基板サイズを大きくする、放熱用銅箔面積を大きくする、放熱板を使用するなどの対策をして、許容損失を超えないようにしてください。

#### 6. 推奨動作条件について

この範囲であればほぼ期待通りの特性を得ることができる範囲です。電気特性については各項目の条件下において保証されるものです。

#### 7. ラッシュカレントについて

IC 内部論理回路は、電源投入時に論理不定状態で、瞬間的にラッシュカレントが流れる場合がありますので、電源カップリング容量や電源、グラウンドパターン配線の幅、引き回しに注意してください。

#### 8. 強電磁界中の動作について

強電磁界中でのご使用では、まれに誤動作する可能性がありますのでご注意ください。

# 9. セット基板での検査について

セット基板での検査時に、インピーダンスの低いピンにコンデンサを接続する場合は、IC にストレスがかかる恐れがあるので、1 工程ごとに必ず放電を行ってください。静電気対策として、組立工程にはアースを施し、運搬や保存の際には十分ご注意ください。また、検査工程での治具への接続をする際には必ず電源を OFF にしてから接続し、電源を OFF にしてから取り外してください。

#### 10. 端子間ショートと誤装着について

プリント基板に取り付ける際、IC の向きや位置ずれに十分注意してください。誤って取り付けた場合、IC が破壊する恐れがあります。また、出力と電源及びグラウンド間、出力間に異物が入るなどしてショートした場合についても破壊の恐れがあります。

# 11. 未使用の入力端子の処理について

CMOS トランジスタの入力は非常にインピーダンスが高く、入力端子をオープンにすることで論理不定の状態になります。これにより内部の論理ゲートの p チャネル、n チャネルトランジスタが導通状態となり、不要な電源電流が流れます。また 論理不定により、想定外の動作をすることがあります。よって、未使用の端子は特に仕様書上でうたわれていない限り、適切な電源、もしくはグランドに接続するようにしてください。

#### 使用上の注意 ― 続き

#### 12. 各入力端子について

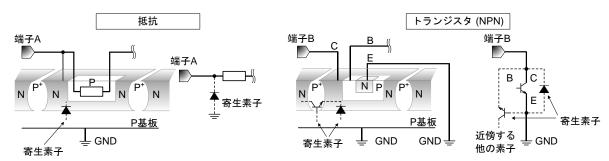

本 IC はモノリシック IC であり、各素子間に素子分離のための P+アイソレーションと、P 基板を有しています。 この P 層と各素子の N 層とで P-N 接合が形成され、各種の寄生素子が構成されます。

例えば、下図のように、抵抗とトランジスタが端子と接続されている場合、

〇抵抗では、GND>(端子 A)の時、トランジスタ(NPN)では GND > (端子 B)の時、P-N 接合が寄生ダイオードとして動作します。

〇また、トランジスタ(NPN)では、GND > (端子 B)の時、前述の寄生ダイオードと近接する他の素子の N 層によって寄生の NPN トランジスタが動作します。

IC の構造上、寄生素子は電位関係によって必然的にできます。寄生素子が動作することにより、回路動作の干渉を引き起こし、誤動作、ひいては破壊の原因ともなり得ます。したがって、入出力端子に GND(P 基板)より低い電圧を印加するなど、寄生素子が動作するような使い方をしないよう十分に注意してください。アプリケーションにおいて電源端子と各端子電圧が逆になった場合、内部回路または素子を損傷する可能性があります。例えば、外付けコンデンサに電荷がチャージされた状態で、電源端子が GND にショートされた場合などです。また、電源端子直列に逆流防止のダイオードもしくは各端子と電源端子間にバイパスのダイオードを挿入することを推奨します。

Figure 38. モノリシック IC 構造例

#### 13. セラミック・コンデンサの特性変動について

外付けコンデンサに、セラミック・コンデンサを使用する場合、直流バイアスによる公称容量の低下、及び温度などによる容量の変化を考慮の上定数を決定してください。

#### 14. 安全動作領域について

本製品を使用する際には、出カトランジスタが絶対最大定格及び ASO を越えないよう設定してください。

#### 15. 温度保護回路について

IC を熱破壊から防ぐための温度保護回路を内蔵しております。許容損失範囲内でご使用いただきますが、万が一許容損失を超えた状態が継続すると、チップ温度 Tj が上昇し温度保護回路が動作し出力パワー素子が OFF します。その後チップ温度 Tj が低下すると回路は自動で復帰します。なお、温度保護回路は絶対最大定格を超えた状態での動作となりますので、温度保護回路を使用したセット設計などは、絶対に避けてください。

#### 16. 過電流保護回路について

出力には電流能力に応じた過電流保護回路が内部に内蔵されているため、負荷ショート時には IC 破壊を防止しますが、この保護回路は突発的な事故による破壊防止に有効なもので、連続的な保護回路動作、過渡時でのご使用に対応するものではありません。

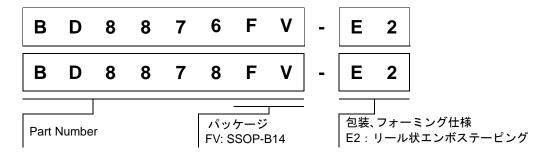

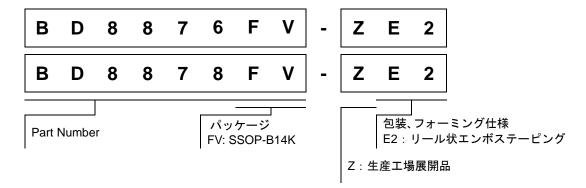

# 発注形名情報

# ラインアップ

|       | BD8876FV                          | BD8878FV |  |

|-------|-----------------------------------|----------|--|

| アンプ方式 | 反転アンプ                             | 非反転アンプ   |  |

| ゲイン   | +6.0dB / +9.0dB<br>(GAIN ピンによる切替) | +6.7dB   |  |

| パッケージ | SSOP-B14                          |          |  |

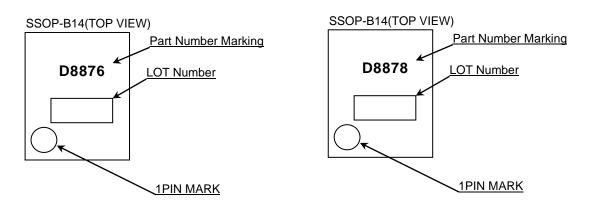

# 標印図

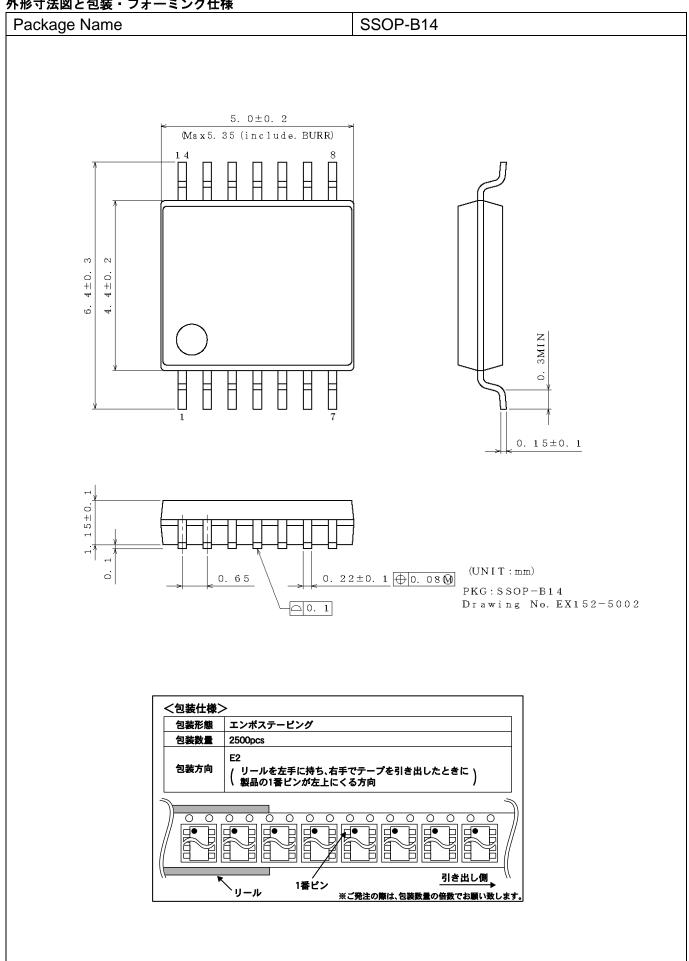

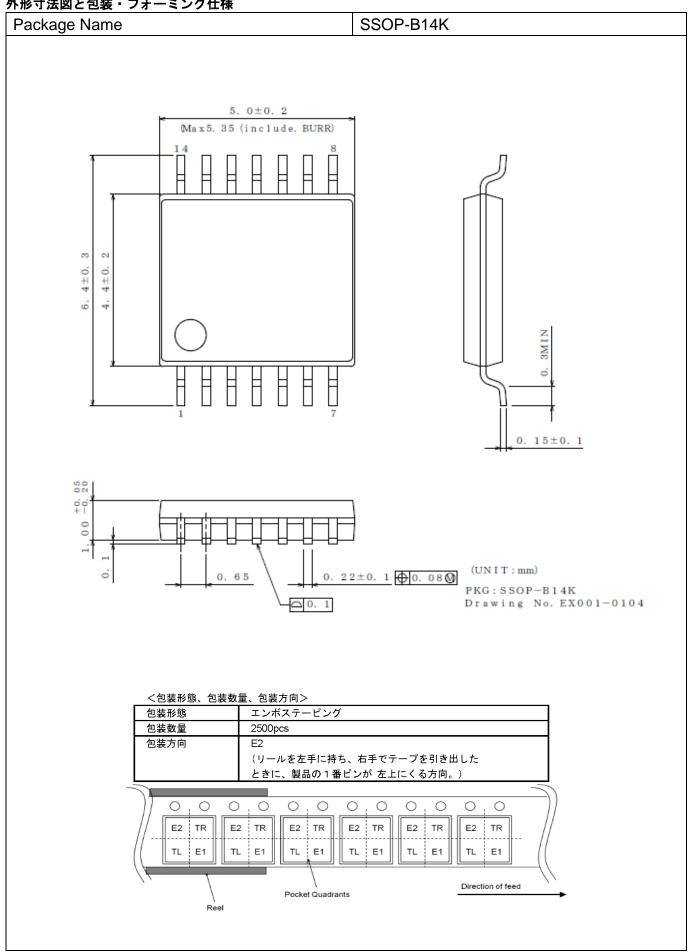

# 外形寸法図と包装・フォーミング仕様

# 改訂履歴

| A          |          |                                            |

|------------|----------|--------------------------------------------|

| Date       | Revision | Changes                                    |

| 2015/10/30 | 001      | 初版                                         |

| 2021/01/18 | 002      | パッケージ(SSOP-B14K)生産工場展開品の追加(限定)P.20-2,P20-3 |

# 発注形名情報

# ラインアップ

|       | BD8876FV                          | BD8878FV |  |

|-------|-----------------------------------|----------|--|

| アンプ方式 | 反転アンプ                             | 非反転アンプ   |  |

| ゲイン   | +6.0dB / +9.0dB<br>(GAIN ピンによる切替) | +6.7dB   |  |

| パッケージ | SSOP-B14K                         |          |  |

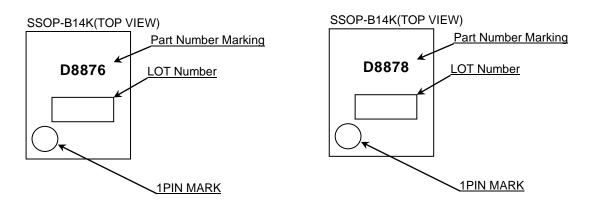

# 標印図

# 外形寸法図と包装・フォーミング仕様

# ご注意

#### ローム製品取扱い上の注意事項

1. 本製品は一般的な電子機器(AV機器、OA機器、通信機器、家電製品、アミューズメント機器等)への使用を意図して設計・製造されております。したがいまして、極めて高度な信頼性が要求され、その故障や誤動作が人の生命、身体への危険もしくは損害、又はその他の重大な損害の発生に関わるような機器又は装置(医療機器(Note 1)、輸送機器、交通機器、航空宇宙機器、原子力制御装置、燃料制御、カーアクセサリを含む車載機器、各種安全装置等)(以下「特定用途」という)への本製品のご使用を検討される際は事前にローム営業窓口までご相談くださいますようお願い致します。ロームの文書による事前の承諾を得ることなく、特定用途に本製品を使用したことによりお客様又は第三者に生じた損害等に関し、ロームは一切その責任を負いません。

(Note 1) 特定用途となる医療機器分類

|   | 日本      | USA      | EU         | 中国   |

|---|---------|----------|------------|------|

| Ī | CLASSⅢ  | CLACCIII | CLASS II b | Ⅲ 米百 |

|   | CLASSIV | CLASSⅢ   | CLASSⅢ     | Ⅲ類   |

- 2. 半導体製品は一定の確率で誤動作や故障が生じる場合があります。万が一、かかる誤動作や故障が生じた場合であっても、本製品の不具合により、人の生命、身体、財産への危険又は損害が生じないように、お客様の責任において次の例に示すようなフェールセーフ設計など安全対策をお願い致します。

- ①保護回路及び保護装置を設けてシステムとしての安全性を確保する。

- ②冗長回路等を設けて単一故障では危険が生じないようにシステムとしての安全を確保する。

- 3. 本製品は、一般的な電子機器に標準的な用途で使用されることを意図して設計・製造されており、下記に例示するような特殊環境での使用を配慮した設計はなされておりません。したがいまして、下記のような特殊環境での本製品のご使用に関し、ロームは一切その責任を負いません。本製品を下記のような特殊環境でご使用される際は、お客様におかれまして十分に性能、信頼性等をご確認ください。

- ①水・油・薬液・有機溶剤等の液体中でのご使用

- ②直射日光・屋外暴露、塵埃中でのご使用

- ③潮風、Cl<sub>2</sub>、H<sub>2</sub>S、NH<sub>3</sub>、SO<sub>2</sub>、NO<sub>2</sub> 等の腐食性ガスの多い場所でのご使用

- ④静電気や電磁波の強い環境でのご使用

- ⑤発熱部品に近接した取付け及び当製品に近接してビニール配線等、可燃物を配置する場合。

- ⑥本製品を樹脂等で封止、コーティングしてのご使用。

- ⑦はんだ付けの後に洗浄を行わない場合(無洗浄タイプのフラックスを使用される場合は除く。ただし、残渣については十分に確認をお願いします。)又は、はんだ付け後のフラックス洗浄に水又は水溶性洗浄剤をご使用の場合

- ⑧本製品が結露するような場所でのご使用。

- 4. 本製品は耐放射線設計はなされておりません。

- 5. 本製品単体品の評価では予測できない症状・事態を確認するためにも、本製品のご使用にあたってはお客様製品に実装された状態での評価及び確認をお願い致します。

- 6. パルス等の過渡的な負荷 (短時間での大きな負荷) が加わる場合は、お客様製品に本製品を実装した状態で必ず その評価及び確認の実施をお願い致します。また、定常時での負荷条件において定格電力以上の負荷を印加されますと、 本製品の性能又は信頼性が損なわれるおそれがあるため必ず定格電力以下でご使用ください。

- 7. 電力損失は周囲温度に合わせてディレーティングしてください。また、密閉された環境下でご使用の場合は、必ず温度 測定を行い、最高接合部温度を超えていない範囲であることをご確認ください。

- 8. 使用温度は納入仕様書に記載の温度範囲内であることをご確認ください。

- 9. 本資料の記載内容を逸脱して本製品をご使用されたことによって生じた不具合、故障及び事故に関し、ロームは一切その責任を負いません。

#### 実装及び基板設計上の注意事項

- 1. ハロゲン系(塩素系、臭素系等)の活性度の高いフラックスを使用する場合、フラックスの残渣により本製品の性能 又は信頼性への影響が考えられますので、事前にお客様にてご確認ください。

- 2. はんだ付けは、表面実装製品の場合リフロー方式、挿入実装製品の場合フロー方式を原則とさせて頂きます。なお、表面実装製品をフロー方式での使用をご検討の際は別途ロームまでお問い合わせください。その他、詳細な実装条件及び手はんだによる実装、基板設計上の注意事項につきましては別途、ロームの実装仕様書をご確認ください。

Notice-PGA-J Rev.004

# 応用回路、外付け回路等に関する注意事項

- 1. 本製品の外付け回路定数を変更してご使用になる際は静特性のみならず、過渡特性も含め外付け部品及び本製品のバラッキ等を考慮して十分なマージンをみて決定してください。

- 2. 本資料に記載された応用回路例やその定数などの情報は、本製品の標準的な動作や使い方を説明するためのもので、 実際に使用する機器での動作を保証するものではありません。したがいまして、お客様の機器の設計において、回路や その定数及びこれらに関連する情報を使用する場合には、外部諸条件を考慮し、お客様の判断と責任において行って ください。これらの使用に起因しお客様又は第三者に生じた損害に関し、ロームは一切その責任を負いません。

## 静電気に対する注意事項

本製品は静電気に対して敏感な製品であり、静電放電等により破壊することがあります。取り扱い時や工程での実装時、保管時において静電気対策を実施のうえ、絶対最大定格以上の過電圧等が印加されないようにご使用ください。特に乾燥環境下では静電気が発生しやすくなるため、十分な静電対策を実施ください。(人体及び設備のアース、帯電物からの隔離、イオナイザの設置、摩擦防止、温湿度管理、はんだごてのこて先のアース等)

# 保管・運搬上の注意事項

- 1. 本製品を下記の環境又は条件で保管されますと性能劣化やはんだ付け性等の性能に影響を与えるおそれがあります のでこのような環境及び条件での保管は避けてください。

- ①潮風、Cl<sub>2</sub>、H<sub>2</sub>S、NH<sub>3</sub>、SO<sub>2</sub>、NO<sub>2</sub>等の腐食性ガスの多い場所での保管

- ②推奨温度、湿度以外での保管

- ③直射日光や結露する場所での保管

- ④強い静電気が発生している場所での保管

- 2. ロームの推奨保管条件下におきましても、推奨保管期限を経過した製品は、はんだ付け性に影響を与える可能性があります。推奨保管期限を経過した製品は、はんだ付け性を確認したうえでご使用頂くことを推奨します。

- 3. 本製品の運搬、保管の際は梱包箱を正しい向き(梱包箱に表示されている天面方向)で取り扱いください。天面方向が 遵守されずに梱包箱を落下させた場合、製品端子に過度なストレスが印加され、端子曲がり等の不具合が発生する 危険があります。

- 4. 防湿梱包を開封した後は、規定時間内にご使用ください。規定時間を経過した場合はベーク処置を行ったうえでご使用ください。

#### 製品ラベルに関する注意事項

本製品に貼付されている製品ラベルに2次元バーコードが印字されていますが、2次元バーコードはロームの社内管理のみを目的としたものです。

#### 製品廃棄上の注意事項

本製品を廃棄する際は、専門の産業廃棄物処理業者にて、適切な処置をしてください。

### 外国為替及び外国貿易法に関する注意事項

本製品は外国為替及び外国貿易法に定める規制貨物等に該当するおそれがありますので輸出する場合には、ロームにお問い合わせください。

#### 知的財産権に関する注意事項

- 1. 本資料に記載された本製品に関する応用回路例、情報及び諸データは、あくまでも一例を示すものであり、これらに関する第三者の知的財産権及びその他の権利について権利侵害がないことを保証するものではありません。

- 2. ロームは、本製品とその他の外部素子、外部回路あるいは外部装置等(ソフトウェア含む)との組み合わせに起因して生じた紛争に関して、何ら義務を負うものではありません。

- 3. ロームは、本製品又は本資料に記載された情報について、ロームもしくは第三者が所有又は管理している知的財産権 そ の他の権利の実施又は利用を、明示的にも黙示的にも、お客様に許諾するものではありません。 ただし、本製品を通 常の用法にて使用される限りにおいて、ロームが所有又は管理する知的財産権を利用されることを妨げません。

# その他の注意事項

- 1. 本資料の全部又は一部をロームの文書による事前の承諾を得ることなく転載又は複製することを固くお断り致します。

- 2. 本製品をロームの文書による事前の承諾を得ることなく、分解、改造、改変、複製等しないでください。

- 3. 本製品又は本資料に記載された技術情報を、大量破壊兵器の開発等の目的、軍事利用、あるいはその他軍事用途目的で使用しないでください。

- 4. 本資料に記載されている社名及び製品名等の固有名詞は、ローム、ローム関係会社もしくは第三者の商標又は登録商標です。

Notice-PGA-J Rev.004

# 一般的な注意事項

- 1. 本製品をご使用になる前に、本資料をよく読み、その内容を十分に理解されるようお願い致します。本資料に記載される注意事項に反して本製品をご使用されたことによって生じた不具合、故障及び事故に関し、ロームは一切その責任を負いませんのでご注意願います。

- 2. 本資料に記載の内容は、本資料発行時点のものであり、予告なく変更することがあります。本製品のご購入及びご使用に際しては、事前にローム営業窓口で最新の情報をご確認ください。

- 3. ロームは本資料に記載されている情報は誤りがないことを保証するものではありません。万が一、本資料に記載された情報の誤りによりお客様又は第三者に損害が生じた場合においても、ロームは一切その責任を負いません。

Notice – WE Rev.001