## 絶縁 DC/DC コンバータ IC

# 車載用スイッチング MOSFET 内蔵 絶縁型フライバック・コンバータ IC

## BD7F105EFJ-C

#### 概要

BD7F105EFJ-C はフォトカプラ不要の絶縁型フライバック・コンバータです。フォトカプラやトランスの三次巻線によるフィードバック回路は不要となり、セット部品の削減に貢献します。さらに独自の適応型 ON 時間制御テクノロジの採用によって、高速負荷応答を実現します。また多くの保護機能を内蔵しており、高い信頼性を実現する絶縁型電源アプリケーションの設計を可能にします。

## 特長

- ■AEC-Q100 対応(Note 1)

- ■フォトカプラ、トランスの三次巻線が不要

- ■二本の外付け抵抗とトランス巻数比で出力電圧を設定

- ■独自の適応型 ON 時間制御テクノロジを採用 高速負荷応答を実現

- ■高効率の軽負荷モード対応 (PFM 動作)

- ■シャットダウン/Enable 制御

- ■60 V スイッチング MOSFET 内蔵

- ■周波数スペクトラム拡散

- ■ソフトスタート機能

- ■負荷電流補償機能

- ■各種保護機能

入力低電圧保護(UVLO) 過電流保護(OCP)、過熱保護(TSD) REF 端子オープン保護(REFOPEN)

短絡保護 (SCP)、 Battery ショート保護 (BSP)

■ HTSOP-J8 パッケージ

(Note 1) Grade1

#### 重要特性

■ 入力電圧範囲:

VIN 端子 3.4 V ~ 42.0 V 8W 端子 60 V (Max) 363 kHz (Typ) 基準電圧精度: ±2.8 % (Typ) りャットダウン時電流: 0 μA (Typ)

■ 動作周囲温度範囲: -40 °C ~ +125 °C

パッケージ HTSOP-J8 **W (Typ)** x **D (Typ)** x **H (Max)** 4.9 mm x 6.0 mm x 1.0 mm

## 用途

- 車載向け絶縁電源 (E-Comp, Inverter etc)

- 産業機器向け絶縁電源

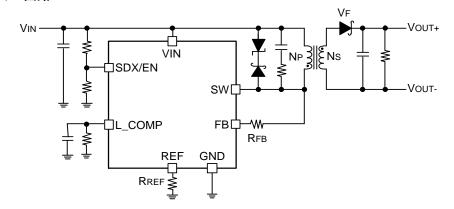

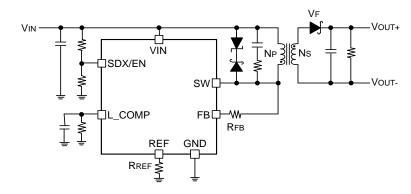

## 基本アプリケーション回路

〇製品構造:シリコンを主材料とした半導体集積回路 〇耐放射線設計はしておりません

## 目 次

| 概要                                           | 1  |

|----------------------------------------------|----|

| 特長                                           | 1  |

| 重要特性                                         | 1  |

|                                              |    |

| 用途                                           |    |

|                                              |    |

| 基本アプリケーション回路                                 |    |

| 目 次                                          | 2  |

| 端子配置図                                        | 3  |

| 端子説明                                         | 3  |

| ブロック図                                        | 3  |

| 各ブロック動作説明                                    | 4  |

| 1 内部電源 (INTERNAL REGULATOR)                  |    |

| 2 入力低電圧保護機能 (UVLO)                           | 4  |

| 3 過熱保護 (TSD)                                 |    |

| 4 SW 端子電圧検出部 (SW VOLTAGE DETECTION)          |    |

| 5 ソフトスタート部 (SOFT START)                      |    |

| 6 PWM コンパレータ部 (PWM COMPARATOR)               |    |

| 7 適応型 ON 時間制御部 (ADAPTIVE ON TIME CONTROLLER) |    |

| 8 最大周波数制限機能 (MAX FREQ)                       |    |

| 9 ドライバ部 (DRIVER)                             |    |

| 10 スイッチング用 MOSFET (Nch MOSFET)               | 5  |

| 11 負荷電流補償部 (LOAD COMPENSATION)               | 6  |

| 12 周波数スペクトラム拡散部 (SPECTRUM SPREAD)            | 6  |

| 13 過電流保護部 (OCP)、Battery ショート保護 (BSP)         | 6  |

| 14 短絡保護 (SCP)、REF 端子オープン保護 (REFOPEN)         | 7  |

| 絶対最大定格                                       | 8  |

| 熱抵抗                                          | 8  |

| 推奨動作条件                                       | 8  |

| 電気的特性                                        | Q  |

|                                              |    |

| 特性データ                                        |    |

| 応用回路例                                        | 18 |

| 1 出力電圧                                       | 18 |

| 2 トランス                                       |    |

| 3 出力コンデンサ                                    | 22 |

| 4 入力コンデンサ                                    |    |

| 5 二次側出力ダイオード                                 |    |

| 6 出力抵抗及びツェナーダイオード(最小負荷電流)                    |    |

| 7 スナバ回路                                      |    |

| 8 SDX/EN 端子抵抗                                |    |

| 9 L_COMP 端子抵抗による出力電圧補償機能                     |    |

| 10 各負荷に対する周波数動作と出力電圧への影響                     |    |

| 入出力等価回路図                                     | 27 |

| 使用上の注意                                       | 28 |

| 発注形名情報                                       | 30 |

| 標印図                                          | 30 |

| 外形寸法図と包装・フォーミング仕様                            |    |

| <b>改訂履歴</b>                                  |    |

| 以口核止                                         | 3∠ |

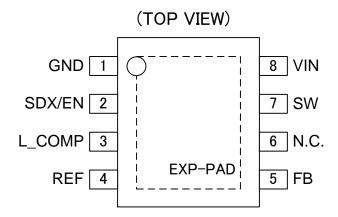

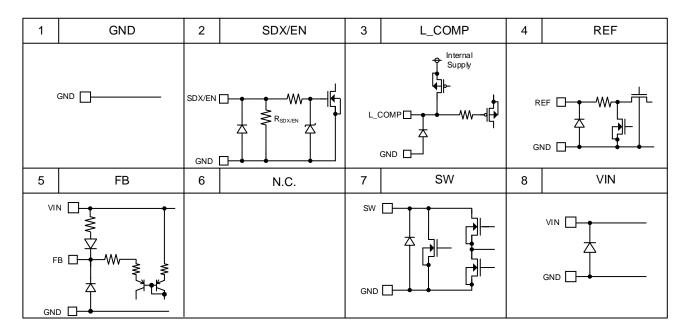

## 端子配置図

## 端子説明

| 77   |         |                                |

|------|---------|--------------------------------|

| 端子番号 | 端子名     | 機能                             |

| 1    | GND     | GND 端子                         |

| 2    | SDX/EN  | シャットダウン/Enable 制御端子            |

| 3    | L_COMP  | 負荷電流補償値設定端子                    |

| 4    | REF     | 出力電圧設定端子                       |

| 5    | FB      | 出力電圧設定端子                       |

| 6    | N.C.    | No Connect <sup>(Note 1)</sup> |

| 7    | SW      | スイッチング出力端子                     |

| 8    | VIN     | 電源入力端子                         |

| -    | EXP-PAD | 裏面放熱端子 <sup>(Note 2)</sup>     |

(Note 1) N.C.端子に内部接続はありません。実装時は端子オープンとしてください。 (Note 2) EXP-PAD 端子は、基板で GND に接続してください。

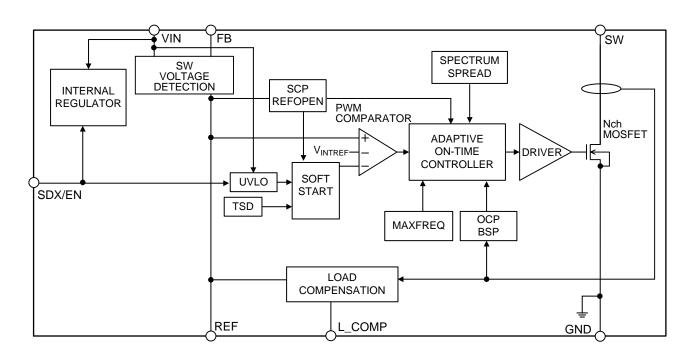

## ブロック図

## 各ブロック動作説明

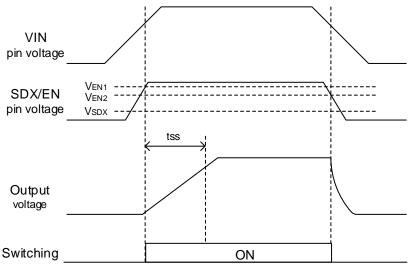

#### 1 内部電源 (INTERNAL REGULATOR)

内部回路用のレギュレータブロックです。

SDX/EN 端子電圧が V<sub>SDX</sub> 以下のシャットダウン状態においては、このブロックもシャットダウンします。

SDX/EN 端子電圧が V<sub>SDX</sub> 以上になると、消費電流が増加します。

SDX/EN 端子電圧が VEN1 以上になると Enable 状態となり、スイッチング動作開始します。

起動からtssの時間はソフトスタート機能が動作し、出力電圧が緩やかに上昇します。

また SDX/EN 端子電圧が V<sub>EN2</sub> 以下になると Disable 状態となり、スイッチング動作を停止します。

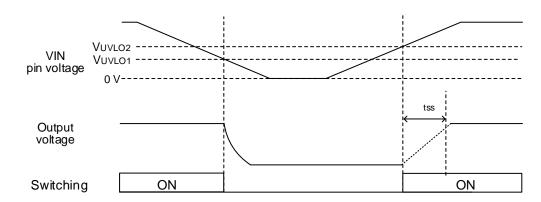

Figure 1. Startup and Stop Timing Chart

## 2 入力低電圧保護機能 (UVLO)

VIN 端子の入力電圧が低い時の低電圧保護回路です。

VIN 端子電圧が VuvLo1 以下になると検出し、スイッチングを停止します。

VIN 端子電圧が VuvLo2 以上になると動作開始し、tss の期間はソフトスタート機能が動作します。

Figure 2. VIN UVLO Timing Chart

## 各ブロック動作説明 ― 続き

#### 3 過熱保護 (TSD)

IC を熱破壊から防ぐための保護回路です。デバイス内部温度が上昇し、175°C (Typ)以上になるとスイッチングを停止します。停止後デバイス内部温度が低下すると 25°C (Typ)のヒステリシスをもって再起動します。ただし、温度保護回路はデバイス自身を保護する目的で内蔵しておりますので、チップ温度は Tjmax = 150°C 以下での熱設計を行ってください。そのため、この機能をセットの温度保護機能として使用しないでください。

#### 4 SW 端子電圧検出部 (SW VOLTAGE DETECTION)

SW 端子に発生するフライバック電圧を検出するブロックです。

トランスのターン OFF 時に、FB 端子から流れる電流を REF 端子の抵抗で電圧変換し、この REF 端子電圧からフライバック電圧を検出します。動作時、IC は検出された REF 端子電圧を VINTREF となるように制御されます。

#### 5 ソフトスタート部 (SOFT START)

SDX/EN 端子電圧が V<sub>EN1</sub> 以上の Enable 状態になると、PWM COMPARATOR の比較電圧は、0 V から V<sub>INTREF</sub> まで段階的に増加し、ソフトスタート時間 tss が経過すると比較電圧は V<sub>INTREF</sub> で動作します。この動作により、出力電圧のオーバーシュートを抑制します。ソフトスタート時間は、IC 内部で tss に固定されています。

また、ソフトスタート開始から tmaskscp の期間は SCP による停止を無効にします。

#### 6 PWM コンパレータ部 (PWM COMPARATOR)

ソフトスタート部の出力電圧または IC 内部基準電圧 VINTREF と出力のフィードバック電圧に相当する REF 端子電圧 を比較します。この出力信号で、ON タイミングを決定します。

エラーアンプを持たず、コンパレータによるフィードバックループを構成しているため、PWM 動作中の負荷変動に対して高速応答を可能にします。

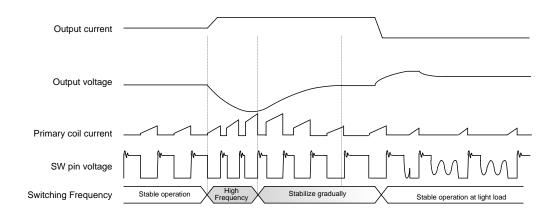

#### 7 適応型 ON 時間制御部 (ADAPTIVE ON TIME CONTROLLER)

独自の適応型 ON 時間制御テクノロジに対応したブロックです。

負荷電流安定時:一定の ON 時間で PWM 動作します。

負荷電流変動時: ON 時間制御で動作し、スイッチング周波数を変動させて高速負荷応答を実現します。 軽負荷時: 不連続モード動作になるとスイッチング周波数が低下し、PFM 動作で高効率を実現します。

負荷電流変動時は fsw\_max 以下の周波数で OFF 時間を短くすることにより一次側平均電流を上昇させ、二次側の電流を増加させることで、出力電圧をすばやく安定化させます。

Figure 3. Load Current Response Timing Chart

## 8 最大周波数制限機能 (MAX FREQ)

最大のスイッチング周波数を制限する機能です。起動時や負荷変動時などの周波数が高速になる場合でも、fsw\_max の最大周波数以下で動作します。これにより、EMI ノイズを抑制します。

#### 9 ドライバ部 (DRIVER)

スイッチング用の Nch MOSFET を駆動するブロックです。

#### 10 スイッチング用 MOSFET (Nch MOSFET)

スイッチング用の Nch MOSFET です。

## 各ブロック動作説明 ― 続き

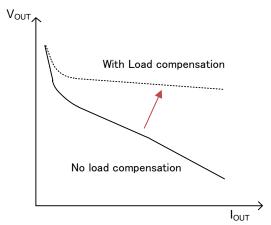

#### 11 負荷電流補償部 (LOAD COMPENSATION)

負荷電流に依存する二次側出力ダイオードの  $V_F$  特性変動による出力電圧の低下を補償するブロックです。スイッチング MOSFET に流れる電流をモニタし、この電流の一部を REF 端子に流します。この流し込む電流量は SW 端子電流に対して REF 端子に流す電流の割合である  $K_{L_COMP}$  と  $L_COMP$  端子に接続される外付け抵抗及びコンデンサによって決定されます。これにより FB 端子から REF 端子の外付け抵抗に流れる電流が減少し、出力電圧低下を補償します。

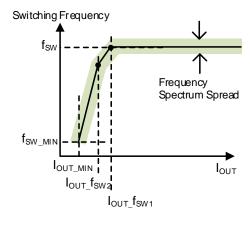

## 12 周波数スペクトラム拡散部 (SPECTRUM SPREAD)

スイッチング周波数を拡散させる機能です。

±5%の範囲で周波数を拡散させることで、低 EMI に貢献します。

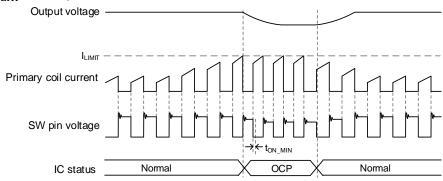

## 13 過電流保護部 (OCP)、Battery ショート保護 (BSP)

MOSFET の過電流保護機能です。

## 13.1 過電流保護部 (OCP)

スイッチング MOSFET ON 時、一次側トランスのピーク電流が ILIMIT 以上になると OCP を検出します。OCP を検出すると、スイッチング MOSFET をターン OFF します。スイッチングサイクルごとに検出しており、OCP が動作すると ON デューティが制限されるため、出力電圧は低下します。またターン ON サージの誤検出防止のため、スイッチング MOSFET のターン ON 後  $t_{ON\_MIN}$ 間 OCP 検出は無効となります。

IC が過電流を検出してからスイッチング MOSFET を OFF させるまでに一定の遅延時間があります。 VIN 電圧が増加すると、遅延時間の影響で  $I_{\text{LIMIT}}$  値が高くなります。この増加量  $\Delta I_{\text{LIMIT}}$  は  $L_{\text{P}}$  値に応じて変化します。

$$\Delta I_{LIMIT} = VIN \times t_{DELAY} / L_P$$

$t_{DELAY}$  : OCP 検出遅延時間  $L_P$  : 一次側インダクタンス  $t_{DELAY}$ は、 $0.2~\mu \mathrm{s}$  以下となります。

Figure 4. OCP Timing Chart

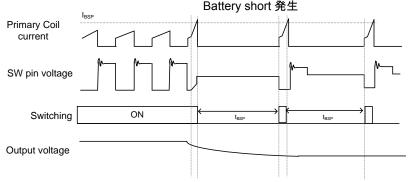

#### 13.2 Battery ショート保護 (BSP)

出力ショートなど、二次側放電電流が低い場合は連続モード動作でピーク電流が増加します。この時、スイッチング MOSFET に ILIMIT を超えた大きな電流が流れます。この電流増加による破壊を抑制するために、Batteryショート保護(BSP)機能が内蔵されています。スイッチング MOSFET ON 時に IBSP 以上の電流が流れた場合に、BSP 状態と判断して tBSP の期間スイッチング動作を停止します。

tasp の期間経過後、再度スイッチング動作します。この時、ソフトスタート機能は動作しません。BSP の状態が続くと、出力電圧が低くなるため SCP 機能により停止します。

BSP の検出についても、VIN 電圧が増加すると遅延時間 tDELAY の影響で IBSP が高くなります。また一次側トランスの巻線ショート時で、この機能が保護動作を行います。

Figure 5. BSP Timing Chart

## 各ブロック動作説明 ― 続き

#### 14 短絡保護 (SCP)、REF 端子オープン保護 (REFOPEN)

REF 端子のショート保護及びオープン保護のブロックです。

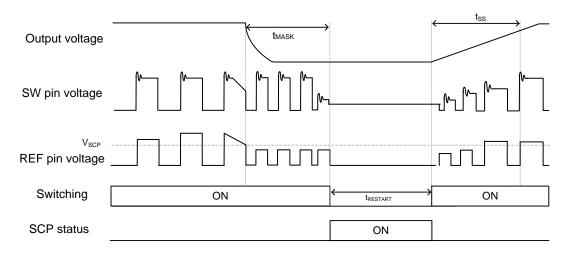

#### 14.1 短絡保護 (SCP)

一次側フライバック電圧を REF 端子電圧に変換することで、二次側出力電圧情報を得ます。出力電圧低下時には REF 端子電圧も低下するので、REF 端子が Vscp 以下となった場合に SCP を検出します。この状態が tmask の期間継続すると、スイッチング動作を停止させます。スイッチング停止から trestart が経過するとソフトスタートで自動復帰します。起動時は SCP 誤検出防止のため、tmaskscp の期間、SCP の検出を無効化します。起動後から tmaskscp の期間 REF 端子電圧が Vscp 以下であった場合、再度 trestart の期間スイッチングを停止します。

Figure 6. SCP Timing Chart

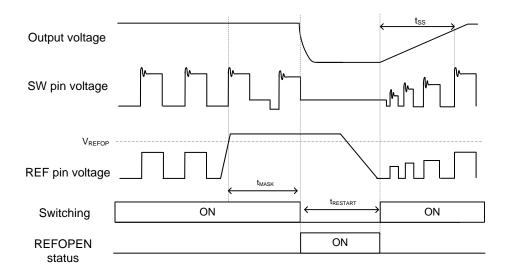

## 14.2 REF 端子オープン保護 (REFOPEN)

REF 端子で一次側フライバック電圧から二次側出力電圧情報を得ます。この端子がオープンになると、出力情報が得られなくなり、スイッチング MOSFET が誤動作を発生する可能性があります。

そのため、REF 端子電圧が VREFOP 以上になると REF 端子オープン保護を検出します。この状態が tmask の期間継続すると、スイッチング動作を停止します。

スイッチング動作停止後、trestart が経過するとソフトスタートで自動復帰をします。

復帰時は tmask の期間スイッチング動作します。tmask の期間 REF 端子電圧が VREFOP 以上の場合、再度 trestart の期間スイッチングを停止します。

Figure 7. REFOPEN Protection Timing Chart

## 絶対最大定格 (Ta = 25 °C)

| 項目          | 記号                  | 定格                | 単位 |

|-------------|---------------------|-------------------|----|

| VIN 端子電圧    | V <sub>IN</sub>     | -0.3 <b>~</b> +45 | V  |

| SW 端子電圧     | Vsw                 | -0.3 <b>~</b> +62 | V  |

| SDX/EN 端子電圧 | V <sub>SDX/EN</sub> | -0.3 <b>~</b> +45 | V  |

| FB 端子電圧     | V <sub>FB</sub>     | -0.3 <b>~</b> +45 | V  |

| REF 端子電圧    | V <sub>REF</sub>    | -0.3 ~ +7         | V  |

| L_COMP 端子電圧 | $V_{L\_COMP}$       | -0.3 <b>~</b> +7  | V  |

| 最高接合部温度     | Tjmax               | 150               | °C |

| 保存温度範囲      | Tstg                | -55 ~ +150        | °C |

注意 1: 印加電圧及び動作温度範囲などの絶対最大定格を超えた場合は、劣化または破壊に至る可能性があります。また、ショートモードもしくはオープンモードなど、破壊状態を想定できません。絶対最大定格を超えるような特殊モードが想定される場合、ヒューズなど物理的な安全対策を施していただけるようご検討お願いします。

注意 2: 最高接合部温度を超えるようなご使用をされますと、チップ温度上昇により、IC 本来の性質を悪化させることにつながります。最高接合部温度を超える場合は基板サイズを大きくする、放熱用銅箔面積を大きくする、放熱板を使用するなど、最高接合部温度を超えないよう熱抵抗にご配慮ください。

## 熱抵抗<sup>(Note 1)</sup>

| 3                                  |             |                          |                           |      |  |  |

|------------------------------------|-------------|--------------------------|---------------------------|------|--|--|

| 項目                                 |             | 熱抵抗                      | 単位                        |      |  |  |

|                                    |             | 1層基板 <sup>(Note 3)</sup> | 4 層基板 <sup>(Note 4)</sup> | 単位   |  |  |

| HTSOP-J8                           | HTSOP-J8    |                          |                           |      |  |  |

| ジャンクション—周囲温度間熱抵抗                   | θја         | 206.4                    | 45.2                      | °C/W |  |  |

| ジャンクション—パッケージ上面中心間熱特性パラメータ(Note 2) | $\Psi_{JT}$ | 21                       | 13                        | °C/W |  |  |

(Note 1) JESD51-2A(Still-Air)に準拠。

(Note 2) ジャンクションからパッケージ(モールド部分)上面中心までの熱特性パラメータ。

(Note 3) JESD51-3 に準拠した基板を使用。

(Note 4) JESD51-5,7 に準拠した基板を使用。

| 測定基板                | 基板材   | 基板寸法                          |

|---------------------|-------|-------------------------------|

| 1層 FR-4             |       | 114.3 mm x 76.2 mm x 1.57 mmt |

| 1層目(表面)銅箔           |       |                               |

| 銅箔パターン 銅箔厚          |       |                               |

| 実装ランドパターン +電極引出し用配線 | 70 µm |                               |

| 測定基板                   | 基板材        | 基板寸法 —                       |               | サーマルヒ           | デア <sup>(Note</sup> | 5)         |  |    |

|------------------------|------------|------------------------------|---------------|-----------------|---------------------|------------|--|----|

| <b>別足基似</b>            | <b>基似的</b> |                              |               | <b>圣似</b> 1 / A |                     | ピッチ        |  | 1径 |

| 4 層                    | FR-4       | 114.3 mm x 76.2 mm x 1.6 mmt |               | 1.20 mm         | Ф0.30 mm            |            |  |    |

| 1層目(表面)銅箔              | 1層目(表面)銅箔  |                              | 2層目、3層目(内層)銅箔 |                 |                     | 4 層目(裏面)銅箔 |  |    |

| 銅箔パターン                 | 銅箔厚        | 銅箔パターン                       | 銅箔厚           | 銅箔パターン          | ·/                  | 銅箔厚        |  |    |

| 実装ランドパターン<br>+電極引出し用配線 | 70 μm      | 74.2 mm口(正方形)                | 35 µm         | 74.2 mm□(正7     | 5形)                 | 70 µm      |  |    |

(Note 5) 貫通ビア。1,2,4層の銅箔と接続する。配置はランドパターンに従う。

## 推奨動作条件

| 項目               | 記号               | 最小  | 標準   | 最大   | 単位 | 条件                         |

|------------------|------------------|-----|------|------|----|----------------------------|

| 動作電源電圧範囲         | V <sub>IN</sub>  | 3.4 | 12.0 | 42.0 | V  | VIN 端子電圧                   |

| 動作電圧範囲           | Vsw              | -   | -    | 60   | V  | SW 端子電圧                    |

| 動作温度             | Topr             | -40 | -    | +125 | °C |                            |

| REF 端子抵抗         | R <sub>REF</sub> | -   | 2.7  | -    | kΩ | 外付け抵抗値 <sup>(Note 6)</sup> |

| L_COMP 電圧範囲      | $V_{L\_COMP}$    | -   | ı    | 1.00 | V  | L_COMP 端子電圧                |

| VIN-GND 間コンデンサ容量 | CVIN             | 10  | -    | -    | μF |                            |

(Note 6) REF 抵抗値は 2.7 k $\Omega$  (Typ)以外は設定しないでください。抵抗精度は出力精度から選択してください。

**電気的特性**(特に指定のない限り Tj = -40 °C ~ +150 °C, V<sub>IN</sub> = 12 V, V<sub>SDX/EN</sub> = 2.5 V)

| 項 目                                   | 記号                   | 最小    | 標準    | 最大    | 単位   | 条件                                       |

|---------------------------------------|----------------------|-------|-------|-------|------|------------------------------------------|

| 電源部                                   |                      |       |       |       |      |                                          |

| シャットダウン時電流                            | Ist                  | -     | 0     | 10    | μА   | SDX/EN 端子 = 0.3 V<br>Tj ≤ 125°C          |

| スイッチング停止時動作電流                         | Icc                  | 0.43  | 1.00  | 1.70  | mA   | REF 端子 = 0.6 V                           |

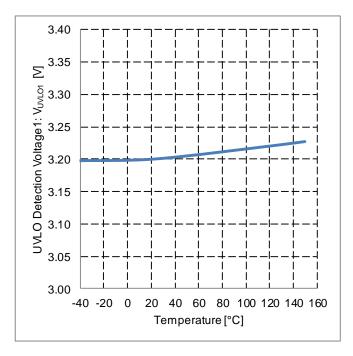

| UVLO 検出電圧 1                           | V <sub>UVLO1</sub>   | 3.00  | 3.20  | 3.40  | V    | VIN 端子下降時                                |

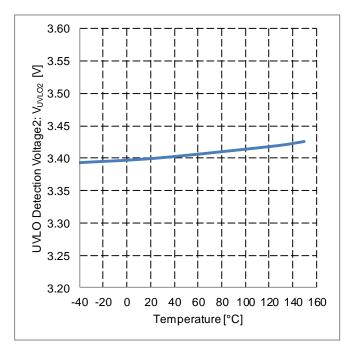

| UVLO 検出電圧 2                           | V <sub>UVLO2</sub>   | 3.20  | 3.40  | 3.60  | V    | VIN 端子上昇時                                |

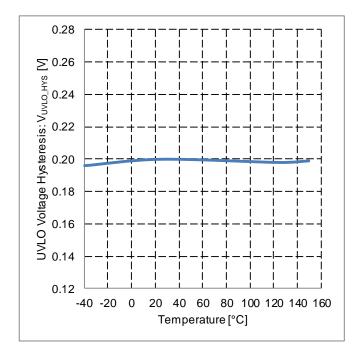

| UVLO ヒステリシス電圧                         | Vuvlo_HYS            | 0.12  | 0.20  | 0.28  | V    |                                          |

| シャットダウン・Enable 制御部                    |                      |       |       |       |      |                                          |

| SDX/EN 端子シャットダウン電圧                    | $V_{SDX}$            | -     | -     | 0.3   | V    |                                          |

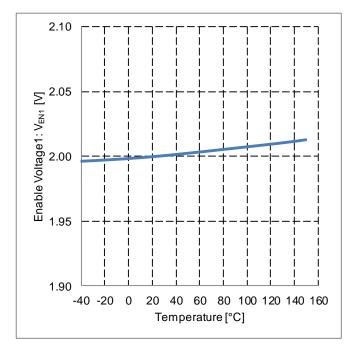

| Enable 電圧 1                           | V <sub>EN1</sub>     | 1.90  | 2.00  | 2.10  | V    | SDX/EN 端子上昇時                             |

| Enable 電圧 2                           | V <sub>EN2</sub>     | 1.60  | 1.80  | 2.00  | V    | SDX/EN 端子下降時                             |

| Enable ヒステリシス電圧                       | V <sub>EN_HYS</sub>  | 0.14  | 0.20  | 0.26  | V    |                                          |

| SDX/EN 端子流入電流                         | I <sub>SDX/EN</sub>  | 0.50  | 1.00  | 2.00  | μA   | SDX/EN 端子 = 2.5 V                        |

| SDX/EN 端子プルダウン抵抗                      | R <sub>SDX/EN</sub>  | 1250  | 2500  | 3750  | kΩ   |                                          |

| 基準電圧部                                 |                      |       |       |       |      |                                          |

| 基準電圧                                  | VINTREF              | 0.525 | 0.540 | 0.555 | V    |                                          |

| REF 端子電流                              | I <sub>REF</sub>     | 140   | 200   | 260   | μΑ   | $R_{REF} = 2.7 \text{ k}\Omega$          |

| スイッチング部                               |                      |       |       |       |      |                                          |

| ON 抵抗                                 | Ron                  | -     | 0.40  | 0.80  | Ω    | SW-GND間 Isw = 50 mA                      |

| 過電流検出電流                               | I <sub>LIMIT</sub>   | 2.08  | 2.60  | 3.12  | Α    |                                          |

| BSP 検出電流                              | I <sub>BSP</sub>     | 2.39  | 3.38  | 4.52  | Α    |                                          |

| 平均スイッチング周波数                           | fsw                  | 300   | 363   | 430   | kHz  | PWM 動作時<br>(デューティ = 40 % )               |

| 最大スイッチング周波数                           | f <sub>SW_MAX</sub>  | -     | -     | 498   | kHz  |                                          |

| ON 時間                                 | ton                  | 0.962 | 1.102 | 1.270 | μs   | PWM 動作時<br>(デューティ = 40 % )               |

| 最小 ON 時間                              | ton_min              | 120   | 250   | 380   | ns   |                                          |

| 最大 OFF 時間                             | toff_max             | 25    | 35    | 45    | μs   |                                          |

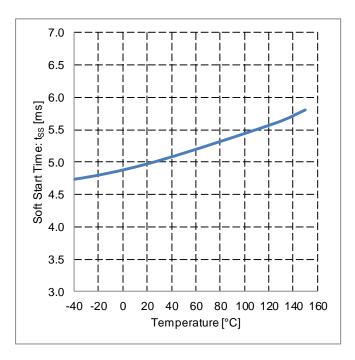

| ソフトスタート時間                             | tss                  | 3.0   | 5.0   | 7.0   | ms   | スイッチング開始から<br>V <sub>INTREF</sub> x 90 % |

| 保護機能部                                 |                      |       |       |       |      |                                          |

| 短絡保護検出電圧                              | V <sub>SCP</sub>     | 0.20  | 0.30  | 0.40  | V    |                                          |

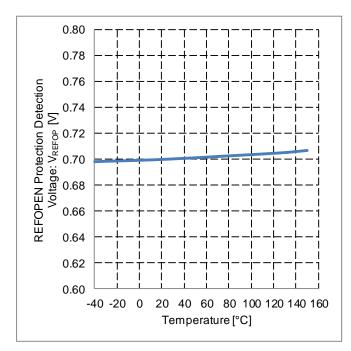

| REF 端子オープン保護検出電圧                      | VREFOP               | 0.60  | 0.70  | 0.80  | V    |                                          |

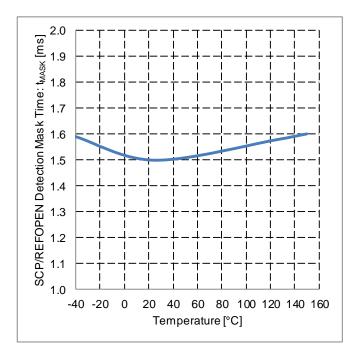

| SCP/REFOPEN 検出マスク時間                   | tmask                | 1.05  | 1.50  | 1.95  | ms   |                                          |

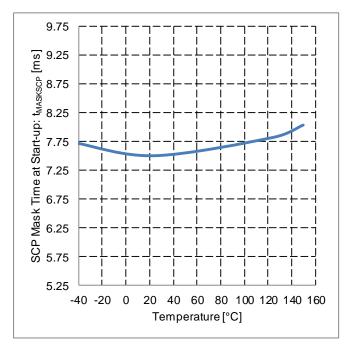

| SCP 起動時検出マスク時間                        | <b>t</b> MASKSCP     | 5.25  | 7.50  | 9.75  | ms   |                                          |

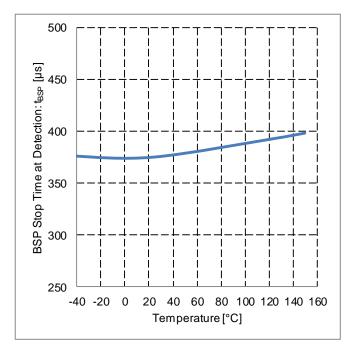

| BSP 検出時停止時間                           | t <sub>BSP</sub>     | 262   | 375   | 488   | μs   |                                          |

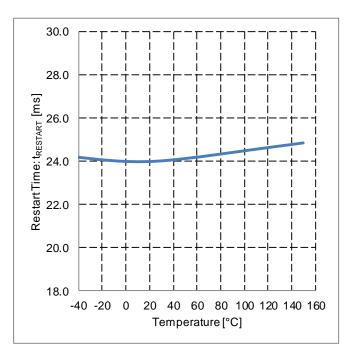

| リスタート時間                               | t <sub>RESTART</sub> | 18.0  | 24.0  | 30.0  | ms   |                                          |

| 負荷補償部                                 |                      |       |       |       |      | -                                        |

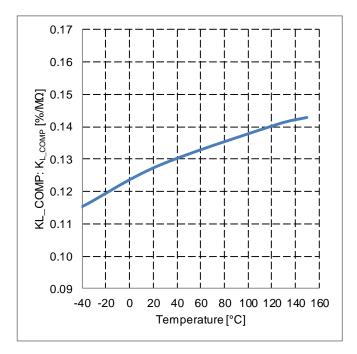

| KL_COMP (SW 端子電流に対する REF<br>端子補償電流係数) | K <sub>L_COMP</sub>  | 0.090 | 0.128 | 0.166 | %/ΜΩ | (Note 1)                                 |

<sup>(</sup>Note 1) 負荷補償電流係数は出力電流に対する出力電圧の低下を補正する係数です。L\_COMP 端子に接続する抵抗値で補正量調整が可能です。 社内検査では RL\_COMP = 10 kΩ で補正量検査を実施しています。

## **特性データ** (参考データ)

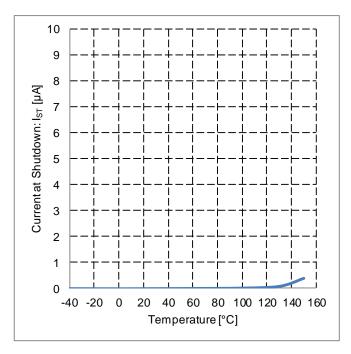

Figure 8. Current at Shutdown vs Temperature

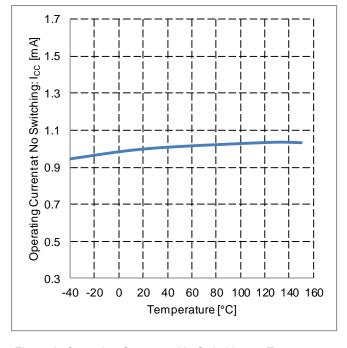

Figure 9. Operating Current at No Switching vs Temperature

Figure 10. UVLO Detection Voltage1 vs Temperature

Figure 11. UVLO Detection Voltage2 vs Temperature

Figure 12. UVLO Voltage Hysteresis vs Temperature

Figure 14. Enable Voltage1 vs Temperature

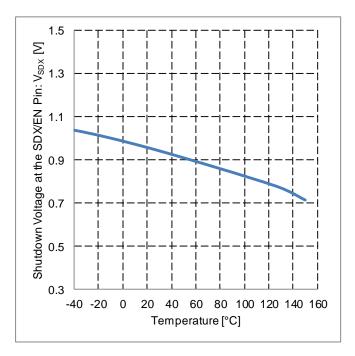

Figure 13. Shutdown Voltage at the SDX/EN Pin vs Temperature

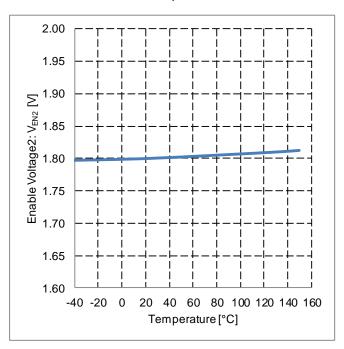

Figure 15. Enable Voltage2 vs Temperature

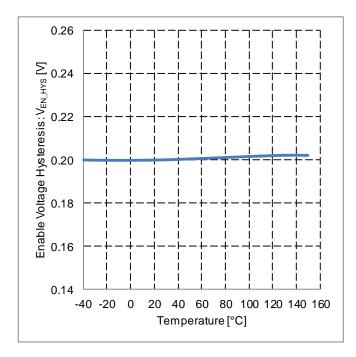

Figure 16. Enable Voltage Hysteresis vs Temperature

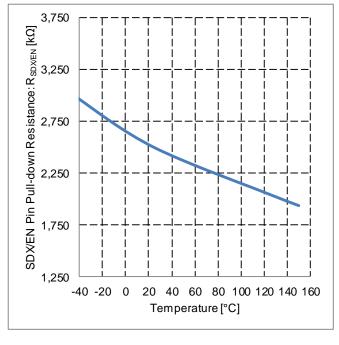

Figure 18. SDX/EN Pin Pull-down Resistance vs Temperature

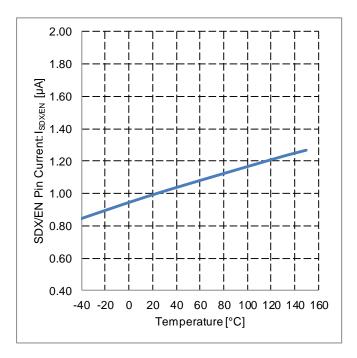

Figure 17. SDX/EN Pin Current vs Temperature

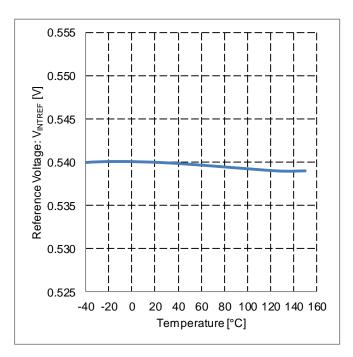

Figure 19. Reference Voltage vs Temperature

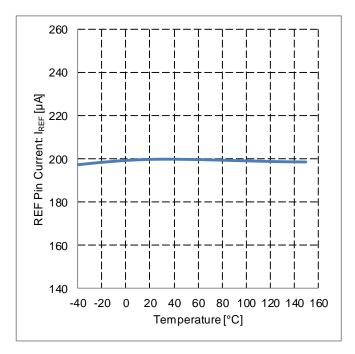

Figure 20. REF Pin Current vs Temperature

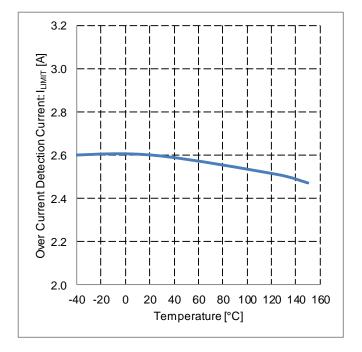

Figure 22. Over Current Detection Current vs Temperature

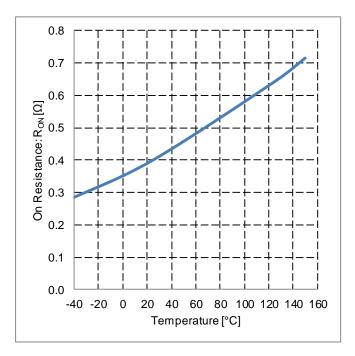

Figure 21. On Resistance vs Temperature

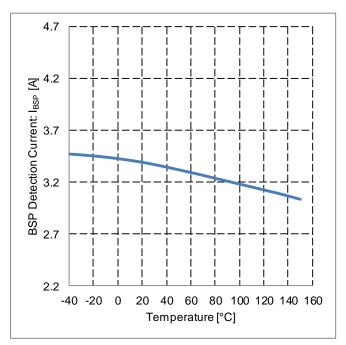

Figure 23. BSP Detection Current vs Temperature

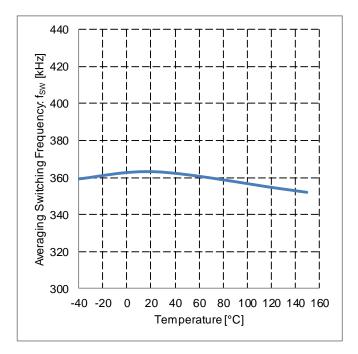

Figure 24. Averaging Switching Frequency vs Temperature

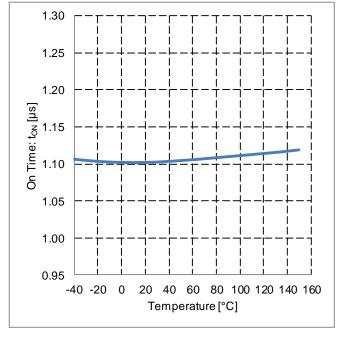

Figure 26. On Time vs Temperature (Duty = 40 %, f<sub>SW</sub> = 363 kHz)

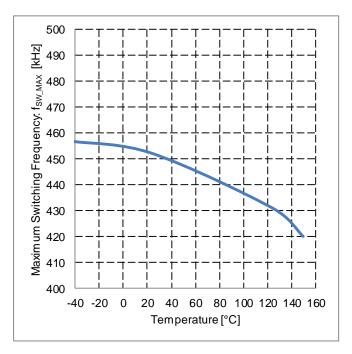

Figure 25. Maximum Switching Frequency vs Temperature

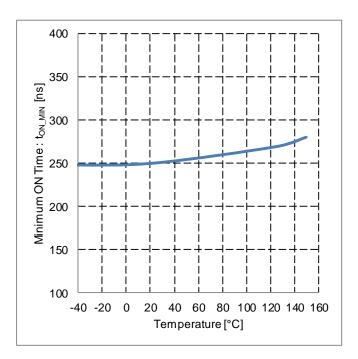

Figure 27. Minimum ON Time vs Temperature

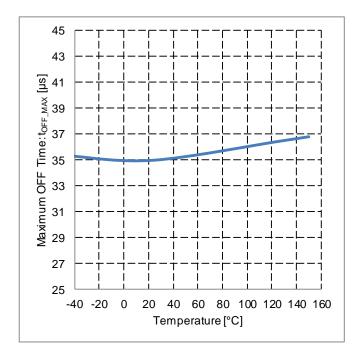

Figure 28. Maximum OFF Time vs Temperature

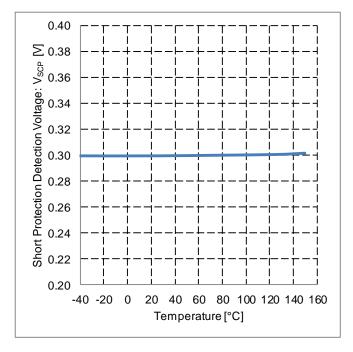

Figure 30. Short Protection Detection Voltage vs Temperature

Figure 29. Soft Start Time vs Temperature

Figure 31. REFOPEN Protection Detection Voltage vs Temperature

Figure 32. SCP/REFOPEN Detection Mask Time vs Temperature

Figure 34. BSP Stop Time vs Temperature

Figure 33. SCP Mask Time at Start-up vs Temperature

Figure 35. Restart Time vs Temperature

Figure 36. KL\_COMP vs Temperature

#### 応用回路例

#### 1 出力電圧

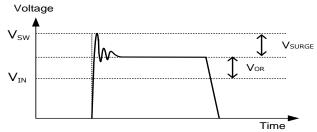

内蔵スイッチング MOSFET のターン OFF 時、SW 端子電圧  $V_{SW}$  が VIN 端子電圧より高くなります。この SW 端子電圧と VIN 端子電圧差は一次側フライバック電圧と等しくなるため、この電圧から二次側出力電圧を計算します。ターン OFF 時の SW 端子電圧  $V_{SW}$  は以下の式で計算されます。

$$V_{SW} = V_{IN} + \frac{N_P}{N_S} \times (V_{OUT} + V_F)$$

[V]

$V_{SW}$  : SW 端子電圧  $V_{IN}$  : VIN 端子電圧

$egin{array}{lll} N_P & : - 次側トランス巻数 \ N_S & : 二次側トランス巻数 \end{array}$

$V_{OUT}$  : 出力電圧

$V_F$  : 二次側の出力ダイオードの順方向電圧

Figure 37. Application Block Diagram

一次側フライバック電圧は、FB-SW 端子間の外付け抵抗 RFBによって FB 端子流入電流 IFB に変換されます。FB 端子電圧は IC 内部回路により VIN 端子電圧とほぼ等しくなるため、FB 端子流入電流 IFB は以下の式で計算されます。

$$I_{FB} = \frac{V_{SW} - V_{FB}}{R_{FB}} = \frac{V_{IN} + \frac{N_P}{N_S} \times (V_{OUT} + V_F) - V_{FB}}{R_{FB}} = \frac{\frac{N_P}{N_S} \times (V_{OUT} + V_F)}{R_{FB}}$$

[A]

$I_{FB}$  : FB 端子流入電流 $V_{FB}$  : FB 端子電圧

$R_{FR}$ : FB、SW 端子間の外付け抵抗

#### 1 出力電圧 - 続き

さらに、FB 端子流入電流 IRFB は REF 端子と GND 端子間の外付け抵抗 RREF に流れるため、REF 端子電圧は以下の式で計算されます。

$$V_{REF} = \frac{R_{REF}}{R_{FB}} \times \frac{N_P}{N_S} \times (V_{OUT} + V_F)$$

[V]

$V_{REF}$  : REF 端子電圧

$R_{REF}$  : REF 端子 - GND 端子間の外付け抵抗

R<sub>REF</sub> は、REF 端子電圧 = V<sub>INTREF</sub> のときに REF 端子に流れる電流が I<sub>REF</sub> となるため、

$R_{REF}=rac{0.54\,V}{200\,\mu A}=2.7\,k\Omega$  の抵抗を設定する必要があります。

REF 端子電圧は、IC 内部の基準電圧とのコンパレータに入力されます。IC の内部回路により、REF 端子電圧は基準電圧と等しくなります。したがって、出力電圧と REF 端子電圧は以下の式で計算されます。

$$V_{OUT} = \frac{R_{FB}}{R_{REF}} \times \frac{N_S}{N_P} \times V_{INTREF} - V_F$$

[V]

この式からわかるように出力電圧 Vout は、一次側と二次側のトランス巻数比(NP/Ns)、及び RFB と RREF の抵抗比によって設定可能です。

上記の関係式より、FB 端子と SW 端子間の外付け抵抗 RFB は以下の式で計算できます。

$$R_{FB} = \frac{R_{REF}}{V_{INTREF}} \times \frac{N_P}{N_S} \times (V_{OUT} + V_F)$$

[\Omega]

ただしトランスの二次側の ESR は上記式の  $V_F$  と同様に出力電圧を低下させる要因となります。 またトランスの結合が低い場合も  $N_P/N_S$  の巻数比がずれるため、出力電圧が低くなる要因となります。 そのため最終的には実機確認で出力電圧を調整してください。

## 応用回路例 - 続き

## 2 トランス

#### 2.1 巻数比 N<sub>P</sub> / N<sub>S</sub> の決定

巻数比は、出力電圧、最大出力電力、デューティ、SW 端子電圧を設定するパラメータです。 フライバック・コンバータのデューティは以下の式で計算されます。

$$Duty = \frac{\frac{N_P}{N_S} \times (V_{OUT} + V_F)}{V_{IN} + \frac{N_P}{N_S} \times (V_{OUT} + V_F)}$$

[%]

$N_P$  : 一次側トランス巻数  $N_S$  : 二次側トランス巻数

$V_{OUT}$  : 出力電圧

$V_F$  : 二次側の出力ダイオードの順方向電圧

$V_{IN}$  : VIN 端子電圧

上式より巻数比は下記で計算します。

$$rac{N_P}{N_S} = rac{D_{TYP}}{1-D_{TYP}} imes rac{V_{IN}}{V_{OUT} + V_F} \ D_{TYP}$$

: VIN 電圧(Typ)時のデューティ

使用動作範囲の中央の VIN 電圧で  $D_{TYP}$  を 30 % ~ 50 %の範囲で設定を推奨します。はじめは  $D_{TYP}$  = 40 %に設定してください。巻数比は、最小入力電圧から決定される最大デューティ  $D_{MAX}$  により制限されます。下記の式で与えられる  $D_{MAX}$  が 70 %を超えないことを必ず確認してください。もし超えるようであれば、

上記の D<sub>TYP</sub>が小さくなるように再設定してください。70 %を超える場合は OFF 時間が短くなるため、フライバック電圧の検出がずれることにより、出力電圧がずれる可能性があります。

$$\frac{N_P}{N_S} = \frac{D_{MAX}}{1 - D_{MAX}} \times \frac{V_{IN(Min)}}{V_{OUT(Max)} + V_{F(Max)}}$$

$D_{MAX}$ : VIN 電圧(Min)条件の最大デューティ

$V_{OUT(Max)}$  : 最大出力電圧

$V_{F(Max)}$  : 二次側ダイオードの順方向電圧(Max)

またフライバック電圧 Vor は下記の式で計算されます。

$$V_{OR} = (V_{OUT} + V_F) \times \frac{N_P}{N_C}$$

[V]

下記で計算される SW 端子電圧が耐圧を超えないように設定してください。

$$V_{SW} = V_{IN(Max)} + V_{OR} + V_{SURGE}$$

[V]

例えば SW 端子耐圧に対しディレーティングを 90 %とる場合、SW 端子電圧は、

60 V×(100 % - 10 %) = 54 V となるので、54 V 以内となるように設計する必要があります。

V<sub>IN(Max)</sub> = 30 V、 V<sub>OR</sub> = 10 V の場合、

$V_{SURGE}$ は 54V-(30V+10V)=14V となるため、サージ電圧を 14V 以内にする必要があります。 $V_{SURGE}$  はトランスの漏れ磁束によって発生します。 $V_{SURGE}$  が大きい場合はトランス構造の見直しやスナバ回路の調整が必要となります。

Figure 38. SW Waveform

トランスを決定時は、上記を満たすような巻数比を仮設定してください。 巻数比が決定されると、FB端子抵抗RFBの設定が可能となり、出力電圧が設定されます。

#### 2 トランス - 続き

#### 2.2 Lp、Lsの計算

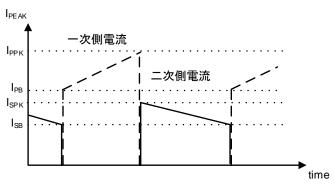

電流連続モード動作となるように Lp、Ls を設定します。

LP、LSを求めるにあたり電流連続モードの深さkを使用して決定します。

kは Figure 39の ISPK、 ISBから下記の式で表されます。

$$k = (I_{SPK} - I_{SB})/I_{SPK}$$

$I_{SPK}$  : 二次側トランスピーク電流  $I_{SB}$  : 二次側トランスボトム電流

K: 電流連続モードの深さを表す定数 (設計時は k=0.25 を目安としてください。)

Figure 39. The Waveform Example of Primary and Secondary Current of Transformer

$I_{PPK}$  : 一次側トランスピーク電流

$I_{PR}$  : 一次側トランスボトム電流

ICの一次側最大ピーク電流は電気的特性の ILIMIT で決定されています。 ILIMIT 最小値から二次側最小ピーク電流 ISPK1(Min)が決定されます。

$$I_{SPK1(Min)} = I_{LIMIT(Min)} \times \frac{N_P}{N_S}$$

[A]

また最大出力電流 IOUT(Max)から二次側ピーク電流 ISPK2(Max)を下記の式で求めます。

$$I_{SPK2(Max)} = \frac{2 \times I_{OUT(Max)}}{(1 - D_{MAX}) \times (2 - k)} \times \frac{1}{\eta}$$

[A]

$\eta$ : 電源効率 70%を目安としてください。

IOUT(Max)を出力するために、ISPK2(Max) < ISPK1(Min)の条件を必ず満たす必要があります。 条件を満たせない場合は k を変更して再設計してください。 k 値は高くなるほど、不連続モードで 動作する負荷領域が広くなります。 k = 1 では全領域で不連続モード動作となります。本 IC は連続 モード動作させることで、高速応答や低 EMI の特性を得るために低い k 値を推奨しています。 k 値が高い場合でも、電源動作に問題はありません。

二次側インダクタンス Ls(Max)は下記の式で計算されます。

$$L_{S(Max)} = \frac{(2-k) \times (V_{OUT} + V_F) \times (1 - D_{MAX})^2}{2 \times I_{OUT(Max)} \times f_{sw(Max)} \times k}$$

[µH]

$f_{SW(Max)}$  : スイッチング周波数 このスイッチング周波数は 430 kHz で計算してください。

$I_{OUT(Max)}$  :最大 2 次側出力電流

この時、一次側インダクタンス Lp は下記の式で求まります。

$$L_P = L_S \times (\frac{N_P}{N_S})^2$$

[µH]

#### 2 トランス - 続き

#### 2.3 IPRMS、ISRMSの計算

最大一次側 RMS 電流 IPRMS 及び最大二次側 RMS 電流 ISRMS は下記の計算となります。

$$I_{PRMS} = \sqrt{\frac{(I_{PPK}^2 + I_{PPK} \times I_{PB} + I_{PB}^2) \times D_{MAX}}{3}}$$

[A]

$$I_{SRMS} = \sqrt{\frac{(I_{SPK}^2 + I_{SPK} \times I_{SB} + I_{SB}^2) \times (1 - D_{MAX})}{3}}$$

[A]

トランスの線径を選択するときは、この RMS 電流を参考に選択してください。

#### 3 出力コンデンサ

出力コンデンサは、できるだけ二次側ダイオードの近くに配置してください。 出力コンデンサ容量値 Cout は出力リップル電圧 ΔVo と起動時間から設定します。 1 回のスイッチングで発生する出力リップル電圧は下記の計算式になります。

$$\Delta V_O = \frac{I_{OUT(Max)} \times D_{MAX}}{f_{SW(Max)} \times C_{OUT}}$$

[V]

一方、出力容量が大きい場合は起動時間が長くなります。起動時に SCP 起動時検出マスク時間 tmaskscp 経過した時点で、REF 電圧が Vscp 電圧よりも低い場合、起動できません。そのため、下記の条件を満たす必要があります。

$$C_{OUT} \leq \frac{1}{2} \times \frac{t_{MASKSCP(Min)} \times \{\left(I_{LIMIT(Min)} \times \frac{N_P}{N_S}\right) \times (1 - Duty) - I_{OUT(Max)}\}}{V_{OUT} \times (\frac{V_{SCP(Max)}}{V_{INTREF(Min)}})}$$

[µF]

ここで、

$$\frac{V_{SCP(Max)}}{V_{INTREF(Min)}}$$

= 0.762 となります。

負荷応答時や電源電圧応答時には出力電圧を保持するために大きいコンデンサ容量値が必要となります。 出力電圧容量の目安としては、20 µF 以上の容量値を推奨します。 セラミック・コンデンサは温度特性や容量バラつき、DC バイアス特性などの影響により 容量値が低下する可能性があります。これらの点に注意して、部品を選択してください。

## 4 入力コンデンサ

入力コンデンサはセラミック・コンデンサを使用し、なるべく IC に近い位置に配置してください。 コンデンサ容量は 10  $\mu$ F 以上の容量値としてください。

#### 応用回路例 - 続き

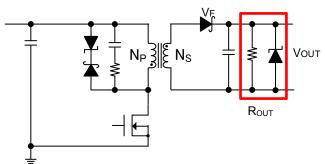

#### 5 二次側出力ダイオード

二次側出力ダイオードの順方向電圧  $V_F$  は出力電圧の誤差要因となるため、 $V_F$  の小さいショットキーバリアダイオードまたはファストリカバリーダイオードを推奨します。二次側出力ダイオードの選定においては、二次側逆電圧のピークがダイオードの定格を超えないようにする必要があります。また二次側 RMS 電流  $I_{SRMS}$  も定格を超えないように設定する必要があります。

一般に、二次側出力ダイオードの逆方向耐圧 VR は 30 %以上のマージンを推奨します。

$$V_R = (V_{IN(Max)} \times \frac{N_S}{N_P} + V_{OUT}) \times 1.3 + V_{SURGE}$$

[V]

$V_R$  : 二次側出力ダイオードの逆方向電圧

$V_{IN(Max)}$ : VIN 端子最大電圧  $N_P$  : 一次側トランス巻数  $N_S$  : 二次側トランス巻数

$V_{OUT}$  : 出力電圧

$V_{SURCE}$ : ダイオードに発生するトランスサージ電圧

また二次側出力ダイオードの定格電流は IsRMS に対して 2 倍以上のマージン設計を推奨します。

## 6 出力抵抗及びツェナーダイオード(最小負荷電流)

無負荷時や軽負荷時に出力電圧は上昇します。この理由は、本IC は軽負荷の時に最大 OFF 時間 toff\_MAX 及び最小 ON 時間 ton\_MIN で決まる最低周波数で必ずスイッチング動作するためです。 この最低周波数のスイッチング周波数で決定される電力 Po\_MIN に対して、二次側負荷がこれよりも軽い場合に出力電圧は上昇します。Po MIN は、下記の式で計算されます。

$$P_{O\_MIN} = rac{{v_{IN(Max)}}^2}{2 imes L_P} imes t_{ON\_MIN(Max)}^2 imes rac{1}{t_{ON\_MIN(Max)} + t_{OFF\_MAX(Min)}}$$

[W]  $I_{OUT\_MIN} = rac{P_{O\_MIN}}{v_{OUT}}$ の式のため、lout\\_MIN から求めることも可能です。

二次側出力電圧の上昇が問題になる場合、二次側出力ツェナーダイオードを接続し、電圧の上昇を抑制してください。 また、二次側出力に抵抗を付けて一定の損失を与えることで、出力電圧の上昇を抑えることも必要です。二次側に接 続する出力抵抗 Rout は下記を目安としてください。またこの抵抗損失 PLoss は下記の計算式になります。

PLOSS =

$$\frac{V_{OUT}^2}{R_{OUT}}$$

[W]

$$R_{OUT} \leq \frac{V_{OUT}^2}{P_{O\_MIN}} = \frac{V_{OUT}^2}{\frac{V_{IN(Max)}^2}{2 \times L_P} \times t_{ON\_MIN(Max)}^2 \times \frac{1}{t_{ON\_MIN(Max)} + t_{OFF\_MAX(Min)}}} [\Omega]$$

実際には、上式で計算された Rout 負荷を使用しても二次側放電時に過渡的に出力電圧が上昇します。 そのため、この Rout よりも十分低く設定する必要があります。

この抵抗値は実機評価において調整してください。また抵抗選択時は抵抗の定格電力に注意してください。 出力電圧上昇の原因は応用回路例「10 各負荷に対する周波数動作と出力電圧への影響」にて後述しています。

Figure 40. Zener Diode and Resistor to Secondary Output

BD7F105EFJ-C Datasheet

## 応用回路例 - 続き

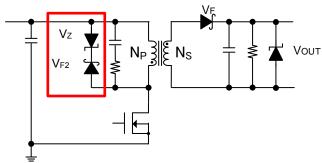

## 7 スナバ回路

トランスの結合度が低い、基板の大電流ラインが長いなどの場合、ターン OFF 時の SW 端子に過大な電圧が印加される可能性があります。

これを抑制するため、Figure 41 で示されるスナバ回路を使用します。

このスナバ回路はフライバック電圧+サージ電圧がこのスナバ電圧を超えた場合に、電圧クランプします。

Figure 41. Snubber Circuit

クランプ電圧は下記の式で決定されます。

$$V_{CLAMP} = V_{F2} + V_{z}$$

[V]

$V_{CLAMP}$  : スナバのクランプ設定電圧

$egin{array}{lll} V_{F2} & : ショットキーダイオードの順方向電圧 \ V_{Z} & : ツェナーダイオードのツェナー電圧 \end{array}$

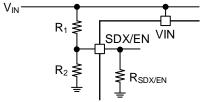

## 8 SDX/EN 端子抵抗

#### 8.1 Enable 電圧の設定

VIN UVLO 解除後の Enable 電圧 Vin ENABLE は、以下の式で設定することができます。

$$V_{IN\_ENABLE} = V_{EN1} \times \frac{R_1 + (R_2//R_{SDX/EN})}{R_2//R_{SDX/EN}}$$

[V]

$V_{IN\;ENABLE}$  : 狙いの動作開始 VIN 電圧

$V_{EN1}$  : Enable 電圧 1

$R_2//R_{SDX/EN}$ : R2 と IC 内部の R<sub>SDX/EN</sub> との分圧抵抗

Figure 42. Resistors Connected to the SDX/EN Pin

#### 8.2 Disable 電圧の設定

VIN 端子電圧立ち下り時の Disable 電圧 VIN\_DISABLE は以下の式で設定することができます。

$$V_{IN\_DISABLE} = V_{EN2} \times \frac{R_1 + (R_2//R_{SDX/EN})}{R_2//R_{SDX/EN}}$$

[V]

$V_{IN\;DISABLE}$  : 狙いの動作停止 VIN 電圧

$V_{EN2}$  :Enable 電圧 2

## 応用回路例 - 続き

#### 9 L COMP 端子抵抗による出力電圧補償機能

本 IC は一次側トランスピーク電流 IP の増加に応じて出力電圧 Vou $\tau$  の電圧降下の補償が可能です。 Vou $\tau$  が変化する原因には、二次側ダイオードの VF 変動やトランスの漏れ磁束が挙げられます。 出力電圧補償機能の一例を Figure 43 に示します。

Figure 43. L COMP Voltage Compensation Example

この機能は出力電圧を決定する REF 電流に IREFCOMP 電流を加えることで出力電圧を補償します。

$$V_{OUT} = R_{FB} \times \frac{N_S}{N_P} \times \left(\frac{V_{INTREF}}{R_{REF}} + I_{REFCOMP}\right) - V_F$$

[V]

$rac{V_{INTREF}}{R_{REF}}=200~\mu A~(Typ)~$ は固定値です。 $I_{REFCOMP}$ は対して、一次側電流の増加に応じて増加します。その結果として、二次側の負荷電流に応じて出力電圧を補償します。

IREFCOMP は下記の式で決定します。

$$I_{REFCOMP} = R_{L\ COMP} \times K_{L\ COMP} \times I_{SW(Ave)}$$

[µA]

$R_{L\ COMP}$ : L\_COMP 端子に接続される抵抗

$I_{SW(Ave)}$ : SW 端子に流れる平均電流

$K_{L,COMP}$ : IC 内部の固定値

SW 端子の平均電流 Isw(Ave)は下記の式に変換できます。

$$I_{SW(Ave)} = I_{S(Ave)} \times \frac{N_S}{N_P} = I_{OUT} \times \frac{1}{n} \times \frac{N_S}{N_P}$$

[A]

$\eta$ : 効率(70 %程度で設計し、アプリケーション評価で  $R_{L\_COMP}$  を調整してください。)

この式で示すように、 $I_{SW(AVe)}$ は  $I_{OUT}$  に比例するため、上記の補償が可能です。 また補償量は  $L_{L}$  LCOMP 端子の抵抗値によって調整可能です。  $I_{SW}$  は三角波電流のため、これを平滑化するために  $L_{L}$  COMP 端子には必ず 0.1 uF 以上の

$I_{SW}$  は三角波電流のため、これを平滑化するために L\_COMP 端子には必ず  $0.1~\mu F$  以上のコンデンサを接続してください。

L\_COMP 端子の抵抗は下記の式で計算します。

$$R_{L\_COMP} = \frac{I_{REFCOMP}}{I_{SW(Ave)}} \times \frac{1}{K_{L\_COMP}}$$

[k\O]

必ずアプリケーション評価にて出力電圧特性を確認し、必要に応じて L\_COMP 端子抵抗を調整してください。 また、補償を行わない場合は L\_COMP 端子を GND ショートとしてください。

## 応用回路例 - 続き

#### 10 各負荷に対する周波数動作と出力電圧への影響

本IC は軽負荷時にスイッチング周波数を低下させることで高効率を実現します。 連続モード動作時、一定負荷に対して周波数は fsw となるように動作します。 負荷が軽くなり、連続モードと不連続モードの切り替り点に達すると、スイッチング周波数が fsw から 低下を始めます。この切り替わり点となる負荷電流 lour fsw1 は以下の式で計算されます。

$$I_{OUT}f_{SW1} = \frac{1}{2} \times \frac{(V_{IN} \times Duty)^2}{L_P \times f_{SW} \times V_{OUT}} \times \eta$$

[A]

$I_{OUT} f_{SW1}$ : 連続モードと不連続モードの切り替り負荷電流

$f_{SW}$ : スイッチング周波数

$V_{IN}$ : VIN 端子電圧

$L_P$ : 一次側インダクタンス

$V_{OUT}$ : 出力電圧

η: 効率

負荷が軽くなると、ON 時間と OFF 時間は低下し、ON 時間は最小 ON 時間  $t_{ON\_MIN}$  で動作します。この最小 ON 幅で動作する時の負荷電流は下記で求まります。

$$I_{OUT\_} f_{SW2} = \frac{1}{2} \times \frac{f_{SW} \times (V_{IN} \times t_{ON\_MIN})^2}{L_P \times V_{OUT}} \times \eta$$

[A]

$I_{OUT\_}f_{SW2}$  :最小 ON 時間で動作する負荷電流

t<sub>ON MIN</sub> : 最小 ON 時間

さらに負荷が軽くなると、ON 時間は  $t_{ON\_MIN}$  よりも短くならないため、OFF 時間が長くなります。本 IC は最大 OFF 時間  $t_{OFF\_MAX}$  が決まっているため、最小周波数は下記で計算されます。

$$f_{SW\_MIN} = \frac{1}{t_{ON\_MIN} + t_{OFF\_MAX}}$$

[kHz]

**f<sub>SW MIN</sub>** : 最小スイッチング周波数

$t_{OFF\;MAX}$  :最大 OFF 時間

無負荷時や軽負荷時にも一定のスイッチング周波数で動作するので、一定の電力が出力されます。そのため無負荷時や軽負荷時には電圧が上昇します。また、本ICはEMI改善のために周波数スペクトラム拡散機能を搭載しています。そのため動作時に周波数は一定の割合で変化します。この機能に依存する周波数により、一定の出力リップル電圧が発生します。

Figure 44. Switching Frequency

## 入出力等価回路図

#### 使用上の注意

#### 1. 電源の逆接続について

電源コネクタの逆接続により LSI が破壊する恐れがあります。逆接続破壊保護用として外部に電源と LSI の電源端子間にダイオードを入れるなどの対策を施してください。

#### 2. 電源ラインについて

基板パターンの設計においては、電源ラインの配線は、低インピーダンスになるようにしてください。グラウンドラインについても、同様のパターン設計を考慮してください。また、LSIのすべての電源端子について電源ーグラウンド端子間にコンデンサを挿入するとともに、電解コンデンサ使用の際は、低温で容量低下が起こることなど使用するコンデンサの諸特性に問題ないことを十分ご確認のうえ、定数を決定してください。

#### 3. グラウンド電位について

グラウンド端子の電位はいかなる動作状態においても、最低電位になるようにしてください。また実際に過渡現象を含め、 グラウンド端子以外のすべての端子がグラウンド以下の電圧にならないようにしてください。

#### 4. グラウンド配線パターンについて

小信号グラウンドと大電流グラウンドがある場合、大電流グラウンドパターンと小信号グラウンドパターンは分離し、パターン配線の抵抗分と大電流による電圧変化が小信号グラウンドの電圧を変化させないように、セットの基準点で1点アースすることを推奨します。外付け部品のグラウンドの配線パターンも変動しないよう注意してください。グラウンドラインの配線は、低インピーダンスになるようにしてください。

#### 5. 推奨動作条件について

推奨動作条件で規定される範囲で IC の機能・動作を保証します。また、特性値は電気的特性で規定される各項目の条件下においてのみ保証されます。

#### 6. ラッシュカレントについて

IC 内部論理回路は、電源投入時に論理不定状態で、瞬間的にラッシュカレントが流れる場合がありますので、電源カップリング容量や電源、グラウンドパターン配線の幅、引き回しに注意してください。

#### 7. セット基板での検査について

セット基板での検査時に、インピーダンスの低い端子にコンデンサを接続する場合は、IC にストレスがかかる恐れがあるので、1 工程ごとに必ず放電を行ってください。静電気対策として、組立工程にはアースを施し、運搬や保存の際には十分ご注意ください。また、検査工程での治具への接続をする際には必ず電源を OFF にしてから接続し、電源を OFF にしてから取り外してください。

#### 8. 端子間ショートと誤装着について

プリント基板に取り付ける際、ICの向きや位置ずれに十分注意してください。誤って取り付けた場合、ICが破壊する恐れがあります。また、出力と電源及びグラウンド間、出力間に異物が入るなどしてショートした場合についても破壊の恐れがあります。

## 9. 未使用の入力端子の処理について

CMOSトランジスタの入力は非常にインピーダンスが高く、入力端子をオープンにすることで論理不定の状態になります。これにより内部の論理ゲートのpチャネル、nチャネルトランジスタが導通状態となり、不要な電源電流が流れます。また論理不定により、想定外の動作をすることがあります。よって、未使用の端子は特に仕様書上でうたわれていない限り、適切な電源、もしくはグラウンドに接続するようにしてください。

#### 使用上の注意 ― 続き

#### 10. 各入力端子について

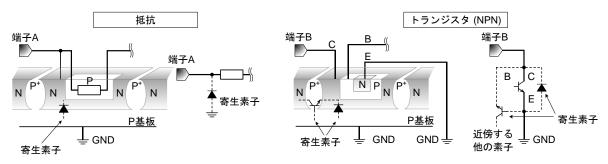

本 IC はモノリシック IC であり、各素子間に素子分離のための P+アイソレーションと、P 基板を有しています。 この P 層と各素子の N 層とで P-N 接合が形成され、各種の寄生素子が構成されます。

例えば、下図のように、抵抗とトランジスタが端子と接続されている場合、

○抵抗では、GND > (端子 A)の時、トランジスタ(NPN)では GND > (端子 B)の時、P-N 接合が寄生ダイオードとして動作します。

Oまた、トランジスタ(NPN)では、GND > (端子 B)の時、前述の寄生ダイオードと近接する他の素子の N 層によって寄生の NPN トランジスタが動作します。

IC の構造上、寄生素子は電位関係によって必然的にできます。寄生素子が動作することにより、回路動作の干渉を引き起こし、誤動作、ひいては破壊の原因ともなり得ます。したがって、入出力端子に GND(P 基板)より低い電圧を印加するなど、寄生素子が動作するような使い方をしないよう十分に注意してください。アプリケーションにおいて電源端子と各端子電圧が逆になった場合、内部回路または素子を損傷する可能性があります。例えば、外付けコンデンサに電荷がチャージされた状態で、電源端子が GND にショートされた場合などです。また、電源端子直列に逆流防止のダイオードもしくは各端子と電源端子間にバイパスのダイオードを挿入することを推奨します。

Figure 45. モノリシック IC 構造例

#### 11. セラミック・コンデンサの特性変動について

外付けコンデンサに、セラミック・コンデンサを使用する場合、直流バイアスによる公称容量の低下、及び温度などによる容量の変化を考慮のうえ、定数を決定してください。

#### 12. 温度保護回路について

IC を熱破壊から防ぐための温度保護回路を内蔵しております。最高接合部温度内でご使用いただきますが、万が一最高接合部温度を超えた状態が継続すると、温度保護回路が動作し出力パワー素子が OFF します。その後チップ温度 Tj が低下すると回路は自動で復帰します。なお、温度保護回路は絶対最大定格を超えた状態での動作となりますので、温度保護回路を使用したセット設計などは、絶対に避けてください。

## 13. 過電流保護回路について

出力には電流能力に応じた過電流保護回路が内部に内蔵されているため、負荷ショート時には IC 破壊を防止しますが、この保護回路は突発的な事故による破壊防止に有効なもので、連続的な保護回路動作、過渡時でのご使用に対応するものではありません。

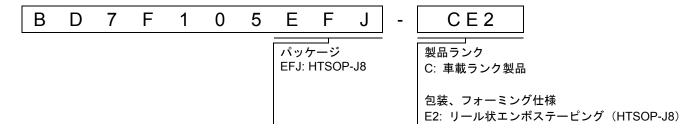

## 発注形名情報

## 標印図

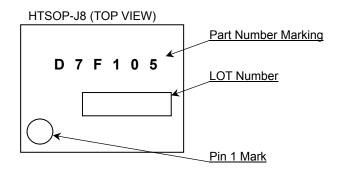

## 外形寸法図と包装・フォーミング仕様

## 改訂履歴

| 日付         | 版   | 変更内容 |

|------------|-----|------|

| 2022.03.01 | 001 | 新規作成 |

## ご注意

## ローム製品取扱い上の注意事項

1. 極めて高度な信頼性が要求され、その故障や誤動作が人の生命、身体への危険もしくは損害、又はその他の重大な損害 の発生に関わるような機器又は装置 (医療機器(Note 1)、航空宇宙機器、原子力制御装置等)(以下「特定用途」という) への本製品のご使用を検討される際は事前にローム営業窓口までご相談くださいますようお願い致します。ロームの文 書による事前の承諾を得ることなく、特定用途に本製品を使用したことによりお客様又は第三者に生じた損害等に関し、ロームは一切その責任を負いません。

(Note 1) 特定用途となる医療機器分類

| Ī | 日本      | USA      | EU       | 中国         |

|---|---------|----------|----------|------------|

| Ī | CLASSⅢ  | CLASSⅢ   | CLASSIIb | Ⅲ類         |

|   | CLASSIV | CLASSIII | CLASSⅢ   | <b>山</b> 規 |

- 2. 半導体製品は一定の確率で誤動作や故障が生じる場合があります。万が一、誤動作や故障が生じた場合であっても、本製品の不具合により、人の生命、身体、財産への危険又は損害が生じないように、お客様の責任において次の例に示すようなフェールセーフ設計など安全対策をお願い致します。

- ①保護回路及び保護装置を設けてシステムとしての安全性を確保する。

- ②冗長回路等を設けて単一故障では危険が生じないようにシステムとしての安全を確保する。

- 3. 本製品は、下記に例示するような特殊環境での使用を配慮した設計はなされておりません。したがいまして、下記のような特殊環境での本製品のご使用に関し、ロームは一切その責任を負いません。本製品を下記のような特殊環境でご使用される際は、お客様におかれまして十分に性能、信頼性等をご確認ください。

- ①水・油・薬液・有機溶剤等の液体中でのご使用

- ②直射日光・屋外暴露、塵埃中でのご使用

- ③潮風、Cl<sub>2</sub>、H<sub>2</sub>S、NH<sub>3</sub>、SO<sub>2</sub>、NO<sub>2</sub> 等の腐食性ガスの多い場所でのご使用

- ④静電気や電磁波の強い環境でのご使用

- ⑤発熱部品に近接した取付け及び当製品に近接してビニール配線等、可燃物を配置する場合

- ⑥本製品を樹脂等で封止、コーティングしてのご使用

- ⑦はんだ付けの後に洗浄を行わない場合(無洗浄タイプのフラックスを使用される場合は除く。ただし、残渣については十分に確認をお願いします。)又は、はんだ付け後のフラックス洗浄に水又は水溶性洗浄剤をご使用の場合 ⑧結露するような場所でのご使用

- 4. 本製品は耐放射線設計はなされておりません。

- 5. 本製品単体品の評価では予測できない症状・事態を確認するためにも、本製品のご使用にあたってはお客様製品に実装された状態での評価及び確認をお願い致します。

- 6. パルス等の過渡的な負荷(短時間での大きな負荷)が加わる場合は、お客様製品に本製品を実装した状態で必ず その評価及び確認の実施をお願い致します。また、定常時での負荷条件において定格電力以上の負荷を印加されますと、 本製品の性能又は信頼性が損なわれるおそれがあるため必ず定格電力以下でご使用ください。

- 7. 電力損失は周囲温度に合わせてディレーティングしてください。また、密閉された環境下でご使用の場合は、必ず温度 測定を行い、最高接合部温度を超えていない範囲であることをご確認ください。

- 8. 使用温度は納入仕様書に記載の温度範囲内であることをご確認ください。

- 9. 本資料の記載内容を逸脱して本製品をご使用されたことによって生じた不具合、故障及び事故に関し、ロームは一切その責任を負いません。

## 実装及び基板設計上の注意事項

- 1. ハロゲン系(塩素系、臭素系等)の活性度の高いフラックスを使用する場合、フラックスの残渣により本製品の性能 又は信頼性への影響が考えられますので、事前にお客様にてご確認ください。

- 2. はんだ付けは、表面実装製品の場合リフロー方式、挿入実装製品の場合フロー方式を原則とさせて頂きます。なお、表面実装製品をフロー方式での使用をご検討の際は別途ロームまでお問い合わせください。 その他、詳細な実装条件及び手はんだによる実装、基板設計上の注意事項につきましては別途、ロームの実装仕様書をご確認ください。

Notice-PAA-J Rev.004

## 応用回路、外付け回路等に関する注意事項

- 1. 本製品の外付け回路定数を変更してご使用になる際は静特性のみならず、過渡特性も含め外付け部品及び本製品のバラッキ等を考慮して十分なマージンをみて決定してください。

- 2. 本資料に記載された応用回路例やその定数などの情報は、本製品の標準的な動作や使い方を説明するためのもので、 実際に使用する機器での動作を保証するものではありません。したがいまして、お客様の機器の設計において、回路や その定数及びこれらに関連する情報を使用する場合には、外部諸条件を考慮し、お客様の判断と責任において行って ください。これらの使用に起因しお客様又は第三者に生じた損害に関し、ロームは一切その責任を負いません。

## 静電気に対する注意事項

本製品は静電気に対して敏感な製品であり、静電放電等により破壊することがあります。取り扱い時や工程での実装時、保管時において静電気対策を実施のうえ、絶対最大定格以上の過電圧等が印加されないようにご使用ください。特に乾燥環境下では静電気が発生しやすくなるため、十分な静電対策を実施ください。(人体及び設備のアース、帯電物からの隔離、イオナイザの設置、摩擦防止、温湿度管理、はんだごてのこて先のアース等)

## 保管・運搬上の注意事項

- 1. 本製品を下記の環境又は条件で保管されますと性能劣化やはんだ付け性等の性能に影響を与えるおそれがあります のでこのような環境及び条件での保管は避けてください。

- ① 潮風、Cl<sub>2</sub>、H<sub>2</sub>S、NH<sub>3</sub>、SO<sub>2</sub>、NO<sub>2</sub>等の腐食性ガスの多い場所での保管

- ② 推奨温度、湿度以外での保管

- ③ 直射日光や結露する場所での保管

- ④ 強い静電気が発生している場所での保管

- 2. ロームの推奨保管条件下におきましても、推奨保管期限を経過した製品は、はんだ付け性に影響を与える可能性があります。推奨保管期限を経過した製品は、はんだ付け性を確認したうえでご使用頂くことを推奨します。

- 3. 本製品の運搬、保管の際は梱包箱を正しい向き(梱包箱に表示されている天面方向)で取り扱いください。天面方向が 遵守されずに梱包箱を落下させた場合、製品端子に過度なストレスが印加され、端子曲がり等の不具合が発生する 危険があります。

- 4. 防湿梱包を開封した後は、規定時間内にご使用ください。規定時間を経過した場合はベーク処置を行ったうえでご使用ください。

#### 製品ラベルに関する注意事項

本製品に貼付されている製品ラベルに2次元バーコードが印字されていますが、2次元バーコードはロームの社内管理のみを目的としたものです。

#### 製品廃棄上の注意事項

本製品を廃棄する際は、専門の産業廃棄物処理業者にて、適切な処置をしてください。

## 外国為替及び外国貿易法に関する注意事項

本製品は、外国為替及び外国貿易法に定めるリスト規制貨物等に該当するおそれがありますので、輸出する場合には、ロームへお問い合わせください。

## 知的財産権に関する注意事項

- 1. 本資料に記載された本製品に関する応用回路例、情報及び諸データは、あくまでも一例を示すものであり、これらに関する第三者の知的財産権及びその他の権利について権利侵害がないことを保証するものではありません。

- 2. ロームは、本製品とその他の外部素子、外部回路あるいは外部装置等(ソフトウェア含む)との組み合わせに起因して 生じた紛争に関して、何ら義務を負うものではありません。

- 3. ロームは、本製品又は本資料に記載された情報について、ロームもしくは第三者が所有又は管理している知的財産権 そ の他の権利の実施又は利用を、明示的にも黙示的にも、お客様に許諾するものではありません。 ただし、本製品を通 常の用法にて使用される限りにおいて、ロームが所有又は管理する知的財産権を利用されることを妨げません。

## その他の注意事項

- 1. 本資料の全部又は一部をロームの文書による事前の承諾を得ることなく転載又は複製することを固くお断り致します。

- 2. 本製品をロームの文書による事前の承諾を得ることなく、分解、改造、改変、複製等しないでください。

- 3. 本製品又は本資料に記載された技術情報を、大量破壊兵器の開発等の目的、軍事利用、あるいはその他軍事用途目的で使用しないでください。

- 4. 本資料に記載されている社名及び製品名等の固有名詞は、ローム、ローム関係会社もしくは第三者の商標又は登録商標です。

Notice-PAA-J Rev.004

## 一般的な注意事項

- 1. 本製品をご使用になる前に、本資料をよく読み、その内容を十分に理解されるようお願い致します。本資料に記載される注意事項に反して本製品をご使用されたことによって生じた不具合、故障及び事故に関し、ロームは一切その責任を負いませんのでご注意願います。

- 2. 本資料に記載の内容は、本資料発行時点のものであり、予告なく変更することがあります。本製品のご購入及びご使用に際しては、事前にローム営業窓口で最新の情報をご確認ください。

- 3. ロームは本資料に記載されている情報は誤りがないことを保証するものではありません。万が一、本資料に記載された情報の誤りによりお客様又は第三者に損害が生じた場合においても、ロームは一切その責任を負いません。

Notice – WE Rev.001