# TFT-LCD パネル用電源 IC シリーズ

# 12V 入力 多チャンネル システム電源 IC

#### **BM81004MUV**

#### ●概要

BM81004MUV は、液晶 TV 向け TFT-LCD パネル用システム電源です。パネル駆動用電源(SOURCE 用電圧、LOGIC 用電圧)に加えて、正/負チャージポンプコントローラ、Gate Pulse Modulation 機能を内蔵しています。また、各種設定値を保持する EEPROM を有しており、出力電圧や SOFT START 時間等を設定することができます。

# ●特長

- 昇圧 DC/DC コンバータ(AVDD). (同期整流,ロードスイッチ内蔵/外付).

- 降圧 DC/DC コンバータ 1(VIO). (非同期整流).

- 降圧 DC/DC コンバータ 2(VCORE). (同期整流).

- 降圧 DC/DC コンバータ 3(HAVDD). (同期整流).

- 正チャージポンプコントローラ(VGH).

- 負チャージポンプコントローラ(VGL).

- Gate Pulse Modulation(GPM)機能.

- 高耐圧 LDO (50mA).

- 10bit DAC 制御 Gamma アンプ 4ch

- 8bit DAC 制御 VCOM アンプ

- I2C による出力電圧制御. EEPROM 内蔵

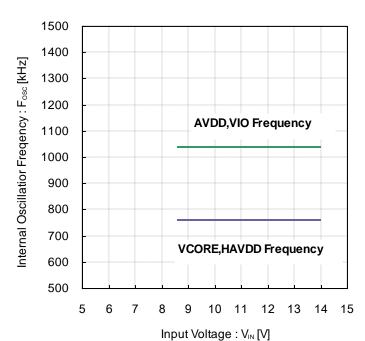

- スイッチング周波数 750kHz. (AVDD, VIO)

- スイッチング周波数 1MHz. (VCORE, HAVDD)

# ●用途

■ TFT-LCD パネル

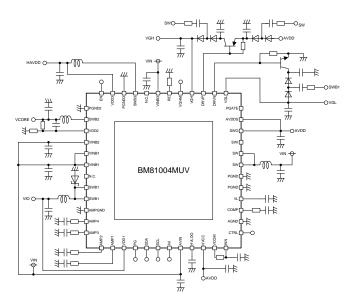

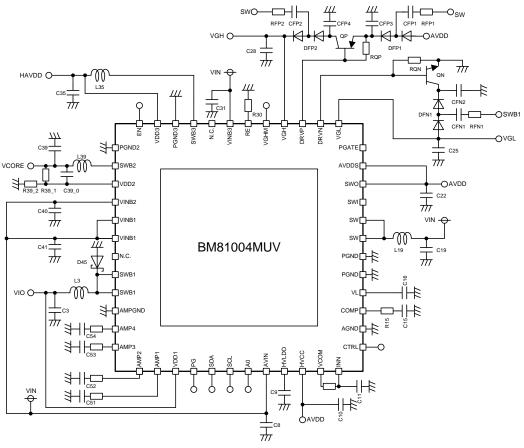

# ●基本アプリケーション回路 1 (TOP VIEW)

#### ●重要特性

■ 入力電圧範囲: 8.6V ~ 14.0V AVDD 出力電圧範囲: 11.7V ~ 18.0V VIO 出力電圧範囲: 2.2V ~ 3.7V ■ HAVDD 出力電圧範囲: 4.8V ~ 11.1V ■ VGH 出力電圧範囲: 25V ~ 40.5V ■ VGL 出力電圧範囲: -10.2V ~ -4.0V ■ スイッチング周波数: 750kHz(Typ.) 1MHz(Typ.) -40°C ~ +105°C ■ 動作温度範囲:

#### ●パッケージ

W(Typ.) x D(Typ.) x H(Max.) VQFN48V7070A 7.00mm x 7.00mm x 1.0mm

Figure 1. Application Circuit 1

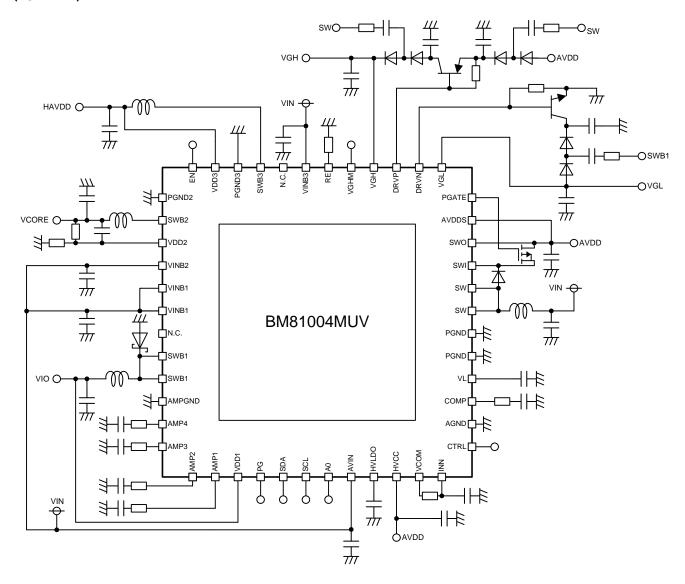

# ●基本アプリケーション回路 2 (TOP VIEW)

Figure 2. Application Circuit 2

# 目 次

| ●概要                        | 1  |

|----------------------------|----|

| ●特長                        | 1  |

| ●用途                        | 1  |

| ●基本アプリケーション回路 1            | 1  |

| ●重要特性                      | 1  |

| ●パッケージ                     | 1  |

| ●基本アプリケーション回路 2            | 2  |

| ●端子配置図                     | 4  |

| ●端子説明                      | 4  |

| ●ブロック図                     | 5  |

| ●各ブロック動作説明                 | 6  |

| ●絶対最大定格                    | 7  |

| ●推奨動作範囲                    | 7  |

| ●電気的特性                     | 8  |

| ●参考データ                     | 12 |

| ●タイミングチャート                 | 24 |

| ●アプリケーション例                 | 25 |

| ●各ブロック保護機能説明               | 26 |

| ●保護機能一覧                    | 28 |

| ●シリアル通信について                | 29 |

| ●Register Map              | 32 |

| ●Command Table 1           | 33 |

| ●Command Table 2           | 34 |

| ●アプリケーション部品選定方法            | 35 |

| ●レイアウトパターン設計について           | 40 |

| <ul><li>●熱損失について</li></ul> | 40 |

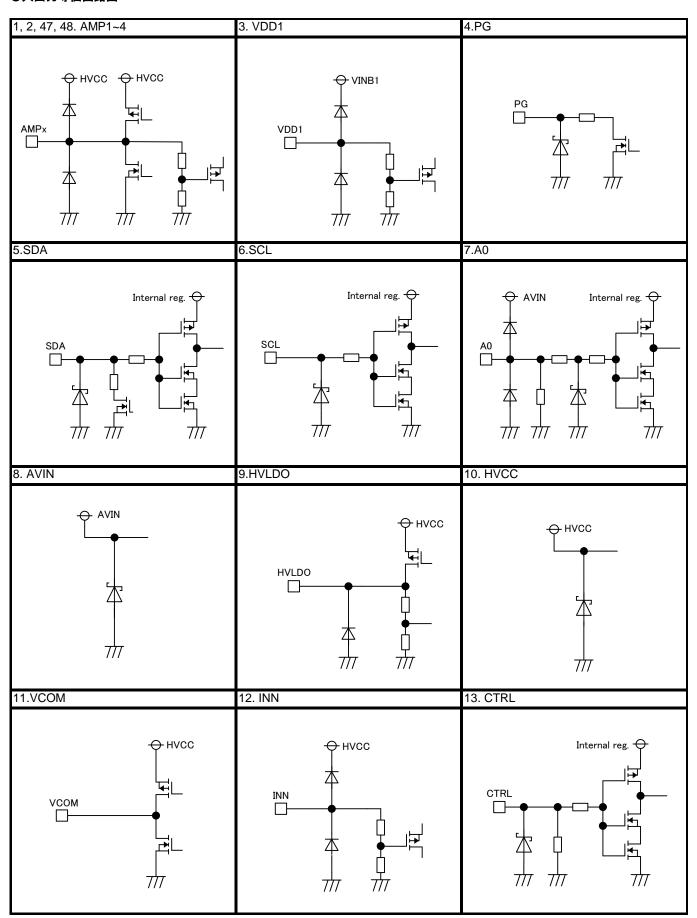

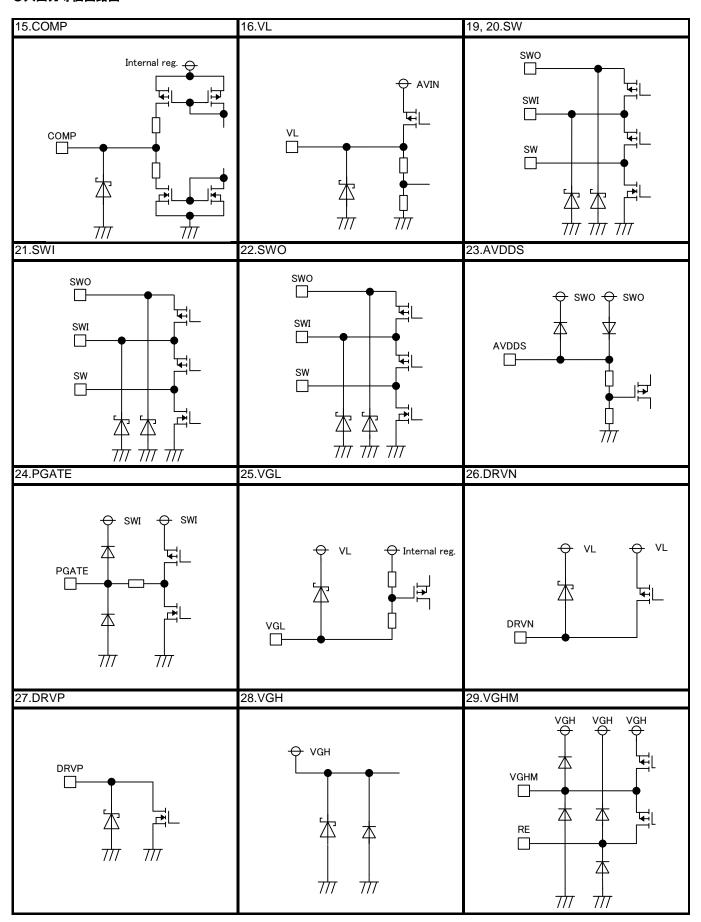

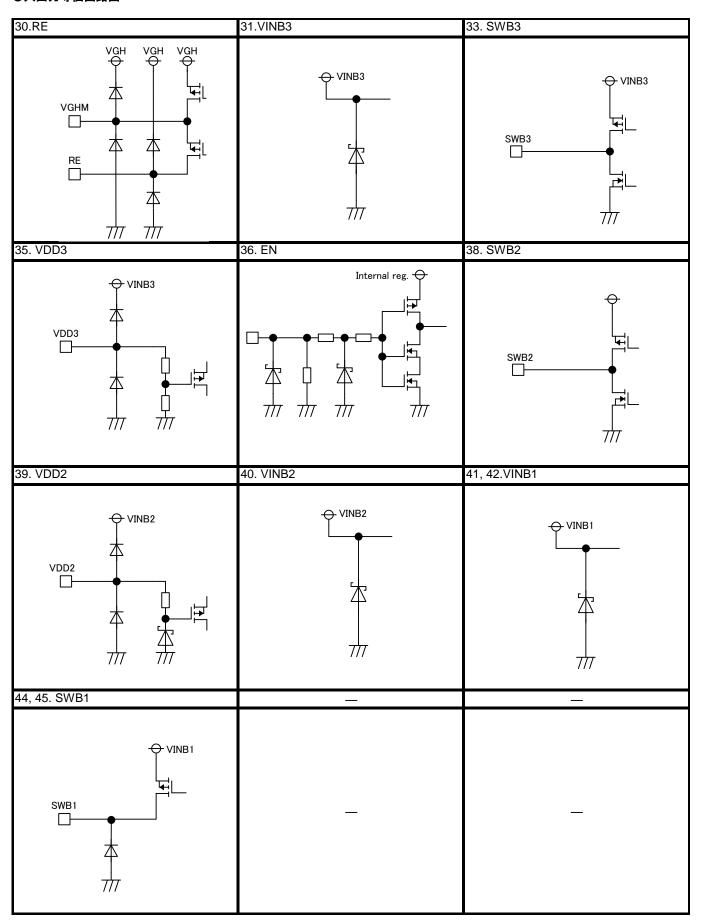

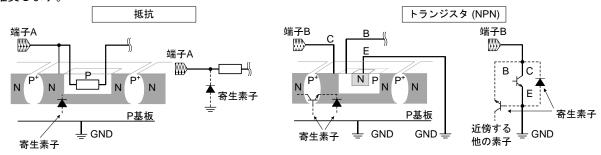

| ●入出力等価回路図                  | 41 |

| ●使用上の注意                    | 44 |

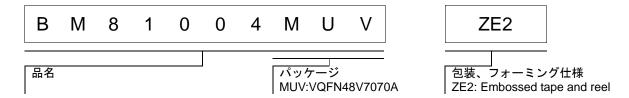

| ●発注形名情報                    | 46 |

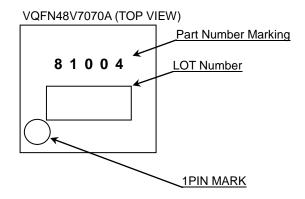

| ●標印図                       | 46 |

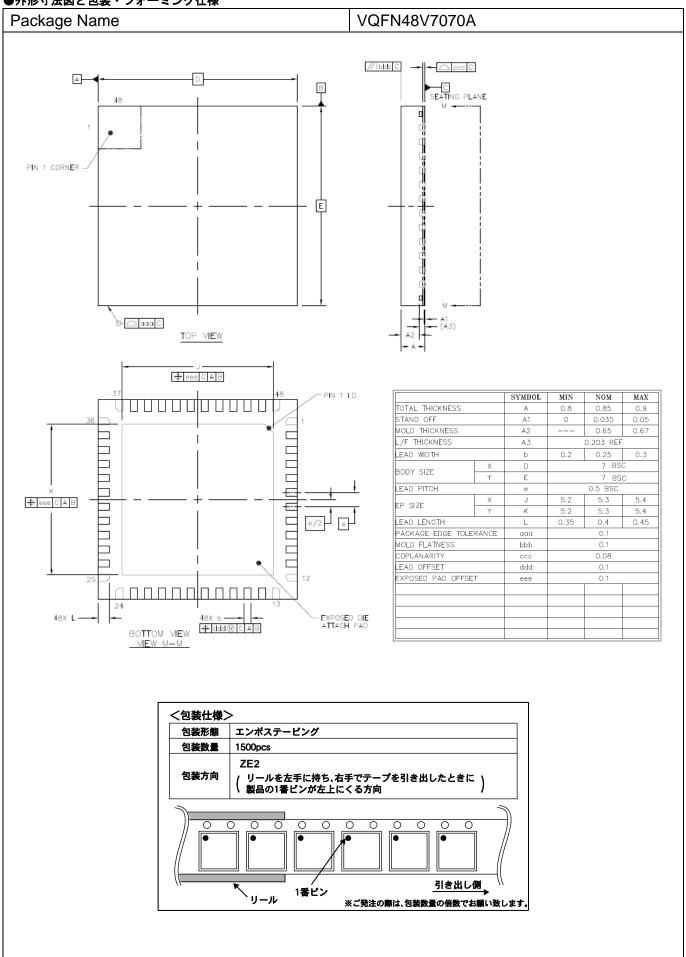

| ●外形寸法図と包装・フォーミング仕様         | 47 |

| ▲冰訂房麻                      | 19 |

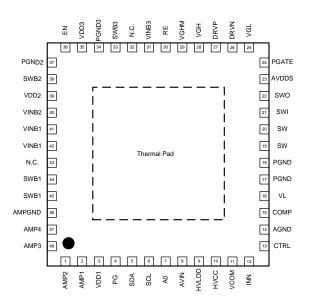

# ●端子配置図 (TOP View)

Figure 3. Pin Configuration

# ●端子説明

| 端子番号 | 記号    | 機 能                 | 端子番号 | 記号     | 機能                  |

|------|-------|---------------------|------|--------|---------------------|

| 1    | AMP2  | Gamma アンプ出力端子 2     | 25   | VGL    | 負チャージポンプ出力端子        |

| 2    | AMP1  | Gamma アンプ出力端子 1     | 26   | DRVN   | 負チャージポンプ ドライブ端子     |

| 3    | VDD1  | 降圧 DC/DC 出力端子 1     | 27   | DRVP   | 正チャージポンプ ドライブ端子     |

| 4    | PG    | Power GOOD 信号出力端子   | 28   | VGH    | 正チャージポンプ出力端子        |

| 5    | SDA   | シリアルデータ入力端子         | 29   | VGHM   | GPM 出力端子            |

| 6    | SCL   | シリアルクロック入力端子        | 30   | RE     | GPM スロープ調整端子        |

| 7    | A0    | I2C アドレス選択端子        | 31   | VINB3  | 降圧 DC/DC 用電源端子 3    |

| 8    | AVIN  | 電源入力端子              | 32   | N.C.   | -                   |

| 9    | HVLDO | 高耐圧 LDO 出力端子        | 33   | SWB3   | 降圧 DC/DC スイッチング端子 3 |

| 10   | HVCC  | VCOM & Gamma 用電源端子  | 34   | PGND3  | 降圧 DC/DC 用 GND 端子 3 |

| 11   | VCOM  | VCOM アンプ出力端子        | 35   | VDD3   | 降圧 DC/DC 出力端子 3     |

| 12   | INN   | VCOM アンプ負帰還端子       | 36   | EN     | イネーブル端子             |

| 13   | CTRL  | GPM コントロール端子        | 37   | PGND2  | 降圧 DC/DC 用 GND 端子 2 |

| 14   | AGND  | アナログ GND 端子         | 38   | SWB2   | 降圧 DC/DC スイッチング端子 2 |

| 15   | COMP  | エラーアンプ出力端子          | 39   | VDD2   | 降圧 DC/DC 出力端子 2     |

| 16   | VL    | 内部 REG 出力端子         | 40   | VINB2  | 降圧 DC/DC 用電源端子 2    |

| 17   | PGND  | 昇圧 DC/DC GND 端子     | 41   | VINB1  | 降圧 DC/DC 用電源端子 1    |

| 18   | PGND  | 昇圧 DC/DC GND 端子     | 42   | VINB1  | 降圧 DC/DC 用電源端子 1    |

| 19   | SW    | 昇圧 DC/DC スイッチング端子   | 43   | N.C.   | <del></del>         |

| 20   | SW    | 昇圧 DC/DC スイッチング端子   | 44   | SWB1   | 降圧 DC/DC スイッチング端子 1 |

| 21   | SWI   | ロードスイッチ入力端子         | 45   | SWB1   | 降圧 DC/DC スイッチング端子 1 |

| 22   | SWO   | ロードスイッチ出力端子         | 46   | AMPGND | Gamma アンプ用 GND 端子   |

| 23   | AVDDS | 昇圧 DC/DC 出力帰還端子     | 47   | AMP4   | Gamma アンプ出力端子 4     |

| 24   | PGATE | ロードスイッチ GATE ドライブ端子 | 48   | AMP3   | Gamma アンプ出力端子 3     |

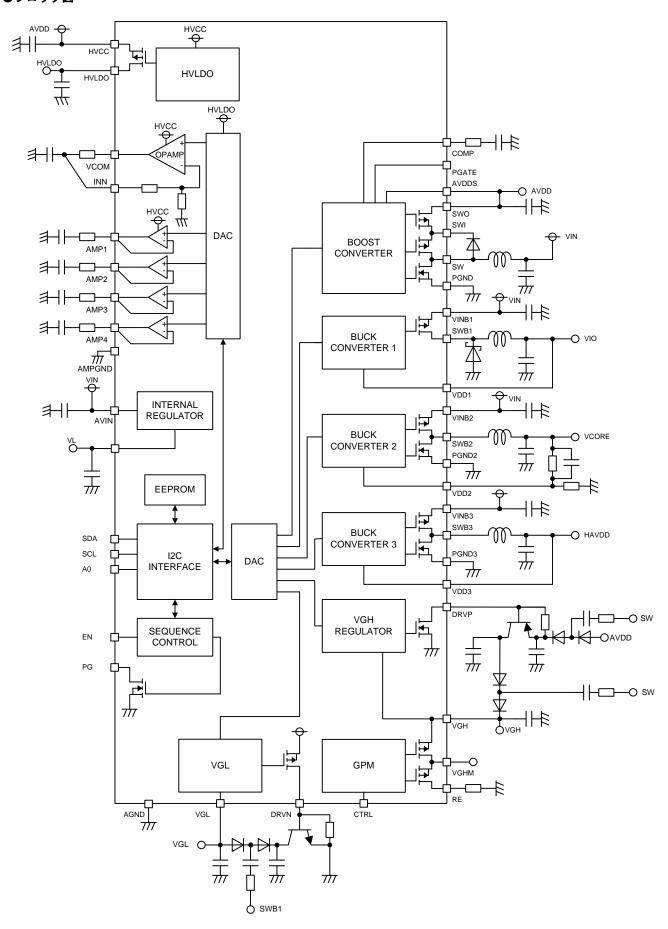

# ●ブロック図

Figure 4. Block Diagram

#### ●各ブロック動作説明

#### 1 BUCK CONVERTER BLOCK 2

電源電圧から VCORE(VDD2)電圧を生成するブロックです。

VIN の UVLO 解除後に VL が起動し、EEPROM への Auto Read が動作した後に VCORE は起動します。 動作中は OVP, UVP, OCP の保護機能により、IC の破壊を防止します。

#### ② BUCK CONVERTER BLOCK 1

電源電圧から VIO(VDD1)電圧を生成するブロックです。

VCORE の起動した後に VIO は起動します。

VIN 起動時に Power On Reset が働き、EEPROM に書き込まれた設定が Register に反映されます。 動作中は OVP, UVP, OCP の保護機能により、IC の破壊を防止します。

#### ③ VGL REGULATOR BLOCK

VGL 電圧を生成するブロックです。

VCORE 起動完了後、VGL は起動を開始します。

VIN 起動時に Power On Reset が働き、EEPROM に書き込まれた設定が Register に反映されます。 動作中は UVP, OCP の保護機能により、IC の破壊を防止します

#### **4** BOOST CONVERTER BLOCK

電源電圧から AVDD(SWO)電圧を生成するブロックです。

VCORE, VIO, VGL が起動した状態で、EN=H となることで起動します。

HAVDD 電圧の設定電圧範囲は AVDD 設定電圧に依存し、

HAVDD 電圧の下限値は AVDD×0.4 に制限されます。

VIN 起動時に Power On Reset が働き、EEPROM に書き込まれた設定が Register に反映されます。 動作中は OVP, UVP, OCP の保護機能により、IC の破壊を防止します。

#### 5 BUCK CONVERTER BLOCK 3

電源電圧から HAVDD(VDD3)電圧を生成するブロックです。

HAVDD 電圧は、AVDD 電圧に追従して起動します。

VIN 起動時に Power On Reset が働き、EEPROM に書き込まれた設定が Register に反映されます。 動作中は OVP, UVP, OCP の保護機能により、IC の破壊を防止します。

#### 6 HIGH VOLTAGE LDO BLOCK

AVDD(HVCC)電圧から HVLDO 電圧を生成するブロックです。

HVLDO 電圧は、AVDD 電圧に追従して起動します。

VIN 起動時に Power On Reset が働き、EEPROM に書き込まれた設定が Register に反映されます。 動作中は UVP, OCP の保護機能により、IC の破壊を防止します。

#### VCOM AMPLIFIER BLOCK

AVDD (HVCC) 電圧から VCOM 電圧を生成するブロックです。VCOM 電圧設定用のキャリブレーターが内蔵されており、VCOM 電圧は、AVDD 電圧に追従して起動します。

VIN 起動時に Power On Reset が働き、EEPROM に書き込まれた設定が Register に反映されます。

#### **8** GAMMA AMPLIFIER BLOCK

AVDD(HVCC) 電圧から AMP1~4 電圧を生成するブロックです。

AMP1~4 電圧は、AVDD 電圧に追従して起動します。

VIN 起動時に Power On Reset が働き、EEPROM に書き込まれた設定が Register に反映されます。

# 9 VGH REGULATOR BLOCK

AVDD 電圧から VGH 電圧を生成するブロックです。

AVDD 起動完了後、VGH は起動を開始します。

VIN 起動時に Power On Reset が働き、EEPROM に書き込まれた設定が Register に反映されます。 動作中は OVP, UVP, OCP の保護機能により、IC の破壊を防止します。

# (1) GPM BLOCK

PMOS FET で構成された TFT のゲート電圧を駆動する為のスイッチ回路です。 VGHM 出力は CTRL 入力と同期し、CTRL=H の時 High 電圧=VGH を出力します。 GPM Falling Limit 電圧は EEPROM で設定可能です。

#### ※ ご注意

- ・EN 端子は入力トレラント対応です。EN>VIN となっても問題ありません。

- · PG 端子を使用しない場合は、GND にショート、またはオープンにしてください。

# ●絶対最大定格

| 項目                                         | ÷1 P                                                                 |      | 定格   |     | <b>#</b> /- |

|--------------------------------------------|----------------------------------------------------------------------|------|------|-----|-------------|

| 項目                                         | 記号                                                                   | MIN  | TYP  | MAX | 単位          |

| Cumply Valtage                             | AVIN, VINB1, VINB2, VINB3                                            | -0.3 | -    | 24  | V           |

| Supply Voltage                             | HVCC                                                                 | -0.3 | -    | 20  | V           |

| Input Voltage                              | SDA, SCL, A0, EN, CTRL                                               | -0.3 | -    | 7   | V           |

|                                            | VL                                                                   | -0.3 | -    | 6.5 | V           |

| Output Voltage                             | COMP, PG                                                             | -0.3 | -    | 7   | V           |

|                                            | SW, SWI, SWO,<br>PGATE, AVDDS, VDD1, SWB1,<br>VDD2, SWB2, VDD3, SWB3 | -0.3 | -    | 24  | V           |

|                                            | HVLDO, VCOM, INN<br>AMP1, AMP2, AMP3, AMP4                           | -0.3 | -    | 20  | V           |

|                                            | VGL, DRVN                                                            | -15  | -    | 7   | V           |

|                                            | DRVP, VGH, VGHM, RE                                                  | -0.3 | -    | 48  | V           |

| Operating Ambient<br>Temperature Range     | Та                                                                   | -40  | -    | 105 | °C          |

| Storage Temperature<br>Range               | Tstg                                                                 | -55  | -    | 150 | °C          |

| Maximum Continuous<br>Junction Temperature | Tjmax (*1)                                                           | -    | -    | 150 | °C          |

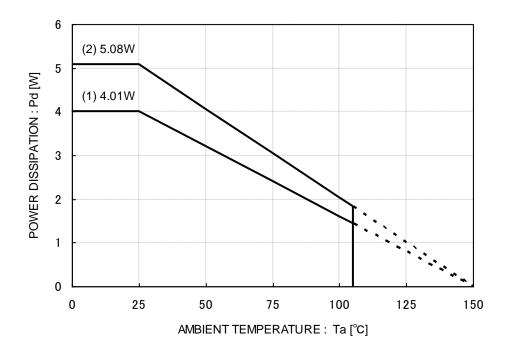

| Power Discipation (*2)                     | Pd                                                                   |      |      | W   |             |

| Power Dissipation (*2)                     | $\theta$ ja                                                          |      | 24.6 |     | degC/W      |

# ●推奨動作範囲

(Ta=-40°C~105°C)

| 項目             | 記号           |      | 単位  |     |     |  |

|----------------|--------------|------|-----|-----|-----|--|

| <b>埃</b> 日     | 記ち           | MIN  | TYP | MAX | +12 |  |

| Supply Voltage | AVIN         | 8.6  | -   | 14  | V   |  |

| 機能端子電圧         | EN, A0, CTRL | -0.1 | -   | 5.5 | V   |  |

| 2 線シリアル端子電圧    | SDA, SCL     | -0.1 | -   | 5.5 | V   |  |

| 2線シリアル周波数      | FCLK         | -    | -   | 400 | kHz |  |

<sup>\*1</sup> 保存時の接合温度を示します。

\*2 Derating in done 40.6mW/°C for operating above Ta≥25°C(On 4-layer 76.2mm×114.3mm×1.6mm board).

(特に記載のない限り、Ta=25°C, AVIN, VINB1, VINB2. VINB3=12V)

| に記載のない限り、Ta=25℃, AVIN                 |                    |        |               |        |      |                                                       |

|---------------------------------------|--------------------|--------|---------------|--------|------|-------------------------------------------------------|

| 項目                                    | 記号                 | MIN    | TYP           | MAX    | 単位   | 条件                                                    |

| [ GENERAL ]                           |                    |        |               |        |      |                                                       |

| VIN Under Voltage                     | VIN_               | 8.0    | 8.3           | 8.6    | V    | VIN rising                                            |

| Lockout Threshold                     | UVLO               | 7.25   | 7.55          | 7.85   | V    | VIN falling                                           |

| Thermal shutdown                      | TSD                | 155    | 175           | 195    | °C   | Design guarantee                                      |

| Internal Oscillator Frequency 1       | FOSC1              | 600    | 750           | 900    | kHz  | AVDD, VIO, 0 < Ta < 50°C                              |

| Internal Oscillator Frequency 2       | FOSC2              | 800    | 1000          | 1200   | kHz  | VCORE, HAVDD, 0 < Ta < 50°C                           |

| VL Voltage                            | VL                 | 4.9    | 5             | 5.1    | V    |                                                       |

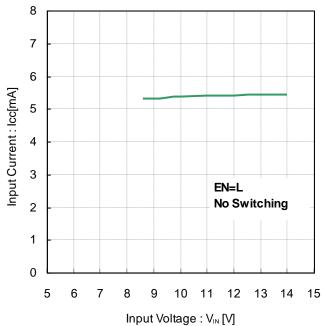

| Consumption Current                   | ICC                | -      | 5.4           | -      | mA   | Not Switching                                         |

| [ LOGIC SIGNALS SDA, SCL,             | EN, A0, CTR        | L ]    |               |        |      |                                                       |

| High Level Input Voltage              | VIH                | 2      | -             | -      | V    |                                                       |

| Low Level Input Voltage               | VIL                | -      | -             | 0.5    | V    |                                                       |

| Minimum Output Voltage                | VSDA               | -      | -             | 0.4    | V    | SDA, ISDA=3mA                                         |

| Pull-Down Resistance                  | RLOGIC             | 140    | 200           | 260    | kΩ   | EN, A0, CTRL                                          |

| [ BOOST CONVERTER (AVDE               | ) ]                |        |               |        |      |                                                       |

| Output Voltage Range                  | AVDD               | 11.7   | -             | 18.0   | V    | 0.1V step                                             |

| Regulation Voltage                    | AVDD_R             | 15.444 | 15.6          | 15.756 | V    | 27h, 1%, 0 < Ta < 50°C                                |

| Hi-Side Leakage Current               | ILK_SWH            | -      | 0             | 10     | uA   | SWI=18V, SW=0V                                        |

| Hi-Side SW ON-Resistance              | RON_SWH            | -      | 100           | 200    | mΩ   | ISW=-500mA                                            |

| Lo-Side SW Leakage Current            | ILK_SWL            | -      | 0             | 10     | uA   | SW=18V                                                |

| Lo-Side SW ON-Resistance              | RON_SWL            | -      | 100           | 200    | mΩ   | ISW=500mA                                             |

| Load SW ON-Resistance                 | RON_LS             | -      | 100           | 200    | mΩ   | ILS=500mA                                             |

| SW Current Limit                      | ILIM_SW            | 4.25   | 5             | 5.75   | А    | 5.0A – Offset(0.0A) setting<br>L=6.8uH, 0 < Ta < 50°C |

| SW Current Limit Offset               | ILIM_SET           | 0      | -             | 2.8    | Α    | 0.4A step                                             |

| Over-Voltage Protection Rise          | VOVP_AVD<br>D_RISE | 18     | 19.5          | 21     | V    |                                                       |

| Over-Voltage Protection Fall          | VOVP_AVD<br>D_FALL | -      | 18            | -      | V    |                                                       |

| AVDD UVP Detecting Voltage            | VUVP_<br>AVDD      | -      | AVDD<br>x 0.8 | -      | V    |                                                       |

| Soft Start Time                       | TSS_<br>AVDD       | 10     | -             | 20     | msec |                                                       |

| Load Switch Current Limit             | ILIM_LSW           | -      | 7             | -      | А    |                                                       |

| External Load Switch<br>Current Limit | ILIM_EXT           | 450    | 540           | 630    | mV   |                                                       |

| PGATE Drive Capability                | PGATE_<br>DRV      | -      | 10            | -      | uA   |                                                       |

(特に記載のない限り、Ta=25℃, AVIN, VINB1, VINB2, VINB3=12V)

| 項目                                    | 記号             |                 | 規格値            |                 | 単位   | 条件                       |

|---------------------------------------|----------------|-----------------|----------------|-----------------|------|--------------------------|

| · · · · · · · · · · · · · · · · · · · | 配力             | MIN             | TYP            | MAX             | 中四   | 木 IT                     |

| [ BUCK CONVERTER 1 (VIO)              | ]              |                 |                |                 | T    |                          |

| Output Voltage Range                  | VIO            | 2.2             | -              | 3.7             | V    | 0.1V step                |

| Regulation Voltage                    | VIO_R          | 3.234           | 3.3            | 3.366           | V    | 0Bh, 2%, 0 < Ta < 50°C   |

| Hi-Side SWB1 Leak Current             | ILK_<br>SWB1H  | -               | 0              | 10              | uA   | VINB1=18V, SWB1=0V       |

| Hi-Side SWB1 ON-Resistance            | RON_<br>SWB1H  | -               | 200            | 300             | mΩ   | SWB1=-500mA              |

| SWB1 Current Limit                    | ILIM_<br>SWB1  | 2.8             | 3.5            | 4.2             | Α    | L=6.8uH, 0 < Ta < 50°C   |

| VIO Over-Voltage Protection           | VOVP_<br>VIO   | VIO<br>x 1.03   | VIO<br>x 1.1   | VIO<br>x 1.17   | V    |                          |

| VIO UVP Detecting Voltage             | VUVP_<br>VIO   | -               | VIO<br>x 0.8   | -               | V    | Frequency 1/4            |

| Soft Start Time                       | TSS_VIO        | -               | 3.3            | -               | msec | VIO=3.3V                 |

| [ BUCK CONVERTER 2 (VCO               | RE) ]          |                 |                |                 |      |                          |

| VCORE Reference Voltage               | VCORE_         | 0.396           | 0.400          | 0.404           | V    | 1%, Ta=25°C              |

| VCORE Reference voltage               | REF            | 0.394           | 0.400          | 0.406           | V    | 1.5%, 0 < Ta < 50°C      |

| Hi-Side SWB2 Leak Current             | ILK_<br>SWB2H  | -               | 0              | 10              | uA   | VINB2=18V, SWB2=0V       |

| Hi-Side SWB2 ON-Resistance            | RON_<br>SWB2H  | -               | 175            | 300             | mΩ   | SWB2=-500mA              |

| Lo-Side SWB2 Leak Current             | ILK_<br>SWB2L  | -               | 0              | 10              | uA   | SWB2=18V                 |

| Lo-Side SWB2 ON-Resistance            | RON_<br>SWB2L  | -               | 175            | 300             | mΩ   | SWB2=500mA               |

| SWB2 Current Limit                    | ILIM_<br>SWB2  | 2.4             | 3.0            | 3.6             | А    | L=6.8uH, 0 < Ta < 50°C   |

| VCORE Over-Voltage<br>Protection      | VOVP_<br>VCORE | VCORE<br>x 1.03 | VCORE<br>x 1.1 | VCORE<br>x 1.17 | V    |                          |

| VCORE UVP Detecting Voltage           | VUVP_<br>VCORE | -               | VCORE<br>x 0.8 | -               | V    | Frequency 1/4            |

| Soft Start Time                       | TSS_<br>VCORE  | -               | 3              | -               | msec |                          |

| [ BUCK CONVERTER 3 (HAVE              | DD) ]          |                 |                |                 |      |                          |

| Output Voltage Range                  | HAVDD          | 4.8             | -              | 11.1            | V    | 0.1V step                |

| Regulation Voltage                    | HAVDD_R        | 7.68            | 7.8            | 7.92            | V    | 1Eh, 1.5%, 0 < Ta < 50°C |

| Hi-Side SWB3 Leak Current             | ILK_<br>SWB3H  | -               | 0              | 10              | uA   | VINB3=18V, SWB3=0V       |

| Hi-Side SWB3 ON-Resistance            | RON_<br>SWB3H  | -               | 300            | 500             | mΩ   | SWB3=-500mA              |

| Lo-Side SWB3 Leak Current             | ILK_<br>SWB3L  | -               | 0              | 10              | uA   | SWB3=18V                 |

| Lo-Side SWB3 ON-Resistance            | RON_<br>SWB3L  | -               | 300            | 500             | mΩ   | SWB3=500mA               |

| SWB3 Current Limit                    | ILIM_<br>SWB3  | 1.2             | 1.8            | 2.4             | Α    | L=6.8uH, 0 < Ta < 50°C   |

| HAVDD Over-Voltage<br>Protection      | VOVP_<br>HAVDD | HAVDD<br>x 1.03 | HAVDD<br>x 1.1 | HAVDD<br>x 1.17 | V    |                          |

| HAVDD UVP Detecting Voltage           | VUVP_<br>HAVDD | -               | HAVDD<br>x 0.8 | -               | V    | Frequency 1/4            |

(特に記載のない限り、Ta=25℃, AVIN, VINB1, VINB2, VINB3=12V)

| に記載のない限り、Ta=25°C, AVIN      |               |       | <del>,</del><br>規 格 値 |       | 単位   | 夕 ル                                |

|-----------------------------|---------------|-------|-----------------------|-------|------|------------------------------------|

| 項目                          | 記号            | MIN   | TYP                   | MAX   | 単位   | 条件                                 |

| [ VGH REGULATOR ]           |               |       |                       |       |      |                                    |

| Output Voltage Range        | VGH           | 25    | -                     | 40.5  | V    | 0.5V step                          |

| Regulation Voltage          | VGH_R         | 34.47 | 35                    | 35.53 | V    | 14h, 1.5%, 0 < Ta < 50°C<br>Io=5mA |

| Over-Current Protection     | ILIM_<br>DRVP | 5     | -                     | -     | mA   |                                    |

| VGH Over-Voltage Protection | VOVP_<br>VGH  | 42    | 45                    | 48    | V    |                                    |

| VGH UVP Detecting Voltage   | VUVP_<br>VGH  | -     | VGH<br>x 0.8          | -     | V    |                                    |

| Soft Start Time             | TSS_VGH       | -     | 7                     | -     | msec | VGH=35V                            |

| [ VGL REGULATOR ]           |               |       |                       |       |      |                                    |

| Output Voltage Range        | VGL           | -10.2 | -                     | -4.0  | V    | 0.2V step                          |

| Regulation Voltage          | VGL R         | -6.09 | -6                    | -5.91 | V    | 0Ah, 1.5%, Ta=25°C<br>Io=5mA       |

| Regulation voltage          | VGL_K         | -6.12 | -6                    | -5.88 | V    | 0Ah, 2.0%, 0 < Ta < 50°C<br>Io=5mA |

| Over-Current Protection     | ILIM_<br>DRVN | 5     | -                     | -     | mA   |                                    |

| VGL UVP Detecting Voltage   | VUVP_<br>VGL  | -     | VGL×0.8               | -     | V    |                                    |

| Delay Time                  | TDLY_VGL      | -     | 2.5                   | -     | msec |                                    |

| [ GATE PULSE MODULATION     | (GPM) ]       |       |                       |       | '    |                                    |

| VGH-VGHM ON-Resistance      | RGHH          | -     | 3                     | 5     | Ω    |                                    |

| RE-VGHM ON-Resistance       | RGHL          | -     | 3                     | -     | Ω    |                                    |

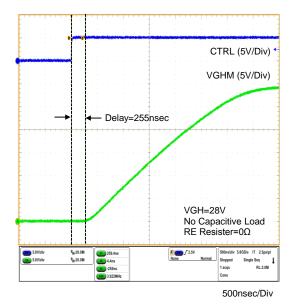

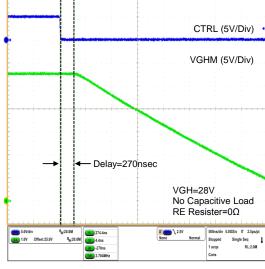

| Propagation Delay           | TGPM          | 150   | 250                   | 350   | nsec |                                    |

(特に記載のない限り、Ta=25℃, AVIN, VINB1, VINB2, VINB3=12V)

| 項目                                            | 記号           | ,              | <del></del> 規 格 値 |                | 単位     | 条件                                                                             |

|-----------------------------------------------|--------------|----------------|-------------------|----------------|--------|--------------------------------------------------------------------------------|

| <b>坦</b>                                      | 配石           | MIN            | TYP               | MAX            | 半四     | * 11                                                                           |

| 【 HIGH VOLTAGE LDO 】                          |              |                |                   |                | 1      |                                                                                |

| Output Voltage Range                          | LDO          | 11.7           | _                 | 18.0           | V      | 0.1V step                                                                      |

| Regulation Voltage                            | LDO_R        | 15.12          | 15.2              | 15.28          | V      | 23h, 0.5%                                                                      |

|                                               | LDO_R        | 15.09          | 15.2              | 15.31          | V      | 23h, 0.7%, 0 < Ta < 50°C                                                       |

| Over-Current Protection                       | ILIM_<br>LDO | -              | 100               | -              | mA     |                                                                                |

| HVLDO UVP Detecting Voltage                   | LDO_UVP      | 1              | LDOx0.8           | -              | V      |                                                                                |

| I/O Differential Voltage                      | LDO_DIF      | -              | 0.2               | 0.5            | V      | HVCC=15V, Io=50mA                                                              |

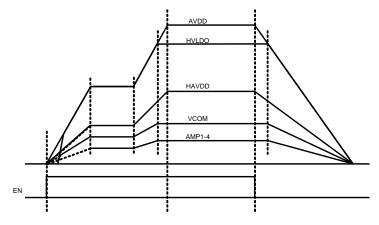

| [ VCOM AMPLIFIER ]                            |              |                |                   |                |        |                                                                                |

| Output Voltage Range                          | VCOM_R       | HVLDO<br>X0.36 | _                 | HVLDO<br>X0.54 | V      |                                                                                |

| Slew Rate                                     | SR           | -              | 30                | -              | V/usec | No external components                                                         |

| Output Current Capability                     | I_VCOM       | -              | ±200              | -              | mA     | C2h                                                                            |

| Load Stability                                | Δ VO1        | -              | ±15               | -              | mV     | Io=-50mA~50mA                                                                  |

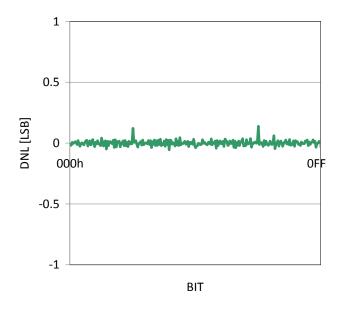

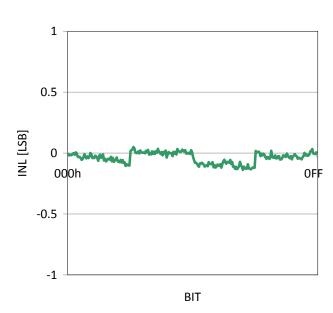

| DAC Resolution                                | RES1         |                | 8                 |                | Bit    |                                                                                |

| DAC Integral Non-linearity Error (INL)        | LE1          | -1             | -                 | +1             | LSB    | 02~FD is the allowable margin of error against the ideal linear.               |

| DAC Differential Non-linearity<br>Error (DNL) | DLE1         | -1             | -                 | +1             | LSB    | 02~FD is the allowable margin of error against the ideal increase of 1LSB.     |

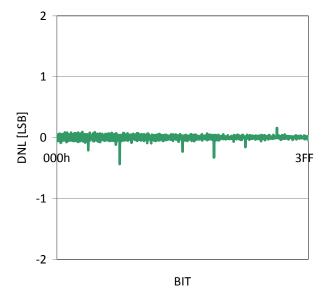

| 【 GAMMA AMPLIFIER 】                           |              |                |                   |                |        |                                                                                |

| Output Current Capability                     | I_AMP        | 30             | -                 | -              | mA     |                                                                                |

| Load Stability                                | ΔVO2         | -              | ±15               | -              | mV     | Io=-5mA~5mA                                                                    |

| DAC Resolution                                | RES2         |                | 10                |                | Bit    |                                                                                |

| DAC Integral Non-linearity Error (INL)        | LE2          | -2             | -                 | +2             | LSB    | 00F ~ 3F0 is the allowable margin of error against the ideal linear.           |

| DAC Differential Non-linearity<br>Error (DNL) | DLE2         | -2             | -                 | +2             | LSB    | 00F ~ 3F0 is the allowable margin of error against the ideal increase of 1LSB. |

〇本製品は、耐放射線設計は行っておりません。

Figure 5. Input Current vs Input Voltage (EN=L, スイッチング停止時)

Figure 6. Internal Oscillator Frequency vs Input Voltage

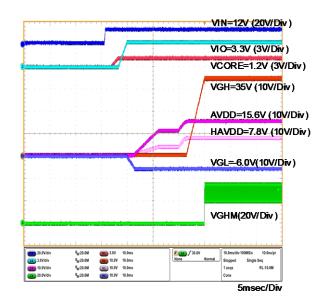

Figure 7. 起動波形 (AVDD・VGH 起動まで)

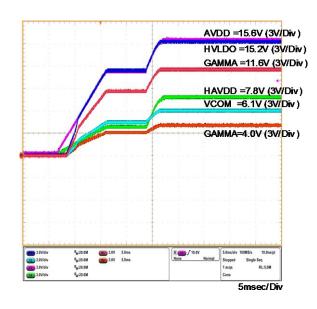

Figure 8. 起動波形 (AVDD 起動後)

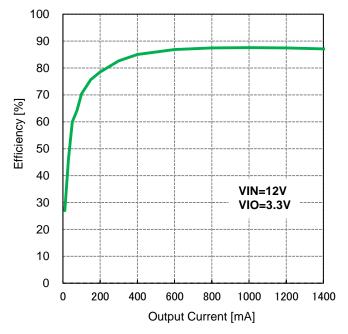

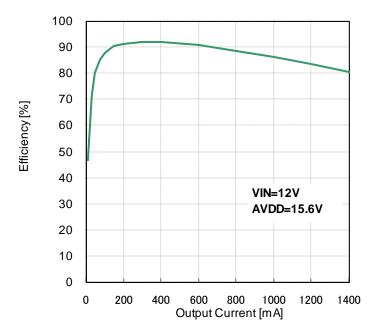

Figure 9. VIO Efficiency vs Output Current

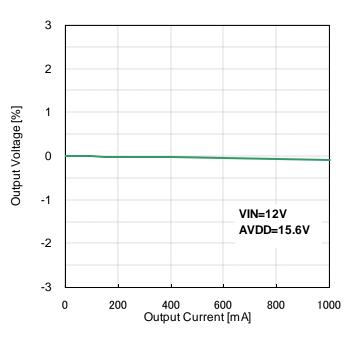

Figure 10. VIO Output Voltage vs Output Current

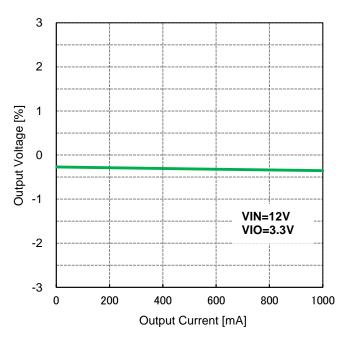

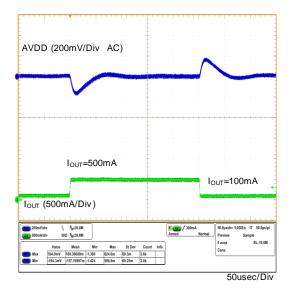

Figure 11. VIO 負荷応答

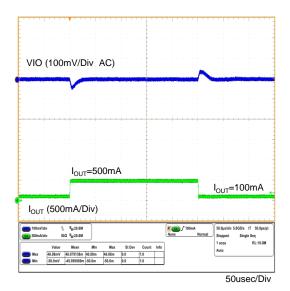

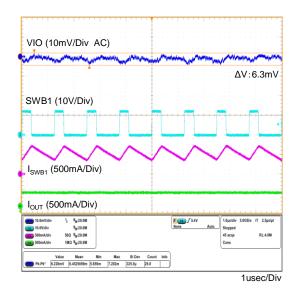

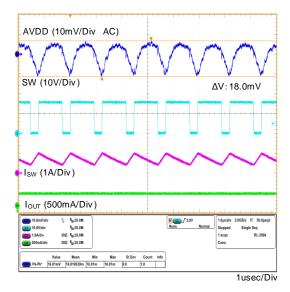

Figure 12. VIO スイッチング波形 (Output Current=500mA)

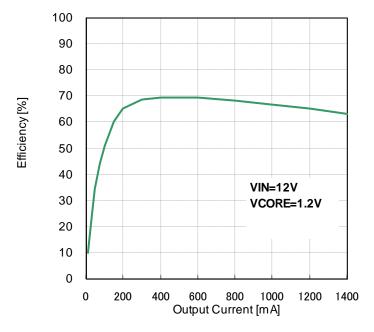

Figure 13. VCORE Efficiency vs Output Current

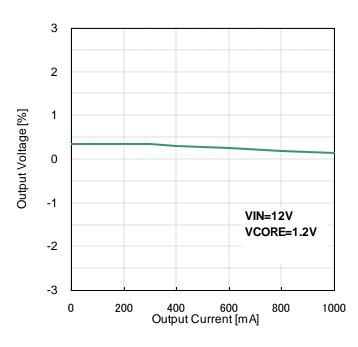

Figure 14. VCORE Output Voltage vs Output Current

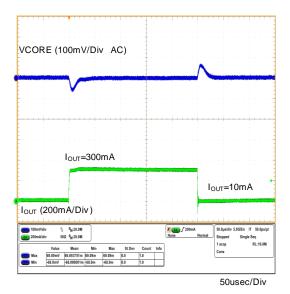

Figure 15. VCORE 負荷応答

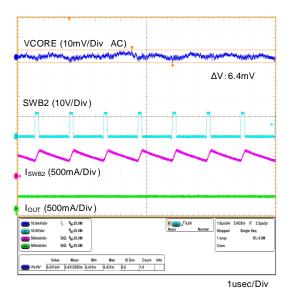

Figure 16. VCORE スイッチング波形 (Output Current=500mA)

3 2 Output Voltage [%] 1 0 -1 VIN=12V AVDD=15.6V -2 HAVDD=7.8V (source) -3 0 200 400 600 800 1000 Output Current [mA]

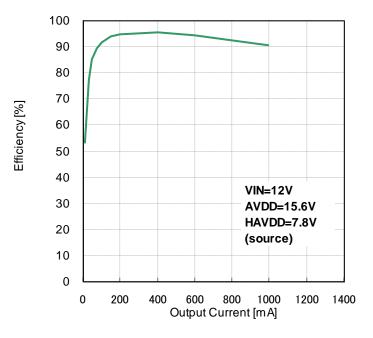

Figure 17. HAVDD Efficiency vs Output Current (source)

Figure 18. HAVDD Output Voltage vs Output Current (source)

HAVDD (10mV/Div AC)

SWB3 (10V/Div)

| SWB3 (500mA/Div)

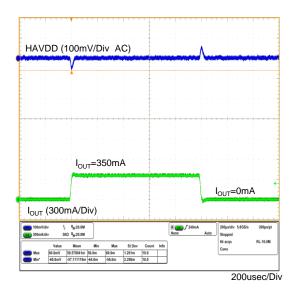

Figure 19. HAVDD 負荷応答 (source)

Figure 20. HAVDD スイッチング波形(source) (Output Current=500mA)

3 2 Output Voltage [%] 1 0 -1 VIN=12V AVDD=15.6V -2 HAVDD=7.8V (sink) -3 0 200 400 600 800 1000 Output Currnet [mA]

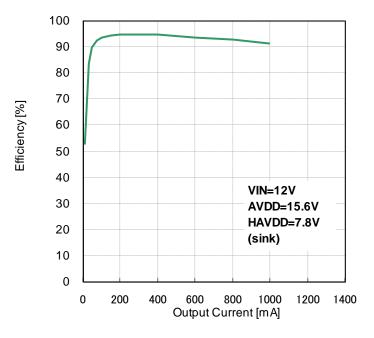

Figure 21. HAVDD Efficiency vs Output Current (sink)

Figure 22. HAVDD Output Voltage vs Output Current (sink)

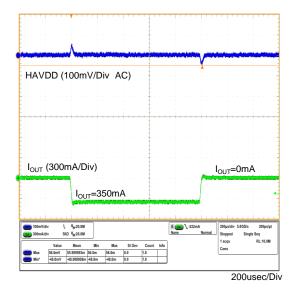

Figure 23. HAVDD 負荷応答 (sink)

Figure 24. HAVDD スイッチング波形(sink) (Output Current=500mA)

Figure 25. AVDD Efficiency vs Output Current

Figure 26. AVDD Output Voltage vs Output Current

Figure 27. AVDD 負荷応答

Figure 28. AVDD スイッチング波形 (Output Current=500mA)

Figure 29. VGH 負荷応答

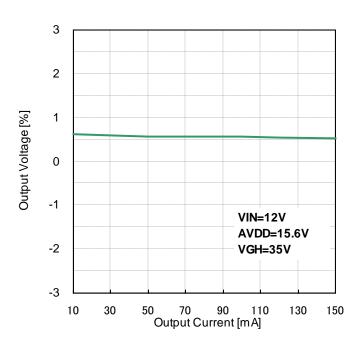

Figure 30. VGH Output Voltage vs Output Current

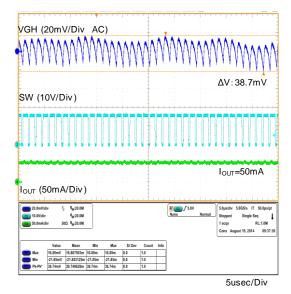

Figure 31. VGH リップル電圧

Figure 32. VGL 負荷応答

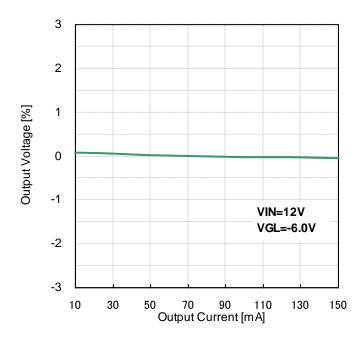

Figure 33. VGL Output Voltage vs Output Current

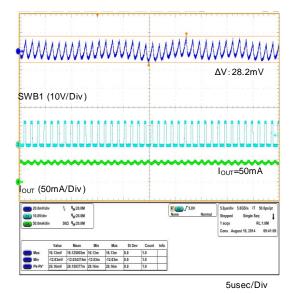

Figure 34. VGL リップル電圧

(特に記載のない限り、Ta=25°C, AVIN, VINB1, VINB2, VINB3=12V, VIO=3.3V, VCORE=1.2V, AVDD=15.6V, HAVDD=7.8V, VGH=35V, VGL=-6.0V, HVLDO=15.2V, VCOM=6.1V, GAMMA=7.8V, 無負荷)

500nsec/Div

Figure 35. GPM Propagation Delay (rise)

Figure 36. GPM Propagation Delay (fall)

Figure 37. GPM Clamp Voltage (20V Clamp)

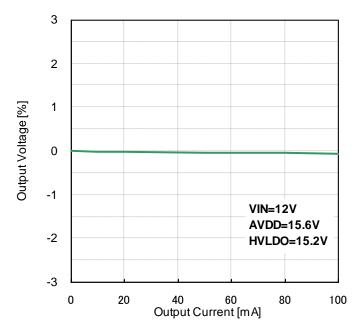

Figure 38. HVLDO Output Voltage vs Output Current

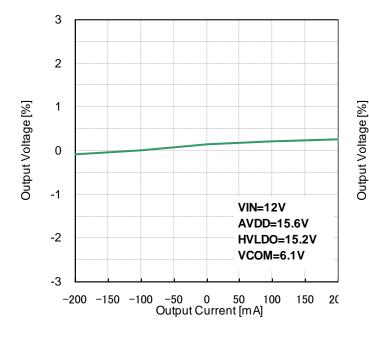

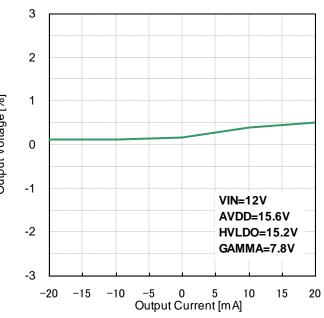

Figure 39. VCOM Output Voltage vs Output Current

Figure 40. GAMMA Output Voltage vs Output Current

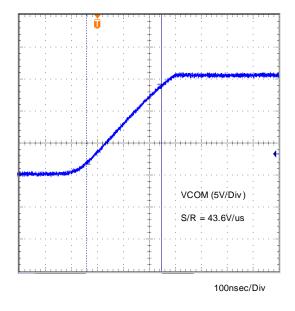

VCOM (5V/Div)

S/R = 43.3V/us

100nsec/Div

Figure 41. VCOM スルーレート (Rise)

Figure 42. VCOM スルーレート (Fall)

Figure 43. VCOM DNL vs BIT

Figure 44. VCOM INL vs BIT

Figure 45. GAMMA DNL vs BIT

Figure 46. GAMMA INL vs BIT

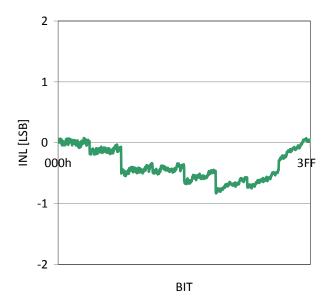

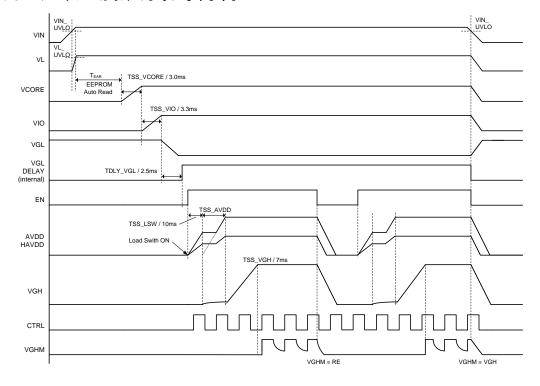

#### ●タイミングチャート

本 IC の ON / OFF シーケンスは以下のようになります。

Figure 47. Timing Chart

VIN の UVLO 解除により、VL が起動します。

VL 起動完了後、Auto Read 動作により EEPROM データを読み出します。(T<sub>EAR</sub>=2msec)

Auto Read 完了後、VCORE が起動します。VCORE の Soft Start 時間は 3.0msec となります。

VCORE の起動完了後、VIO が起動します。VIO の Soft Start 時間は 3.3V 設定時に 3.3msec となります。

VIO 起動完了後 PG=High となり、VGL が起動します。(SWB1 を使用した場合)。

VGL の SoftStart 時間は電圧設定や外付け容量により変わります。

VIO 起動完了し 2.5msec 経過後、EN=High とすると Load SW が ON(10msec)し、AVDD が起動します。

AVDD の SoftStart 時間はレジスタ設定にて変更可能です。(10msec or 20msec)

AVDD 起動完了後、VGH が起動します。VGH の SoftStart 時間は 35V 設定時に 7msec となります。

VGH 起動完了後、CTRL の立ち上がりもしくは立ち下りがトリガとなり、GPM 動作を開始します。

CTRL=Low により VGHM 電圧が下がります。

GPM クランプ電圧まで到達すると、VGHM 出力はハイインピーダンスとなります。

EN=Low により GPM, VGH, AVDD, HAVDD がシャットダウンします。この時、GPM 出力(VGHM)は RE と同電位になります。 VIN の UVLO を検出すると、全出力がシャットダウンします。この時、VGHM は VGH と同電位になります。

HVLDO, HAVDD は AVDD 電圧に追随して起動します。 VCOM, AMP1~4 は HVLDO 電圧に追随して起動しま す。

EN オフ時、AVDD, HAVDD の出力は HiZ 状態となります。HVLDO, VCOM, AMP1~4 の各出力は、AVDD が一定以下となるまで関係を保ってオフします。

Figure 48. Timing Chart 2

# ●アプリケーション例 (TOP VIEW)

Figure 49. Application Example

# ●アプリケーション回路部品リスト

| Parts name | Value      | Company | Parts Number       | Parts<br>name | Value      | Company     | Parts Number      |

|------------|------------|---------|--------------------|---------------|------------|-------------|-------------------|

| C3         | 4x 10 [uF] | MURATA  | GRM21BB31A106KE18  | C40           | 10 [uF]    | MURATA      | GRM31CB31E106KA75 |

| C8         | 1 [uF]     | MURATA  | GRM188B31E105KA75  | C41           | 2x 10 [uF] | MURATA      | GRM31CB31E106KA75 |

| C9         | 10 [uF]    | MURATA  | GRM31CB31E106KA75  | C51-54        | 0.1 [uF]   | MURATA      | GRM188B31H104KA92 |

| C10        | 10 [uF]    | MURATA  | GRM31CB31E106KA75  | R15           | 2.7 [kΩ]   | ROHM        | MCR03             |

| C11        | 10 [uF]    | MURATA  | GRM31CB31E106KA75  | R30           | 300 [Ω]    | ROHM        | MCR25             |

| C15        | 6.8 [nF]   | MURATA  | GRM188B11E682KA01  | R39_1         | 330 [Ω]    | ROHM        | MCR03             |

| C16        | 1 [uF]     | MURATA  | GRM188CB31E105KA75 | R39_2         | 120 [Ω]    | ROHM        | MCR03             |

| C19        | 2x 10 [uF] | MURATA  | GRM31CB31E106KA75  | RFN1          | 2.2 [Ω]    | ROHM        | MCR25             |

| C22        | 4x 10 [uF] | MURATA  | GRM31CB31E106KA75  | RFP1-2        | 2.2 [Ω]    | ROHM        | MCR25             |

| C25        | 4.7 [uF]   | MURATA  | GRM219B31C475KE15  | RQN           | 100 [kΩ]   | ROHM        | MCR03             |

| CFN1       | 0.1 [uF]   | MURATA  | GRM188B31H104KA92  | RQP           | 100 [kΩ]   | ROHM        | MCR03             |

| CFN2       | 470 [pF]   | MURATA  | GRM188B11H471KA01  | L19           | 6.8 [uH]   | TAIYO YUDEN | NS10165T6R8N      |

| CFP1       | 0.1 [uF]   | MURATA  | GRM188B31H104KA92  | L3            | 6.8 [uH]   | TAIYO YUDEN | NRS8040T6R8M      |

| CPF2       | 0.1 [uF]   | MURATA  | GRM188B31H104KA92  | L35           | 6.8 [uH]   | TAIYO YUDEN | NRS8040T6R8M      |

| CPF3       | 1 [uF]     | MURATA  | GRM21BB31H105KA12  | L39           | 6.8 [uH]   | TAIYO YUDEN | NRS8040T6R8M      |

| CFP4       | 2.2 [nF]   | MURATA  | GRM188B11H222KA01  | D45           | =          | ROHM        | RSX301L-30        |

| C28        | 10 [uF]    | MURATA  | GRM31CB31H106KA12  | DFN1          | -          | ROHM        | RB558W            |

| C31        | 10 [uF]    | MURATA  | GRM31CB31E106KA75  | DFP1          | -          | ROHM        | RB558W            |

| C35        | 2x 10 [uF] | MURATA  | GRM31CB31E106KA75  | DFP2          | -          | ROHM        | RB558W            |

| C39        | 4x 10 [uF] | MURATA  | GRM21BB31A106KE18  | QN            | PNP        | ROHM        | 2SCR513P          |

| C39_0      | 22 [nF]    | MURATA  | GRM188B31H104KA92  | QP            | NPN        | ROHM        | 2SAR513P          |

#### ●各ブロック保護機能説明

#### 1. BUCK CONVERTER BLOCK 1 (VIO)

#### 1-1. Over Voltage Protection (OVP)

VIO 電圧が上昇して IC 等が破壊するのを防ぐために OVP 機能を有しています。VDD1 端子に入力される電圧をモニタし、VDD1 端子電圧>110%(typ.)となると異常状態と判断し、OVP が機能します。OVP を検出するとスイッチングを停止、OVP 検出解除電圧(100%, typ.)まで VIO 電圧が降下後、スイッチングを再開します。

#### 1-2. Over Current Protection (OCP)

SWB1 のピーク電流が 3.5A(typ.)以上になった場合、Switching を制御し内蔵 Power MOS に流れる電流を制限します。

#### 1-3. Under Voltage Protection (UVP)

出力に対してタイマーラッチ式 UVP 機能を持っています。異常状態 (VIO<80%)を検出すると、SWB1 周波数が 1/4 に分周 されます。異常状態が 10msec(typ.)継続した場合、全出力がシャットダウン状態でラッチされます。ラッチ状態を解除し、再起動させるためには電源の再投入が必要です。

# 2. BUCK CONVERTER BLOCK 2 (VCORE)

#### 2-1. Over Voltage Protection (OVP)

VCORE 電圧が上昇して IC 等が破壊するのを防ぐために OVP 機能を有しています。VDD2 端子に入力される電圧をモニタし、VDD2 端子電圧>110%(typ.)となると異常状態と判断し、OVP が機能します。OVP を検出するとスイッチングを停止、OVP 検出解除電圧(100%, typ.)まで VCORE 電圧が降下後、スイッチングを再開します。

#### 2-2. Over Current Protection (OCP)

SWB2 のピーク電流が 3.0A(typ.)以上になった場合、Switching を制御し内蔵 Power MOS に流れる電流を制限します。

#### 2-3. Under Voltage Protection (UVP)

出力に対してタイマーラッチ式 UVP 機能を持っています。異常状態 (VCORE<80%)を検出すると、SWB2 周波数が 1/4 に 分周されます。異常状態が 10msec(typ.)継続した場合、全出力がシャットダウン状態でラッチされます。ラッチ状態を解除し、再起動させるためには電源の再投入が必要です。

#### 3. VGL REGULATOR BLOCK

# 3-1. Over Current Protection (OCP)

DRVN 電流が 5 mA(min.)以上になった場合、DRVN のソース電流(NPN Tr の Base 電流)を制限します。

# 3-2. Under Voltage Protection (UVP)

出力に対してタイマーラッチ式 UVP 機能を持っています。異常状態 (VGL>80%)が 10msec(typ.)継続した場合、全出力がシャットダウン状態でラッチされます。ラッチ状態を解除し、再起動させるためには電源の再投入が必要です。

# 4. BOOST CONVERTER BLOCK (AVDD)

# 4-1. Over Voltage Protection (OVP)

AVDD電圧が上昇して IC 等が破壊するのを防ぐために OVP 機能を有しています。SWO 端子に入力される電圧をモニタし、 SWO 端子電圧が 19.5V (typ.)となると異常状態と判断し、OVP が機能します。 OVP を検出するとスイッチングを停止し、 OVP 検出解除電圧 18V (typ.)まで AVDD 電圧が降下するとスイッチングを再開します。

# 4-2. Over Current Protection (OCP)

SW のピーク電流が 5.0A(typ.)以上になった場合、Switching を制御し内蔵 Power MOS に流れる電流を制限します。

# 4-3. Under Voltage Protection (UVP)

出力に対してタイマーラッチ式 UVP 機能を持っています。異常状態 (AVDD<80%)が 10msec(typ.)継続した場合、全出力が シャットダウン状態でラッチされます。ラッチ状態を解除し、再起動させるためには電源の再投入が必要です。

#### 4-4. Load Switch Over Current Protection (LSW\_OCP)

Load Switch のピーク電流が 7A(typ.)以上になった場合、Load Switch を制御し内蔵 Power MOS に流れる電流を制限します。

#### 5. BUCK CONVERTER BLOCK 3 (HAVDD)

# 5-1. Over Voltage Protection (OVP)

HAVDD 電圧が上昇して IC 等が破壊するのを防ぐために OVP 機能を有しています。VDD3 端子に入力される電圧をモニタし、VDD3 端子電圧>110%(typ.)となると異常状態と判断し、OVP が機能します。OVP を検出するとスイッチングを停止、OVP 検出解除電圧(100%, typ.)まで HAVDD 電圧が降下後、スイッチングを再開します。

# 5-2. Over Current Protection (OCP)

SWB3 のピーク電流が 1.5A(typ.)以上になった場合、Switching を制御し内蔵 Power MOS に流れる電流を制限します。

#### 5-3. Under Voltage Protection (UVP)

出力に対してタイマーラッチ式 UVP 機能を持っています。異常状態 (HAVDD<80%)を検出すると、SWB3 周波数が 1/4 に 分周されます。異常状態が 10msec(typ.)継続した場合、全出力がシャットダウン状態でラッチされます。ラッチ状態を解除し、再起動させるためには電源の再投入が必要です。

#### 6. HIGH VOLTAGE LDO BLOCK

#### 6-1. Over Current Protection (OCP)

HVLDO 電流が 100mA(typ.)以上になった場合、HVLDO のソース電流を制限します。

#### 6-2. Under Voltage Protection (UVP)

出力に対してタイマーラッチ式 UVP 機能を持っています。異常状態 (HVLDO<80%)が 10msec(typ.)継続した場合、全出力がシャットダウン状態でラッチされます。ラッチ状態を解除し、再起動させるためには電源の再投入が必要です。

#### 7. VGH REGULATOR BLOCK

#### 7-1. Over Voltage Protection (OVP)

VGH 電圧が上昇して IC 等が破壊するのを防ぐために OVP 機能を有しています。VGH 端子に入力される電圧をモニタし、VGH 端子電圧>45V(typ.)となると異常状態と判断し、OVP が機能します。OVP を検出すると DRVP 端子の電流を制限します。OVP 検出解除電圧(42V, typ.)まで VGH 電圧が降下後、DRVP 端子の電流制限を解除します。

# 7-2. Over Current Protection (OCP)

DRVP 電流が 5 mA(min.)以上になった場合、DRVP のシンク電流(PNP Tr の Base 電流)を制限します。

### 7-3. Under Voltage Protection (UVP)

出力に対してタイマーラッチ式 UVP 機能を持っています。異常状態 (VGH<80%)が 10msec(typ.)継続した場合、全出力が シャットダウン状態でラッチされます。ラッチ状態を解除し、再起動させるためには電源の再投入が必要です。

# 8. GENERAL

#### 8-1. Thermal shutdown

IC が 175℃(typ.)以上になると全出力がシャットダウンします。温度が 150℃(typ.)まで下がると動作は復帰します。

#### 8-2. VIN Under Voltage Lock Out

UVLO 電圧以下での回路誤動作を防止しています。 VIN 電圧が UVLO 電圧(7.55V / 8.3V)以下の条件では、スタンバイ状態となります。

# ●保護機能一覧

| BUCK CONVERTER 1 OVP VIO>110% Control switching pulse duty to not over current Frequency becomes 1/4 IC shutdown if UVP status maintains during 10r  BUCK CONVERTER 2 OVP VCORE>110% Stops switching.  OVP VCORE>110% Stops switching.  Frequency becomes 1/4 IC shutdown if UVP status maintains during 10r  Frequency becomes 1/4 IC shutdown if UVP status maintains during 10r  Frequency becomes 1/4 IC shutdown if UVP status maintains during 10r  VGL REGULATOR UVP VGL<80% IC shutdown if UVP status maintains during 10r  VGL Shutdown if UVP status maintains during 10r  VGL Shutdown if UVP status maintains during 10r | VIO>80%                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| CONVERTER 1  UVP  VIO<80%  Control switching pulse duty to not over current Frequency becomes 1/4  IC shutdown if UVP status maintains during 10r  Stops switching.  OVP  VCORE>110%  Stops switching.  Control switching pulse duty to not over current Frequency becomes 1/4  UVP  VCORE<80%  IC shutdown if UVP status maintains during 10r  Frequency becomes 1/4  IC shutdown if UVP status maintains during 10r  VGL  REGULATOR  UVP  VGL<80%  IC shutdown if UVP status maintains during 10r                                                                                                                                  | VIO>80%                     |

| BUCK CONVERTER 2  OVP VCORE>110%  Control switching pulse duty to not over current Prequency becomes 1/4  IC shutdown if UVP status maintains during 10r  Stops switching.  Control switching pulse duty to not over current Prequency becomes 1/4  IC shutdown if UVP status maintains during 10r  VGL REGULATOR  VIO<80%  IC shutdown if UVP status maintains during 10r  VGL Shutdown if UVP status maintains during 10r  VGL Shutdown if UVP status maintains during 10r                                                                                                                                                         |                             |

| OVP VCORE>110% Stops switching.  BUCK CONVERTER 2  UVP VCORE<80%  OCP I_SWB2>3.0A Control switching pulse duty to not over current Frequency becomes 1/4 IC shutdown if UVP status maintains during 10r  VGL REGULATOR  UVP VGL<80%  IC shutdown if UVP status maintains during 10r                                                                                                                                                                                                                                                                                                                                                  | msec. IC restart            |

| BUCK CONVERTER 2 UVP VCORE<80%  Control switching pulse duty to not over current Frequency becomes 1/4 IC shutdown if UVP status maintains during 10r  VGL REGULATOR  UVP VGL<80%  IC shutdown if UVP status maintains during 10r                                                                                                                                                                                                                                                                                                                                                                                                    | 1                           |

| CONVERTER 2  UVP  VCORE<80%  UVP  VCORE<80%  I_SWB2>3.0A  Control switching pulse duty to not over current Frequency becomes 1/4  IC shutdown if UVP status maintains during 10r  VGL  REGULATOR  UVP  VGL<80%  IC shutdown if UVP status maintains during 10r                                                                                                                                                                                                                                                                                                                                                                       | VCORE<100%                  |

| VGL REGULATOR UVP VCORE<80% Frequency becomes 1/4  IC shutdown if UVP status maintains during 10r  VGL REGULATOR UVP VGL<80% IC shutdown if UVP status maintains during 10r                                                                                                                                                                                                                                                                                                                                                                                                                                                          | nt limit. I_SWB2<3.0A       |

| VGL REGULATOR UVP VGL<80% IC shutdown if UVP status maintains during 10r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VCORE>80%                   |

| REGULATOR UVP VGL<80% IC shutdown if UVP status maintains during 10r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | msec. IC restart            |

| OVP VGL<80% IC shutdown if OVP status maintains during for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | I_DRVN<5mA                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | IC restart                  |

| OVP AVDD>19.5V Stops switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | AVDD<18V                    |

| BOOST CONVERTER OCP I_SW>5A Control switching pulse duty to not over current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nt limit. I_SW<5A           |

| UVP AVDD<80% IC shutdown if UVP status maintains during 10r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | msec. IC restart            |

| LOAD SW OCP I_SWO>7.0A Off the Load Switch.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | IC restart                  |

| OVP HAVDD>110% Stops switching.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | HAVDD<100%                  |

| BUCK CONVERTER OCP I_SWB3>1.5A Control switching pulse duty to not over current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | nt limit. I_SWB3<1.5A       |

| Frequency becomes 1/4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | HAVDD>80%                   |

| UVP HAVDD<80% IC shutdown if UVP status maintains during 10r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | msec. IC restart            |

| HIGH OCP I_HVLDO>100mA Limit HVLDO current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I_HVLDO<100mA               |

| VOLTAGE LDO UVP HVLDO<80% IC shutdown if UVP status maintains during 10r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | IC restart                  |

| OVP VGH>45V DRVP current limit to 0mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VGH<42V                     |

| VGH REGULATOR OCP I_DRVP>5 mA Limit DRVP current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | I_DRVP<5mA                  |

| UVP VGH<80% IC shutdown if UVP status maintains during 10r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                             |

| TSD Tj>175°C IC shutdown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | IC restart                  |

| GENERAL UVLO VIN<7.55V IC shutdown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Omsec. IC restart  Tj<150°C |

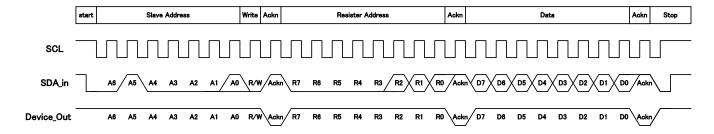

#### ●シリアル通信について

ホストとのコマンド・インターフェースに  $I^2C$  バス制御を用います。スレーブアドレスの他に 1 バイトのレジスタ・アドレスを指定して書き込みや読み出しを行います。 $I^2C$  バス スレーブモードのフォーマットを以下に示します。

| Write operation | Ctort |   | Slave Address |       |      |      |   |    | R/W | Α | Register Address               | Α | DATA      | Α | Stop |

|-----------------|-------|---|---------------|-------|------|------|---|----|-----|---|--------------------------------|---|-----------|---|------|

| write operation | Start | 0 | 1             | 0     | 0    | 0    | 0 | Α0 | 0   | 0 | Select Register Address (8bit) | 0 | 8bit DATA | 0 | Stop |

| Dood operation  | Ctort |   | ;             | Slave | e Ad | dres | s |    | R/W | Α | Register Address               | Α | DATA      | Α | Cton |

| Read operation  | Start | 0 | 1             | 0     | 0    | 0    | 0 | A0 | 1   | 0 | Select Register Address (8bit) | 0 | 8bit DATA | 0 | Stop |

Start : スタート・コンディション

Slave Address : 7bit のスレーブアドレスを送ります。(MSB ファースト)

A0 はスレーブアドレス選択端子により(1/0)選択が可能です。

A : アクノリッジ

送受信されているデータにはバイトごとにアクノリッジ・ビットが付け加わる。

データの送受信が正しく行われているときは"L"が送受信されます。

"H"の場合は、アクノリッジが無かったことになります。

Register Address : 8bit のレジスタ・アドレスを用います。

DATA : データ・バイト。送受信するデータ(MSB ファースト)

Stop : ストップ・コンディション

I2C BUS からレジスタへの書き込みモードとして、①シングルモード、②マルチモードがあります。 シングルモードでは指定された1つのレジスタにデータを書き込みます。 マルチモードでは2Byte 目で指定されたレジスタをスタートアドレスとして、複数のデータを入力することにより、連続してデータの書き込みを行なうことができます。 シングルモード・マルチモードの設定は STOP ビットの有無により設定できます。

① シングルモードタイミングチャート

② マルチモードタイミングチャート

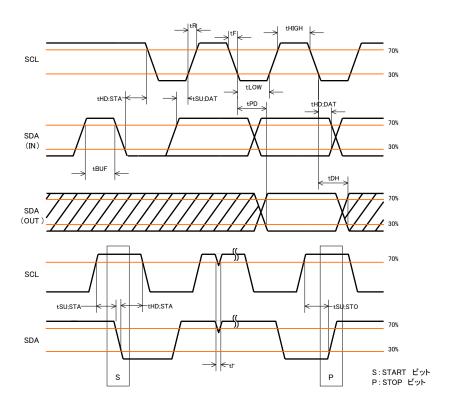

# ●I2C タイミング規定

Figure 50. I2C Timing

# タイミング規定

| パラメータ          | 記号       | N   | ORMAL <del>T</del> — | ・ド  |     | FAST <del>E</del> -F | ×.  | 単位  |

|----------------|----------|-----|----------------------|-----|-----|----------------------|-----|-----|

| 7793-9         | 記写       | MIN | TYP                  | MAX | MIN | TYP                  | MAX | 甲亚  |

| SCL 周波数        | f SCL    | -   | -                    | 100 | -   | -                    | 400 | kHz |

| SCL"H"時間       | tHIGH    | 4.0 | -                    | -   | 0.6 | -                    | -   | us  |

| SCL"L"時間       | tLOW     | 4.7 | -                    | -   | 1.2 | -                    | -   | us  |

| 立ち上がり時間        | tR       | -   | -                    | 1.0 | -   | -                    | 0.3 | us  |

| 立ち下り時間         | tF       | -   | -                    | 0.3 | -   | -                    | 0.3 | us  |

| スタート条件ホールド時間   | tHD; STA | 4.0 | -                    | -   | 0.6 | -                    | -   | us  |

| スタート条件セットアップ時間 | tSU; STA | 4.7 | -                    | -   | 0.6 | -                    | -   | us  |

| SDA ホールド時間     | tHD; DAT | 200 | -                    | -   | 100 | -                    | -   | ns  |

| SDA セットアップ時間   | tSU; DAT | 200 | -                    | -   | 100 | -                    | -   | ns  |

| アクノレッジ遅延時間     | tPD      | -   | -                    | 0.9 | -   | -                    | 0.9 | us  |

| アクノレッジホールド時間   | tDH      | -   | 0.1                  | -   | -   | 0.1                  | -   | us  |

| ストップ条件セットアップ時間 | tSU; STO | 4.7 | -                    | -   | 0.6 | -                    | -   | us  |

| バス開放時間         | tBUF     | 4.7 | -                    | -   | 1.2 | -                    | -   | us  |

| ノイズスパイク幅       | TI       | -   | 0.1                  | -   | -   | 0.1                  | -   | us  |

# ●コマンド・インターフェースについて

データ送受信するための通信フォーマットは以下の通りです。

#### **I2C** Write format

| Stort |   | ; | Slave | e Ad | dres | s |    | R/W | Α | Register Address | Α | DATA         | Α | Stop |

|-------|---|---|-------|------|------|---|----|-----|---|------------------|---|--------------|---|------|

| Start | 0 | 1 | 0     | 0    | 0    | 0 | A0 | 0   | 0 | 00h to 0Fh       | 0 | N-bytes DATA | 0 | Згор |

3byte 目以降は DATA を続けて入力することで続きの Register に入力可能です。 10h 以降の DATA は無効となります。

入力された Data は ACK が出力されたタイミングで Register に反映されます。

#### I2C Read format

#### Read data from DAC Register

| Start    |   | ; | Slave | e Ad | dres | s |    | R/W | Α | Register Address | Α |      |

|----------|---|---|-------|------|------|---|----|-----|---|------------------|---|------|

| Start    | 0 | 1 | 0     | 0    | 0    | 0 | Α0 | 0   | 0 | 00h to 0Fh       | 0 |      |

| Repeated |   | ; | Slave | e Ad | dres | S |    | R/W | Α | DATA             | Α | Stop |

| Start    | 0 | 1 | 0     | 0    | 0    | 0 | A0 | 1   | 0 | N-bytes DATA     | 0 | Stop |

# ●EEPROM の書き込み条件について

Register のデータを EEPROM に書き込むための通信フォーマットは以下の通りです。下記のコマンドにより、各 Register に格納されている DATA が EEPROM に書き込まれます。

#### **EEPROM Write format**

| I | Start |   | ; | Slave | e Ad | dres | s |    | R/W | Α |   |   | Reg | ister | Add | lress |   |   | Α |   |   |   | DA | ΛTΑ |   |   |   | Α | Cton |

|---|-------|---|---|-------|------|------|---|----|-----|---|---|---|-----|-------|-----|-------|---|---|---|---|---|---|----|-----|---|---|---|---|------|

|   | Start | 0 | 1 | 0     | 0    | 0    | 0 | Α0 | 0   | 0 | 1 | 1 | 1   | 1     | 1   | 1     | 1 | 1 | 0 | 1 | Χ | Χ | Х  | Χ   | Х | Х | Х | 0 | Stop |

D6 ~ D0 は Don't care

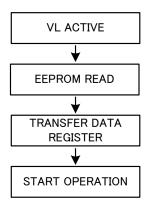

# ●起動時の Automatic EEPROM Read 機能について

VIN 電圧起動時にリセット信号を発生させ、各レジスタの初期化を行います。

その後、VL 起動完了によりスタンバイ状態が解除されると EEPROM に書き込まれている DATA をレジスタに読み込ます。 従って、PMIC は EEPROM の設定で起動します。

以下に Automatic EEPROM READ シーケンスを示します。

Figure 51. Automatic EEPROM Read Function at Start-up

# ●EEPROM 設定項目

| Register<br>Address | Bits | Function                          | Default(*1)        | Resolution                                   |

|---------------------|------|-----------------------------------|--------------------|----------------------------------------------|

| 00h                 | 6    | Channel Disable Register          | 00h                | -                                            |

| 01h                 | 6    | AVDD output voltage setting[5:0]  | 15.6V [27h]        | 0.1V [11.7V to 18.0V]                        |

| 02h                 | 3    | AVDD OCP offset setting[2:0]      | 1.6A [04h]         | 0.4A [0A to 2.8A]                            |

| 03h                 | 1    | AVDD soft start time setting[0]   | 10msec [00h]       | 10msec [10msec or 20msec]                    |

| 04h                 | 4    | VIO output voltage setting[3:0]   | 3.3V [0Bh]         | 0.1V [2.2V to 3.7V]                          |

| 05h                 | 6    | HAVDD output voltage setting[5:0] | 7.8V [1Eh]         | 0.1V [4.8V to 11.1V]                         |

| 06h                 | 5    | VGH output voltage setting[4:0]   | 35V [14h]          | 0.5V [25V to 40.5V]                          |

| 07h                 | 2    | GPM clamp voltage setting[1:0]    | 20V [01h]          | 5V [15V to 30V]                              |

| 08h                 | 5    | VGL output voltage setting[4:0]   | -6.0V [0Ah]        | 0.2V [-10.2V to -4.0V]                       |

| 09h                 | 6    | HVLDO output voltage setting[5:0] | 15.2V [23h]        | 0.1V [11.7V to 18.0V]                        |

| 0Ah                 | 8    | VCOM output voltage setting[7:0]  | 6.103V[C5h]        | HVLDOx0.18/256<br>[HVLDOx0.36 to HVLDOx0.54] |

| 0Bh[7:6], 0Ch       | 10   | AMP1 output voltage setting[9:0]  | 7.808V[1F2h]       | HVLDO/1024[0V to HVLDO]                      |

| 0Bh[5:4], 0Dh       | 10   | AMP2 output voltage setting[9:0]  | 7.808V[1F2h]       | HVLDO/1024[0V to HVLDO]                      |

| 0Bh[3:2], 0Eh       | 10   | AMP3 output voltage setting[9:0]  | 7.808V[1F2h]       | HVLDO/1024[0V to HVLDO]                      |

| 0Bh[1:0], 0Fh       | 10   | AMP4 output voltage setting[9:0]  | 7.808V[1F2h]       | HVLDO/1024[0V to HVLDO]                      |

| FFh                 | 8    | Con                               | trol Register[7:0] |                                              |

# ● Channel Disable Register

|     |     |       | Register Ad | dress = 00h |     |     |          |

|-----|-----|-------|-------------|-------------|-----|-----|----------|

| [7] | [6] | [5]   | [4]         | [3]         | [2] | [1] | [0]      |

| -   | -   | VCORE | HAVDD       | VGH         | VGL | GPM | AVDD_EXT |

0 : Enable 1 : Disable

AVDD\_EXT 1: AVDD 外付けモード

# **●**Control Register

| Register<br>Address | DATA<br>[BIN] | Function                                |

|---------------------|---------------|-----------------------------------------|

| FFh                 | 1xxx_xxxx     | Write to EEPROM from DAC Register data. |

x : Don't care bit

# ● Register Map

| Resister<br>Address | D7  | D6     | D5    | D4        | D3         | D2        | D1           | D0        | Default |

|---------------------|-----|--------|-------|-----------|------------|-----------|--------------|-----------|---------|

| 00h                 | _   | _      | VCORE | HAVDD     | VGH        | VGL       | GPM          | AVDD_EXT  | 00h     |

| 01h                 | _   | _      |       |           | AVD        | D[5:0]    |              |           | 27h     |

| 02h                 | _   | _      | _     | _         | _          | AVI       | DD OCP offse | t[2:0]    | 04h     |

| 03h                 | _   | _      | _     | _         | _          | _         |              | AVDD SS   | 00h     |

| 04h                 | _   | _      | _     | _         |            | VIC       | [3:0]        |           | 0Bh     |

| 05h                 | _   | _      |       |           | HAVE       | DD [5:0]  |              |           | 1Eh     |

| 06h                 | _   | _      | _     |           |            | VGH [4:0] |              |           | 14h     |

| 07h                 | _   | _      | _     | _         | _          | _         | GPM cl       | amp [1:0] | 01h     |

| 08h                 | _   | _      | _     |           |            | VGL [4:0] |              |           | 0Ah     |

| 09h                 |     | _      |       |           | HVL        | OO[5:0]   |              |           | 23h     |

| 0Ah                 |     |        |       | VCO       | M [7:0]    |           |              |           | C5h     |

| 0Bh                 | AMP | 1[9:8] | AMP:  | 2[9:8]    | AMP:       | 3[9:8]    | AMF          | 94[9:8]   | 55h     |

| 0Ch                 |     |        |       | AMF       | P1[7:0]    |           |              |           | F2h     |

| 0Dh                 |     |        |       | AMF       | P2[7:0]    |           |              |           | F2h     |

| 0Eh                 |     |        |       | AMF       | P3[7:0]    |           |              |           | F2h     |

| 0Fh                 |     |        |       | AMF       | P4[7:0]    |           |              |           | F2h     |

| FFh                 |     |        |       | ( Control | Register ) |           |              |           | _       |

出荷時の EEPROM DATA となります。 Default 電圧設定時の値です。各出力の Soft start 時間は設定電圧によって変化します。

# ●Command Table 1

| е _ | 1        |              |             |              |            |              |              |       |               |              |

|-----|----------|--------------|-------------|--------------|------------|--------------|--------------|-------|---------------|--------------|

|     |          |              |             |              |            | ister Add    |              |       |               |              |

|     |          | 01           | 02          | 03           | 04         | 05           | 06           | 07    | 08            | 09           |

| ŀ   |          | [5:0]        | [2:0]       | [0]          | [3:0]      | [5:0]        | [4:0]        | [1:0] | [4:0]         | [5:0]        |

|     | DATA     | AVDD         | AVDD<br>OCP | AVDD<br>soft | VIO        | HAVDD        | VGH          | GPM   | VGL           | HVLDO        |

|     | (HEX)    | [V]          | offset      | start        | [V]        | [V]          | [V]          | clamp | [V]           | [V]          |

|     | (IILX)   | [*]          | [A]         | [msec]       | [4]        | [*]          | [4]          | [V]   | [*]           | [ [,         |

| ŀ   | 00       | 11.7         | 0.0         | 10           | 2.2        | 4.8          | 25.0         | 15    | -4.0          | 11.7         |

| ı   | 01       | 11.8         | 0.4         | 20           | 2.3        | 4.9          | 25.5         | 20    | -4.2          | 11.8         |

| ı   | 02       | 11.9         | 0.8         |              | 2.4        | 5.0          | 26.0         | 25    | -4.4          | 11.9         |

|     | 03       | 12.0         | 1.2         |              | 2.5        | 5.1          | 26.5         | 30    | -4.6          | 12.0         |

| ļ   | 04       | 12.1         | 1.6         |              | 2.6        | 5.2          | 27.0         |       | -4.8          | 12.1         |

| ļ   | 05       | 12.2         | 2.0         |              | 2.7        | 5.3          | 27.5         |       | -5.0          | 12.2         |

| ŀ   | 06       | 12.3         | 2.4         | ļ            | 2.8        | 5.4          | 28.0         |       | -5.2          | 12.3         |

| ŀ   | 07       | 12.4<br>12.5 | 2.8         | 1            | 2.9        | 5.5          | 28.5         |       | -5.4          | 12.4<br>12.5 |

| ŀ   | 08<br>09 | 12.5         |             |              | 3.0<br>3.1 | 5.6<br>5.7   | 29.0<br>29.5 |       | -5.6<br>-5.8  | 12.5         |

| ŀ   | 03<br>0A | 12.7         |             |              | 3.2        | 5.8          | 30.0         |       | -6.0          | 12.7         |

| ŀ   | 0B       | 12.8         |             |              | 3.3        | 5.9          | 30.5         |       | -6.2          | 12.8         |

| ı   | 0C       | 12.9         |             |              | 3.4        | 6.0          | 31.0         |       | -6.4          | 12.9         |

| Ī   | 0D       | 13.0         |             |              | 3.5        | 6.1          | 31.5         |       | -6.6          | 13.0         |

|     | 0E       | 13.1         |             |              | 3.6        | 6.2          | 32.0         |       | -6.8          | 13.1         |

| ſ   | 0F       | 13.2         |             |              | 3.7        | 6.3          | 32.5         |       | -7.0          | 13.2         |

| ļ   | 10       | 13.3         |             |              |            | 6.4          | 33.0         |       | -7.2          | 13.3         |

| ŀ   | 11       | 13.4         |             |              |            | 6.5          | 33.5         |       | -7.4          | 13.4         |

| ŀ   | 12<br>13 | 13.5<br>13.6 |             |              |            | 6.6<br>6.7   | 34.0         |       | -7.6<br>-7.8  | 13.5<br>13.6 |

| ŀ   | 14       | 13.7         |             |              |            | 6.8          | 34.5<br>35.0 |       | -7.8          | 13.7         |

| ŀ   | 15       | 13.8         |             |              |            | 6.9          | 35.5         |       | -8.2          | 13.8         |

| ŀ   | 16       | 13.9         |             |              |            | 7.0          | 36.0         |       | -8.4          | 13.9         |

| ı   | 17       | 14.0         |             |              |            | 7.1          | 36.5         |       | -8.6          | 14.0         |

| ı   | 18       | 14.1         |             |              |            | 7.2          | 37.0         |       | -8.8          | 14.1         |

|     | 19       | 14.2         |             |              |            | 7.3          | 37.5         |       | -9.0          | 14.2         |

| ļ   | 1A       | 14.3         |             |              |            | 7.4          | 38.0         |       | -9.2          | 14.3         |

| ŀ   | 1B       | 14.4         |             |              |            | 7.5          | 38.5         |       | -9.4          | 14.4         |

| ŀ   | 1C       | 14.5         |             |              |            | 7.6          | 39.0         |       | -9.6          | 14.5         |

| ŀ   | 1D<br>1E | 14.6<br>14.7 |             |              |            | 7.7<br>7.8   | 39.5<br>40.0 |       | -9.8<br>-10.0 | 14.6<br>14.7 |

| ŀ   | 1F       | 14.8         |             |              |            | 7.9          | 40.5         |       | -10.2         | 14.8         |

| ŀ   | 20       | 14.9         |             |              |            | 8.0          | 40.0         |       | 10.2          | 14.9         |

| ı   | 21       | 15.0         |             |              |            | 8.1          |              |       |               | 15.0         |

|     | 22       | 15.1         |             |              |            | 8.2          |              |       |               | 15.1         |

|     | 23       | 15.2         |             |              |            | 8.3          |              |       |               | 15.2         |

| ļ   | 24       | 15.3         | ,           |              |            | 8.4          |              |       |               | 15.3         |

| ŀ   | 25       | 15.4         |             |              |            | 8.5          |              |       |               | 15.4         |

| ŀ   | 26       | 15.5         |             |              |            | 8.6          |              |       |               | 15.5         |

| ŀ   | 27<br>28 | 15.6<br>15.7 |             |              |            | 8.7<br>8.8   |              |       |               | 15.6<br>15.7 |

| ŀ   | 29       | 15.7         |             |              |            | 8.9          |              |       |               | 15.8         |

| ŀ   | 2A       | 15.9         |             |              |            | 9.0          |              |       |               | 15.9         |

| ţ   | 2B       | 16.0         |             |              |            | 9.1          |              |       |               | 16.0         |

| ţ   | 2C       | 16.1         |             |              |            | 9.2          |              |       |               | 16.1         |

| Į   | 2D       | 16.2         |             |              |            | 9.3          |              |       |               | 16.2         |

| ļ   | 2E       | 16.3         |             |              |            | 9.4          |              |       |               | 16.3         |

| ļ   | 2F       | 16.4         |             |              |            | 9.5          |              |       |               | 16.4         |

| ŀ   | 30       | 16.5         |             |              |            | 9.6          |              |       |               | 16.5         |

| ŀ   | 31<br>32 | 16.6<br>16.7 |             |              |            | 9.7<br>9.8   |              |       |               | 16.6<br>16.7 |

| ŀ   | 33       | 16.7         |             |              |            | 9.8          |              |       |               | 16.7         |

| ŀ   | 34       | 16.9         |             |              |            | 10.0         |              |       |               | 16.9         |

| ı   | 35       | 17.0         |             |              |            | 10.1         |              |       |               | 17.0         |

| ľ   | 36       | 17.1         |             |              |            | 10.2         |              |       |               | 17.1         |

| ľ   | 37       | 17.2         |             |              |            | 10.3         |              |       |               | 17.2         |

| ſ   | 38       | 17.3         |             |              |            | 10.4         |              |       |               | 17.3         |

| ļ   | 39       | 17.4         |             |              |            | 10.5         |              |       |               | 17.4         |

| ļ   | 3A       | 17.5         |             |              |            | 10.6         |              |       |               | 17.5         |

| ŀ   | 3B       | 17.6         |             |              |            | 10.7         |              |       |               | 17.6         |

| ŀ   | 3C<br>3D | 17.7<br>17.8 |             |              |            | 10.8<br>10.9 |              |       |               | 17.7<br>17.8 |

| ŀ   | 3E       | 17.8         |             |              |            | 11.0         |              |       |               | 17.8         |

| ŀ   | 3F       | 18.0         |             |              |            | 11.1         |              |       |               | 18.0         |

| L   |          |              |             | ı            |            |              |              |       | · Default     |              |

: Default Value

# ●Command Table 2

|       | Register Address         |

|-------|--------------------------|

|       | 0A                       |

|       | [7:0]                    |

|       |                          |

| DATA  | VCOM                     |

| (HEX) | [V]                      |

| ` '   | I                        |

| 00    | HVLDOx0.18x(3 - 0/256)   |

| 01    | HVLDOx0.18x(3 - 1/256)   |

| 02    | HVLDOx0.18x(3 - 2/256)   |

| _     | _                        |

| :     | :                        |

|       |                          |

| FD    | HVLDOx0.18x(3 - 253/256) |

| FE    | HVLDOx0.18x(3 - 254/256) |

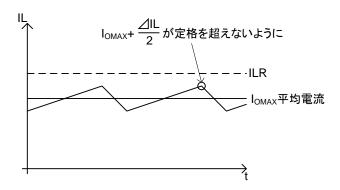

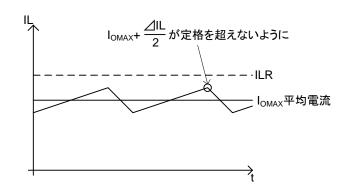

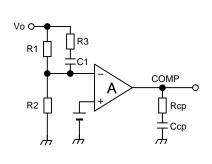

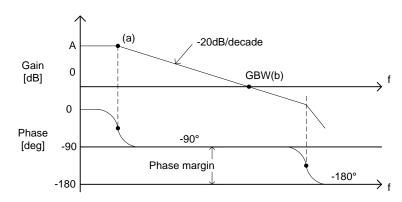

| FF    | HVLDOx0.18x(3 - 255/256) |