# 4線式抵抗膜方式 タッチパネルコントローラ

# **BU21021GUL**

#### ●概要

BU21021GUL は 12bit 逐次型 ADC を内蔵し、4 線式抵抗膜 方式タッチパネルに対応した最大 2 点検出可能なコントローラです。1 点検出では X/Y 座標の位置検出とタッチ圧検出、2 点検出では個々の X/Y 座標の位置検出が可能です。

1点/2点座標の移動からジェスチャ検出を行い、個別に検出フラグ出力が可能です。CPUを内蔵しフィルタリング等の処理、検出座標の自動生成、ジェスチャ検出をコントローラ内部で行います。

# ●特長

- 4線式抵抗膜方式タッチパネル対応

- マルチタッチ(2点)検出対応

- タッチ座標自動生成

- ジェスチャ検出

- 3V 単一電源

- 逐次比較型 12 ビット A/D コンバータ内蔵

- クロック発振回路内蔵

- ホストインターフェース (IFSEL pinにて選択)4線 SPI / 2線シリアルバス

#### ●重要特件

■ 電源電圧範囲

型 動作温度範囲

型 静止電流

型 待機電流

2. 7[V] ~3. 6[V]

-20[°C] ~85[°C]

5. 0[uA] (Max.)

60[uA] (Typ.)

■ 動作電流 4.0[mA] (Typ.)

■ 座標分解能 12bit

●パッケージ VCSP50L2

2. 70 mm x 2. 65 mm x 0. 55 (max) mm

#### ●用途

- 4線式抵抗膜方式タッチスクリーンによる ユーザーインターフェースを内蔵する機器

- 携帯電話機、携帯情報端末(PDA)などの携帯通信機器

- デジタルカメラ (DSC)、デジタルビデオ (DVC)、 携帯テレビなどの映像機器

- ノート PC、タッチスクリーンモニタ、プリンタなどの PC/PC 周辺機器

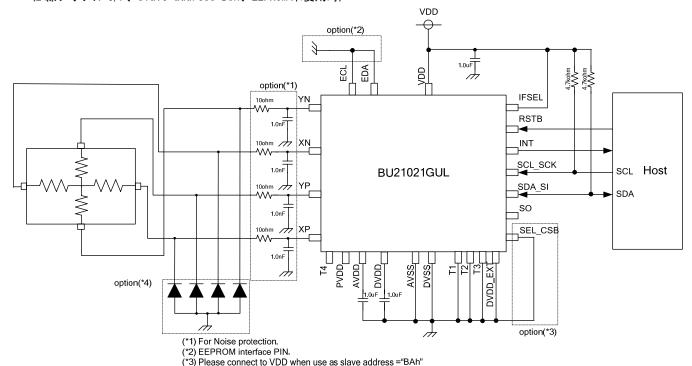

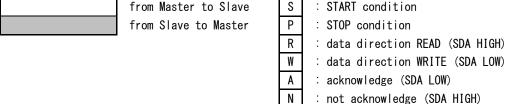

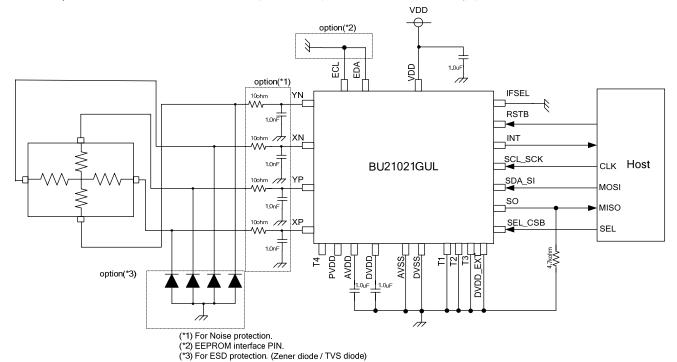

# ●基本アプリケーション回路

(2線シリアル I/F、Slave address=B8h、EEPROM 未使用時)

(\*4) For ESD protection.(Zener diode/TVS diode) Figure 1. アプリケーション回路例

#### ●端子配置図

|   | 1   | 2       | 3       | 4      | 5        |

|---|-----|---------|---------|--------|----------|

| A | T4  | PVDD    | DVDD    | VDD    | DVSS     |

| В | XP  |         | AVDD    | AVSS   | DVDD_EXT |

| С | XN  | YP      | RSTB    | T1     | T2       |

| D | YN  | SEL_CSB | S0      | Т3     | IFSEL    |

| E | ECL | EDA     | SCL_SCK | SDA_SI | INT      |

Top view

Figure 2. 端子配置図

# ●端子説明

| 番号         | 端子名      | I/0 |                           | 説明                          |        |            |   |  |  |

|------------|----------|-----|---------------------------|-----------------------------|--------|------------|---|--|--|

| D1         | YN       | 1/0 | パネルインターフ                  | パネルインターフェース                 |        |            |   |  |  |

| C1         | XN       | 1/0 | パネルインターフ                  | パネルインターフェース                 |        |            |   |  |  |

| C2         | YP       | 1/0 | パネルインターフ                  | ェース                         |        |            | D |  |  |

| B1         | XP       | 1/0 | パネルインターフ                  | ェース                         |        |            | D |  |  |

| <b>A</b> 1 | T4       | 1/0 | テスト端子 4                   |                             |        |            | D |  |  |

| A2         | PVDD     | 0   | パネル用レギュレ                  | ータ出力                        |        |            | D |  |  |

| В3         | AVDD     | 0   | アナログ用レギュ                  | レータ出力                       |        |            | D |  |  |

| <b>A</b> 3 | DVDD     | 1/0 | デジタル用レギュ                  | レータ出力 / 外部印加設定時             | デジタル電源 | <b>原入力</b> | D |  |  |

| B4         | AVSS     | -   | アナロググランド                  |                             |        |            | - |  |  |

| A4         | VDD      | -   | チップ電源                     | チップ電源                       |        |            |   |  |  |

| <b>A</b> 5 | DVSS     | -   | デジタルグランド                  | デジタルグランド                    |        |            |   |  |  |

| B5         | DVDD_EXT | I   | DVDD 外部印加設定               | DVDD 外部印加設定 (L=内部生成、H=外部印加) |        |            |   |  |  |

| C3         | RSTB     | I   | H/W リセット                  | d/W リセット                    |        |            |   |  |  |

| C4         | T1       | I   | テスト端子1                    |                             |        |            | Α |  |  |

| C5         | T2       | I   | テスト端子 2                   |                             |        |            | Α |  |  |

| D4         | Т3       | I   | テスト端子3                    |                             |        |            | Α |  |  |

| D5         | IFSEL    | I   | ホストインターフ                  | ェース選択 (L=4 線 SPI,H=2        | 線シリアル  | )          | Α |  |  |

| D3         | S0       | 0   | 2線シリアル                    | 未使用(HiZ)                    | 4線SPI  | データ出力      | E |  |  |

| E5         | INT      | 0   | 割り込み出力                    | 割り込み出力                      |        |            |   |  |  |

| D2         | SEL_CSB  | I   | 2線シリアル                    | С                           |        |            |   |  |  |

| E4         | SDA_SI   | I/0 | 2線シリアル                    | В                           |        |            |   |  |  |

| E3         | SCL_SCK  | I   | 2 線シリアル クロック 4 線 SPI クロック |                             |        |            |   |  |  |

| E2         | EDA      | I/0 | EEPROM 用 SDA              |                             |        |            |   |  |  |

| E1         | ECL      | 1/0 | EEPROM 用 SCL              |                             |        |            | В |  |  |

- (\*1) AVDD, DVDD 端子は 1[uF] (\*5) にて GND に接続、PVDD, T4 端子はオープンにて使用してください。

- (\*1) AVDD, DVDD 端子は「[ur] (\*3) に C GND に KgM, FVDD, 14 編子はカーノンに C RC 用して、たさい。

(\*2) DVDD\_EXT 端子 "H" レベル固定にて、デジタル CORE 電源を DVDD 端子より供給可能です。

(\*3) EEPROM 使用時には ECL、EDA を 4.7 [ kΩ] (\*5) にてプルアップしてください。未使用時には直接 GND に接続してください。

(\*4) 2 線シリアル I/F 使用時は SCL\_SCK、SDA\_SI を 4.7 [ kΩ] (\*5) にてプルアップ、SO 端子はオープンにて使用してください。

- (\*5) 各定数は推奨値であり、保証値ではありません。

- (\*6) VDD (チップ電源) 未印加時に RSTB を"H"にすることを禁止致します。

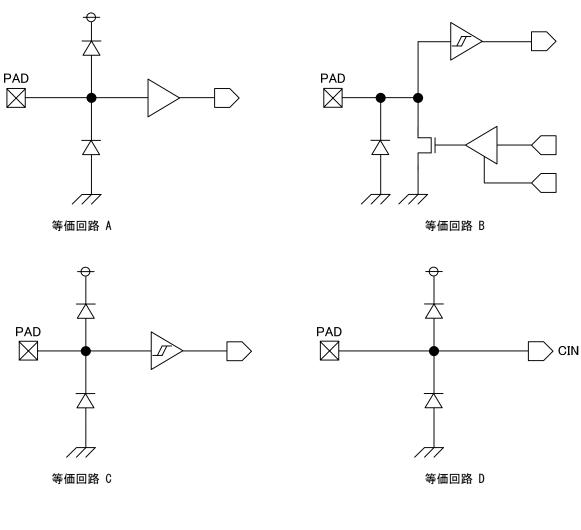

# ●端子等価回路図

Figure 3. 端子等価回路図

#### ● OVERVIEW

BU21021GUL は 4 線式抵抗膜方式タッチパネルに対応したタッチコントローラです。

32bit-CPU、逐次比較型 12bitA/D コンバータ、クロック発振回路、内部用 LDO を内蔵し 2.7V~3.6V 単一電源で動作します。 既存の 4 線式タッチスクリーンコントローラ同様に 1 点検出、タッチ圧検出に加え、

予め設定されたパネルパラメータを基に2点検出、座標移動から自動でジェスチャ検出行います。

検出されたジェスチャは個別に検出フラグとして出力されます。

BU21021GUL は内蔵 CPU 起動後に定期的にパネル状態をセンシングし、その結果に座標演算、フィルタ処理を行い 1 点または 2 点のタッチ座標とジェスチャ検出フラグとしてレジスタに保存します。 レジスタの更新時に INT 端子により HOST ヘデータ更新を通知することで HOST マイコンの制御、演算負荷を大幅に低減します。

#### ■ 1点検出

内蔵の逐次比較型 12bitA/D コンバータにより既存の 4 線式タッチスクリーンコントローラ同様に X 軸、Y 軸の位置検出とタッチ圧検出をコントローラ内部で演算し出力可能です。 また 2 点検出機能が内蔵されているため既存の 4 線式タッチスクリーンコントローラで解決できない 2 点タッチ時に重心点が 1 点タッチとして入力されてしまう誤入力となっていた問題を解決します。

#### ■ 2点検出

従来の4線式抵抗膜方式コントローラによる1点検出と異なり、2点検出は2点タッチ時のパネル状態と各軸座標系との変換をコントローラ内部で行い、2点検出座標を出力します。 その為パネルの状態と各軸座標系とを合わせるためパネルパラメータを予め設定する必要があります。 パネルの状態を内蔵の専用回路によってセンシングし、内蔵 CPU で演算することで1点検出/2点検出の自動判別、2点検出時にはゴーストノイズを除いた検出座標を出力可能です。

#### ■ジェスチャ検出

1点検出時、4方向のフリック入力を検出し個別ビットに検出フラグを出力します。

2点検出時、Zoom in/out 操作を検出し Pinch/Spread、一方の座標を回転軸に右回転、左回転操作を 検出し Rotate L/R の個別ビットに検出フラグを出力します。

各ジェスチャと認識する閾値を個別に設定することが可能です。

(注意) ジェスチャの検出フラグのみ出力する機能となりますので速度、移動量、回転量は生成座標データより 別途 HOST マイコンにて演算ください。

#### ■オートパワーダウン、パワーオン機能

オートパワーダウン機能によりタッチインターフェースに入力が発生しない状態が続いた場合、内部消費電力を抑えるため自動的に待機時状態(スリープ状態)となります。 また待機状態中にタッチパネルを操作することで自動的に通常センシング状態へ復帰します。 レジスタにてこの機能の有効/無効、スリープ状態移行閾値を設定可能です。

# ■ホストインターフェース

I2C ライクな 2 線シリアルバス と 4 線 SPI に対応し HOST のスレーブデバイスとして動作します。 インターフェースは IFSEL pin にて選択可能です。 (IFSEL=GND: SPI、IFSEL=VDD: 2 線シリアルバス)

#### ■ EEPROM

内蔵 CPU を機能させる為にファームウェアを内部 RAM へダウンロードする必要があります。 ダウンロードが必要なファームウェアのファイル容量は 16kB (16384byte) です。 ダウンロード方法として「HOST インターフェース」、「外付けの EEPROM」が選択可能です。

#### ■ DVDD 外部印加設定

ご使用のシステム内に 1.8V 系電源がある場合、電源電圧 (VDD) 用に 3V 系電源と コントローラのデジタル CORE 電源電圧 (DVDD) 用に 1.8V 系電源を供給することで待機時消費電流を 10uA (typ) に 抑えることが可能です。

#### ●ブロック図

Figure 4. ブロック図

#### ●各ブロック動作説明

Panel-I/F : 4線式抵抗膜方式タッチパネルインターフェース

ADC : 12bit A/D コンバータ

OSC : 内部用クロック 20MHz 生成発振器

Regulator : 内部用電源 DVDD=1.8V 生成 AVDD, PVDD 電圧はレジスタ設定で変更可能

DVDD のみ外部供給可能

Clock generator : システムクロック, 内部タイミング生成

CPU : ノイズフィルタリング, 2 点タッチ検出, タッチ座標生成

Work memory : CPU ワークメモリ Program memory : CPU プログラムメモリ

EEPROM-I/F : CPU プログラムメモリダウンロードデータ格納用外部 EEPROM-I/F

Host-I/F : 4線 SPI I/F 2線シリアル I/F

Filter : メディアンアベレージフィルタ (最大 16 データ)

#### ●絶対最大定格

| 項目     | 記号   | 定格                | 単 位 | 備考     |

|--------|------|-------------------|-----|--------|

| 電源電圧   | VDD  | -0.3 ~ 4.5        | ٧   | 電源電圧   |

| 端子印加電圧 | VIN  | VSS-0.3 ~ VDD+0.3 | ٧   | 端子印加電圧 |

| 許容損失   | Pd   | 910*1             | mW  | 許容損失   |

| 保存温度範囲 | Tstg | −50 <b>~</b> 125  | လူ  | 保存温度範囲 |

<sup>\*1</sup> 弊社指定 50x58x1. 75mm (8 層) ガラスエポキシ基板実装時。Ta=25℃以上で使用する場合は,1℃につき 9. 10mW を滅じる。

# ●推奨動作範囲

| 75 D           | =7 0 | 規格値   |      | ** 1  | /# #v |            |  |

|----------------|------|-------|------|-------|-------|------------|--|

| 項目             | 記号   | 最小    | 標準   | 最大    | 単位    | 備考         |  |

| 電源電圧           | VDD  | 2. 7  | 3. 0 | 3. 6  | ٧     |            |  |

| デジタル CORE 電源電圧 | DVDD | 1. 62 | 1.80 | 1. 98 | ٧     | DVDD 外部設定時 |  |

| 動作温度           | Topr | -20   | 25   | 85    | °C    |            |  |

# ●電気的特性 (特に記述のない場合は、Ta=25°C、VDD=3.0Vとする)

| 項目       | 記号   | 規格値      |    |          | 単位  | 備考              |  |

|----------|------|----------|----|----------|-----|-----------------|--|

| <b>人</b> | 品 与  | 最 小      | 標準 | 最 大      | 平 位 | ν# <i>1</i> 5   |  |

| 低レベル入力電圧 | VIL  | VSS-0. 5 | _  | 0. 2xVDD | ٧   |                 |  |

| 高レベル入力電圧 | VIH  | 0.8xVDD  | _  | VDD+0. 5 | ٧   |                 |  |

| 低レベル出力電圧 | V0L  | _        | _  | VSS+0. 4 | ٧   |                 |  |

| 高レベル出力電圧 | VOH  | VDD-0. 4 | _  | _        | ٧   |                 |  |

| 静止電流     | Ist  | -        | _  | 5        | uA  | RSTB=L          |  |

| 待機電流 1   | Icc1 | 1        | 60 | 100      | uA  | DVDD_EXT=L      |  |

| 待機電流 2   | Icc2 | 1        | 10 | 20       | uA  | DVDD_EXT=H (*1) |  |

| 動作電流     | Idd  | ı        | 4  | 8        | mA  | 負荷なし            |  |

| 発振周波数    | Freq | 15       | 20 | 24       | MHz |                 |  |

<sup>\*1</sup> DVDD\_EXT="H"の場合 DVDD端子からデジタル CORE電源(1.8V)の供給が必要となります。

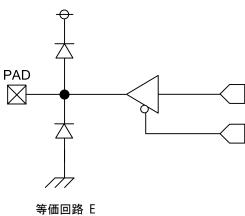

# ●ホストインターフェースタイミング仕様(4線 SPI)

(それぞれ SCK=SCL\_SCK 端子, SI=SDA\_SI 端子, CSB=SEL\_CSB 端子, SO=SO 端子です)

4線 SPI はバーストライト及びバーストリードに対応しています。 自動アドレス加算がおこなわれるのは 0x5F までとなります。アドレス 0x5F アクセス後は 0x5F のままとなります。

Figure 5. タイミング仕様 (4線 SPI)

Table 1. 4線 SPI タイミング仕様 (VDD = 3.0V Ta=25℃)

| 1石口          | ÷⊐ P.                       |    | 規格値 |    | 単位  | 条件 |  |

|--------------|-----------------------------|----|-----|----|-----|----|--|

| 項目           | 記号                          | 最小 | 標準  | 最大 | 早12 | 未针 |  |

| CSB セットアップ時間 | t <sub>1</sub>              | 30 | _   | _  | ns  |    |  |

| SCK の"H"期間   | t <sub>2</sub>              | 30 | _   | _  | ns  |    |  |

| SCK の"L"期間   | t <sub>3</sub>              | 30 | _   | _  | ns  |    |  |

| SI セットアップ時間  | t <sub>4</sub>              | 20 | _   | _  | ns  |    |  |

| SI ホールド時間    | $t_{\scriptscriptstyle{5}}$ | 20 | _   | _  | ns  |    |  |

| CSB ホールド時間   | t <sub>6</sub>              | 20 | _   | -  | ns  |    |  |

| CSB の"H"期間   | t <sub>7</sub>              | 50 | _   | _  | ns  |    |  |

| SO 出力遅延時間    | t <sub>8</sub>              | _  | _   | 15 | ns  |    |  |

| SCK 周波数      | t <sub>9</sub>              | _  | _   | 15 | MHz |    |  |

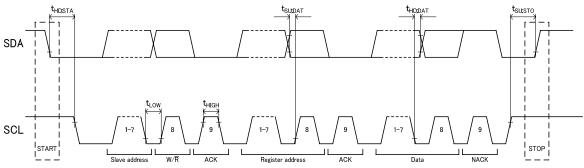

#### ●ホストインターフェースタイミング仕様(2線シリアルバス)

(それぞれ SCL=SCL\_SCK 端子, SDA=SDA\_SI 端子です)

2線シリアルバスはバーストライト及びバーストリードに対応しています。

自動アドレス加算がおこなわれるのは 0x5F までとなります。アドレス 0x5F アクセス後は 0x5F のままとなります。 また、リスタートには対応しておりません。必ずストップ条件を送った後にスタート条件を送ってください。

2 線シリアルバスのスレーブアドレスは、 $SEL_CSB$  端子の状態によって、B8h 又はBAh の どちらかを使用することができます。

$SEL\_CSB = "L"$  : Slave Address = B8h ( 7bit = 5Ch + W/R bit )  $SEL\_CSB = "H"$  : Slave Address = BAh ( 7bit = 5Dh + W/R bit )

Figure 6. タイミング仕様(2線シリアルバス)

Table 2. 2 線シリアルバスタイミング仕様 (VDD = 3.0V Ta=25℃)

| Table 2. Z NK Z J J JV NX Z |                     |      |     |     |            |    |

|-----------------------------|---------------------|------|-----|-----|------------|----|

| 項目                          | 記号                  |      | 規格値 |     | 単位         | 条件 |

| <b>人</b>                    | 品。行                 | 最小   | 標準  | 最大  | <b>平</b> 位 | 木江 |

| SCL クロック周波数                 | f <sub>scL</sub>    | 0    | -   | 400 | kHz        |    |

| START ホールド時間                | t <sub>HD:STA</sub> | 0. 6 | _   | _   | us         |    |

| SCL の"L"期間                  | t <sub>LOW</sub>    | 1.3  | _   | _   | us         |    |

| SCL の"H"期間                  | t <sub>HIGH</sub>   | 0. 6 | _   | _   | us         |    |

| データホールド時間                   | t <sub>HD:DAT</sub> | 0. 1 | _   | _   | us         |    |

| データセットアップ時間                 | t <sub>su:DAT</sub> | 0. 1 | _   | _   | us         |    |

| STOP セットアップ時間               | t <sub>su:sto</sub> | 0. 6 | _   | _   | us         |    |

# • Write Protocol

| S | SLAVE<br>ADDRESS  | W | Α | REGISTER<br>ADDRESS | Α | WRITE<br>DATA | Α | Р |

|---|-------------------|---|---|---------------------|---|---------------|---|---|

|   | 7bit = 5Ch or 5Dh |   |   | 8bit                |   | 8bit          |   |   |

#### · Read Protocol

| S | SLAVE<br>ADDRESS  | W | Α | REGISTER<br>ADDRESS | Α | Р | S | SLAVE<br>ADDRESS  | R | A | READ<br>DATA | N | Р |

|---|-------------------|---|---|---------------------|---|---|---|-------------------|---|---|--------------|---|---|

|   | 7bit = 5Ch or 5Dh |   |   | 8bit                |   |   |   | 7bit = 5Ch or 5Dh |   |   | 8bit         |   |   |

| ı |                   |   |   |                     | ı |   |   |                   |   |   |              |   |   |

Figure 7. Read/Write Protocol

#### ●応用回路例

BU21021GUL は2つのホストインターフェース(4線 SPI, 2線シリアルバス)を有します。 各インターフェース使用時のアプリケーション回路例を下図に示します。

(BU21021GUL は CSP パッケージですが端子表示で示します)

Option(\*1) タッチパネルノイズ除去用

ファームウェアダウンロードを HOST から行う場合、EEPROM は不要です。 Option(\*2)

ECL/EDA 端子は VSS へ接続してください。

EEPROM からファームウェアダウンロードを行う場合は EEPROM を接続して下さい。

Option(\*3) Slave address = BAh で使用される場合は GND ではなく VDD に接続してください。

Figure 8. アプリケーション回路例 1 (4線 SPI)

Figure 9. アプリケーション回路例 2 (2線シリアルバス)

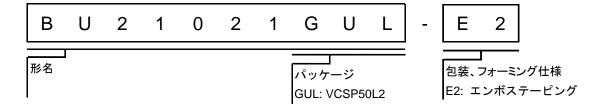

#### ●発注形名セレクション

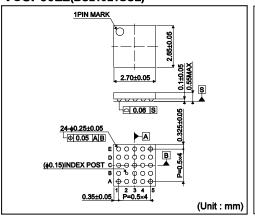

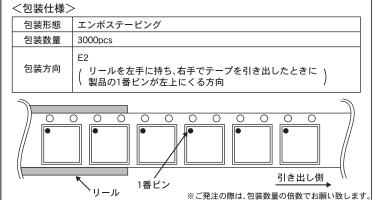

#### ●包装図、フォーミング仕様

# VCSP50L2(BU21021GUL)

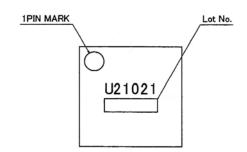

#### ●標印図

# 改訂履歴

| 日付         | 版   | 変更内容                                                                                                                                                                                                                      |

|------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2012/06/19 | 001 | 新規作成                                                                                                                                                                                                                      |

| 2016/11/30 | 002 | 1 ページ 重要特性<br>動作温度範囲を訂正しました。<br>(前) -25[℃]~85[℃] (後) -20[℃]~85[℃]<br>1 ページ Figure 1<br>9 ページ Figure 8, Figure 9<br>アプリケーション回路例に下の変更を行いました。<br>・ VDD とグランド間にバイパスコンデンサを追加しました。<br>・ YN、XN、YP、XP 端子の ESD 保護用 Di のタイプを変更しました。 |

|            |     |                                                                                                                                                                                                                           |

|            |     |                                                                                                                                                                                                                           |

# ご注意

#### ローム製品取扱い上の注意事項

1. 本製品は一般的な電子機器(AV機器、OA機器、通信機器、家電製品、アミューズメント機器等)への使用を意図して設計・製造されております。したがいまして、極めて高度な信頼性が要求され、その故障や誤動作が人の生命、身体への危険もしくは損害、又はその他の重大な損害の発生に関わるような機器又は装置(医療機器(Note 1)、輸送機器、交通機器、航空宇宙機器、原子力制御装置、燃料制御、カーアクセサリを含む車載機器、各種安全装置等)(以下「特定用途」という)への本製品のご使用を検討される際は事前にローム営業窓口までご相談くださいますようお願い致します。ロームの文書による事前の承諾を得ることなく、特定用途に本製品を使用したことによりお客様又は第三者に生じた損害等に関し、ロームは一切その責任を負いません。

(Note 1) 特定用途となる医療機器分類

|   | 日本      | USA      | EU         | 中国   |

|---|---------|----------|------------|------|

| Ī | CLASSⅢ  | CLACCIII | CLASS II b | Ⅲ 米百 |

|   | CLASSIV | CLASSⅢ   | CLASSⅢ     | Ⅲ類   |

- 2. 半導体製品は一定の確率で誤動作や故障が生じる場合があります。万が一、かかる誤動作や故障が生じた場合であっても、本製品の不具合により、人の生命、身体、財産への危険又は損害が生じないように、お客様の責任において次の例に示すようなフェールセーフ設計など安全対策をお願い致します。

- ①保護回路及び保護装置を設けてシステムとしての安全性を確保する。

- ②冗長回路等を設けて単一故障では危険が生じないようにシステムとしての安全を確保する。

- 3. 本製品は、一般的な電子機器に標準的な用途で使用されることを意図して設計・製造されており、下記に例示するような特殊環境での使用を配慮した設計はなされておりません。したがいまして、下記のような特殊環境での本製品のご使用に関し、ロームは一切その責任を負いません。本製品を下記のような特殊環境でご使用される際は、お客様におかれまして十分に性能、信頼性等をご確認ください。

- ①水・油・薬液・有機溶剤等の液体中でのご使用

- ②直射日光・屋外暴露、塵埃中でのご使用

- ③潮風、Cl<sub>2</sub>、H<sub>2</sub>S、NH<sub>3</sub>、SO<sub>2</sub>、NO<sub>2</sub>等の腐食性ガスの多い場所でのご使用

- ④静電気や電磁波の強い環境でのご使用

- ⑤発熱部品に近接した取付け及び当製品に近接してビニール配線等、可燃物を配置する場合。

- ⑥本製品を樹脂等で封止、コーティングしてのご使用。

- ⑦はんだ付けの後に洗浄を行わない場合(無洗浄タイプのフラックスを使用された場合も、残渣の洗浄は確実に 行うことをお薦め致します)、又ははんだ付け後のフラックス洗浄に水又は水溶性洗浄剤をご使用の場合。

- ⑧本製品が結露するような場所でのご使用。

- 4. 本製品は耐放射線設計はなされておりません。

- 5. 本製品単体品の評価では予測できない症状・事態を確認するためにも、本製品のご使用にあたってはお客様製品に実装された状態での評価及び確認をお願い致します。

- 6. パルス等の過渡的な負荷 (短時間での大きな負荷) が加わる場合は、お客様製品に本製品を実装した状態で必ず その評価及び確認の実施をお願い致します。また、定常時での負荷条件において定格電力以上の負荷を印加されますと、 本製品の性能又は信頼性が損なわれるおそれがあるため必ず定格電力以下でご使用ください。

- 7. 電力損失は周囲温度に合わせてディレーティングしてください。また、密閉された環境下でご使用の場合は、必ず温度 測定を行い、最高接合部温度を超えていない範囲であることをご確認ください。

- 8. 使用温度は納入仕様書に記載の温度範囲内であることをご確認ください。

- 9. 本資料の記載内容を逸脱して本製品をご使用されたことによって生じた不具合、故障及び事故に関し、ロームは一切その責任を負いません。

#### 実装及び基板設計上の注意事項

- 1. ハロゲン系(塩素系、臭素系等)の活性度の高いフラックスを使用する場合、フラックスの残渣により本製品の性能又は信頼性への影響が考えられますので、事前にお客様にてご確認ください。

- 2. はんだ付けは、表面実装製品の場合リフロー方式、挿入実装製品の場合フロー方式を原則とさせて頂きます。なお、表面実装製品をフロー方式での使用をご検討の際は別途ロームまでお問い合わせください。その他、詳細な実装条件及び手はんだによる実装、基板設計上の注意事項につきましては別途、ロームの実装仕様書をご確認ください。

# 応用回路、外付け回路等に関する注意事項

- 1. 本製品の外付け回路定数を変更してご使用になる際は静特性のみならず、過渡特性も含め外付け部品及び本製品のバラッキ等を考慮して十分なマージンをみて決定してください。

- 2. 本資料に記載された応用回路例やその定数などの情報は、本製品の標準的な動作や使い方を説明するためのもので、 実際に使用する機器での動作を保証するものではありません。したがいまして、お客様の機器の設計において、回路や その定数及びこれらに関連する情報を使用する場合には、外部諸条件を考慮し、お客様の判断と責任において行って ください。これらの使用に起因しお客様又は第三者に生じた損害に関し、ロームは一切その責任を負いません。

#### 静電気に対する注意事項

本製品は静電気に対して敏感な製品であり、静電放電等により破壊することがあります。取り扱い時や工程での実装時、保管時において静電気対策を実施のうえ、絶対最大定格以上の過電圧等が印加されないようにご使用ください。特に乾燥環境下では静電気が発生しやすくなるため、十分な静電対策を実施ください。(人体及び設備のアース、帯電物からの隔離、イオナイザの設置、摩擦防止、温湿度管理、はんだごてのこて先のアース等)

# 保管・運搬上の注意事項

- 1. 本製品を下記の環境又は条件で保管されますと性能劣化やはんだ付け性等の性能に影響を与えるおそれがあります のでこのような環境及び条件での保管は避けてください。

- ①潮風、CI<sub>2</sub>、H<sub>2</sub>S、NH<sub>3</sub>、SO<sub>2</sub>、NO<sub>2</sub>等の腐食性ガスの多い場所での保管

- ②推奨温度、湿度以外での保管

- ③直射日光や結露する場所での保管

- ④強い静電気が発生している場所での保管

- 2. ロームの推奨保管条件下におきましても、推奨保管期限を経過した製品は、はんだ付け性に影響を与える可能性があります。推奨保管期限を経過した製品は、はんだ付け性を確認したうえでご使用頂くことを推奨します。

- 3. 本製品の運搬、保管の際は梱包箱を正しい向き(梱包箱に表示されている天面方向)で取り扱いください。天面方向が 遵守されずに梱包箱を落下させた場合、製品端子に過度なストレスが印加され、端子曲がり等の不具合が発生する 危険があります。

- 4. 防湿梱包を開封した後は、規定時間内にご使用ください。規定時間を経過した場合はベーク処置を行ったうえでご使用ください。

#### 製品ラベルに関する注意事項

本製品に貼付されている製品ラベルに2次元バーコードが印字されていますが、2次元バーコードはロームの社内管理のみを目的としたものです。

#### 製品廃棄上の注意事項

本製品を廃棄する際は、専門の産業廃棄物処理業者にて、適切な処置をしてください。

# 外国為替及び外国貿易法に関する注意事項

本製品は外国為替及び外国貿易法に定める規制貨物等に該当するおそれがありますので輸出する場合には、ロームにお問い合わせください。

#### 知的財産権に関する注意事項

- 1. 本資料に記載された本製品に関する応用回路例、情報及び諸データは、あくまでも一例を示すものであり、これらに関する第三者の知的財産権及びその他の権利について権利侵害がないことを保証するものではありません。

- 2. ロームは、本製品とその他の外部素子、外部回路あるいは外部装置等(ソフトウェア含む)との組み合わせに起因して生じた紛争に関して、何ら義務を負うものではありません。

- 3. ロームは、本製品又は本資料に記載された情報について、ロームもしくは第三者が所有又は管理している知的財産権 そ の他の権利の実施又は利用を、明示的にも黙示的にも、お客様に許諾するものではありません。 ただし、本製品を通 常の用法にて使用される限りにおいて、ロームが所有又は管理する知的財産権を利用されることを妨げません。

# その他の注意事項

- 1. 本資料の全部又は一部をロームの文書による事前の承諾を得ることなく転載又は複製することを固くお断り致します。

- 2. 本製品をロームの文書による事前の承諾を得ることなく、分解、改造、改変、複製等しないでください。

- 3. 本製品又は本資料に記載された技術情報を、大量破壊兵器の開発等の目的、軍事利用、あるいはその他軍事用途目的で使用しないでください。

- 4. 本資料に記載されている社名及び製品名等の固有名詞は、ローム、ローム関係会社もしくは第三者の商標又は登録商標です。

Notice-PGA-J Rev.003

# 一般的な注意事項

- 1. 本製品をご使用になる前に、本資料をよく読み、その内容を十分に理解されるようお願い致します。本資料に記載される注意事項に反して本製品をご使用されたことによって生じた不具合、故障及び事故に関し、ロームは一切その責任を負いませんのでご注意願います。

- 2. 本資料に記載の内容は、本資料発行時点のものであり、予告なく変更することがあります。本製品のご購入及びご使用に際しては、事前にローム営業窓口で最新の情報をご確認ください。

- 3. ロームは本資料に記載されている情報は誤りがないことを保証するものではありません。万が一、本資料に記載された情報の誤りによりお客様又は第三者に損害が生じた場合においても、ロームは一切その責任を負いません。

Notice – WE Rev.001