#### SIC MOSFET

# MOSFET 병렬접속 시의 발진 대책

근래, 산업 기기나 xEV 등의 애플리케이션에서 대전류화가 진행되어, 저렴한 디스크리트 패키지의 파워 디바이스를 병렬로 사용한 회로 방식의 채용이 진행되고 있습니다. MOSFET 를 병렬접속 함으로써, 각각의 디바이스에 흐르는 전류를 줄이고, 발열을 분산시킬 수 있게 됩니다. 그러나, 각각의 디바이스에는 특성 편차가 존재하기 때문에, MOSFET를 병렬로 연결하여 동시에 동작시킬 경우, 각각의 MOSFET를 완전히 동일한 타이밍으로 동작시키는 것은 어려우며, 단독으로 사용하는 경우와 비교하여, 구동 방법에 주의할 필요가 있습니다. 그래서. 이 애플리케이션 노트에서는 SiC MOSFET의 병렬접속 시의 발진에 대해서, 실측 결과에 근거하여 동작을 밝힘과 동시에, 구동 회로를 포함한 기판 레이아웃의 주의점을 가이드라인으로써 제시하는 것을 목적으로 하고 있습니다. \*1

#### 목차

| 2  |

|----|

|    |

| 2  |

|    |

| 3  |

| •  |

| 3  |

|    |

| 2  |

|    |

| 11 |

|    |

| 14 |

| _  |

\*1: 금번에는 2개의 MOSFET를 병렬 접속시켰을 때의 동작에 대해서 해설하고 있지만, 병렬 수가 많아지면, 각각의 디바이스 편차로 인한 예상치 못한 사태는 피할 수 없으므로, 병렬접속 시에는 충분한 평가를 하여, 사용 여부 판단을 부탁드립니다. 또한, 디바이스의 특성 편차는 불가피한 것이므로, 가능한 단일 디바이스로 설계를 부탁드립니다.

© 2023 ROHM Co., Ltd. No.66AN030K Rev.001 1/15

# 1.병렬접속용 기판

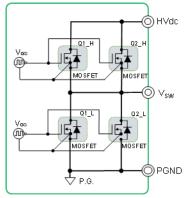

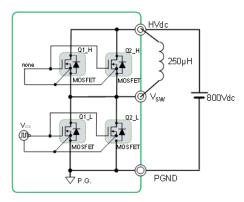

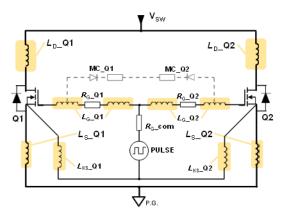

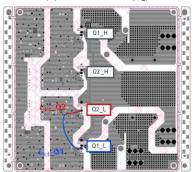

병렬접속용으로 작성한 블록도를 Figure 1-1 에 나타냅니다. 브릿지 구성으로 되어 있으며, 상하 각각의 Arm 에 MOSFET 가 병렬 접속되어 있으며, 하나의 구동 신호로 ON/OFF 하고 있습니다. 기판 사진을 Figure 1-2 에 나타냅니다.

Figure 1-1. PCB008P 간이 블록도

Figure 1-2. PCB008P (top view)

# 2.병렬접속 시의 게이트 구동회로

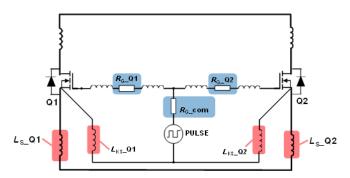

병렬 접속시의 게이트 구동회로는 통상 2 개 이상의 MOSFET 에 대해 1 개의 게이트 드라이버로 설계합니다. Figure 2-1 에 참고 회로를 나타냅니다. Figure 2-1 에서는 주의점을 간단히 나타낸 회로이므로 부품 정수 등은 사용하는 MOSFET의 특성에 맞춰 설정할 필요가 있습니다.

1. 게이트 드라이버의 출력 전류를 확인하고, Q1, Q2 의 게이트 구동 전류가 부족하면, Q3, Q4를 이용하여 버퍼 회로를 추가합니다. PCB008P 에서는 바이폴라 트랜지스터(ROHM: 2SCR542P, 2SAR542P)를 사용하여 최대 10A로 증폭했습니다.

- 2. 반드시 공통 게이트 저항  $R_{G_{-}}$ com 외에 개별 게이트 저항  $R_{G_{-}}$ Q1,  $R_{G_{-}}$ Q2 를 삽입합니다. 이유는 Q1, Q2 의 스위칭 동작을 균일화하기 위한 것이지만, 자세한 것은 본 애플리케이션 노트 「6.발진 대처법의 검증」에서 나타냅니다. PCB008P 에서는  $R_{G_{-}}$ com 을  $4.7\Omega$ ,  $R_{G_{-}}$ Q1,  $R_{G_{-}}$ Q2 를  $2\Omega$ 으로 설정했습니다. 그 이유에 대해서도 본 애플리케이션 노트 「5.발진 평가 결과」 및 「6.발진 대처법의 검증」에서 설명합니다.

- 3. Miller Clamp(이하, MC) 기능을 갖는 게이트 드라이버의 경우는  $R_{G_-}$ Q1,  $R_{G_-}$ Q2 보다 게이트 근방을 감시하고, Dot OR 회로(다이오드를 통해 접속하여, 높은 전압의 신호가 유효하게 되는 회로)가 되도록 다이오드 D1, D2 를 이용하여 MC 단자에 접속합니다. 이와 같이 접속함으로써 Q1, Q2 가 환류 동작 시의 게이트 전압 상승을 억제할 수 있습니다. R2, R3 는 MC 단자에 흐르는 전류를 조정합니다. PCB008P 에서는 0Ω으로 설정했습니다.

Figure 2-1. 게이트 구동 회로 (Low side)

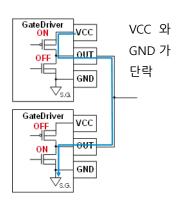

또한, 1개의 MOSFET에 대하여, 1개씩 게이트 드라이버를 사용하는 것도 가능합니다. 이 경우, 이번에 설명한 경로에서 발진은 일어나지 않습니다. 다만, MOSFET의 특성 편차와 게이트 드라이버의 특성 편차까지 포함하여 ON/OFF하기 때문에, 스위칭 타이밍에도 편차가 발생하기 쉽고, 한쪽의 MOSFET가 과부하가 될 가능성이 있으므로, 보다 편차가 작은 설계를 할 필요가 있습니다. 또한, 타이밍을 맞추기 위해, 게이트 드라이버끼리 출력을 직접 연결하면, Figure 2-2 에 나타냈듯이 게이트 드라이버의 편차에 의해, 게이트 드라이버 내의 어느 한쪽이 ON, 다른한쪽이 OFF가 되어 버릴 가능성이 있어, ON 측의 게이트 전압과 OFF 측의 GND 가 단락되어 게이트 드라이버가 파괴될 가능성이 있으므로, 게이트 드라이버끼리 출력을 직접 연결하지 말아 주십시오.

Figure 2-2. 게이트 드라이버 출력의 직접 연결에 의한 게이트 드라이버 간의 단락

# 3.병렬접속 시의 발진 요인

병렬접속 시에 일어나는 발진은 각각의 디바이스 동작 타이밍의 어긋남이 트리거가 되어 발생합니다. 레이아웃의 불균형이나 MOSFET 자체의 편차에 의하여 ON 또는 OFF 타이밍이 어긋났을 때, 한쪽의 MOSFET 에 전류가 치우쳐, 레이아웃의 기생 인덕턴스에 발생하는 유도기전력이 이웃한 MOSFET 끼리 다름에 따라 전위차가 생깁니다. 이 전위차에 의한 에너지가 MOSFET 의 기생 용량을 통해 왕래함으로써 발진 현상이 출현합니다. (Figure 4-1 참조)

Figure 4-1. 발진 경로

이 발진의 진폭이 커지면, 파괴를 초래할 위험이 있습니다. 게다가 게이트 단자의 발진 진폭이  $V_{GS}$  정격을 넘지 않았다고 해도, EMC 시험에서 규격을 상회하는 노이즈가 발생해 버릴 가능성도 있기 때문에, 이러한 발진은 가능한 한 억제할 필요가 있습니다.

MOSFET 의 ON 또는 OFF 타이밍에 차이가 생기는 요인을 아래에 5 가지 나타냅니다. 회로상의 요인이  $A \sim C$ , MOSFET 의 특성으로 발생하는 요인이 D, E 입니다.

A: 기판 상의 기생 인덕턴스(이하, 기생 L)가 Q1, Q2 에 불균형하게 되어 있는 것

B: MOSFET 의 d/b/dt 가 큰 것

C: 개별 게이트 저항 R<sub>G</sub>Q1, R<sub>G</sub>Q2 가 다른 값인 경우

D : MOSFET 의 역치(이하, V<sub>GS(th)</sub>)가 Q1, Q2 에서 불균형적으로 되어 있는 것

E : MOSFET 의 기생용량이 Q1、Q2 에서 불균형적으로 되어 있는 것

이러한 요인에 대하여, 평가 기판 PCB008P 를 사용하여 실제로 검증한 결과를 다음 절에서 설명합니다.

# 4.발진 평가 항목

앞 절에서 제시한 5 가지 요인으로부터 평가 항목을 아래와 같이 결정하였습니다.

A': 기생 L을 Q1, Q2 로 불균형적으로 함

A'-1 : Drain 의 기생 인덕턴스 (이하,  $L_D$ )를 Q1, Q2 로 불균형적으로 함

A'-2 : Source 의 기생 인덕턴스 (이하,  $L_S$ )를 Q1, Q2 로 불균형적으로 함

A'-3 : Gate 의 기생 인덕턴스 (이하,  $L_G$ )를 Q1, Q2 로 불균형적으로 함

A'-4 : Kelvin source 의 기생 인덕턴스 (이하,  $L_{KS}$ )를 Q1, Q2 로 불균형적으로 함

B': MOSFET 의 Drain 전류 변화율(이하, d/b/dt)을 크게 함

B'-1 : Drain 전류(이하, I<sub>D, pulse</sub>)를 크게 함 B'-2 : 공통 Gate 저항 *R*<sub>G</sub>\_com 을 낮춤

C': 개별 Gate 저항  $R_{G_-}$ Q1,  $R_{G_-}$ Q2 를 불균형적으로 함

D': V<sub>GS(th)</sub>를 Q1, Q2 로 불균형적으로 함

E': 기생 용량을 Q1, Q2 로 불균형적으로 함

E'-1: CGD 를 Q1, Q2 로 불균형적으로 함

E'-2: CGS 를 Q1, Q2 로 불균형적으로 함

E'-3: C<sub>DS</sub>를 Q1, Q2로 불균형적으로 함

다만, 평가 항목 E'에 대해서는 평가 샘플의 입수 관련 문제가 있으므로, 시뮬레이션을 이용하여 확인했습니다.

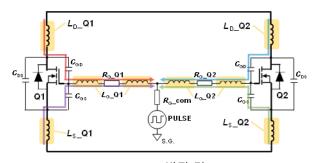

발진 평가 조건 및 회로를 Figure 4-2 에 나타냅니다. 또한, 평가 사진을 Figure 4-3 에 나타냅니다. 이번 평가에서는, Gate 의 발진 파형을 올바르게 측정하기 위해,  $V_{GS}$  파형 측정 Probe 에 Tektronix®의 광절연 방식의 차동 Probe 를 사용했습니다. 특히 Gate 전압 측정에 있어서, High side 측은 측정 환경의 영향도 커지므로, 충분히 주의할 필요가 있습니다. 자세한 내용은 애플리케이션 노트「Gate

- Source 전압 측정 시의 주의점」[1]에서 확인해 주십시오.

평가 기판 : PCB008P

병렬수: 2 병렬

SiC MOSFET : SCT4018KR (1200V 18mohm TO-247- 4L) 평가 회로 : Low side(이하, LS) 스위칭 더블 펄스 회로

HV dc 전압 *E*=800V 인덕터 *L*=250µH Gate 전압 *V*<sub>GS</sub>=18V/0V 측정 온도 *T*=25°C

#### 측정기

오실로스코프: MSO58 5-BW-500 Tektronix®  $V_{DS}$ 파형 측정 Probe: THDP0200 Tektronix®

V<sub>GS</sub> 파형 측정 Probe : TIVP05, 650-6122-00 Tektronix®

Љ파형 측정 Probe: SS-665 IWATSU

Figure 4-2. 평가 회로 (더블 펄스 LS 스위칭)

Figure 4-3. 평가 환경 사진

이번 발진 평가에서는 Gate 의 발진 파형에 주목했습니다. 또한, Gate OFF 할 때가, Gate ON 할 때보다 Drain 전류의 변화율이 크고, 발진 트리거가 커지므로, Gate OFF 파형으로 비교하였습니다.

# 5.발진 평가 결과

# A': 기생 L을 Q1, Q2 로 불균형적으로 함

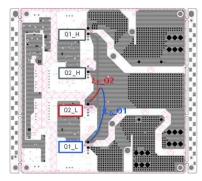

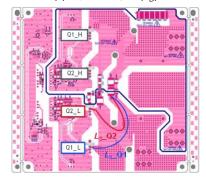

우선 기판 상의 기생 L 성분을 Ansys®의 전자계 해석 소프트웨어(Q3D Extractor®)를 사용해 추출했습니다. 기생 L 추출 장소를 표기한 회로도를 Figure 5-1 에 나타내고, PCB008P의 기판 패턴 레이아웃을 Figure 5-2 에 나타내고, 기생 L 추출 결과를 Table 5-1 에 나타냅니다.

Figure 5-1. 기생 L 추출 장소

(a) 부품면 패턴 (L<sub>G</sub>)

(b) 제 2 층 패턴 (L<sub>KS</sub>)

(c) 제 3 층 패턴 (L<sub>D</sub>)

(d) 솔더면 패턴 (L<sub>S</sub>) Figure 5-2. PCB008P 레이아웃

Table 5-1. 기생 L 추출 결과

|                 | L_Q1[nH] | L_Q2[nH] | L_Q1-L_Q2[nH] |

|-----------------|----------|----------|---------------|

| LD              | 15.67    | 4.61     | 11.06         |

| Ls              | 10.70    | 16.20    | -5.50         |

| L <sub>G</sub>  | 17.66    | 6.74     | 10.92         |

| L <sub>KS</sub> | 7.74     | 2.62     | 5.12          |

추출 결과에 따라, 기생 L 이 기판 상에서 이미 불균형하게 되어 있는 것을 알 수 있습니다. 이번 평가에서는 Figure 5-1 에서 점선으로 나타낸 MC 회로의 기생 L 은 고려하지 않았습니다. 이유는, 이번 평가에서 사용한 다이오드의 기생 용량(약 50pF)으로는 이번에 발생하고 있는 발진 주파수 대역에서는 High impedance 가 되어, 발진 경로가 되지 않고, 기생 L 은 무시할 수 있기 때문입니다.

불균형을 보다 크게 하기 위해 기생 L 이 큰 MOSFET 의 Lead 단자에 배선을 의도적으로 추가하였습니다. Figure 5-3 에 MOSFET 를 옆에서 봤을 때의 배선 추가 이미지를 나타냅니다.

Figure 5-3. 배선 추가 이미지

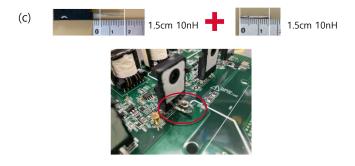

아래 (b)~(d) 3 종류의 배선을 추가하여 접속했습니다.

Figure 5-4 에 실제로 추가한 배선의 상태를 나타냅니다.

- (a) 추가 없음

- (b) 10nH 추가

- (c) 20nH 추가

- (d) 100nH 추가

Figure 5-4. 기생 L 추가

일반적인 기판 상의 편차를 10nH~20nH 로 하고, PCB008P 기판에 추가로 10nH, 20nH 을 더함으로써 10nH~25nH 까지의 편차를 평가하는 것이 가능합니다. 또한, 이번 평가에서는 한계 평가를 실시함으로써 MOSFET 가 발진에 의한 파괴 여부를 조사하기 위해, 비현실적인

기생 L 의 불균형 값으로 100nH 에서의 평가도 실시했습니다. 평가 항목 A'의 더블 펄스 평가 조건은 다음과 같습니다. 발진을 보다 쉽게 관측하기 위해, 개별 Gate 저항은 0Ω으로 했습니다.

/<sub>D, pulse</sub>: 128A (합계 256A)

$R_{G}$ Q1,  $R_{G}$ Q2: 0 $\Omega$

$R_{G}$ \_com :  $2\Omega$

V<sub>GS(th)</sub>\_Q1, V<sub>GS(th)</sub>\_Q2 : 4.2V(사용한 디바이스의 실측치)

#### A'-1: LD를 Q1, Q2 로 불균형적으로 함

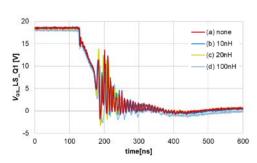

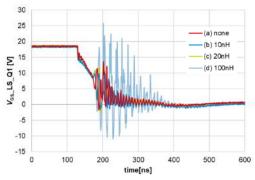

$L_D$ 는 Q1 의 기생 L 이 크므로 Q1 에 배선을 추가했습니다. Gate OFF 시의  $V_{GS}$ LS\_Q1 파형을 Figure 5-5 에 나타냅니다.

Figure 5-5. V<sub>GS</sub> 파형 (L<sub>D</sub> 불균형)

조건(a)에서 발진이 보이는 것은 개별 Gate 저항이  $0\Omega$ 인 것이나 기판의 기생 L 의 불균형이 영향을 주고 있는 것을 생각할 수 있습니다. 조건(a)를 기준으로 조건(b), (c), (d)를 보면 진폭은 큰 차이가 없습니다.

#### A'-2: 서를 Q1, Q2로 불균형적으로 함

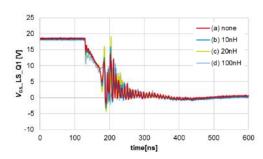

$L_{\rm S}$  는 Q2 의 기생 L 이 크기 때문에, Q2 에 배선을 추가했습니다. Gate OFF 시의  $V_{\rm GS}$ \_LS\_Q1 파형을 Figure 5-6 에 나타냅니다. Q2 에 배선을 추가하더라도, Q1, Q2 의 Gate 끼리는  $R_{\rm G}$ \_Q1,  $R_{\rm G}$ \_Q2 를 통해 연결되어 있어, 동일한 파형이 관측될 수 있음을 확인하였으므로, 이번 평가에서는 모든 조건을 Q1 의 Gate 전압 파형으로 비교하였습니다.

Figure 5-6. V<sub>GS</sub> 파형 (L<sub>S</sub> 불균형)

조건(a)를 기준으로 조건(b), (c), (d)를 보면 조건(c)까지는 큰 차이가 없지만, 조건(d)에서는 진폭이 약 -10V~25V 까지흔들려,  $V_{GS}$  정격을 큰 폭으로 초과합니다. 발진의 지속시간은 3 배 정도로 길어졌습니다. 이것이 병렬 공진에 의한 발진으로, 이대로 사용하면 파괴될 가능성이 있습니다.  $L_{S}$ 의 불균형은 발진의 진폭, 발진 지속 시간을 증대시키는 것을 알수 있습니다.

#### A'-3: L<sub>G</sub>를 Q1, Q2로 불균형적으로 함

$L_{\rm G}$  는 Q1 의 기생 L 이 크기 때문에, Q1 에 배선을 추가했습니다. Gate OFF 시의  $V_{\rm GS\_LS\_Q1}$  파형을 Figure 5-7 에 나타냅니다.

Figure 5-7.  $V_{GS}$  파형 ( $L_{G}$  불균형)

조건(a)를 기준으로 조건(b), (c), (d)를 보면, 조건에 따라 진폭이 군데군데 크게 나오는 변화가 있지만, 발진의 지속 시간에 큰 변화는 없습니다.

# $A'-4: L_{KS}$ 를 Q1, Q2 로 불균형적으로 함

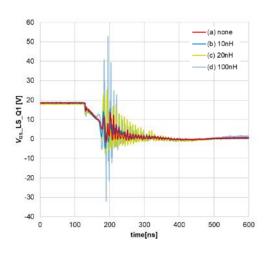

$L_{KS}$  는 Q1 의 기생 L 이 크기 때문에, Q1 에 배선을 추가했습니다. Gate OFF 시의  $V_{GS}$ LS\_Q1 파형을 Figure 5-8 에 나타냅니다.

Figure 5-8. V<sub>GS</sub> 파형 (L<sub>KS</sub> 불균형)

조건(a)를 기준으로 조건(b), (c), (d)를 보면,  $L_{KS}$ 를 불균형하게 할수록 Gate 전압의 진폭이 커지고 있음을 알 수 있었습니다. 조건(d)에서는 진폭이 50V를 넘어서,  $V_{GS}$ 정격을 초과하고 있지만, 조건(c)에서도 정격을 초과할 위험이 있습니다.  $L_{KS}$ 의 불균형은 발진의 진폭, 발진 지속시간을 증대시킵니다.

# B' : MOSFET 의 $d/_D/dt$ 를 크게 하다

#### B'-1: /<sub>D. pulse</sub> 를 크게 하다

/<sub>D, pulse</sub> 의 크기로 발진 비교를 실시했습니다. 평가항목 B'-1 의 평가조건은 다음과 같습니다.

기생 L: 기판의 인덕턴스(Table 5-1)만

$R_{G}$ Q1,  $R_{G}$ Q2: 0 $\Omega$

$R_{G}$ \_com :  $2\Omega$

$V_{GS(th)}$ \_Q1,  $V_{GS(th)}$ \_Q2: 4.2V

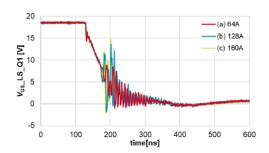

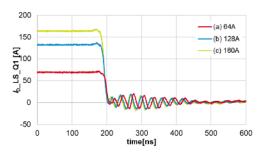

$L_{\rm D,~pulse}$  를 아래의 (a)  $\sim$  (c)의 조건으로 했을 때, Gate OFF 시의  $V_{\rm GS}$ \_LS\_Q1 파형을 Figure 5-9 에 나타냅니다.

(a) /<sub>D, pulse</sub>: 64A (합계 128A) (b) /<sub>D, pulse</sub>: 128A (합계 256A) (c) /<sub>D, pulse</sub>: 160A (합계 320A)

Figure 5-9.  $V_{GS}$  파형 ( $I_{D, pulse}$  증가)

또한,  $h_L$ LS\_Q1 파형을 Figure 5-10 에 나타냅니다. Gate OFF 시의 MOSFET 하나당 d $h_0$ /dt 은 다음과 같습니다.

(a) /<sub>D, pulse</sub>: 64A (합계 128A) d/<sub>D</sub>/dt: 5.8A/ns (b) /<sub>D, pulse</sub>: 128A (합계 256A) d/<sub>D</sub>/dt: 8.5A/ns (c) /<sub>D, pulse</sub>: 160A (합계 320A) d/<sub>D</sub>/dt: 10.2A/ns

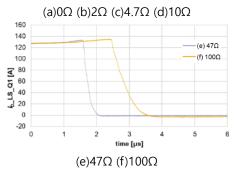

Figure 5-10.  $_{h}$  파형 ( $_{h}$ , pulse 증가)

Љ 를 크게 하면, Gate OFF 시의 d⅓/dt 는 커져서, 스위칭 스피드가 빨라지기 때문에, 발진 트리거가 되기 쉽고, 발진 진폭이 커진 것을 알 수 있습니다.

### B'-2 : 공통 Gate 저항 R<sub>G</sub>\_com 을 낮춤

공통 Gate 저항을 낮추면 스위칭 스피드가 빨라져  $d/_D/dt$  가 커집니다. 평가항목 B'-2 의 평가조건은 다음과 같습니다.  $R_{G\_}com$  이  $0\Omega$  일 때, 개별 Gate 저항이  $0\Omega$ 이라면, Gate 저항의 합계가  $0\Omega$ 이 되어,  $V_{DS}$  가 정격을 초과해 버렸기때문에,  $R_{G\_}Q1$ ,  $R_{G\_}Q2$  을  $2\Omega$ 으로 했습니다.

/<sub>D, pulse</sub>: 128A (합계 256A)

기생 L: 기판의 인덕턴스(Table 5-1)만

$R_{G}$ Q1,  $R_{G}$ Q2: 2 $\Omega$

$V_{GS(th)}$ \_Q1,  $V_{GS(th)}$ \_Q2: 4.2V

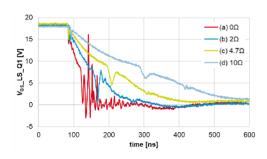

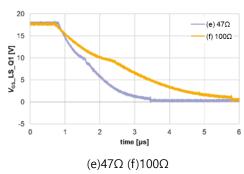

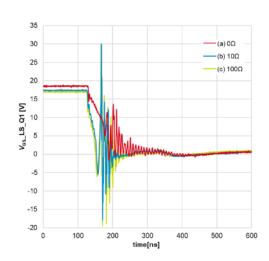

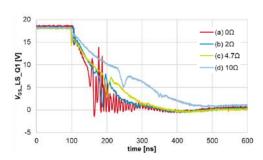

아래의 (a) ~ (f)까지  $R_{\rm G}$ \_com 을 바꿨을 때, Gate OFF 시의  $V_{\rm GS}$ \_LS\_Q1 파형을 Figure 5-11 에 나타냅니다.

(a)  $R_{\rm G}$ \_com :  $0\Omega$ (b)  $R_{\rm G}$ \_com :  $2\Omega$ (c)  $R_{\rm G}$ \_com :  $4.7\Omega$ (d)  $R_{\rm G}$ \_com :  $10\Omega$ (e)  $R_{\rm G}$ \_com :  $47\Omega$ (f)  $R_{\rm G}$ \_com :  $100\Omega$

(a)0 $\Omega$  (b)2 $\Omega$  (c)4.7 $\Omega$  (d)10 $\Omega$

Figure 5-11.  $V_{GS}$  파형 ( $R_{G}$ com 감소)

(a) ~ (f)까지  $R_{G}$ \_com 을 바꿨을 때, Gate OFF 시의  $I_{D}$ \_LS\_Q1 파형을 Figure 5-12 에 나타냅니다. 또한, 각각의 MOSFET 하나당 d/<sub>D</sub>/dt 는 아래와 같이 되었습니다.

(a)  $R_{G}$  com :  $\Omega\Omega$  d $I_{D}$ /dt : 12.3A/ns (b)  $R_{G}$ com :  $2\Omega$  d $I_{D}$ /dt : 8.7A/ns (c)  $R_{G}$ \_com : 4.7 $\Omega$  d $I_{D}$ /dt : 6.4A/ns (d)  $R_{G}$  com :  $10\Omega$  d/ $_{D}$ /dt : 3.5A/ns (e)  $R_{G}$ \_com : 47 $\Omega$  d $I_{D}$ /dt : 4.0A/ns (f)  $R_G$ \_com :  $100\Omega$  d $I_D$ /dt : 2.0A/ns

Figure 5-12. h 파형 ( $R_{G}$ com 감소)

R<sub>G</sub>\_com 이 작을수록 Gate OFF 시의 d/₀/dt 는 커지고, 스위칭 스피드가 빨라 발진이 발생합니다. 이번 평가 기판에서는  $4.7~\Omega$  이상(MOSFET 하나당  $d_h/dt$ 6.4A/ns 이하)이 되면 발진을 억제할 수 있음을 알 수 있습니다. 이를 통해, d/b/dt 의 영향을 크게 받음을 알 수 있습니다.

# C': 개별 Gate 저항 $R_G$ \_Q1, $R_G$ \_Q2 를 불균형적으로 함

$R_{G_{-}}Q1$  와  $R_{G_{-}}Q2$  를 불균형적으로 하여 실시했습니다. 평가항목 C'의 평가조건은 다음과 같습니다.

Љ, pulse : 128A (합계 256A)

기생 L: 기판의 인덕턴스(Table 5-1)만

$V_{GS(th)}$ \_Q1,  $V_{GS(th)}$ \_Q2: 4.2V

$R_{G_{-}}$ Q1 과  $R_{G_{-}}$ Q2,  $R_{G_{-}}$ com 을 아래 (a) ~ (c)의 조건으로 했을 때, Gate OFF 시의 V<sub>GS</sub>\_LS\_Q1 파형을 Figure 5-13 에 나타냅니다. 조건(a)에서는  $R_{G}$ com 을  $0\Omega$ 으로 비교해야 하지만, Gate 저항의 합계가  $0\Omega$ 인 경우,  $V_{DS}$  가 정격을 초과하므로, 2Ω으로 했습니다.

(a)  $R_{G}$ \_com :  $2\Omega$   $R_{G}$ \_Q1 :  $0\Omega$   $R_{G}$ \_Q2 :  $0\Omega$ (b)  $R_{G}$ \_com :  $0\Omega$   $R_{G}$ \_Q1 :  $0\Omega$   $R_{G}$ \_Q2 :  $10\Omega$ (c)  $R_{G}$ \_com :  $0\Omega$   $R_{G}$ \_Q1 :  $0\Omega$   $R_{G}$ \_Q2 :  $100\Omega$

Figure 5-13.  $V_{GS}$  파형 (개별  $R_{G}$  불균형)

개별 RG의 불균형이 클수록 발진이 오래 지속되는 것처럼 보이지만, 조건(c)에서는 발진 수렴 속도만 느려질 뿐, 조건(c)와 조건(b)에서는 발진 진폭에 큰 차이가 없습니다. 한편, 조건(a)와 조건(b)에서는 발진 진폭의 차가 크고, 개별 Gate 저항이 불균형하게 되는 것이 발진 진폭을 크게 하게 됩니다. 다만, 일반적으로 Gate 저항이 10Ω이나 불균형하게 되는 경우는 없습니다. 이 결과는 Gate OFF 타이밍이 어긋나면 발진 진폭이 커지는 것을 나타냅니다.

#### D': V<sub>GS(th)</sub>를 Q1, Q2 로 불균형적으로 함

하여 평가를 V<sub>GS(th)</sub>를 불균형적으로 실시했습니다. 평가항목은 D'의 평가조건은 아래와 같습니다. 발진을 보다 쉽게 관측하기 위하여, 개별 Gate 저항은 0Ω으로 했습니다.

/<sub>D, pulse</sub>: 128A (합계 256A)

기생 L: 기판의 인덕턴스(Table 5-1)만

$R_{\rm G}$  com :  $2\Omega$

$R_{G}$ Q1,  $R_{G}$ Q2: 0 $\Omega$

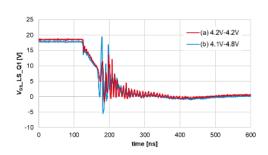

$V_{GS(th)}$ 을 아래의 (a)(b) 조건으로 했을 때, Gate OFF 시의 V<sub>GS</sub>\_LS\_Q1 파형을 Figure 5-14 에 나타냅니다.

(a)  $V_{GS(th)}$ \_Q1 : 4.2V  $V_{GS(th)}$ \_Q2 : 4.2V (b)  $V_{GS(th)}Q1: 4.1V V_{GS(th)}Q2: 4.8V^{*2}$

\*2 : 동일 Lot 내 MOSFET 의  $V_{GS(th)}$ 가 0.7V 편차를 나타내고 있는 데이터는 아닙니다.

Figure 5-14. V<sub>GS</sub> 파형 (V<sub>GS(th)</sub> 불균형)

$V_{GS(th)}$ 가 다르면, Gate OFF 타이밍이 어긋나기 때문에, 발진 진폭은 커진다는 것을 알 수 있는데, 이번 평가 조건에서는  $R_{\rm G}$ Q1,  $R_{\rm G}$ Q2 가 0  $\Omega$  이었기 때문이며, 적절한  $R_{\rm G}$ Q1,  $R_{G_-}$ Q2 를 설정함으로써  $V_{GS(th)}$ 의 편차에 의한 발진은 억제할 수 있습니다.

#### E': 기생 용량을 Q1, Q2 로 불균형적으로 함 (시뮬레이션)

본 평가 항목은 샘플을 입수하기 어렵기 때문에, 시뮬레이션으로 평가를 실시했습니다. 평가항목 E'의 평가조건은 아래와 같습니다. 시뮬레이션 상에서는 ,  $R_{G_{-}}Q1$ ,  $R_{\rm G}$ \_Q2 을  $0\Omega$ 으로 하면 발진이 수렴하지 않으므로, 이번에는 2Ω으로 하여 시뮬레이션을 실시했습니다.

/<sub>D. pulse</sub>: 128A (합계 256A)

기생 L: 기판의 인덕턴스(Table 5-1)를 참조

$R_{G}$ \_com :  $2\Omega$

$R_{G}$ Q1,  $R_{G}$ Q2: 2 $\Omega$

#### E'-1 : C<sub>GD</sub>를 Q1, Q2 로 불균형적으로 함

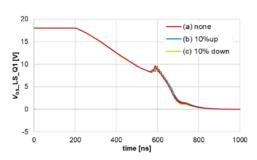

$C_{GD}$ - $V_{DS}$  곡선을 시뮬레이션 상에서 이동시켰습니다. 아래의 (a) ~ (c) 조건으로 했을 때, Gate OFF 시의 V<sub>GS\_</sub>LS\_Q1 파형을 Figure 5-15 에 나타냅니다.

(a)  $C_{GD}$ Q1 : 변경 없음 CGD\_Q2: 변경 없음

(b) Q1의  $C_{GD}$  절대치를 크게 함

$C_{GD}$ Q1 :  $C_{GD}$  curve 를 10% 고용량 쪽으로 이동

CGD Q2: 변경 없음

(c) Q1의  $C_{GD}$  절대치를 작게 함

$C_{GD}$ Q1 :  $C_{GD}$  curve 를 10% 저용량 쪽으로 이동

C<sub>GD\_</sub>Q2 : 변경 없음

Figure 5-15. V<sub>GS</sub> 파형 (C<sub>GD</sub> 불균형)

조건(c)는  $C_{GD}$  가 불균형이 됨에 따라 Gate OFF 타이밍이 어긋나고, 게다가 Q1 의  $C_{GD}$  절대치가 작기 때문에 발진하고 있다고 생각합니다. 특히  $C_{GD}$ 의 절대치가 작은 칩 사이즈의 작은 디바이스를 사용할 때는 주의가 필요합니다. 단, 본 결과는 시뮬레이션이며, 실제로 발진이 발생한 것을 보여주는 결과는 아닙니다.

#### E'-2 : CGS 를 Q1, Q2 로 불균형적으로 함

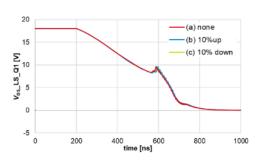

마찬가지로  $C_{GS}$ - $V_{DS}$ 곡선을 시뮬레이션 이동시켰습니다. 아래의 (a)~(c) 조건으로 했을 때의 Gate OFF 시의 V<sub>GS\_</sub>LS\_Q1 파형을 Figure 5-16 에 나타냅니다.

(a) C<sub>GS</sub>\_Q1: 변경 없음 CGS\_Q2: 변경 없음

(b) Q1의  $C_{GS}$  절대치를 크게 함

$C_{GS}$ \_Q1 :  $C_{GS}$  curve 를 10% 고용량 쪽으로 이동

*C*<sub>GS\_</sub>Q2 : 변경 없음

(c) Q1의  $C_{GS}$  절대치를 작게 함

$C_{GS}$ \_Q1 :  $C_{GS}$  curve 를 10% 저용량 쪽으로 이동

CGS\_Q2: 변경 없음

Figure 5-16. V<sub>GS</sub> 파형 (C<sub>GS</sub> 불균형)

$C_{GS}$ 를 불균형하게 해도 발진 진폭은 변화가 없습니다. 다만, 본 결과는 시뮬레이션이며, 실제로 발진이 발생하지 않는다는 것을 보여주는 결과는 아닙니다.

#### E'-3: C<sub>DS</sub>를 Q1, Q2로 불균형적으로 함

마찬가지로  $C_{\rm DS}$ - $V_{\rm DS}$ 곡선을 시뮬레이션 상에서 이동시켰습니다. 아래의 (a)~(c) 조건으로 했을 때의 Gate OFF 시의 V<sub>GS\_</sub>LS\_Q1 파형을 Figure 5-17 에 나타냅니다.

(a)  $C_{DS}$ Q1 : 변경 없음 CDS\_Q2: 변경 없음

(b) Q1 의 C<sub>DS</sub> 절대치를 크게 함

C<sub>DS</sub>\_Q1 : C<sub>DS</sub> curve 를 10% 고용량 쪽으로 이동

CDS\_Q2: 변경 없음

(c) Q1 의 C<sub>DS</sub> 절대치를 작게 함

C<sub>DS</sub>\_Q1 : C<sub>DS</sub> curve 를 10% 저용량 쪽으로 이동

CDS\_Q2: 변경 없음

Figure 5-17. V<sub>GS</sub> 파형 (C<sub>DS</sub> 불균형)

Cps 를 불균형하게 해도 발진 진폭은 변화가 없습니다. 다만, 본 결과는 시뮬레이션이며, 실제로 발진이 발생하지 않는다는 것을 보여주는 결과는 아닙니다.

이번에는 10%의 편차로 조사를 했지만, 동일 Lot 내 MOSFET 의  $V_{GS(th)}$ 가 0.7V 편차를 나타내고 있는 데이터는 아닙니다. 다만, 가능한 한 Q1, Q2 는 동일 Lot 내의 MOSFET 를 사용하는 것이 바람직합니다. 또한, 실제의  $C_{GD}$ ,  $C_{GS}$ ,  $C_{DS}$  불균형은 복합적으로 일어날 가능성이 있습니다.

이번 시뮬레이션에서는 Spice 모델을 조작하여, 기생 용량을 조작하여 변경했습니다. 아래 Statement 의 X 에 배율을 넣는 것에 의해 기생 용량의 curve 를 증감시킬 수 있습니다. 상세한 모델에 대한 설명은 애플리케이션 노트「열 모델의 확인해 주세요. 단, 시뮬레이션이므로 정확한 발진 여부의 판단으로서 사용하는 것은 삼가 주십시오.

#### 예)SCT4018KR

$C_{GD}$ : C1 23 12 1p  $\rightarrow$  C1 23 12 {1p\***X**}

$C_{GS}$ : C2 22 33 4.857n  $\rightarrow$  C2 22 33 {4.857n\***X**}

$C_{DS}$ : C11 53 1 1p  $\rightarrow$  C11 53 1 {1p\***X**}

상세한 모델은 아래의 링크를 참고해 주세요. SCT4018KR 시뮬레이션 모델 (rohm.com)\*2

\*2: 2023/5/30 현재 모델

발진 평가 결과를 Table 5-2 에 나타냅니다. 「Gate 전압 진폭차」는 가장 발진하는 조건의 발진 진폭의 최댓값에서 가장 발진하지 않은 조건의 발진 진폭의 최댓값을 뺀 것입니다. 이 값이 큰 요인일수록 대책이 필요하다는 것을 나타냅니다.

Table. 5-2

| 요인 | 평가 항목 번호 | 평가 항목                   | V <sub>GS</sub> 진폭차 [V] |

|----|----------|-------------------------|-------------------------|

| Α  | A'-1     | L <sub>D</sub> 불균형      | 0.2                     |

| Α  | A'-2     | L <sub>s</sub> 불균형      | 12.0                    |

| Α  | A'-3     | L <sub>G</sub> 불균형      | 6.2                     |

| Α  | A'-4     | L <sub>KS</sub> 불균형     | 39.9                    |

| В  | B'-1     | I <sub>D</sub> 의 증가     | 6.0                     |

| В  | B'-2     | 공통 R <sub>G</sub> 감소    | 11.0                    |

| С  | C'       | 개별 R <sub>G</sub> 불균형   | 9.9                     |

| D  | D'       | V <sub>GS(th)</sub> 불균형 | 5.6                     |

| E  | E'-1     | C <sub>GD</sub> 불균형     | 6.0                     |

| E  | E'-2     | C <sub>GS</sub> 불균형     | 0.2                     |

| E  | E'-3     | C <sub>DS</sub> 불균형     | 0.2                     |

이 결과로부터, 요인 A의  $L_{S}$ ,  $L_{KS}$  불균형이 발진에 가장 큰 영향을 준다는 것을 알 수 있고,  $L_S$ ,  $L_{KS}$  는 가능한 한 같은 길이로 설계하는 것이 최우선이 됩니다. 또한, 동일한 값의  $R_{G_-}Q1$ ,  $R_{G_-}Q2$  를 두고,  $R_{G_-}com$  를 추가로 두는 것이 중요합니다. D, E 에 대해서는 MOSFET 의 특성이므로, 기판 설계에 있어서 대책을 세울 수 없습니다. 그러므로, A~C 회로상의 요인을 기판 설계에서 충분히 고려하는 것이 중요합니다.

# 6.발진대처법 검증

발진 요인 A~C를 개선하는 대처법을 3 가지, 그 밖의 회로설계에 의한 대처법을 2 가지, 총 5 가지의 발진 대처법에 대해 실제로 발진이 억제되는지 검증했습니다. 설계 단계에서 확인하는 것이 중요하지만, 설계 완료 후의 검증 단계에서 발진이 출현한 경우에도 사용할 수 있는 대처법입니다.

대처법은 아래의 I~V 입니다.

#### 발진 요인 A~C를 개선하는 대처법

- I.  $L_{S}(L_{KS})$ 를 같은 길이로 한다

- II.  $R_{G_{-}}$ com 를 증가시킨다

- III.  $R_{G}$ Q1,  $R_{G}$ Q2 를 증가시킨다

#### 그 밖의 회로 설계에 의한 대처법

- IV. 칩 페라이트 비드를 게이트 라인에 추가한다

- V. 외장 *C*<sub>GS</sub>를 추가한다

발진 평가의 조건은 「4.발진 평가 항목」에 나타내는 바와 같습니다.

#### I. $L_{s}(L_{ks})$ 를 같은 길이로 한다

「5.발진 평가 결과」의 요인 A 로부터  $L_S$ ,  $L_{KS}$ 의 불균형이 발진에 영향을 주는 것으로 판명되었습니다.  $L_S$ ,  $L_{KS}$ 는 실제로 같은 전위이기 때문에, 파워라인인  $L_S$ 를 같은 길이로 하는 검증을 실시했습니다.  $L_S$ 의 추출 결과는

$L_{S}Q1 : 10.7nH$  $L_{S}Q2 : 16.2nH$

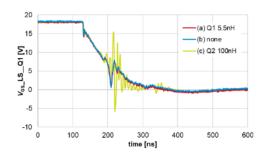

이므로, 조건(a)는 같은 길이로 하기 위해,  $L_{S_{-}}$ Q1 에 5.5nH 를 추가했습니다. Figure 6-1 에 추가한 배선의 상태를 나타냅니다. 조건(c)에서는 조건(a)와 비교하기 위해, 「5.발진 평가 결과 A': 기생 L 을 Q1, Q2 로 불균형적으로 함」으로부터, Figure 5-4. 기생 L 추가 조건(d)와 마찬가지로  $L_{S_{-}}$ Q2 에 100nH 를 추가하였습니다.

- (a) Q1 에 5.5nH 추가 (같은 길이)

- (b) 추가 없음

- (c) Q2 에 100nH 추가

Figure 6-1. 기생 L 추가 (a)

아래의 조건으로 평가를 실시했습니다.

Љ. pulse : 128A (총합 256A)

$R_{G}$ Q1,  $R_{G}$ Q2: 2 $\Omega$

$R_{G}$ \_com :  $2\Omega$

$V_{GS(th)}$ \_Q1,  $V_{GS(th)}$ \_Q2: 4.2V

$R_{G_{-}}Q1$ ,  $R_{G_{-}}Q2$  는 「5.발진 평가 결과」가 나타내듯이, 발진 대책에서 필요한 조건이 되었기 때문에  $2\Omega$ 으로 했습니다. 기생 L 을 (a) $\sim$ (c)의 조건으로 했을 때의 Gate OFF 시의  $V_{GS}$  LS Q1 파형을 Figure 6-2 에 나타냅니다.

Figure 6-2.  $V_{GS}$  파형 ( $L_{S}$  같은 길이)

$R_{G_-}Q1$ ,  $R_{G_-}Q2$  를 넣는 것을 전제로 하여,  $L_S$ 를 같은 길이에 가깝게 하면 발진을 억제할 수 있음을 알 수 있습니다. 그러나, 차이가 5nH 인 경우와 0nH 인 경우에는 파형에 큰 변화가 없기 때문에, 이번 조건에서는 5nH 정도의 차이는 허용될 수 있음을 알 수 있습니다.

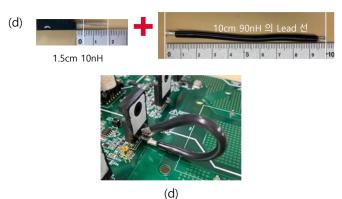

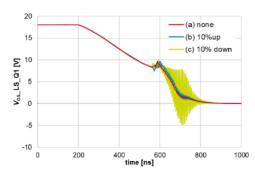

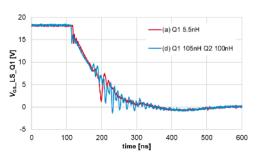

다음으로 조건(d)에서는  $L_S$ 가 같은 길이인 채,  $L_S$ 의 절대치를 길게 하여 검증했습니다. Q1, Q2 의 양쪽에 약 90nH 의 추가  $L_S$ 를 달았습니다. Figure 6-3 에 배선의 추가 상태를 나타냅니다.

- (a) Q1 에 5.5nH 추가(같은 길이, 짧다)

- (d) Q1 에 105nH 추가, Q2 에 100nH 추가(같은 길이, 길다)

Figure 6-3. 기생 L 추가 (d)

기생 L 을 (a), (d)의 조건으로 했을 때, Gate OFF 시의  $V_{GS}$ \_LS\_Q1 파형을 Figure 6-4 에 나타냅니다.

Figure 6-4. V<sub>GS</sub> 파형 (L<sub>S</sub> 같은 길이, 장단 비교)

조건(a)와 조건(d)를 비교하면 절대치가 큰 조건 (d)의 파형은 발진이 발생하고 있습니다. 이 점으로부터,  $L_S$ 를 같은 길이로 하여 가능한 한 짧게 배치할 필요가 있습니다. 그러나 Figure 6-2 의 조건(c)와 비교하면 발진의 정도가 작은 것으로부터,  $L_S$ 의 절대치는 다소 크더라도 같은 길이로 하는 것이 최우선임을 알 수 있습니다.

## II. $R_{G}$ com 을 증가시키다

「5.발진 평가 결과」 요인 B 의 평가항목 B'-2 으로부터,  $R_{G_C}$ com 을 키우면 발진이 억제되는 것으로 나타났습니다. 다만, 스위칭 손실이 증가하므로, 시스템 효율이나 발열 등을 충분히 고려한 후에 선정할 필요가 있습니다.

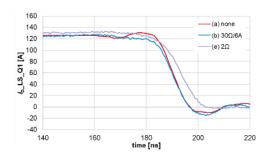

#### III. $R_{G_{-}}Q1$ , $R_{G_{-}}Q2$ 를 증가시키다

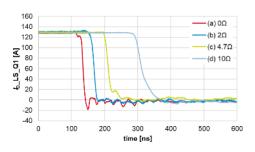

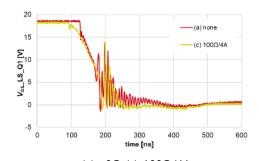

II 로부터  $R_{G\_}$ com 를 증가시킴으로써 발진은 억제할 수 있지만,  $R_{G\_}$ Q1, Q2 를 키우는 것도 가능합니다.  $R_{G\_}$ Q1, Q2 를 아래의 (a)  $\sim$  (d)의 조건으로 했을 때의 Gate OFF 시의  $V_{GS\_}$ LS\_Q1 파형을 Figure 6-5 에 나타냅니다.

/<sub>D. pulse</sub>: 128A (총합 256A)

$R_{G}$ \_com :  $2\Omega$

$V_{GS(th)}$ \_Q1,  $V_{GS(th)}$ \_Q2: 4.2V

기생 L : 기판의 인덕턴스(Table 5-1)만

(a)  $R_{G}$ Q1,  $R_{G}$ Q2: 0 $\Omega$ (b)  $R_{G}$ Q1,  $R_{G}$ Q2: 2 $\Omega$ (c)  $R_{G}$ Q1,  $R_{G}$ Q2: 4.7 $\Omega$ (d)  $R_{G}$ Q1,  $R_{G}$ Q2: 10 $\Omega$

Figure 6-5. V<sub>GS</sub> 파형 (R<sub>G</sub>\_Q1, Q2 증가)

$R_{G_-}Q1$ , Q2 를 증가시킴으로써 발진을 억제하는 것이 가능하다는 것을 알 수 있습니다. 다만,  $\lceil B'-2 \mid$  공통 게이트 저항  $R_{G_-}com$  을 낮춤」보다,  $R_{G_-}com$  를 증가시킴으로써 스위칭 스피드가 느려지고, 보다 발진 억제에 효과가 있기 때문에,  $R_{G_-}com$ 을 크게 하고,  $R_{G_-}Q1$ , Q2는  $2\Omega$  정도가 이번 평가 조건에서는 최적이었습니다.

#### Ⅳ. 칩 페라이트 비드를 게이트 라인에 추가한다

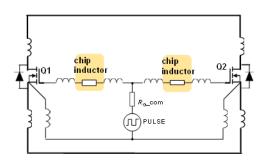

이어지는 대처법은 칩 페라이트 비드를 이용하는 방법입니다. 칩 페라이트 비드는 게이트 구동 라인에 직렬로 넣음으로써 노이즈를 억제할 수 있습니다. Figure 6-6 에 회로도를 나타냅니다. 이번 평가에서는 실장 패턴을 마련하지 않았기 때문에,  $R_{G_{-}}$ Q1, Q2 의 패턴으로 대체했습니다. Figure 6-7 에 칩 페라이트 비드 실장도를 나타냅니다.

Figure 6-6. 칩 페라이트 비드 실장 회로

Figure 6-7. 칩 페라이트 비드 실장

평가 조건은 다음과 같습니다.

/<sub>D, pulse</sub>: 128A (총합 256A)

$R_{G}$ \_com :  $2\Omega$

$V_{GS(th)}$ \_Q1,  $V_{GS(th)}$ \_Q2 : 4.2V

기생 L: 기판의 인덕턴스(Table 5-1)만

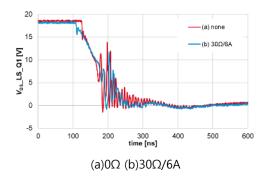

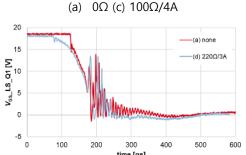

이번 개별 게이트 저항의 랜드 패턴에 아래  $(b) \sim (d)$ 의 칩 페라이트 비드를 붙였을 때, Gate OFF 시의  $V_{GS\_LS\_Q1}$  파형을 Figure 6-8 에 나타냅니다. 사용한 칩 페라이트 비드는 하기  $(b) \sim (d)$ 의 TDK 제품입니다.

(a)  $R_{\rm G}$ \_Q1,  $R_{\rm G}$ \_Q2 : 칩 페라이트 비드 없음  ${\sf MCR18EZPJ000}(0\Omega~{\sf 저항})$

(b)  $R_{\rm G}$ \_Q1,  $R_{\rm G}$ \_Q2 : MPZ2012S300ATD25(30 $\Omega$ /6A) (c)  $R_{\rm G}$ \_Q1,  $R_{\rm G}$ \_Q2 : MPZ2012S101ATD25(100 $\Omega$ /4A) (d)  $R_{\rm G}$ \_Q1,  $R_{\rm G}$ \_Q2 : MPZ2012S221ATD25(220 $\Omega$ /3A)

(a)  $0\Omega$  (d)  $220\Omega/3A$  Figure 6-8.  $V_{GS}$  파형 (칩 페라이트 비드 추가)

이 결과를 통해, (b)의 칩 페라이트 비드가 발진 억제에 효과가 있음을 알 수 있습니다.

칩 페라이트 비드에는 정격 전류가 있으며, 이번 평가에서는  $C_{iss}=1000$  F당 1A 정도로 선정하여, 실기에 의한 게이트 신호의 충방전 전류를 측정한 후에 결정했습니다. 이번에 사용한 SCT4018KR 의 경우,  $C_{iss}=4532$  pF 이었기 때문에, 결과적으로 5A 이상인 것이 적합합니다. 또한, 주파수 특성에도 주의하여, 발진 주파수 대역에서 수  $\Omega$ 이상의 임피던스를 갖는 것을 선정합니다. 다만, 칩 페라이트 비드를 삽입하면, 특정 주파수에서  $V_{GS}$  서지가 증가할 가능성이 있습니다. 이번에는 게이트 OFF 파형에 포커스 하여, 발진 억제에 효과가 있는 것을 보였습니다만, 반드시  $V_{GS}$  파형 전체를 확인하여 서지가 정격을 초과하고 있지 않은지를 확인해 주세요.

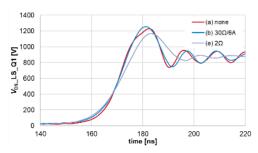

「 $III.R_{G_-}Q1$ ,  $R_{G_-}Q2$  를 증가」의 대책과 비교하면, 발진 억제 효과는 적게 보이지만 메리트도 있습니다. 게이트 OFF 시의  $V_{DS_-}LS_-Q1$  파형을 Figure 6-9 에,  $V_{D_-}LS_-Q1$  파형을 Figure 6-10 에 나타냅니다.

(a) R<sub>G</sub>\_Q1, R<sub>G</sub>\_Q2 : 칩 페라이트 비드 없음

MCR18EZPJ000 (0Ω 저항)

(b)  $R_{G}$ Q1,  $R_{G}$ Q2 : MPZ2012S300ATD25(30 $\Omega$ /6A)

(e) R<sub>G\_</sub>Q1, R<sub>G\_</sub>Q2 : 칩 페라이트 비드 없음

MCR18EZPJ2R0(2Ω 저항)

Figure 6-9. V<sub>DS</sub> 파형 (칩 페라이트 비드와 R<sub>G</sub> 비교)

Figure 6-10. ₺ 파형 (칩 페라이트 비드와 R<sub>G</sub> 비교)

V<sub>DS</sub> 파형을 비교하면 dV<sub>DS</sub>/dt 에 있어서 조건(a)와 (b)는 거의 변하지 않고, 조건(e)에서는 dV<sub>DS</sub>/dt 가 완만하게 되어 있습니다. 게다가, d√b/dt 에 있어서도 조건(a)와 (b)에서는 거의 변하지 않았지만, 조건(e)에서는 완만하게 되어 있습니다. 조건(b)에서는 dV<sub>DS</sub>/dt 나 d√b/dt 가 저하되지 않고, 발진 진폭을 억제할 수 있기 때문에, 스위칭 손실 증가의 우려가 없습니다. 스위칭으로 인한 손실이 중요한 경우는 게이트 저항 대책에 덧붙여 칩 페라이트 비드에 의한 대책을 추가함으로써 게이트 저항 증가로 인한 손실과 발진 억제의 균형을 맞출 수 있습니다.

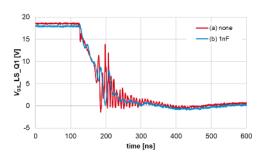

#### V. 외장 *C*<sub>GS</sub>를 추가한다

마지막으로 외장  $C_{GS}$ 를 추가하는 대책에 대해 소개합니다. MOSFET 의 기생용량  $C_{GS}$  와는 별도로 Gate – Source 간에 추가 용량을 디스크리트로 넣어 스위칭 속도를 저감 하고, 발진을 억제할 수 있습니다. 외장  $C_{GS}$ 를 추가할 때, Gate OFF 시의  $V_{GS}$ \_LS\_Q1 파형을 Figure 6-10 에 나타냅니다.

/<sub>D. pulse</sub>: 128A (총합 256A)

$R_{G}$ \_com :  $2\Omega$

$R_{G}$ Q1,  $R_{G}$ Q2: 0 $\Omega$

$V_{GS(th)}$ \_Q1,  $V_{GS(th)}$ \_Q2: 4.2V

기생 L: 기판의 인덕턴스(Table 5-1)만

- (a) 외장 C<sub>GS</sub> 없음

- (b) 외장  $C_{GS} = 1nF$

Figure 6-11. V<sub>GS</sub> 파형 (외장 C<sub>GS</sub> 추가)

Figure 6-11 으로부터 외장  $C_{GS}$ 로 발진을 억제할 수 있음을 알 수 있습니다.

마지막으로 발진 대처법의 결과를 Table 6-1 에 정리하였습니다. 게이트 전압 진폭차에서는 대책 전 파형의 발진 진폭 최대치와 가장 발진을 억제할 수 있었던 조건의 발진 진폭을 뺀 값입니다. 이 값이 클수록, 이번 평가에서 효과 있는 대책이 되어,  $R_{G_c}$ com 를 추가시키는 것이 가장 효과적이었습니다.

Table. 6-1

|    | 대처법                                       | V₀s진폭차[V] | 단점                  |

|----|-------------------------------------------|-----------|---------------------|

| I  | $L_{\rm S}$ 를 같은 길이 (짧고, 같게)              | 7.9       | 없음                  |

| I  | $L_{\rm S}$ 를 같은 길이 (길고, 같게)              | 6.1       | 없음                  |

| I  | R <sub>G</sub> _com를 증가                   | 11.0      | 스위칭 손실 증가           |

| Ш  | R <sub>G_</sub> Q1,R <sub>G_</sub> Q2를 증가 | 7.8       | 스위칭 손실 증가           |

| IV | 칩 페라이트 비드를 게이트 라인에 추가                     | 2.0       | 발진 주파수 이외 V GS서지 증가 |

| ٧  | 외장 C <sub>GS</sub> 추가                     | 6.3       | 스위칭 손실 증가           |

병렬접속 시에 발진이 일어났을 경우에는 우선 억제에 대한 효과가 크고, 단점이 없는  $L_S$ 를 같은 길이로 하고, 가능한 한 짧게 하는 것이 중요합니다. 그래도 발진을 억제할 수 없는 경우에는 단점에 주의하면서 대책을 실시합니다.

칩 페라이트 비드를 게이트 라인에 삽입하는 대책으로는 발진 억제에 대한 효과는 적지만, 발진 주파수에서 서지를 저감 할 수 있는 대책으로 노이즈 억제에 효과적인 대책입니다.

# 7.결론

병렬접속 시에 특히 주의할 점은 아래의 3 가지입니다.

- L<sub>S</sub>, L<sub>KS</sub> 불균형이 가장 발진에 큰 영향을 미칩니다. L<sub>S</sub>,

L<sub>KS</sub>는 가능한 한 같은 길이가 되는 것을 최우선으로 설계한다. (Figure 7-1 참조)

- 같은 값의  $R_{G_-}Q1$ ,  $R_{G_-}Q2$  를 사용하고,  $R_{G_-}com$  를 추가로 사용한다 (Figure 7-1 참조)

- 그런데도 발진이 출현하는 경우에는 칩 페라이트 비드나 C<sub>GS</sub> 등의 외장 대책 부품을 추가한다.

발진 현상을 올바르게 이해하고, 최적의 회로 설계를 실시함으로써 게이트 발진을 충분히 억제하는 것이 가능합니다. 만일, 병렬 발진이 일어났을 때에는 상기의 대처법을 시험하여, MOSFET 의 정격 내에서 동작하도록 조정하고 안전하게 사용해 주십시오.

Figure 7-1. 병렬접속 시에 주의할 파라미터

#### 참고 자료 :

- [1] 「Gate Source 전압 측정 시의 주의점」 애플리케이션 노트(No. 63AN046K Rev.002) 로옴주식회사, 2020 년 9 월

- [2] 「열 모델의 사용 방법」 애플리케이션 노트(No. 63AN006K Rev.001) 로옴주식회사, 2020 년 2 월

Tektronix®는 Tektronix, Inc. 의 등록 상표입니다. Ansys® 및 Q3D Extractor® 는 ANSYS, Inc. 의 등록 상표입니다.。 누 E

- 1) 본 자료의 기재 내용은 로옴 그룹 (이하, 「로옴」) 제품 소개를 목적으로 합니다. 로옴 제품 사용 시에는, 별도로 최신 데이터시트 또는 사양서를 반드시 확인하여 주십시오.

- 2) 로옴 제품은 일반적인 전자기기 (AV 기기, OA 기기, 통신기기, 가전제품, 오락기기 등) 또는 데이터시트에 명시되어 있는 용도로 사용하는 것을 의도하여 설계ㆍ제조되어 있습니다. 따라서, 매우 고도의 신뢰성이 요구되고, 고장 및 오동작이 인명, 신체에 대한 위험 또는 손해, 또는 기타 중대한 손해의 발생으로 이어지는 기기 또는 장치 (의료기기, 수송기기, 교통기기, 항공우주기기, 원자력 제어 장치, 연료 제어, 자동차 액세서리를 포함한 자동차기기, 각종 안전 장치 등) (이하, 「특정 용도」)에 로움 제품의 사용을 검토하는 경우, 사전에 로옴 영업으로 상담하여 주십시오. 로옴의 문서에 의한 사전 승낙 없이 특정 용도에 로옴 제품을 사용함에 따라 고객 또는 제3자에게 발생한 손해 등에 대해 로옴은 일절 책임을 지지 않습니다.

- 3) 반도체를 포함하는 전자부품은 일정한 확률로 오동작이나 고장이 발생하는 경우가 있습니다. 만일의 경우 오동작이나 고장이 발생하더라도, 인명, 신체, 재산에 대한 위험 또는 손해가 발생하지 않도록 고객의 책임 하에 Fail-safe 설계 등 안전 대책을 실시하여 주십시오.

- 4) 본 자료에 기재된 응용 회로 예나 정수 등의 정보는, 로옴 제품의 표준적인 동작이나 사용 방법을 설명하기 위한 것으로, 실제로 사용하는 기기에서의 동작을 명시적으로나 묵시적으로 보증하는 것은 아닙니다. 따라서, 고객의 기기 설계에 있어서, 회로나 정수 및 관련 정보를 사용하는 경우에는 외부 제반 조건을 고려하여 고객의 판단과 책임하에 실시하여 주십시오. 이러한 정보의 사용으로 기인하여 고객 또는 제3자에게 발생한 손해에 대해 로옴은 일절 책임을 지지 않습니다.

- 5) 로옴 제품 및 본 자료에 기재된 기술을 수출 또는 국외에 제공하는 경우에는, 「외국 외환 및 외국 무역법」, 「미국 수출 관리 규정」 등 적용되는 수출 관련 법령을 준수하여 필요한 절차에 따라 실시하여 주십시오.

- 6) 본 자료에 기재된 응용 회로 예 등 기술 정보 및 관련 데이터는 어디까지나 일례를 나타낸 것으로, 이에 관련된 제3자의 지적재산권 및 기타 권리에 대해 권리 침해가 없음을 보증하는 것은 아닙니다. 또한, 로옴은 본 자료에 기재된 정보에 대해 로옴 또는 제3자가 소유 또는 관리하고 있는 지적재산권 및 기타 권리의 실시, 사용 또는 이용을 명시적이나 묵시적으로 고객에게 허락하는 것은 아닙니다.

- 7) 본 자료의 전부 또는 일부를 로옴의 문서에 의한 사전 승낙 없이 전재 또는 복사하는 행위는 금지합니다.

- 8) 본 자료에 기재된 내용은 본 자료 발행 시점의 내용이며, 예고 없이 변경되는 경우가 있습니다. 로옴 제품의 구입 및 사용 시에는 사전에 로옴 영업에 최신 정보를 확인하여 주십시오.

- 9) 로옴은 본 자료에 기재된 정보에 오류가 없음을 보증하지 않습니다. 만일 본 자료에 기재된 정보의 오류로 인해고객 또는 제3자에게 손해가 발생한 경우, 로옴은 일절 책임을 지지 않습니다.

Thank you for your accessing to ROHM product informations. More detail product informations and catalogs are available, please contact us.

# ROHM Customer Support System

https://www.rohm.co.kr/contactus