SIC MOSFET

# Snubber Circuit Design Methods

최근, SiC MOSFET은 다양한 전원 애플리케이션이나 전력 라인의 스위칭 소자로서 급격히 사용이 가속화되고 있습니다. 이는 기존의 파워반도체와 비교하여 고속 스위칭 동작이 가능해진 것이 하나의 이유이지만, 고속 스위칭 시의 전압이나 전류가 급변함에 따른 디바이스 자체의 패키지 인덕턴스와 주변회로의 배선 인덕턴스의 영향을 무시할 수 없게 되어 결과적으로 드레인-소스 간에 큰 서지가 발생합니다. 이 서지는 사용하는 MOSFET 의 최대정격을 넘지 않도록 해야 하며 다양한 억제 방법이 있습니다. 거기서, 이 애플리케이션 노트에서는, 드레인-소스간의 서지 억제 방법의 하나인 Snubber Circuit의 설계 방법에 대해 설명하겠습니다.

### Drain-Source 사이에 발생하는 서지

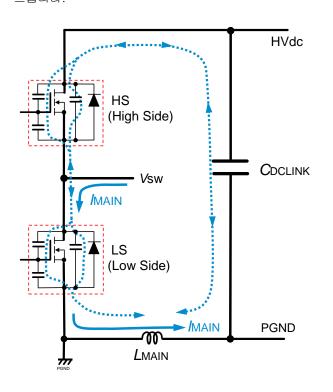

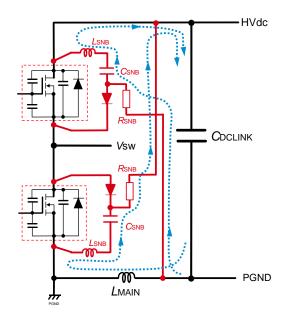

드레인-소스간에 발생하는 서지는 턴-온 시에 흐른 전류의 에너지, 배선이나 기판 패턴의 인덕턴스에 축적된 상태로 되어 있어 그 에너지가 스위칭 디바이스의 기생용량과 공진함으로써 발생합니다. Figure 1.은 서지 발생시 전류의 경로에 대한 설명입니다. 이 그림에서는 High 측(HS)과 Low 측(LS)에 스위칭 디바이스가 접속되는 브리지 구성으로, LS 디바이스가 턴-온하고, 스위칭 전류 MAIN 이 흘렀을 경우를 나타내고 있습니다. 이 IMAIN 은 보통 Vsw 에서 유입되어 배선 인덕턴스 ZMAIN 를 통해 흐릅니다.

Figure 1. 턴온 서지 발생 시 전류 경로

다음으로 LS 디바이스가 턴-오프되었을 때 LMAIN 에 흐

르고 있던 IMAIN 이 보통 입력전원 HVdc-PGND 간에 연결되어 있는 벌크용 콘덴서 CDCLINK 를 통해 HS 디바이스와 LS 디바이스의 기생용량을 경유하여 점선과 같이 흐릅니다. 이때 LS 측 드레인-소스 간에 LMAIN 와 MOSFET의 기생용량 Coss(CDs+CDg)에 의한 공진 현상이일어나며, 드레인-소스 사이에 서지가 발생합니다. 그서지의 최대치 VDS\_SURGE는 HVdc 단자에 인가되는 전압을 VHVDC, MOSFET 가 턴-오프 할 때의 저항을 ROFF 라 하면 아래의 식으로 나타납니다\*1.

$$V_{\text{DS\_SURGE}} = \frac{V_{\text{A}} * e^{-(a/\omega)[\tan^{-1}(a/\omega) + \phi]}}{1 + (a/\omega)^{2}} + V_{\text{HVDC}}$$

(1)

$$V_{\text{A}} = \sqrt{V_{\text{HVDC}}^{2} + (a/\omega)^{2} * \left(2 * R_{\text{OFF}} * I_{\text{MAIN}} - V_{\text{HVDC}}\right)^{2}}$$

$$\phi = tan^{-1} \frac{V_{\text{HVDC}}}{(a/\omega) * (2 * R_{\text{OFF}} * I_{\text{MAIN}} - V_{\text{HVDC}})}$$

$$a = \frac{1}{2 * R_{\text{OFF}} * C_{\text{OSS}}}$$

$$\omega_{SURGE} = \frac{1}{\sqrt{L_{\text{TRACE}} * C_{\text{OSS}}}} * \sqrt{1 - \left(\frac{\sqrt{L_{\text{TRACE}} / C_{\text{OSS}}}}{2 R_{\text{OFF}}}\right)^{2}}$$

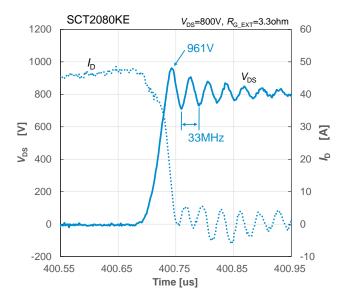

Figure 2.에 ROHM 의 SiC MOSFET (SCT2080KE)를 사용한 턴-오프시의 서지 파형을 나타냅니다. HVdc 에 800V를 인가했을 때 Vbs\_surge는 961V, R 링깅 주파수는 약 33M Hz 로 되어 있는 것을 알 수 있습니다. 식 (1)을 사용해 이 파형으로부터 LMAIN를 산출하면 약 110nH 가됩니다.

Figure 2. 턴-오프 서지 파형

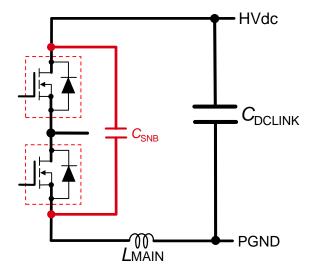

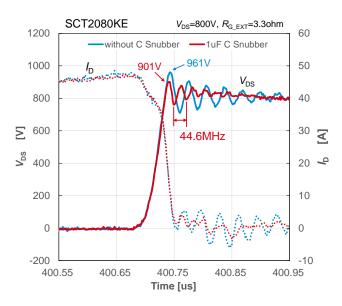

다음으로 Figure 3.에 나타낸 스너버 회로 CSNB 를 추가하여 실질적으로 LMAIN 가 제거되었을 때의 턴-오프 서지파형을 Figure 4.에 나타냅니다.

Figure 3. C 스너버 회로

이때 서지가 50V 이상 저감되어(약 901V), 링깅 주파수도 44.6MHz로 커져 CSNB를 포함한 회로망에서의 LMAIN가 작아지고 있음을 알 수 있습니다. 마찬가지로 식 (1)을 이용하여 LMAIN를 산출하면 약 71nH가 됩니다.

원래라면 이 배선 인덕턴스를 최소화하는 패턴 설계가 바람직하지만 보통 기기의 방열설계를 우선하기 때문에 반드시 이상적인 배선설계가 되지는 않습니다. 따라서, 스너버 회로를 가능한 스위칭 디바이스 근처에 레이아웃하여 바이패스 회로를 형성함으로써 서지 발생원이 되는 배선 인덕턴스의 축적된 에너지를 흡수할 수 있습니다.

Figure 4. C 스너버 회로에 의한 턴-오프 서지의 저감

그리고 스위칭 디바이스의 전압을 클램프하여 턴-오프 서 지를 작게 할 수 있습니다.

#### Snubber Circuit 의 종류와 선정

스너버 회로에는 저항이나 코일 및 콘덴서 등의 수동 부품을 조합한 회로, 또는 반도체 디바이스를 이용한 액티브회로가 있습니다.\*1 이 어플리케이션 노트에서는, 제어가불필요하고 비용적으로 뛰어난 회로 방식에 대해 설명하겠습니다.

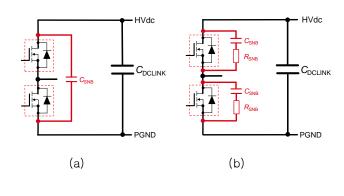

Figure 5.는 스너버 회로 예를 나타냅니다. 브릿지로 구성되어 있는 MOSFET 의 상하로 일괄적으로 콘덴서 CSNB 를 접속하는 (a)C 스너버 회로, 각 스위칭 디바이스의 드레인-소스간에 저항 RSNB와 콘덴서 CSNB를 접속하는 (b)RC 스너버 회로, RC 스너버 회로에 다이오드를 추가한 (c)방전형 RCD 스너버 회로, RDC 스너버 회로 등이 있습니다.

이러한 스너버 회로가 더욱 효과를 발휘하기 위해서는, 가능한 한 스위칭 디바이스의 근처에 실장되어야 합니다.

(a)는 부품수가 적지만 브릿지 구성의 상하간에 접속해야 하기 때문에 배선길이가 길어지는 단점이 있으며, 디스크리트 구성보다 2in1 구성 등의 모듈에서 사용되는 경우가 많습니다.

(b)는 각 스위칭 디바이스 근처에 스너버 회로를 레이아웃 할 수 있지만 디바이스가 턴-온 할 때마다  $C_{SNB}$  에 축적된 모든 에너지를  $A_{SNB}$  로 소비해야 합니다. 따라서 스위칭 주파수가 높아지면  $A_{SNB}$  에서 소비되는 전력은 수 W 가 되며  $C_{SNB}$ 를 그다지 크게 하지 못해 서지 억제효과가 한정적으로 되기 쉬운 방식입니다. 또,  $A_{SNB}$  에 의해 서지 흡수 능력은 제한되어 억제 효과도 한정적이됩니다.

Figure 5. 스너버 회로의 종류 (a)C 스너버 회로, (b)RC 스너버 회로, (c)방전형 RCD 스너버 회로, (d)비방전형 RCD 스너버 회로

(c)는 PSNB 에서 소비하는 전력은 (b)와 같지만 서지를 다이오드만 경유하여 흡수하기 때문에 (b)보다 서지흡수 효과가 높고 실용적입니다. 단, 사용하는 다이오드의 리커버리 특성에 주의하고, 서지 흡수시의 전류변화가 크기 때문에 스너버 회로의 배선 인덕턴스를 최대한 작게 하는 등의 배려가 필요합니다. 추가로 *R*SNB 는 *C*SNB 와 병렬로 접속해도 동작은 동일합니다.

(d)는 CSNB에서 흡수한 서지 에너지만을 PSNB로 소비할 뿐 CSNB 에 축적된 모든 에너지를 스위칭마다 방전하지 않습니다. 그 때문에, 스위칭 주파수가 고속화해도 RSNB 의 소비전력은 그만큼 커지지 않고, CSNB 를 크게 하는 것이 가능해져, 지극히 억제 효과가 높은 회로를 실현할 수 있습니다. 단, 배선 레이아웃이 복잡해져 4 층 이상의 기판이 아니면 실현이 매우 어렵습니다.

이와 같이 여기서 소개한 스너버 회로에도 일장일단이 있어 전원회로 구성이나 변환전력 용량에 따른 최적의 스너버 회로를 선택할 필요가 있습니다. 이어서 각 스너버 회로의 설계 방법에 대해 설명하겠습니다.

## C스너버 회로 설계

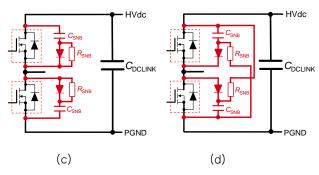

Figure 6.에 나타낸 C 스너버 회로는 CSNB 를 통해 LMAIN 의 축적 에너지를 흡수합니다. 그 때문에, 스너버 회로에 형성되는 LSNB 는 LMAIN 보다 작게 할 필요가 있습니다. CSNB 에 축적된 에너지는 기본적으로 방전되지

않으므로 정전용량은 클수록 서지 억제효과는 높아지지만 사용하는 콘덴서의 등가직렬 인덕턴스(ESL)도 LSNB 에 가미해야 합니다. 일반적으로 콘덴서는 크기가 커질수록 ESL 은 커지기 때문에 정전용량 선정에 있어 주의가 필요합니다.

LMAIN 에 축적된 에너지를 모두 CSNB로 흡수한다고 하고, 정전용량을 식(2)에서 나타낸 기준으로서 선정합니다.

Figure 6. C 스너버 회로

#### RC 스너버 회로 설계

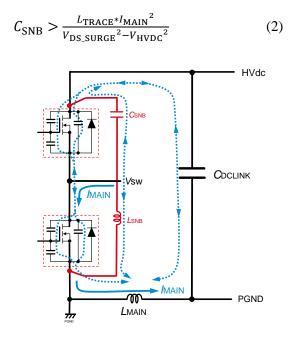

Figure 7.은 RC 스너버 회로의 동작시 전류의 경로를 나타냅니다.

Figure 7. RC 스너버 회로

CSNB 는 C 스너버 회로와 마찬가지로 식 (2)에 의해 결정합니다. 다음 *R*SNB 의 기준치를 식 (3)에서 구합니다.

$$R_{\rm SNB} < \frac{-1}{f_{\rm sw} * C_{SNB}* \ln[(V_{DS\_SURGE} - V_{SNB})/V_{DS\_SURGE}]} \ \ (3)$$

fsw: 스위칭 주파수

V<sub>SNB</sub>: 방전 스너버 전압(VDS\_SURGE의 0.9 배) R<sub>SNB</sub> 를 결정한 후에 R<sub>SNB</sub> 로 소비되는 전력을 식(4)로 계산해, 손실을 만족하는 저항기를 선정합니다.

$$P_{\text{SNB}} = \frac{L_{TRACE} \times I_{MAIN}^2 \times f_{sw}}{2} + \frac{C_{SNB} \times V_{HVDC}^2 \times f_{sw}}{2} \quad (4)$$

RC 스너버 회로에서는 식(4)의 제 2 항이 추가되어 fsw 혹은 HVpc 가 높을수록 RsnB 에서 소비되는 전력은 커지기 때문에  $P_{SNB}$  가 커 저항의 선정이 어려운 경우는  $C_{SNB}$  의 정전 용량치를 낮춰 재계산해야 합니다.

더욱이 RC 스너버회로가 충분히 서지를 흡수하기 위해서는  $R_{\text{SNB}}$ 와  $C_{\text{SNB}}$ 에 의한 공진각주파수 $\omega_{\text{SNB}}$ 가 서지의 공진각주파수ωsurge 보다 충분히 낮아야 하므로, 식 (5)와 같이 RC 스너버 회로의 공진주파수ωsNB 를 확인합니다.

$$\omega_{\rm SNB} = \frac{1}{R_{SNB}*C_{SNB}} \ll \omega_{\rm SURGE}$$

(5)

#### 방전형 RCD 스너버 회로 설계

방전형 RCD 스너버 회로의 설계는 기본적으로 RC 스너버 회로와 같습니다. 단 다이오드에 의한 서지흡수를 위해 식 (5)에 의한 공진주파수의 확인은 불필요합니다. 하지만 다이오드는 리커버리 전류가 작은 제품을 선정하지 않으면 안됩니다.

#### 비방전형 RCD 스너버 회로 설계

비방전형 RCD 스너버 회로는 방전형 RCD 스너버 회로와 달리  $R_{SNB}$  로 소비하는 전력은 서지분만의 에너지이며 허용손실이 억제되어 *A*SNB 의 선택사항이 넓어집니다. 따라서  $C_{\mathsf{SNB}}$  의 정전용량을 크게 하는 것이 가능해져 클램프 효과를 높일 수 있습니다.

$C_{SNB}$  는 식 (2)에서 결정하고,  $P_{SNB}$  는 식 (3)에서 결정합니다만, R<sub>SNB</sub>의 소비전력은 식 (6)에서 결정되며, 식 (4)의  $C_{SNB}$  및  $f_{SW}$  를 포함한 제 2 항이 없습니다. 따라서  $C_{SNB}$  혹은  $f_{SW}$  에 의한 소비전력 증가가 기본적으로 없습니다. 따라서 정전용량의  $C_{SNB}$  를 선택할 수 있기 때문에 클램프 효과가 높은 스너버 회로를 실현할 수 있을뿐만 아니라  $f_{sw}$ 의 고주파화에 대응할 수 있습니다.

$$P_{\rm SNB} = \frac{L_{TRACE} \times I_{MAIN}^2 \times f_{sw}}{2} \tag{6}$$

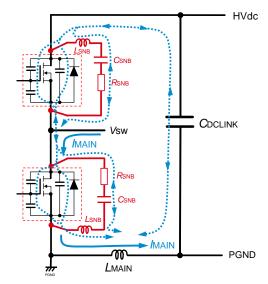

Figure 8.은 비방전형 RCD 스너버 회로의 동작 후 방전

경로를 나타냅니다. 위 암 서지는 PGND, 아래 암은 HVdc 로 방전전류가  $R_{SNB}$  를 경유해 흐르기 때문에 배선 인덕턴스의 영향을 많이 받지 않습니다. 한편, MOSFET 의 드레인-소스간에 접속하는 배선 인덕턴스  $L_{\mathsf{SNB}}$  는 전류 변화가 크기 때문에 최대한 작게 할 필요가 있습니다.

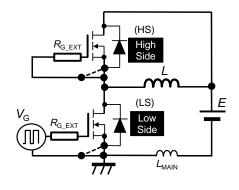

Figure 8. 비방전형 RCD 스너버 회로 방전

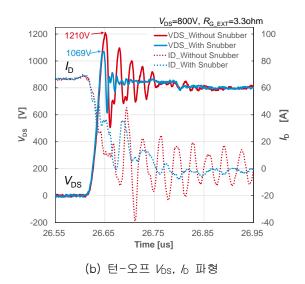

Figure 9.는 ROHM 의 SiC MOSFET (SCT3080KR)를 이 용한 비방전형 RCD 스너버 회로의 효과를 ROHM 평가기 판 (P02SCT3040KR-EVK-001)을 사용해 검증한 파형을 나타냅니다. (a) 는 측정회로 、(b) 는 측정파형입니다.  $R_{G\_EXT}$  는 3.3 $\Omega$ , HVdc 는 800V, 드레인 전류 b 는 약 70A 시의 턴-오프 파형입니다.

스너버 회로를 접속하지 않을 때 서지는 1210V 가 발생 하고 있습니다만, 스너버 회로를 추가하면 1069V 가 되어, 약 12% 저감하고 있는 것을 알 수 있습니다.

(a) 측정회로(LS 측면스위칭)

Figure 9. 턴-오프 서지 비교 (스너버 회로의 유무)

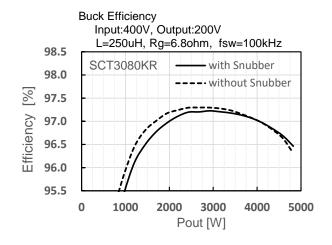

또한 Figure 10.은 Buck Converter 에서의 변환효율을 비교한 그래프를 나타냅니다. 입력전압 400V, 출력전압 200V, R<sub>G\_EXT</sub> 6.8 $\Omega$  로 설정하여 발진 주파수 100kHz 시의효율을 나타내고 있습니다.

Figure 10. Buck Converter 변환효율의 비교

부하전력을 1kW~4.8kW 까지 변화시켰을 때 이하에서는 스너버 회로가 없는 경우의 효율이 최대 0.4% 좋은 결과를 보인 반면 4kW 이상에서는 스너버 회로가 경우의 효율이 0.15% 좋아졌습니다. 이것은 부하전력이 커지면 서지에 의한 전력손실이 커져 스너버 힌 로 에 의한 서지억제로 스위칭 손실이 결과적으로 저감되었기 때문입니다.

#### Package 에 의한 서지 발생 차이

마지막으로 턴오프 서지 발생이 패키지마다 다르다는 것을 설명합니다.

Figure 11 은 ROHM SiC MOSFET 의 대표적인 패키지

입니다만, (a)는 넓게 일반적으로 사용되고 있는 TO-24 7N(3L), (b)는 최근 채용되고 있는 구동 회로용 소스 단자 (켈빈 접속)를 갖춘 TO-247-4L 입니다.

Figure 11. SiC MOSFET Package 例시 (a)TO-247N. (b)TO-247-4L

이 4L 타입은 3L 타입에 비해 구동 회로의 경로를 변경하여 스위칭 속도를 빠르게 한 것입니다. 따라서 턴-온 서지와 턴-오프 서지가 기존보다 커지는 경향이 있습니다.

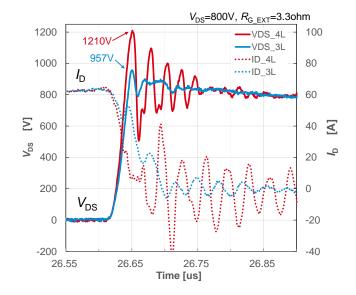

Figure 12. 턴-오프 서지 비교 (TO-247N VS. TO-247-4L)

Figure 12.는 3L 타입과 4L 타입의 턴-오프 서지 비교를 검증한 파형을 나타냅니다. 1/bs=800V, R<sub>G\_EXT</sub>=3.3Ω, I<sub>D</sub>=65A 시의 턴-오프이며, 드레인-소스간 서지는 3L 타입이 957V 인데 반해, 4L 타입은 1210V 로 커지고 있음을 알 수 있습니다.

이 서지에 의한  $V_{OS}$ 의 링깅은 Figure 7.이나 Figure 8.에서 나타난 바와 같이  $C_{OS}$  뿐만 아니라  $C_{GD}$ ,  $C_{GS}$  도 경유하여 흐르기 때문에 MOSFET 의 게이트-소스간 전압  $V_{GS}$  에 예기치 않은 서지를 발생시키는 경우가 있어  $V_{GS}$ 의 서지 규격을 초과하는 경우가 있습니다. 따라서  $V_{GS}$ 의 서지 억제 방법에 대해 별도 어플리케이션 노트\*2 를 제공하고

있습니다만, 억제효과가 부족한 경우에는 드레인-소스간에 스너버 회로를 추가하여 서지를 억제하는 것이 효과적인 수단이 되는 경우도 있습니다.

이상과 같이 브릿지 구성에 의한 MOSFET의 게이트신호는 MOSFET 끼리 서로 관련되면서 동작하여 게이트-소스 간전압에 예기치 않은 전압서지를 발생시키고 있으며 그억제 방법은 기판의 패턴 레이아웃과 얽히면서 다양한 대응이 필요합니다. 서지 발생 억제를 위한 도움이 되는 자료로 활용되기를 기대합니다.

이상

#### 참고자료 :

- \*1 The Fundamentals of Switching-Mode Converters」

P95~P107

K. Harada, T. Ninomiya, W. Gu

CORONA PUBLISHING CO., LTD., Feb. 1992

- \* 2 「Bridge 구성에서 Gate-Source 전압의 작용」 Application Note (No. 63AN110K Rev.001) 로옴 주식회사, 2020 년 9월

#### Notes

- 1) The information contained herein is subject to change without notice.

- Before you use our Products, please contact our sales representative and verify the latest specifications:

- 3) Although ROHM is continuously working to improve product reliability and quality, semiconductors can break down and malfunction due to various factors. Therefore, in order to prevent personal injury or fire arising from failure, please take safety measures such as complying with the derating characteristics, implementing redundant and fire prevention designs, and utilizing backups and fail-safe procedures. ROHM shall have no responsibility for any damages arising out of the use of our Poducts beyond the rating specified by ROHM.

- 4) Examples of application circuits, circuit constants and any other information contained herein are provided only to illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

- 5) The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. ROHM does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by ROHM or any other parties. ROHM shall have no responsibility whatsoever for any dispute arising out of the use of such technical information.

- 6) The Products specified in this document are not designed to be radiation tolerant.

- 7) For use of our Products in applications requiring a high degree of reliability (as exemplified below), please contact and consult with a ROHM representative: transportation equipment (i.e. cars, ships, trains), primary communication equipment, traffic lights, fire/crime prevention, safety equipment, medical systems, servers, solar cells, and power transmission systems.

- 8) Do not use our Products in applications requiring extremely high reliability, such as aerospace equipment, nuclear power control systems, and submarine repeaters.

- 9) ROHM shall have no responsibility for any damages or injury arising from non-compliance with the recommended usage conditions and specifications contained herein.

- 10) ROHM has used reasonable care to ensure the accuracy of the information contained in this document. However, ROHM does not warrants that such information is error-free, and ROHM shall have no responsibility for any damages arising from any inaccuracy or misprint of such information.

- 11) Please use the Products in accordance with any applicable environmental laws and regulations, such as the RoHS Directive. For more details, including RoHS compatibility, please contact a ROHM sales office. ROHM shall have no responsibility for any damages or losses resulting non-compliance with any applicable laws or regulations.

- 12) When providing our Products and technologies contained in this document to other countries, you must abide by the procedures and provisions stipulated in all applicable export laws and regulations, including without limitation the US Export Administration Regulations and the Foreign Exchange and Foreign Trade Act.

- 13) This document, in part or in whole, may not be reprinted or reproduced without prior consent of ROHM.

Thank you for your accessing to ROHM product informations. More detail product informations and catalogs are available, please contact us.

# ROHM Customer Support System

http://www.rohm.com/contact/