#### Dear customer

ROHM Co., Ltd. ("ROHM"), on the 1st day of April, 2024, has absorbed into merger with 100%-owned subsidiary of LAPIS Technology Co., Ltd.

Therefore, all references to "LAPIS Technology Co., Ltd.", "LAPIS Technology" and/or "LAPIS" in this document shall be replaced with "ROHM Co., Ltd." Furthermore, there are no changes to the documents relating to our products other than the company name, the company trademark, logo, etc.

Thank you for your understanding.

ROHM Co., Ltd. April 1, 2024

# ML62Q1000 Series User's Manual (ML62Q1300/1500/1800/1700 Group)

Issue Date: Dec. 15, 2023

#### Notes

- 1) When using LAPIS Technology Products, refer to the latest product information and ensure that usage conditions (absolute maximum ratings\*1, recommended operating conditions, etc.) are within the ranges specified. LAPIS Technology disclaims any and all liability for any malfunctions, failure or accident arising out of or in connection with the use of LAPIS Technology Products outside of such usage conditions specified ranges, or without observing precautions. Even if it is used within such usage conditions specified ranges, semiconductors can break down and malfunction due to various factors. Therefore, in order to prevent personal injury, fire or the other damage from break down or malfunction of LAPIS Technology Products, please take safety at your own risk measures such as complying with the derating characteristics, implementing redundant and fire prevention designs, and utilizing backups and fail-safe procedures.

- \*1: Absolute maximum ratings: a limit value that must not be exceeded even momentarily.

- 2) The Products specified in this document are not designed to be radiation tolerant.

- 3) Descriptions of circuits, software and other related information in this document are provided only to illustrate the standard operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. And the peripheral conditions must be taken into account when designing circuits for mass production. LAPIS Technology disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, and other related information.

- 4) No license, expressly or implied, is granted hereby under any intellectual property rights or other rights of LAPIS Technology or any third party with respect to LAPIS Technology Products or the information contained in this document (including but not limited to, the Product data, drawings, charts, programs, algorithms, and application examples, etc.). Therefore, LAPIS Technology shall have no responsibility whatsoever for any dispute, concerning such rights owned by third parties, arising out of the use of such technical information.

- 5) LAPIS Technology intends our Products to be used in a way indicated in this document. Please be sure to contact a ROHM sales office if you consider the use of our Products in different way from original use indicated in this document. For use of our Products in medical systems, please be sure to contact a LAPIS Technology representative and must obtain written agreement. Do not use our Products in applications which may directly cause injuries to human life, and which require extremely high reliability, such as aerospace equipment, nuclear power control systems, and submarine repeaters, etc. LAPIS Technology disclaims any and all liability for any losses and damages incurred by you or third parties arising by using the Product for purposes not intended by us without our prior written consent.

- 6) All information contained in this document is subject to change for the purpose of improvement, etc. without any prior notice. Before purchasing or using LAPIS Technology Products, please confirm the latest information with a ROHM sales office. LAPIS Technology has used reasonable care to ensure the accuracy of the information contained in this document, however, LAPIS Technology shall have no responsibility for any damages, expenses or losses arising from inaccuracy or errors of such information.

- 7) Please use the Products in accordance with any applicable environmental laws and regulations, such as the RoHS Directive. LAPIS Technology shall have no responsibility for any damages or losses resulting non-compliance with any applicable laws or regulations.

- 8) When providing our Products and technologies contained in this document to other countries, you must abide by the procedures and provisions stipulated in all applicable export laws and regulations, including without limitation the US Export Administration Regulations and the Foreign Exchange and Foreign Trade Act.

- 9) Please contact a ROHM sales office if you have any questions regarding the information contained in this document or LAPIS Technology's Products.

- 10) This document, in part or in whole, may not be reprinted or reproduced without prior consent of LAPIS Technology.

(Note) "LAPIS Technology" as used in this document means LAPIS Technology Co., Ltd.

Copyright 2018 – 2023 LAPIS Technology Co., Ltd.

### LAPIS Technology Co., Ltd.

2-4-8 Shinyokohama, Kouhoku-ku, Yokohama 222-8575, Japan https://www.lapis-tech.com/en/

LTSZ08023 • 01 • 002

FEUL62Q1000 i

### Notes for product usage

Notes on this page are applicable to the all LAPIS Technology microcontroller products. For individual notes on each LAPIS Technology microcontroller product, refer to [Note] in the chapters of each user's manual.

The individual notes of each user's manual take priority over those contents in this page if they are different.

#### 1. HANDLING OF UNUSED INPUT PINS

Fix the unused input pins to the power pin or GND to prevent to cause the device performing wrong operation or increasing the current consumption due to noise, etc. If the handlings for the unused pins are described in the chapters, follow the instruction.

#### 2. STATE AT POWER ON

At the power on, the data in the internal registers and output of the ports are undefined until the power supply voltage reaches to the recommended operating condition and "L" level is input to the reset pin. On LAPIS Technology microcontroller products that have the power on reset function, the data in the internal registers and output of the ports are undefined until the power on reset is generated. Be careful to design the application system does not work incorrectly due to the undefined data of internal registers and output of the ports.

#### 3. ACCESS TO UNUSED MEMORY

If reading from unused address area or writing to unused address area of the memory, the operations are not guaranteed.

#### 4. CHARACTERISTICS DIFFERENCE BETWEEN THE PRODUCTS

Electrical characteristics, noise tolerance, noise radiation amount, and the other characteristics are different from each microcontroller product.

When replacing from other product to LAPIS Technology microcontroller products, please evaluate enough the apparatus/system which implemented LAPIS Technology microcontroller products.

#### 5. USE ENVIRONMENT

When using LAPIS Technology microcontroller products in a high humidity environment and an environment where dew condensation, take moisture-proof measures.

FEUL62Q1000 ii

### **Preface**

This manual describes the operation of the hardware of the 16-bit microcontroller ML62Q1000 Series. This manual is for ML62Q1300 group, ML62Q1500 group, ML62Q1700 group and ML62Q1800 group. See other manuals for ML62Q1200 group, ML62Q1400 group and ML62Q1600 group.

See the relevant manuals listed in supplementary volume; "MCU Relevant Documents list" as necessary.

FEUL62Q1000 iii

### **Notation**

| Classification  | Notation                                                                                                 | Description                                                                                                                                                                                                                              |

|-----------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ♦ Numeric value | XXh, XXH, 0xXX                                                                                           | Indicates a hexadecimal number.                                                                                                                                                                                                          |

| ♦ Unit          | word, W byte, B nibble, N mega-, M kilo-, K kilo-, k milli-, m micro-, µ nano-, n second, s (lower case) | 1 word = 16 bits<br>1 byte = 8 bits<br>1 nibble = 4 bits<br>$10^6$<br>$2^{10} = 1024$<br>$10^3 = 1000$<br>$10^{-3}$<br>$10^{-6}$<br>$10^{-9}$<br>second                                                                                  |

| ◆ Terminology   | "H" level                                                                                                | Indicates high level voltage $V_{IH}$ and $V_{OH}$ as specified by the electrical characteristics in the data-sheet. Indicates low level voltage $V_{IL}$ and $V_{OL}$ as specified by the electrical characteristics in the data-sheet. |

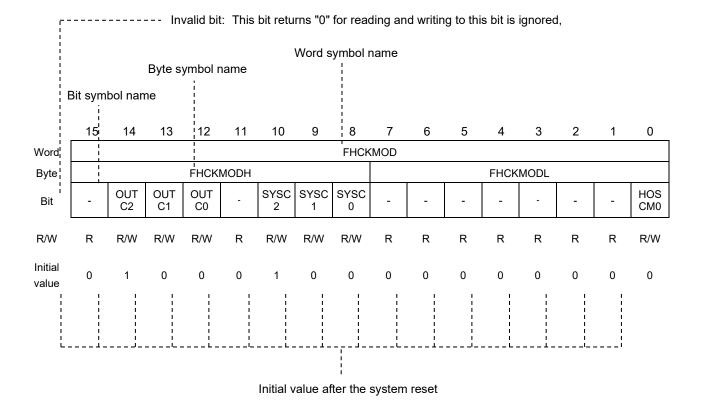

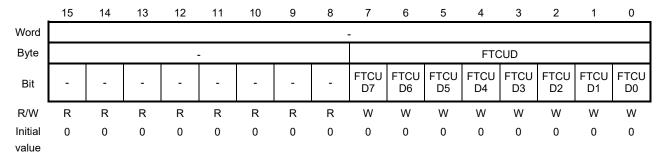

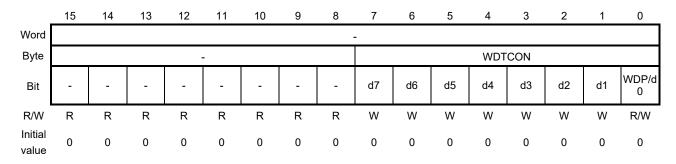

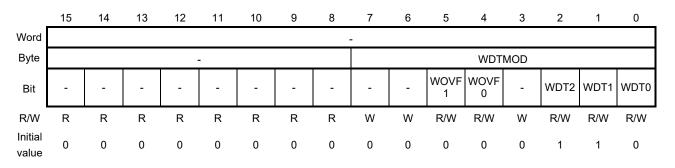

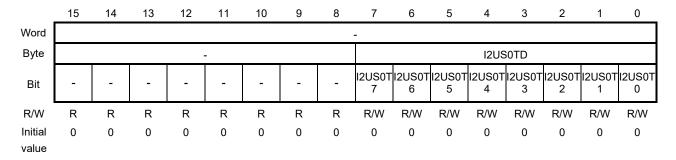

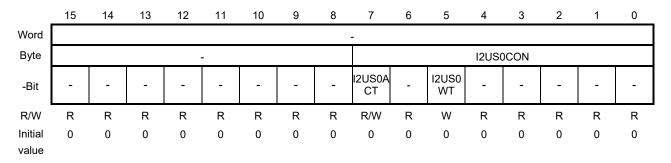

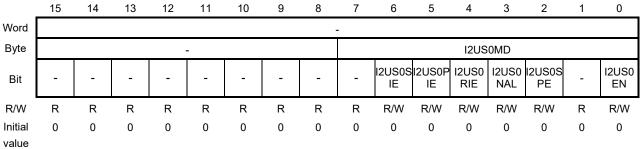

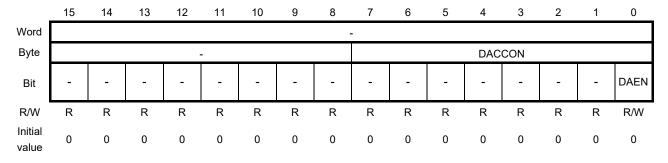

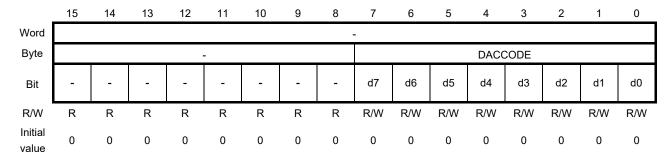

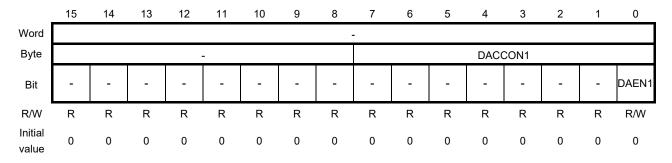

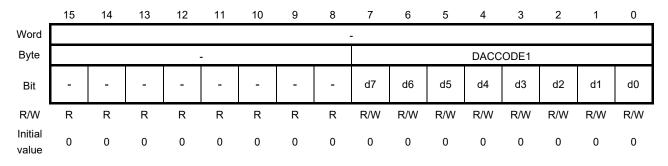

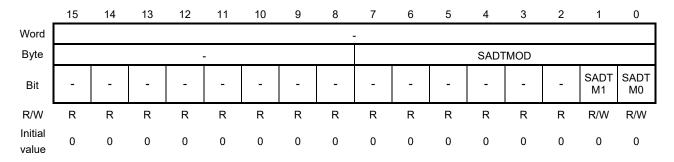

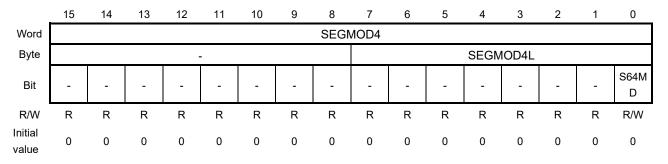

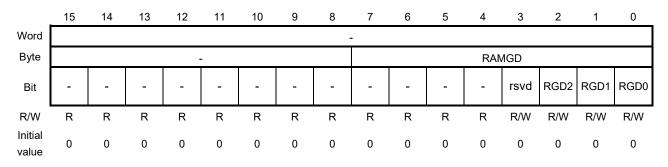

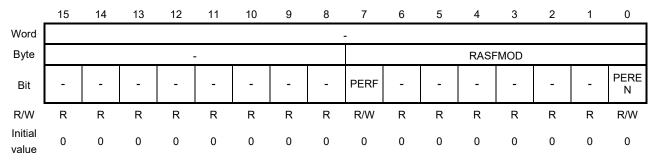

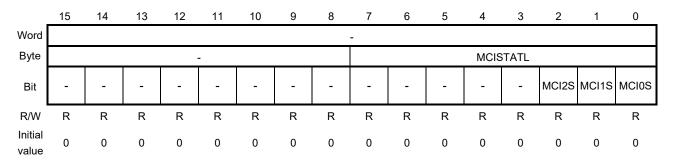

#### ♦ Register description

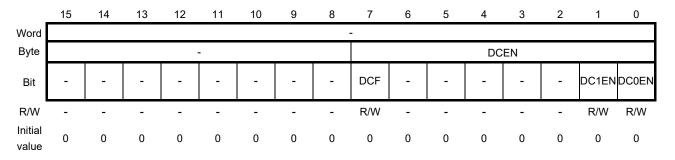

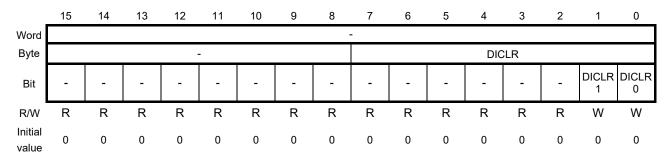

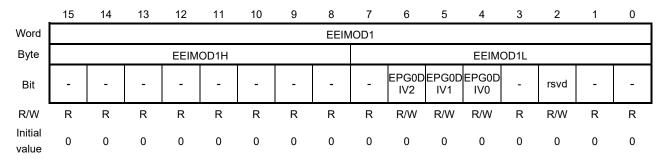

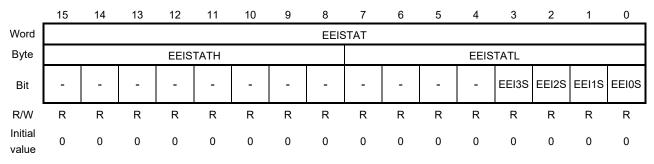

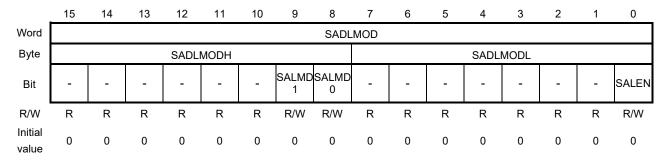

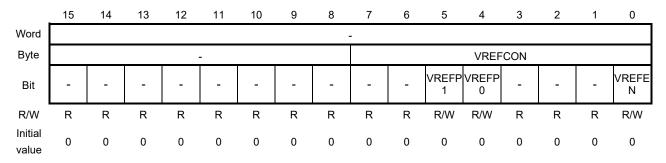

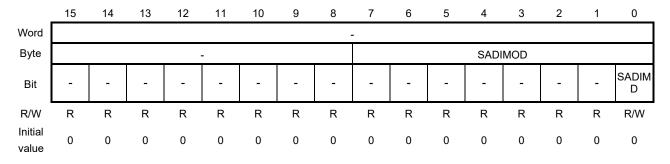

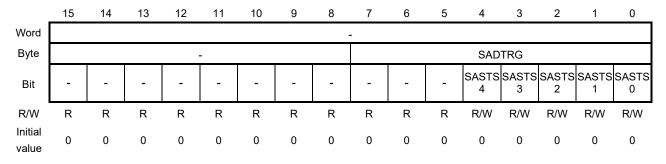

"R/W" indicates that Read/Write attribute. "R" indicates that data can be read and "W" indicates that data can be written. "R/W" indicates that data can be read or written.

MSB: The highest bit of 16-bit register LSB: The lowest bit of 16-bit register

Registers that have a word symbol allow the word-access. If writing or reading the registers not using the word symbol, specify the even number addresses.

FEUL62Q1000 iv

### **Table of Contents**

| able of Contents                                     |      |

|------------------------------------------------------|------|

| Chapter 1                                            |      |

| 1. Overview                                          | 1-1  |

| 1.1 Features                                         |      |

| 1.2 BLOCK DIAGRAM                                    |      |

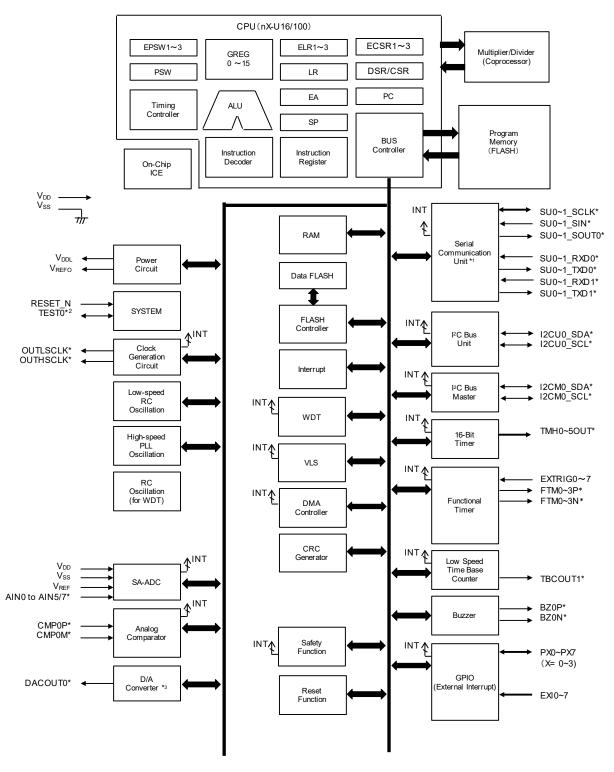

| 1.2.1 Block Diagram of ML62Q1300 Group.              |      |

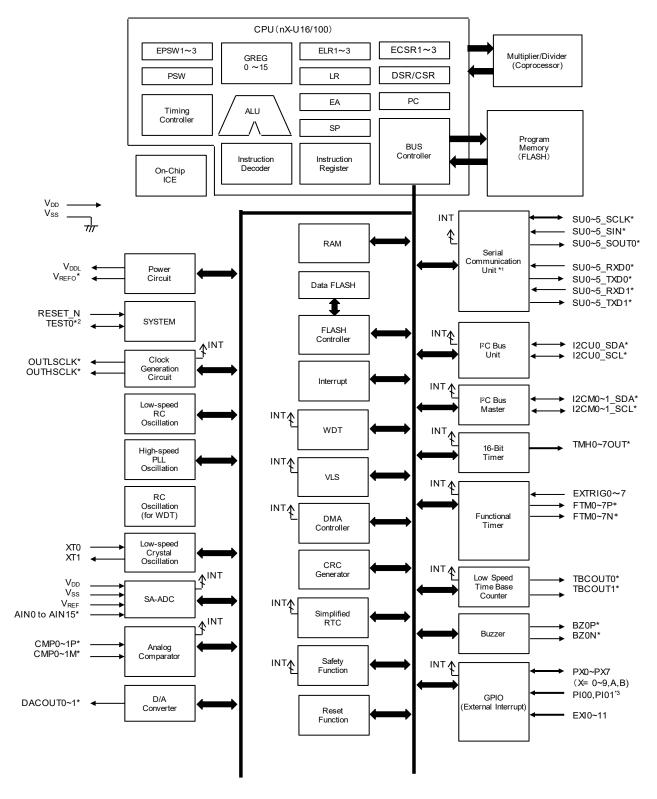

| 1.2.2 Block Diagram of ML62Q1500/ML62Q1800 Group     |      |

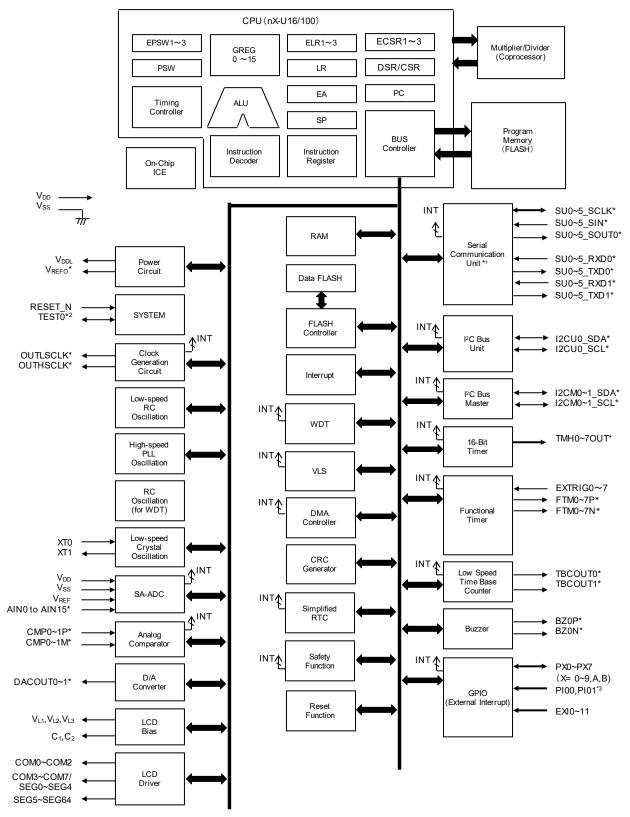

| 1.2.3 Block Diagram of ML62Q1700 Group               |      |

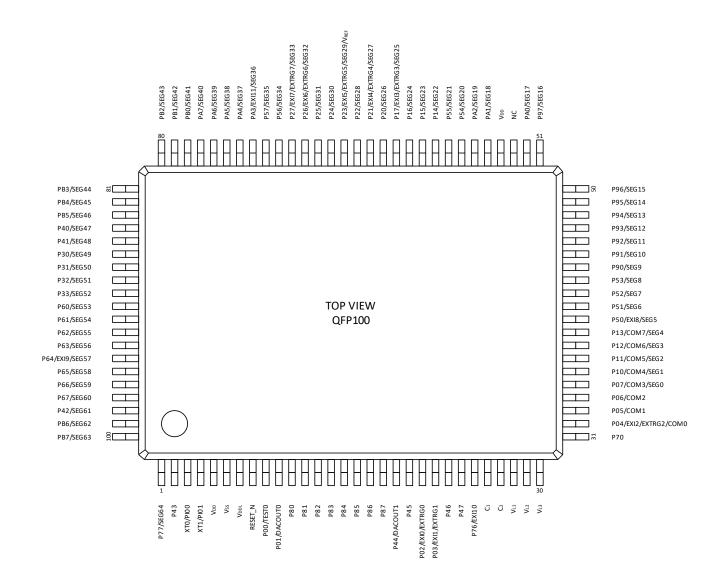

| 1.3 PIN                                              |      |

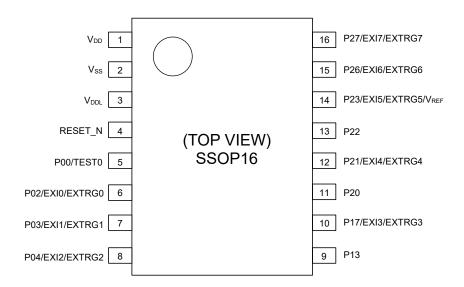

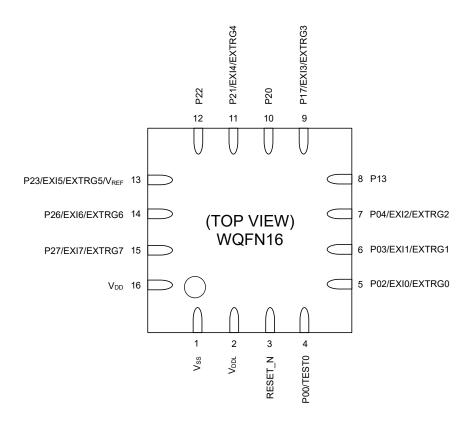

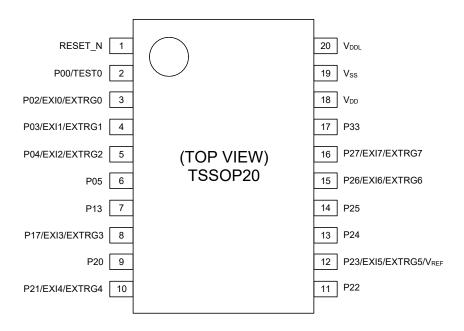

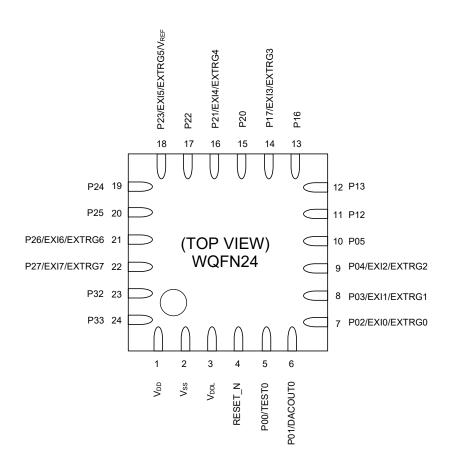

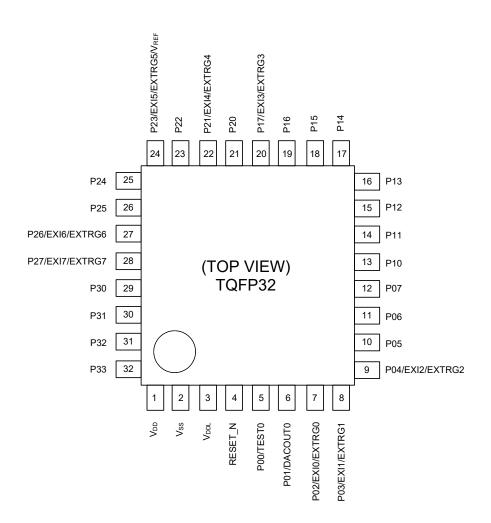

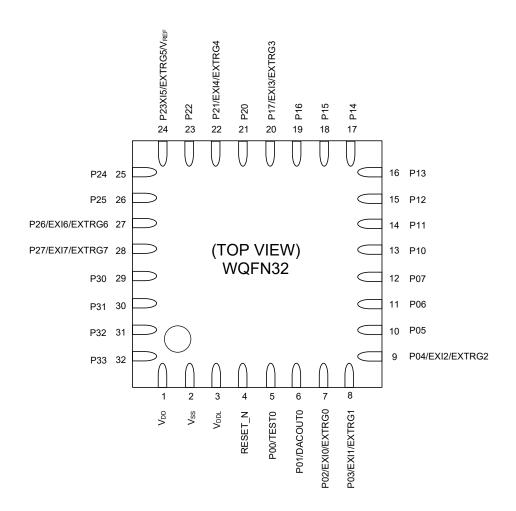

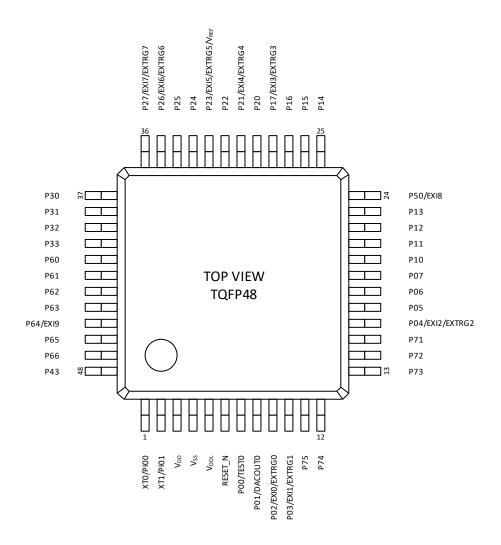

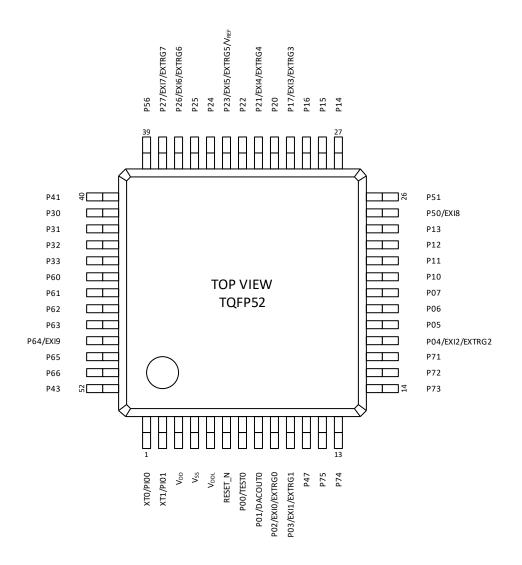

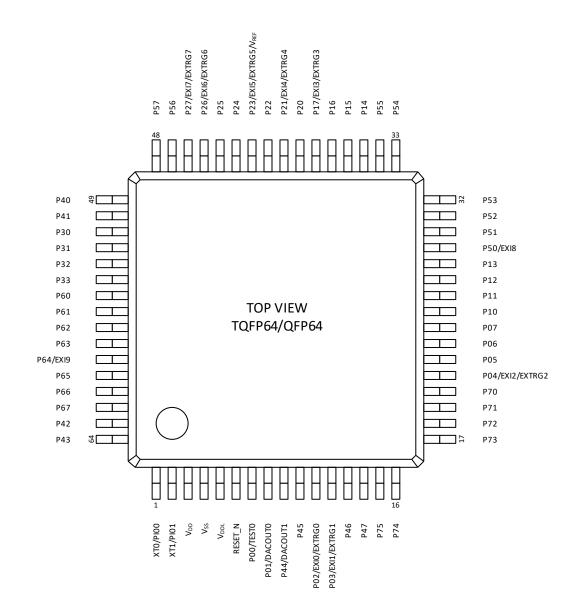

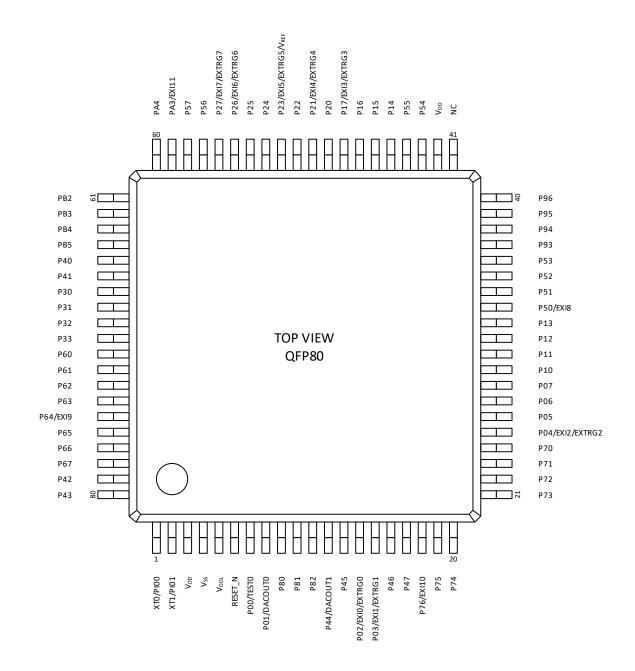

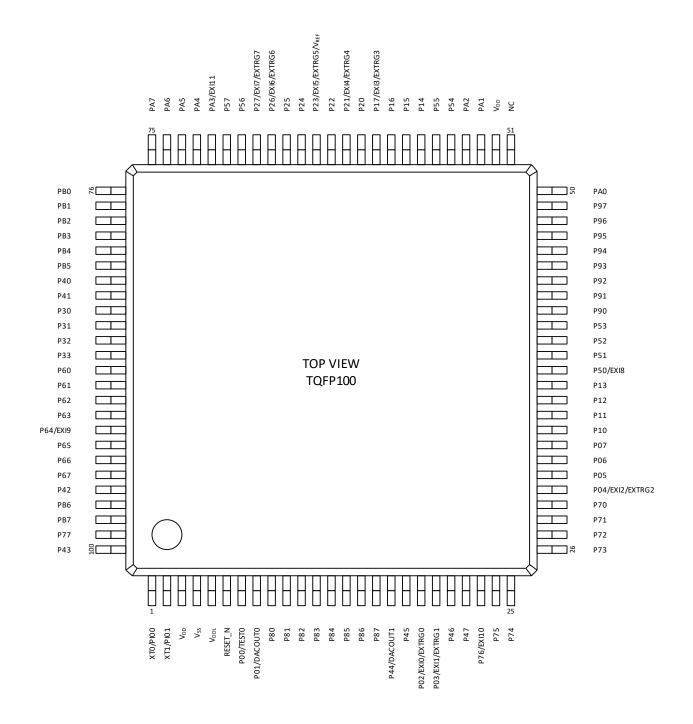

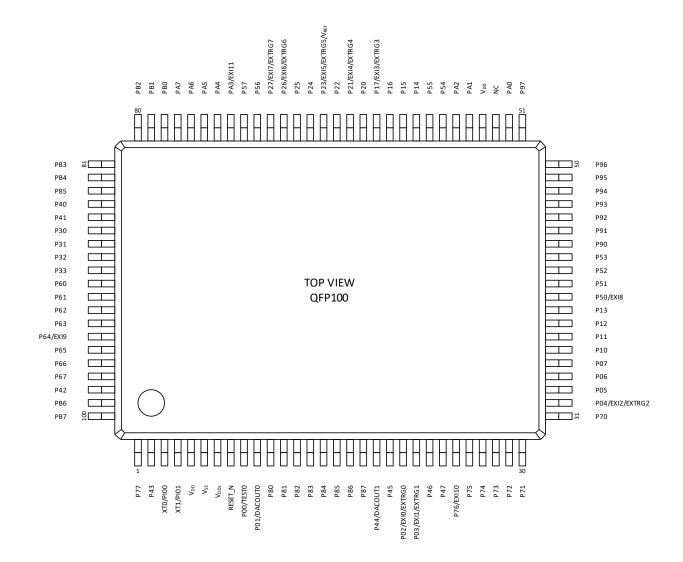

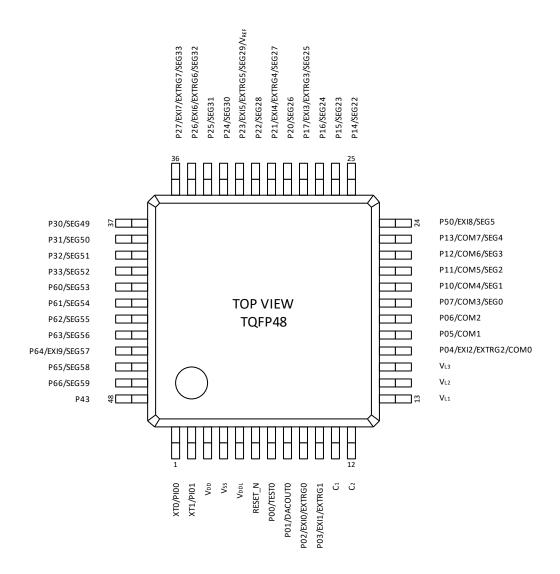

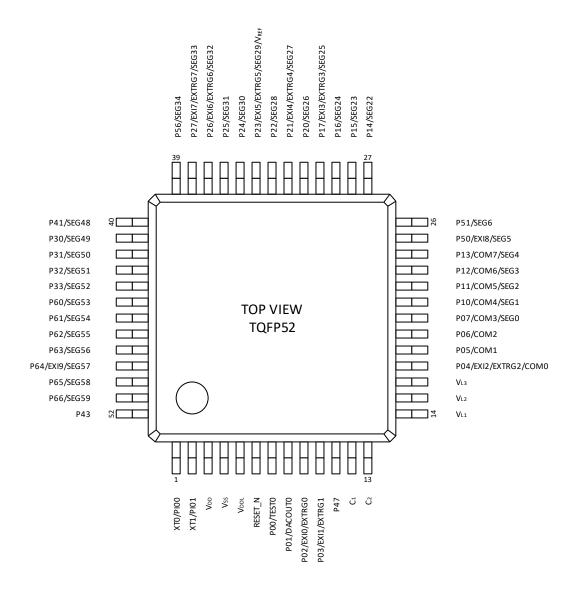

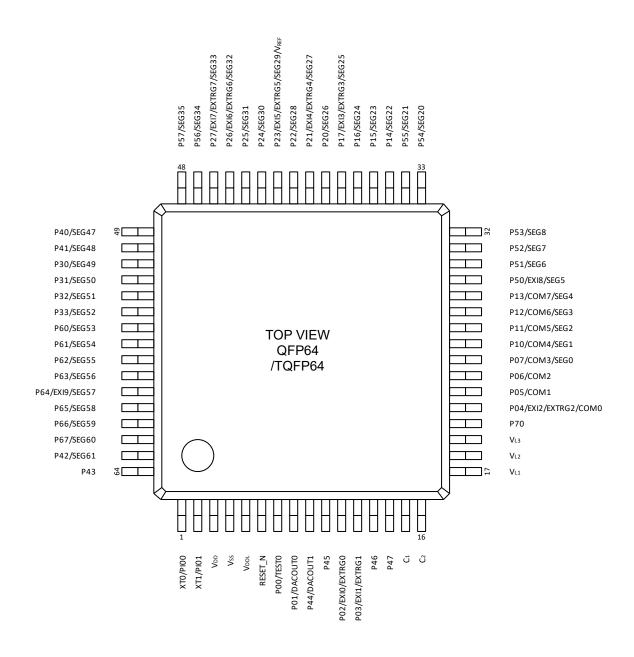

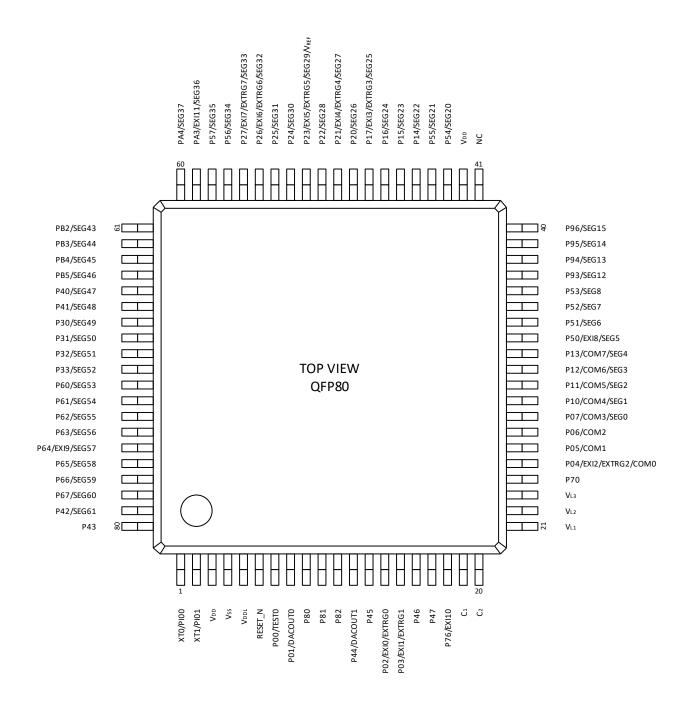

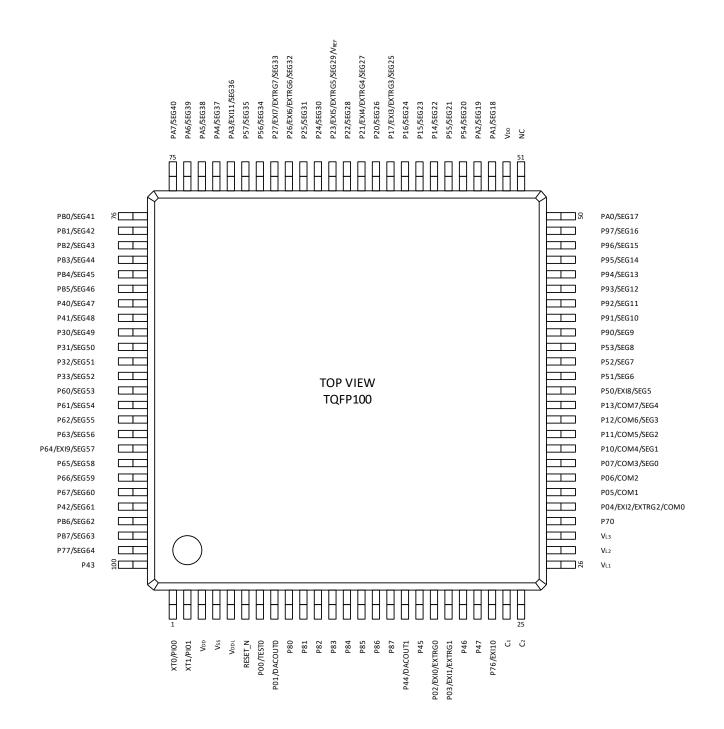

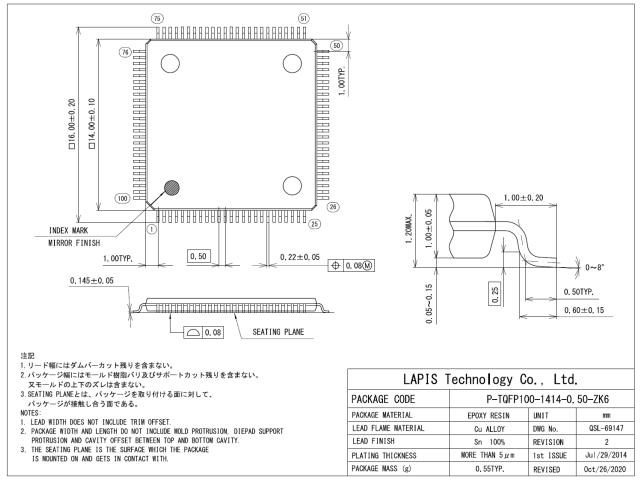

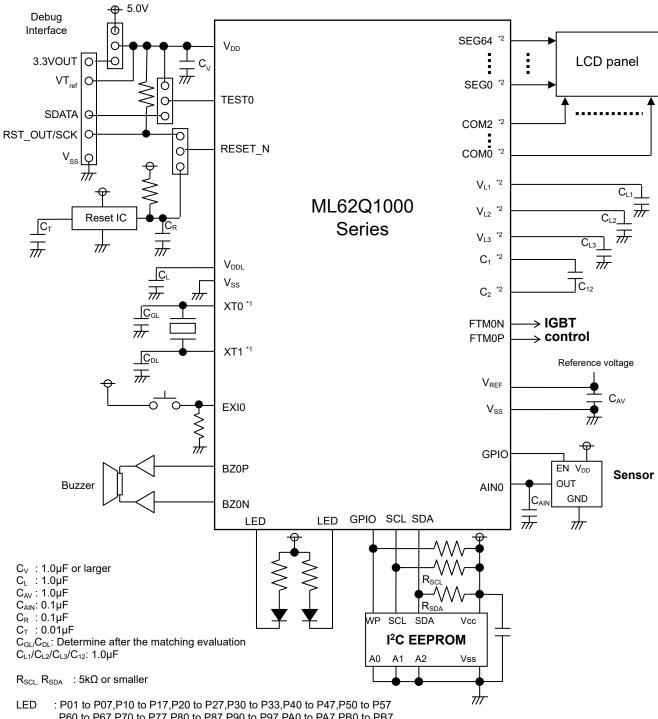

| 1.3.1 Pin Layout                                     |      |

| 1.3.2 PIN LIST                                       |      |

| 1.3.3 PIN DESCRIPTION                                |      |

| 1.3.4 TERMINATION OF UNUSED PINS                     |      |

| Chapter 2                                            |      |

| 2. CPU and Memory Space                              | 2-   |

| 2.1 General Description                              | 2-   |

| 2.2 CPU nX-U16/100                                   |      |

| 2.2.1 Wait Mode and No-wait Mode                     | 2-5  |

| 2.2.2 Notes When Executing SB/RB Instruction         |      |

| 2.2.3 Notes on the Description of Read-modify-write  | 2-5  |

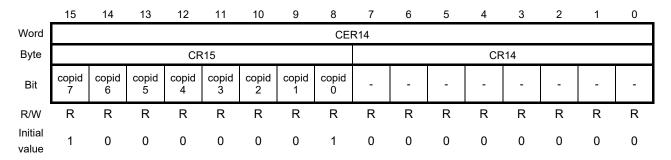

| 2.3 Coprocessor                                      | 2-0  |

| 2.3.1 Multiplier/ Divider                            |      |

| 2.3.2 List of Coprocessor General-purpose Registers  |      |

| 2.3.3 How to Use Multiplier/Divider                  |      |

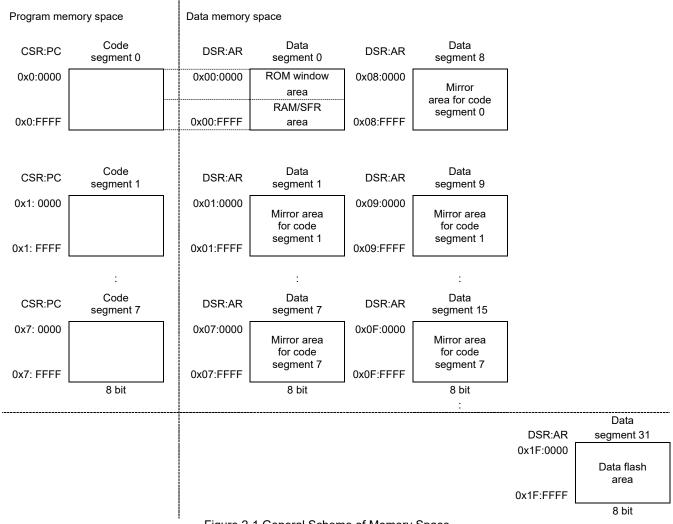

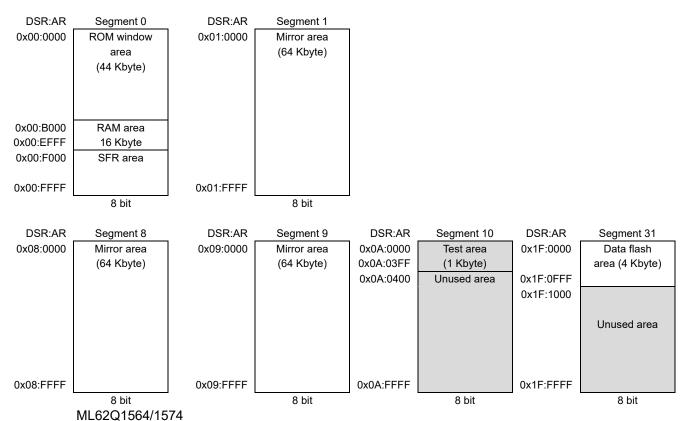

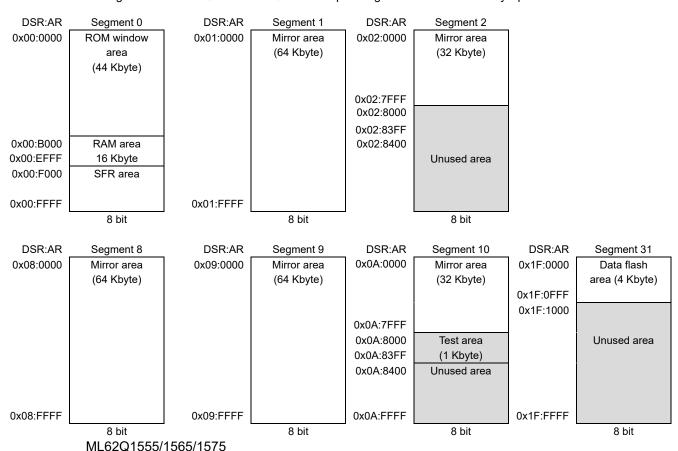

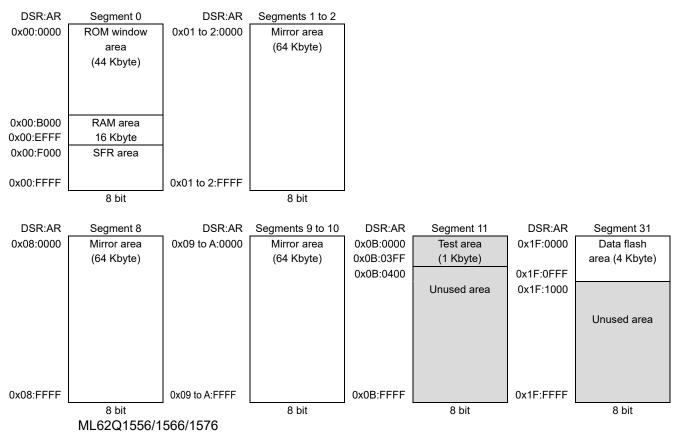

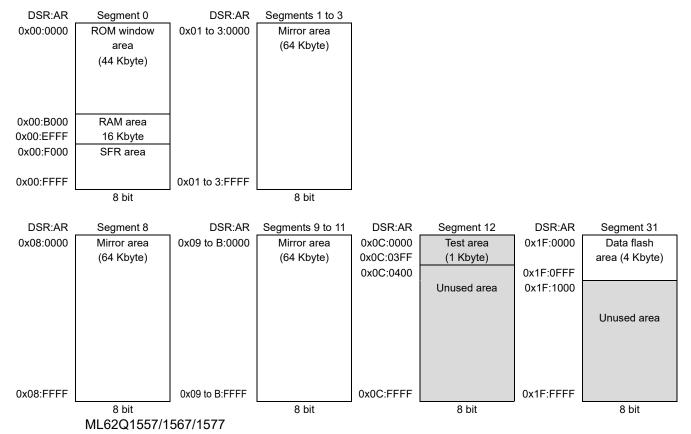

| 2.4 Memory Space                                     |      |

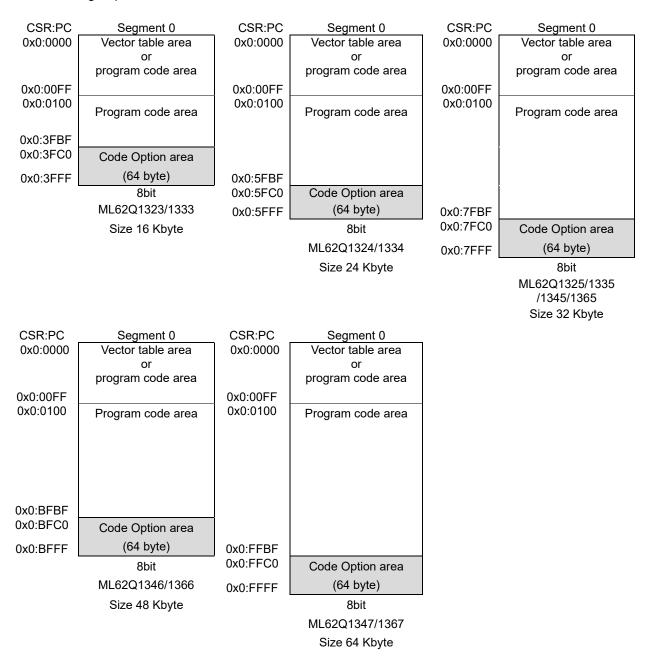

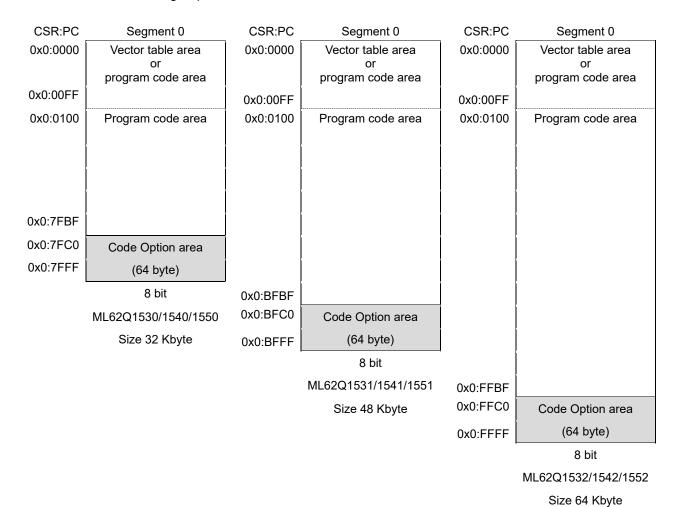

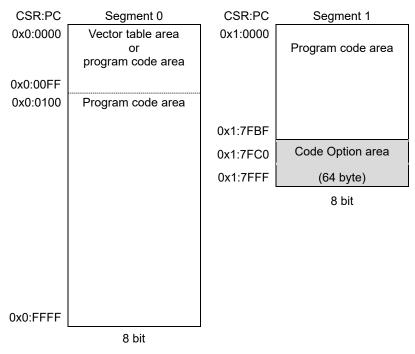

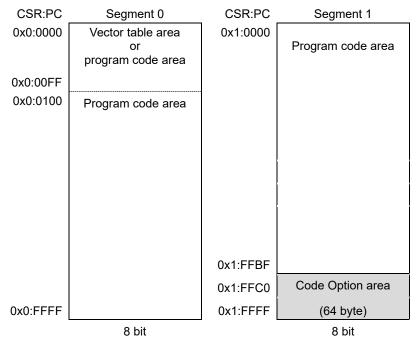

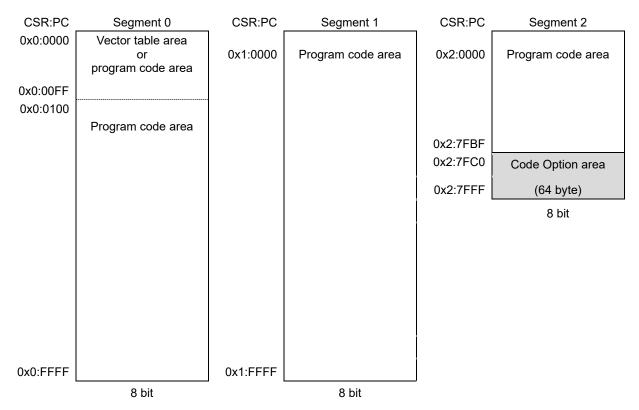

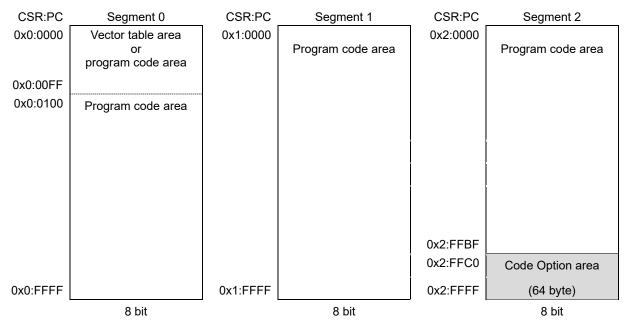

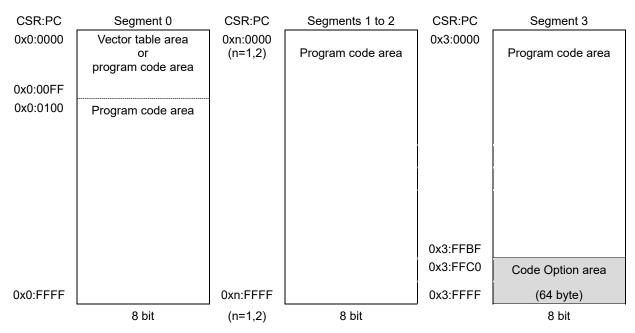

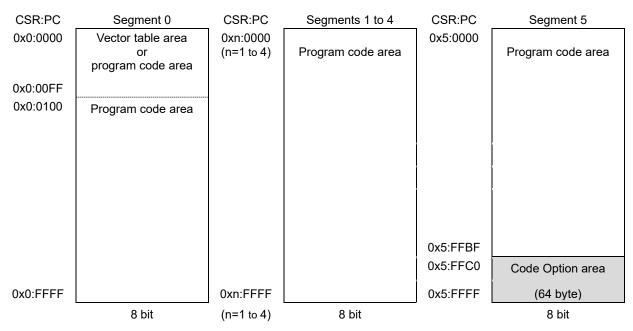

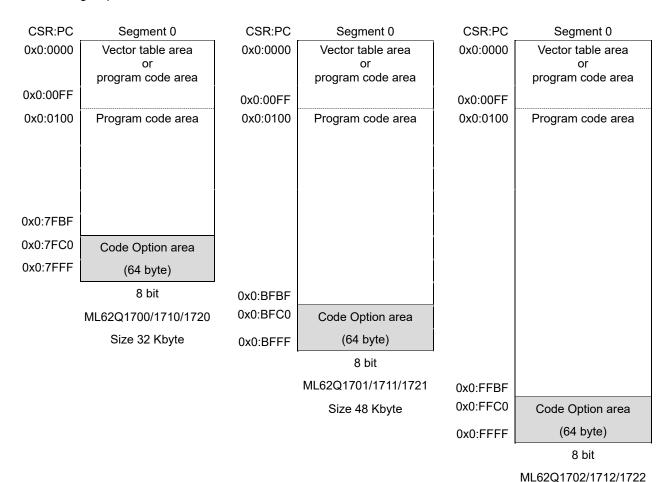

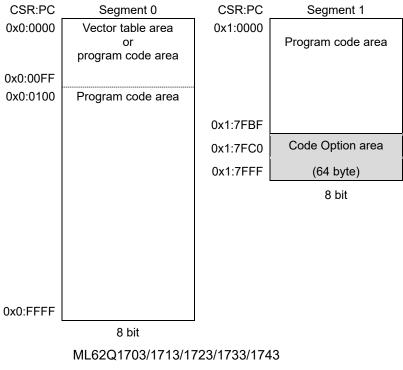

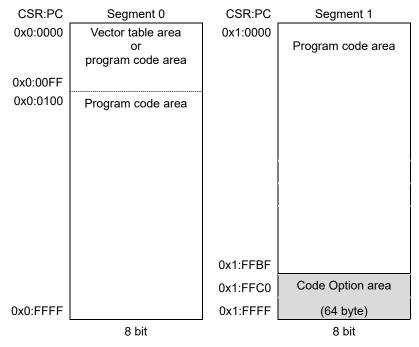

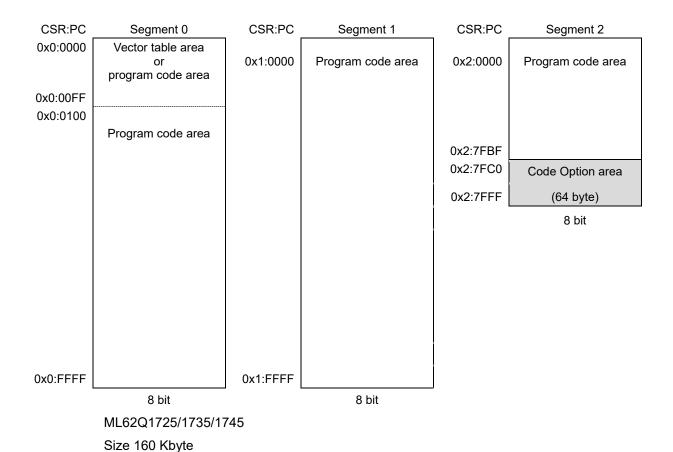

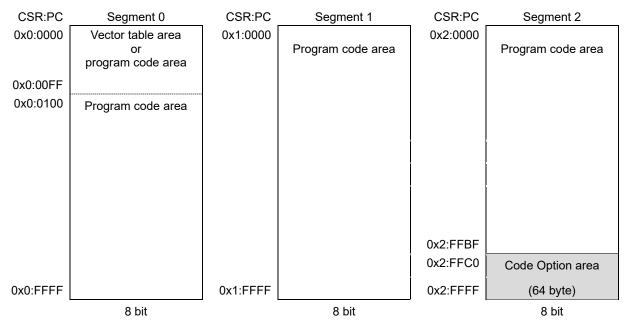

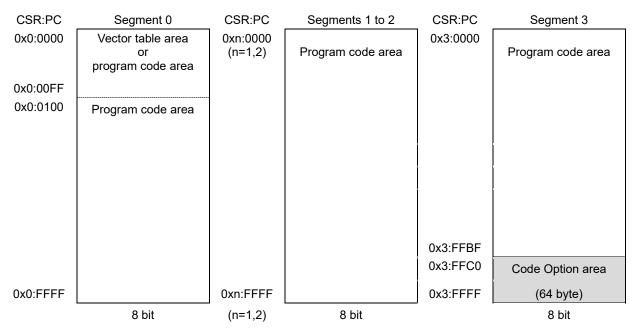

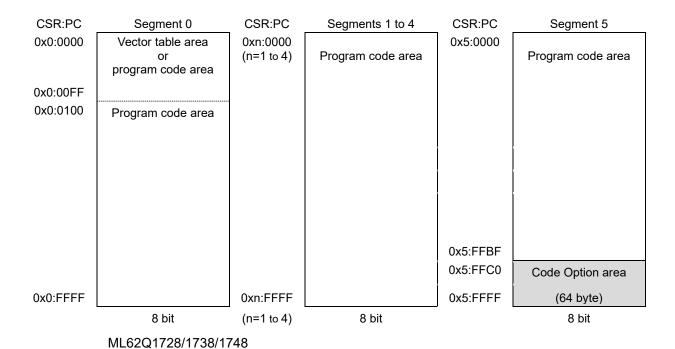

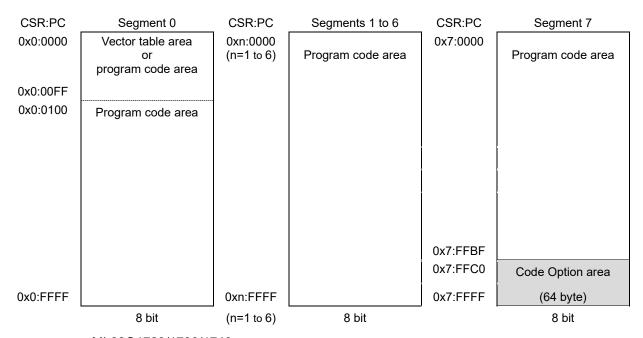

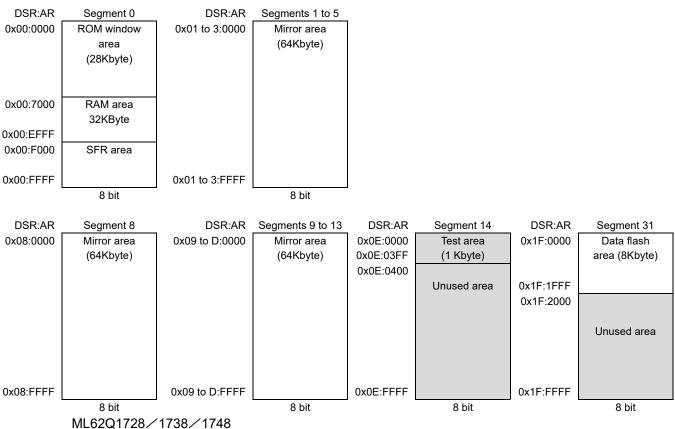

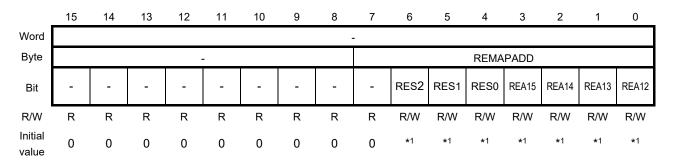

| 2.5 Program Memory Space                             |      |

| 2.6 Data Memory Space                                |      |

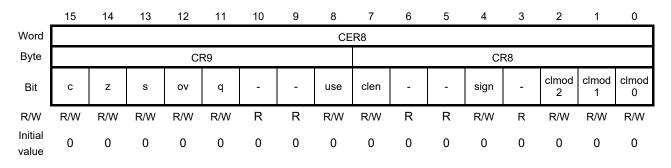

| 2.7 Description of Registers                         |      |

| 2.7.1 List of Registers                              |      |

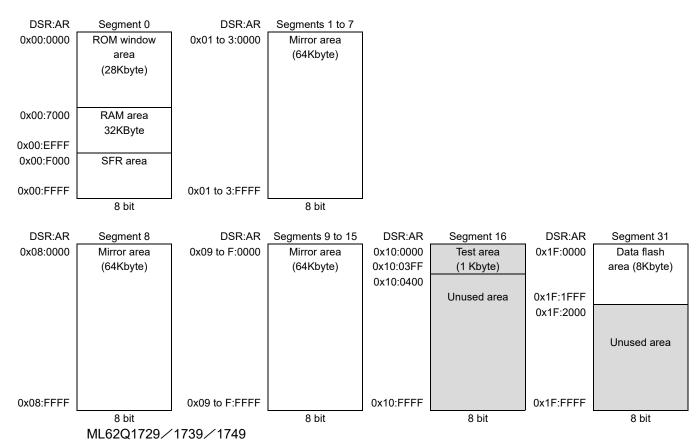

| 2.7.2 Data Segment Register (DSR)                    |      |

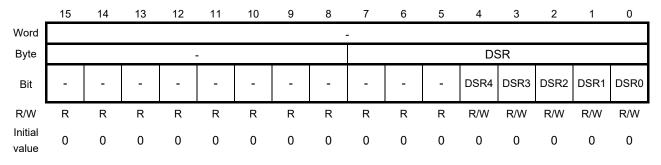

| 2.7.3 Flash Remap Address Register (REMAPADD)        |      |

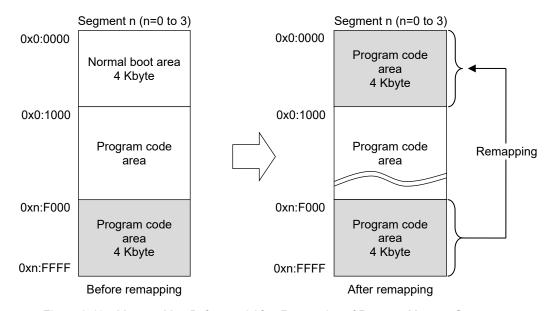

| 2.8 Remapping Function                               |      |

| 2.8.1 Description of Remapping Function              |      |

| 2.8.2 Software Remap                                 |      |

| 2.8.3 Code Option Remap                              | 2-47 |

| Chapter 3                                            |      |

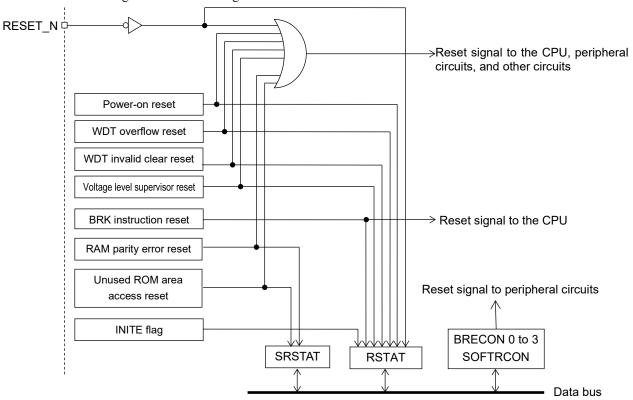

| 3. Reset Function                                    | 3-:  |

| 3.1 General Description                              | 3-:  |

| 3.1.1 Features                                       | 3-2  |

| 3.1.2 Configuration                                  | 3-3  |

| 3.1.3 List of Pins                                   | 3-4  |

| 3.2 Description of Registers                         |      |

| 3.2.1 List of Registers                              |      |

| 3.2.2 Reset status register (RSTAT)                  | 3-0  |

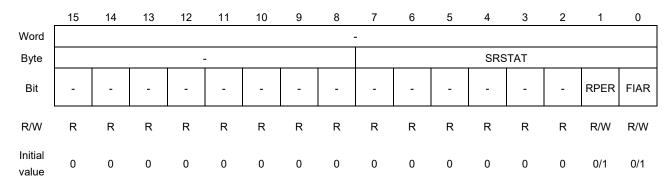

| 3.2.3 Safety Function Reset Status Register (SRSTAT) |      |

| 3.3 Description of Operation                         | 3-9  |

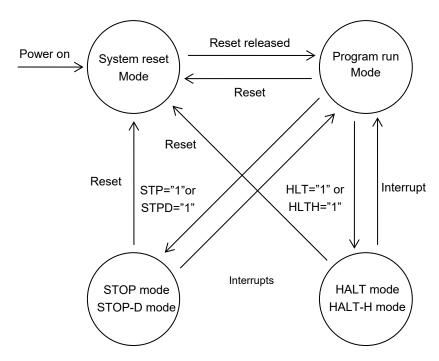

| 3.3.1 Operation of Reset Function                    |      |

| 3.3.2 System Reset Mode                              | 3-10 |

| 4. Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 4.1 General Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-1                                                |

| 4.1.1 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-2                                                |

| 4.1.2 Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                    |

| 4.2 Description of Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-4                                                |

| 4.2.1 List of Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |

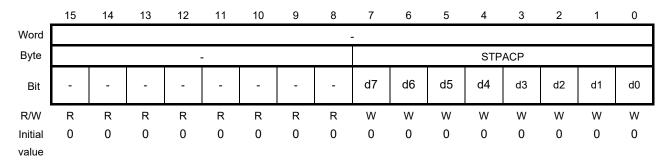

| 4.2.2 Stop Code Acceptor (STPACP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-5                                                |

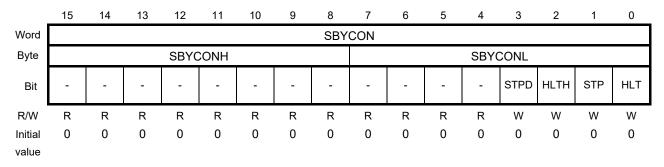

| 4.2.3 Standby Control Register (SBYCON)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-6                                                |

| 4.2.4 Software Reset Acceptor (SOFTRACP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                    |

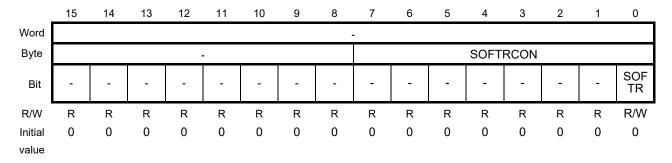

| 4.2.5 Software Reset Control Register (SOFTRCON)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-8                                                |

| 4.2.6 Block Clock Control Register 0 (BCKCON0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                    |

| 4.2.7 Block Clock Control Register 1 (BCKCON1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-10                                               |

| 4.2.8 Block Clock Control Register 2 (BCKCON2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-12                                               |

| 4.2.9 Block Clock Control Register 3 (BCKCON3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-14                                               |

| 4.2.10 Block Reset Control Register 0 (BRECON0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                    |

| 4.2.11 Block Reset Control Register 1 (BRECON1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-16                                               |

| 4.2.12 Block Reset Control Register 2 (BRECON2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-18                                               |

| 4.2.13 Block Reset Control Register 3 (BRECON3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-20                                               |

| 4.3 Description of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-21                                               |

| 4.3.1 Program Run Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-21                                               |

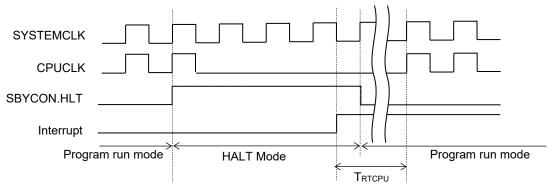

| 4.3.2 HALT Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-21                                               |

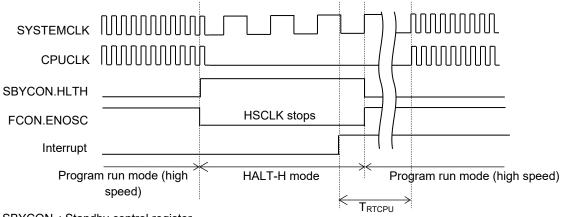

| 4.3.3 HALT-H Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-22                                               |

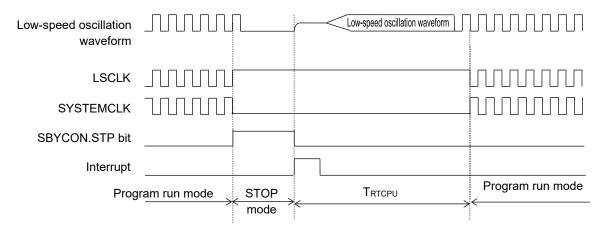

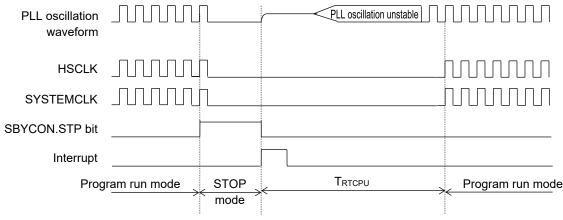

| 4.3.4 STOP Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-23                                               |

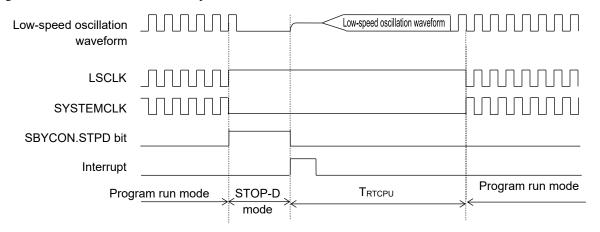

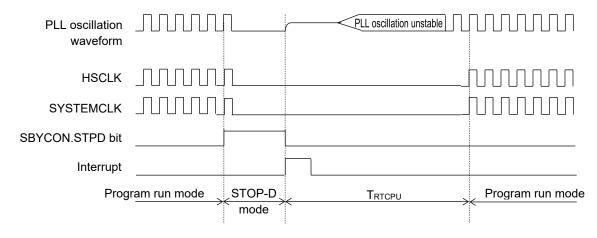

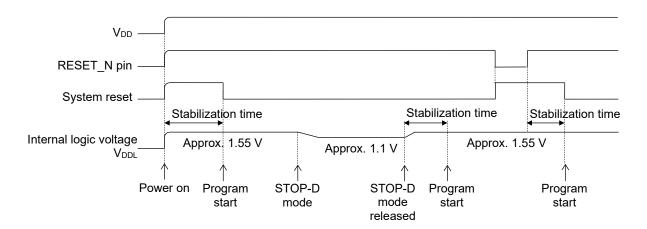

| 4.3.5 STOP-D Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-24                                               |

| 4.3.6 Note on Return Operation from Standby Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                    |

| 4.3.7 Operation of Each Function in Standby Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                    |

| 4.3.8 Block Control Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                    |

| 4.3.9 Examples of entering to STOP/STOP-D mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-30                                               |

| 4.3.10 Note of entering to the standby mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                    |

| Chantan 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                    |

| Chapter 5  5. Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-1                                                |

| 5. Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                    |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5-1                                                |

| 5. Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-1<br>5-1                                         |

| 5. Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-1<br>5-1<br>5-2                                  |

| 5. Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-1<br>5-1<br>5-2                                  |

| 5. Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-1<br>5-1<br>5-2<br>5-2                           |

| 5. Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                    |

| 5. Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-1<br>5-2<br>5-2<br>5-6<br>5-6                    |

| 5. Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-1<br>5-2<br>5-2<br>5-6<br>5-6<br>5-9             |

| 5. Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                    |

| 5. Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-15-15-25-25-65-75-95-115-13                      |

| 5. Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-15-15-25-65-75-115-135-15                        |

| 5. Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-15-15-25-65-75-95-135-155-17                     |

| 5. Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-15-15-25-25-65-75-135-155-19                     |

| 5. Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-15-25-25-65-75-115-135-155-175-195-21            |

| 5. Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-15-15-25-25-65-75-115-135-175-195-21             |

| 5. Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-15-15-25-65-75-95-135-155-195-215-23             |

| 5. Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-15-25-25-65-75-95-135-155-195-215-225-24         |

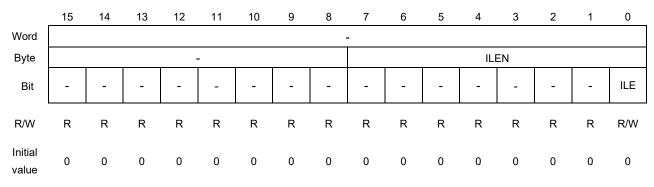

| 5. Interrupts 5.1 General Description 5.1.1 Features 5.2 Description of Registers 5.2.2 Interrupt Enable Register 01 (IE01) 5.2.3 Interrupt Enable Register 23 (IE23) 5.2.4 Interrupt Enable Register 45 (IE45) 5.2.5 Interrupt Enable Register 67 (IE67) 5.2.6 Interrupt Request Register 01 (IRQ01) 5.2.7 Interrupt Request Register 23 (IRQ23) 5.2.8 Interrupt Request Register 45 (IRQ45) 5.2.9 Interrupt Request Register 67 (IRQ67) 5.2.10 Interrupt Level Control Enable Register (ILEN) 5.2.11 Current Interrupt Level Management Register (CIL) 5.2.12 Interrupt Level Control Register 0 (ILC0) 5.2.13 Interrupt Level Control Register 1 (ILC1) 5.2.14 Interrupt Level Control Register 2 (ILC2) 5.2.15 Interrupt Level Control Register 3 (ILC3)                                                                                                                                                                                                                                                                                                           | 5-15-15-25-65-75-95-135-155-195-215-225-245-265-28 |

| 5. Interrupts 5.1 General Description 5.1.1 Features 5.2 Description of Registers 5.2.1 List of Registers 5.2.2 Interrupt Enable Register 01 (IE01) 5.2.3 Interrupt Enable Register 23 (IE23) 5.2.4 Interrupt Enable Register 45 (IE45) 5.2.5 Interrupt Enable Register 67 (IE67) 5.2.6 Interrupt Request Register 01 (IRQ01) 5.2.7 Interrupt Request Register 23 (IRQ23) 5.2.8 Interrupt Request Register 45 (IRQ45) 5.2.9 Interrupt Request Register 47 (IRQ67) 5.2.10 Interrupt Level Control Enable Register (ILEN) 5.2.11 Current Interrupt Level Management Register (CIL) 5.2.12 Interrupt Level Control Register 0 (ILC0) 5.2.13 Interrupt Level Control Register 1 (ILC1) 5.2.14 Interrupt Level Control Register 2 (ILC2) 5.2.15 Interrupt Level Control Register 3 (ILC3) 5.2.16 Interrupt Level Control Register 4 (ILC4)                                                                                                                                                                                                                                  | 5-1                                                |

| 5. Interrupts 5.1 General Description 5.1.1 Features 5.2 Description of Registers 5.2.2 Interrupt Enable Register 01 (IE01) 5.2.3 Interrupt Enable Register 23 (IE23) 5.2.4 Interrupt Enable Register 45 (IE45) 5.2.5 Interrupt Enable Register 67 (IE67) 5.2.6 Interrupt Request Register 01 (IRQ01) 5.2.7 Interrupt Request Register 23 (IRQ23) 5.2.8 Interrupt Request Register 45 (IRQ45) 5.2.9 Interrupt Request Register 67 (IRQ67) 5.2.10 Interrupt Level Control Enable Register (ILEN) 5.2.11 Current Interrupt Level Management Register (CIL) 5.2.12 Interrupt Level Control Register 0 (ILC0) 5.2.13 Interrupt Level Control Register 1 (ILC1) 5.2.14 Interrupt Level Control Register 2 (ILC2) 5.2.15 Interrupt Level Control Register 3 (ILC3)                                                                                                                                                                                                                                                                                                           | 5-1                                                |

| 5. Interrupts 5.1 General Description 5.1.1 Features 5.2 Description of Registers 5.2.2 List of Registers 5.2.2 Interrupt Enable Register 01 (IE01) 5.2.3 Interrupt Enable Register 23 (IE23) 5.2.4 Interrupt Enable Register 45 (IE45) 5.2.5 Interrupt Enable Register 67 (IE67) 5.2.6 Interrupt Request Register 01 (IRQ01) 5.2.7 Interrupt Request Register 23 (IRQ23) 5.2.8 Interrupt Request Register 45 (IRQ45) 5.2.9 Interrupt Request Register 67 (IRQ67) 5.2.10 Interrupt Level Control Enable Register (ILEN) 5.2.11 Current Interrupt Level Control Register 0 (ILC0) 5.2.12 Interrupt Level Control Register 1 (ILC1) 5.2.13 Interrupt Level Control Register 2 (ILC2) 5.2.15 Interrupt Level Control Register 3 (ILC3) 5.2.16 Interrupt Level Control Register 4 (ILC4) 5.2.17 Interrupt Level Control Register 5 (ILC5)                                                                                                                                                                                                                                  | 5-1                                                |

| 5. Interrupts 5.1 General Description 5.1.1 Features 5.2 Description of Registers 5.2.2 List of Registers 5.2.2 Interrupt Enable Register 01 (IE01). 5.2.3 Interrupt Enable Register 23 (IE23). 5.2.4 Interrupt Enable Register 45 (IE45). 5.2.5 Interrupt Enable Register 67 (IE67). 5.2.6 Interrupt Request Register 01 (IRQ01). 5.2.7 Interrupt Request Register 23 (IRQ23). 5.2.8 Interrupt Request Register 45 (IRQ45). 5.2.9 Interrupt Request Register 67 (IRQ67). 5.2.10 Interrupt Level Control Enable Register (ILEN) 5.2.11 Current Interrupt Level Management Register (CIL) 5.2.12 Interrupt Level Control Register 0 (ILC0). 5.2.13 Interrupt Level Control Register 1 (ILC1). 5.2.14 Interrupt Level Control Register 2 (ILC2). 5.2.15 Interrupt Level Control Register 3 (ILC3). 5.2.16 Interrupt Level Control Register 4 (ILC4). 5.2.17 Interrupt Level Control Register 5 (ILC5). 5.2.18 Interrupt Level Control Register 6 (ILC6).                                                                                                                 | 5-1                                                |

| 5. Interrupts 5.1 General Description 5.1.1 Features 5.2 Description of Registers 5.2.2 Interrupt Enable Register 01 (IE01) 5.2.3 Interrupt Enable Register 23 (IE23) 5.2.4 Interrupt Enable Register 45 (IE45) 5.2.5 Interrupt Enable Register 67 (IE67) 5.2.6 Interrupt Request Register 10 (IRQ01) 5.2.7 Interrupt Request Register 23 (IRQ23) 5.2.8 Interrupt Request Register 45 (IRQ45) 5.2.9 Interrupt Request Register 67 (IRQ67) 5.2.10 Interrupt Level Control Enable Register (ILEN) 5.2.11 Current Interrupt Level Management Register (CIL) 5.2.12 Interrupt Level Control Register 0 (ILC0) 5.2.13 Interrupt Level Control Register 1 (ILC1) 5.2.14 Interrupt Level Control Register 3 (ILC2) 5.2.15 Interrupt Level Control Register 3 (ILC3) 5.2.16 Interrupt Level Control Register 4 (ILC4) 5.2.17 Interrupt Level Control Register 5 (ILC5) 5.2.18 Interrupt Level Control Register 6 (ILC6) 5.2.19 Interrupt Level Control Register 6 (ILC5) 5.2.18 Interrupt Level Control Register 7 (ILC7)                                                      | 5-1                                                |

| 5. Interrupts 5.1 General Description 5.1.1 Features 5.2 Description of Registers 5.2.1 List of Registers 5.2.2 Interrupt Enable Register 01 (IE01) 5.2.3 Interrupt Enable Register 23 (IE23) 5.2.4 Interrupt Enable Register 45 (IE45) 5.2.5 Interrupt Enable Register 67 (IE67) 5.2.6 Interrupt Request Register 01 (IRQ01) 5.2.7 Interrupt Request Register 23 (IRQ23) 5.2.8 Interrupt Request Register 45 (IRQ45) 5.2.9 Interrupt Request Register 45 (IRQ67) 5.2.10 Interrupt Level Control Enable Register (ILEN) 5.2.11 Current Interrupt Level Management Register (CIL) 5.2.12 Interrupt Level Control Register 0 (ILC0) 5.2.13 Interrupt Level Control Register 1 (ILC1) 5.2.14 Interrupt Level Control Register 2 (ILC2) 5.2.15 Interrupt Level Control Register 3 (ILC3) 5.2.16 Interrupt Level Control Register 5 (ILC5) 5.2.17 Interrupt Level Control Register 5 (ILC5) 5.2.18 Interrupt Level Control Register 5 (ILC5) 5.2.19 Interrupt Level Control Register 7 (ILC7) 5.2.19 Interrupt Level Control Register 7 (ILC7) 5.3 Description of Operation | 5-1                                                |

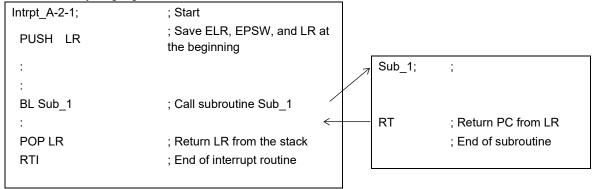

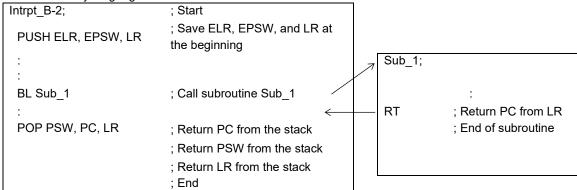

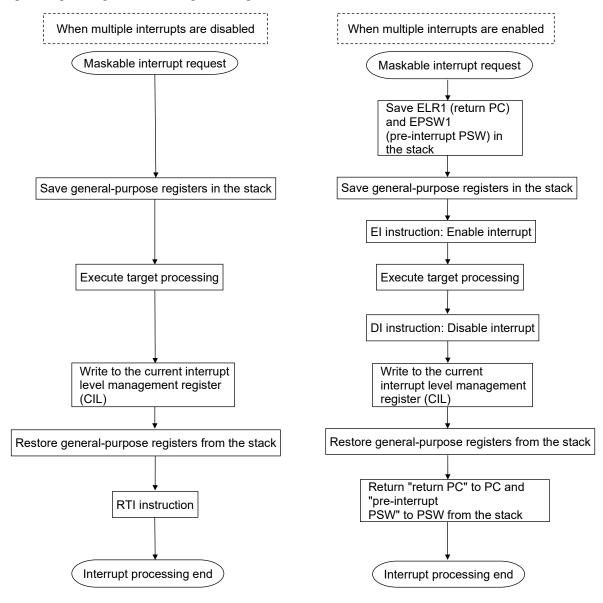

| 5.3.4 Notes on Interrupt Routine (with Interrupt Level Control Disabled)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-42                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| 5.3.5 Flow Charts When Interrupt Level Control Is Enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-47                                                                     |

| 5.3.6 How To Write Interrupt Processing When Interrupt Level Control Enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-49                                                                     |