FEUL62Q2045-02

## ML62Q2033/2035/2043/2045 User's Manual

## Notice

#### **Precaution on using ROHM Products**

1) When using ROHM Products, refer to the latest product information and ensure that usage conditions (absolute maximum ratings<sup>\*1</sup>, recommended operating conditions, etc.) are within the ranges specified. ROHM disclaims any and all liability for any malfunctions, failure or accident arising out of or in connection with the use of ROHM Products outside of such usage conditions specified ranges, or without observing precautions. Even if it is used within such usage conditions specified ranges, semiconductors can break down and malfunction due to various factors. Therefore, in order to prevent personal injury, fire or the other damage from break down or malfunction of ROHM Products, please take safety at your own risk measures such as complying with the derating characteristics, implementing redundant and fire prevention designs, and utilizing backups and fail-safe procedures.

\*1: Absolute maximum ratings: a limit value that must not be exceeded even momentarily.

- 2) The Products specified in this document are not designed to be radiation tolerant.

- 3) Descriptions of circuits, software and other related information in this document are provided only to illustrate the standard operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. And the peripheral conditions must be taken into account when designing circuits for mass production. ROHM disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, and other related information.

- 4) No license, expressly or implied, is granted hereby under any intellectual property rights or other rights of ROHM or any third party with respect to ROHM Products or the information contained in this document (including but not limited to, the Product data, drawings, charts, programs, algorithms, and application examples, etc.). Therefore, ROHM shall have no responsibility whatsoever for any dispute, concerning such rights owned by third parties, arising out of the use of such technical information.

- 5) ROHM intends our Products to be used in a way indicated in this document. Please be sure to contact a ROHM sales office if you consider the use of our Products in different way from original use indicated in this document. For use of our Products in medical systems, please be sure to contact a ROHM representative and must obtain written agreement. Do not use our Products in applications which may directly cause injuries to human life, and which require extremely high reliability, such as aerospace equipment, nuclear power control systems, and submarine repeaters, etc. ROHM disclaims any and all liability for any losses and damages incurred by you or third parties arising by using the Product for purposes not intended by us without our prior written consent.

- 6) Please use the Products in accordance with any applicable environmental laws and regulations, such as the RoHS Directive. ROHM shall have no responsibility for any damages or losses resulting non-compliance with any applicable laws or regulations.

- 7) When providing our Products and technologies contained in this document to other countries, you must abide by the procedures and provisions stipulated in all applicable export laws and regulations, including without limitation the US Export Administration Regulations and the Foreign Exchange and Foreign Trade Act.

- 8) Please contact a ROHM sales office if you have any questions regarding the information contained in this document or ROHM's Products.

- 9) This document, in part or in whole, may not be reprinted or reproduced without prior consent of ROHM.

(Note) "ROHM" as used in this document means ROHM Co., Ltd.

### **Other Precaution**

- 1) All information contained in this document is subject to change for the purpose of improvement, etc. without any prior notice. Before purchasing or using ROHM Products, please confirm the latest information with a ROHM sales office.

- 2) ROHM has used reasonable care to ensure the accuracy of the information contained in this document, however, ROHM shall have no responsibility for any damages, expenses or losses arising from inaccuracy or errors of such information.

LTSZ08023 • 01 • 003

## Notes for product usage

Notes on this page are applicable to the all ROHM microcontroller products. For individual notes on each RHOM microcontroller product, refer to [Note] in the chapters of each user's manual.

The individual notes of each user's manual take priority over those contents in this page if they are different.

| 1. | HANDLING OF UNUSED INPUT PINS<br>Fix the unused input pins to the power pin or GND to prevent to cause the device performing wrong operation or<br>increasing the current consumption due to noise, etc. If the handlings for the unused pins are described in the chapters,<br>follow the instruction.                                                                                                                                                                                                                                                                                     |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2. | STATE AT POWER ON<br>At the power on, the data in the internal registers and output of the ports are undefined until the power supply voltage<br>reaches to the recommended operating condition and "L" level is input to the reset pin.<br>On ROHM microcontroller products that have the power on reset function, the data in the internal registers and output<br>of the ports are undefined until the power on reset is generated.<br>Be careful to design the application system does not work incorrectly due to the undefined data of internal registers and<br>output of the ports. |

| 3. | ACCESS TO UNUSED MEMORY<br>If reading from unused address area or writing to unused address area of the memory, the operations are not guaranteed.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4. | CHARACTERISTICS DIFFERENCE BETWEEN THE PRODUCT<br>Electrical characteristics, noise tolerance, noise radiation amount, and the other characteristics are different from each<br>microcontroller product.<br>When replacing from other product to ROHM microcontroller products, please evaluate enough the apparatus/system<br>which implemented ROHM microcontroller products.                                                                                                                                                                                                             |

| 5. | USE ENVIRONMENT<br>When using ROHM microcontroller products in a high humidity environment and an environment where dew<br>condensation, take moisture-proof measures.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Classification | Notation               | Description                                                                                                                       |

|----------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Numeric value  | XXh, XXH, 0xXX         | Indicates a hexadecimal number.                                                                                                   |

| Unit           | word, W                | 1 word = 16 bits                                                                                                                  |

|                | byte, B                | 1 byte = 8 bits                                                                                                                   |

|                | nibble, N              | 1 nibble = 4 bits                                                                                                                 |

|                | mega-, M               | 10 <sup>6</sup>                                                                                                                   |

|                | kilo-, K               | 2 <sup>10</sup> = 1024                                                                                                            |

|                | kilo-, k               | 10 <sup>3</sup> = 1000                                                                                                            |

|                | milli-, m              | 10 <sup>-3</sup>                                                                                                                  |

|                | micro-, μ              | 10 <sup>-6</sup>                                                                                                                  |

|                | nano-, n               | 10 <sup>-9</sup>                                                                                                                  |

|                | second, s (lower case) | second                                                                                                                            |

| Terminology    | "H" level              | Indicates high level voltage VIH and VOH as specified by the electrical characteristics in the data-sheet.                        |

|                | "L" level              | Indicates low level voltage $V_{\text{IL}}$ and $V_{\text{OL}}$ as specified by the electrical characteristics in the data-sheet. |

|                | SFR                    | Special function register. It is control register for system or peripherals.                                                      |

## Notation

• Register description

"R/W" indicates that Read/Write attribute. "R" indicates that data can be read and "W" indicates that data can be written. "R/W" indicates that data can be read or written.

MSB: The highest bit of 16-bit register LSB: The lowest bit of 16-bit register

Registers that have a word symbol allow the word-access. If writing or reading the registers not using the word symbol, specify the even number addresses.

|                  | <br>   |                  |           | Invalic   | l bit: Th | nis bit re | eturns "  | 0" for re | eading | and writ | ing to t | his bit i | s ignore | ed. |   |            |

|------------------|--------|------------------|-----------|-----------|-----------|------------|-----------|-----------|--------|----------|----------|-----------|----------|-----|---|------------|

|                  |        | Word symbol name |           |           |           |            |           |           |        |          |          |           |          |     |   |            |

|                  | Ì      | Byte symbol name |           |           |           |            |           |           |        |          |          |           |          |     |   |            |

|                  |        | Bit syml         | ool nam   | ne        |           |            |           | <br> <br> |        |          |          |           |          |     |   |            |

|                  | 15     | 14               | 13        | 12        | 11        | 10         | 9         | 8         | 7      | 6        | 5        | 4         | 3        | 2   | 1 | 0          |

| Word             |        | 1                |           |           |           |            | -         | FHCK      |        |          |          |           |          |     |   |            |

| Byte             | i<br>I | FHCKMODH         |           |           |           |            |           | FHCKMODL  |        |          |          |           |          |     |   |            |

| Bit              |        | OUTC<br>2        | OUTC<br>1 | OUTC<br>0 | _         | SYSC<br>2  | SYSC<br>1 | SYSC<br>0 | _      | _        | _        | Ι         | -        | Ι   | Ι | HOS<br>CM0 |

| R/W              | R      | R/W              | R/W       | R/W       | R         | R/W        | R/W       | R/W       | R      | R        | R        | R         | R        | R   | R | R/W        |

| Initial<br>value | 0      | 1                | 0         | 0         | 0         | 1          | 0         | 0         | 0      | 0        | 0        | 0         | 0        | 0   | 0 | 0          |

|                  |        |                  |           |           |           |            |           |           |        |          |          |           |          |     |   |            |

|                  | L      | J                |           |           | !         | L          | /         |           | <br>   | !        |          | !         | J        |     | Ł |            |

Initial value after the system reset

#### ML62Q2033/35/43/45 User's Manual Contents

## Table of Contents

| Chapter 1 Overview                              |     |

|-------------------------------------------------|-----|

| 1. Overview                                     | 1-1 |

| 1.1 Features                                    |     |

| 1.1.1 How To Read The Part Number               |     |

| 1.1.2 Main Function List                        |     |

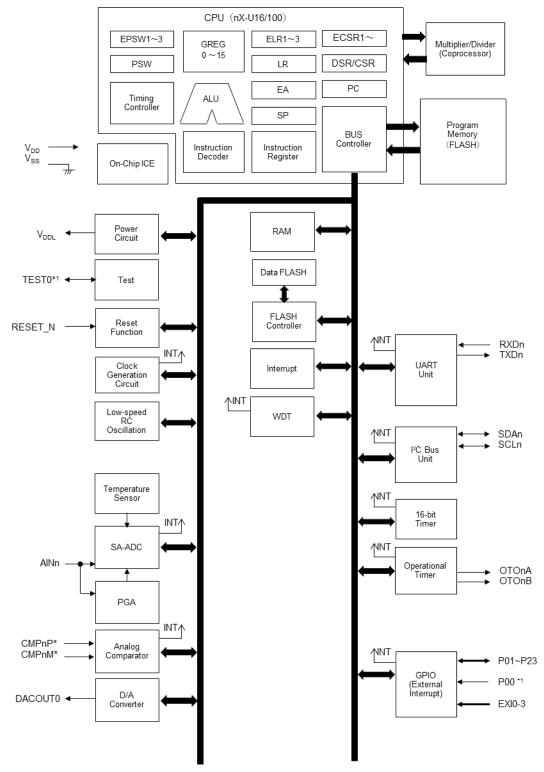

| 1.2 Block Diagram                               |     |

| 1.2.1 Block Diagram of ML62Q2033/2035/2043/2045 |     |

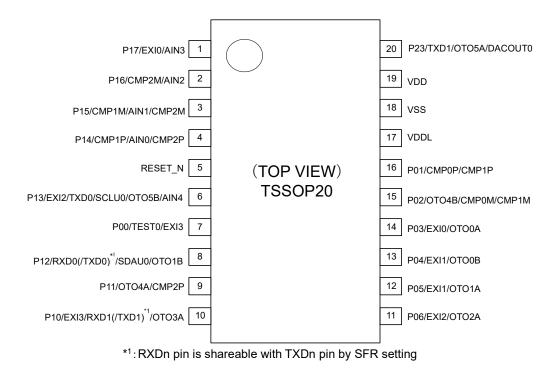

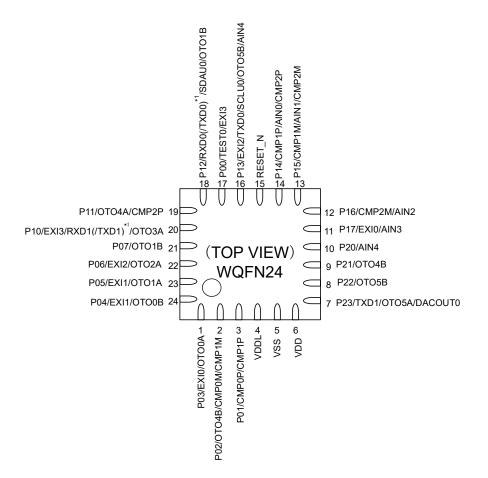

| 1 3 Pin                                         | 1-8 |

| 1.3.1 Pin Layout                                |     |

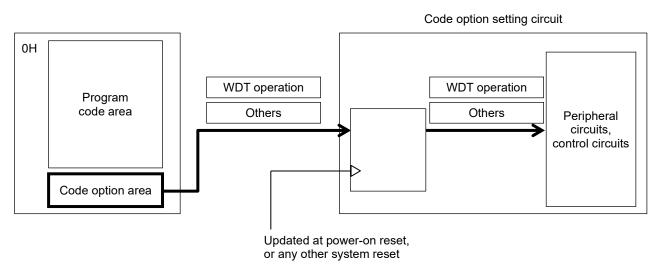

| 1.3.1.1 ML62Q2035/2033 : 20 pin TSSOP           |     |

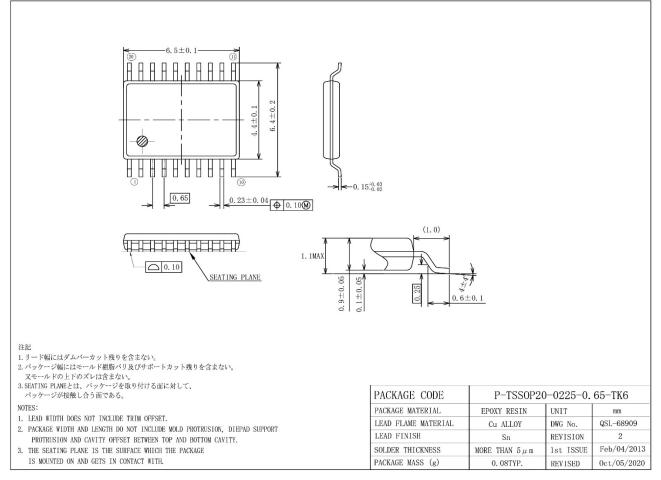

| 1.3.1.2 ML62Q2045/2043 : 24 pin WQFN            |     |

| 1.3.2 Pin List                                  |     |

| 1.3.3 Pin Description                           |     |

| 1.3.4 Termination of Unused Pins                |     |

#### Chapter 2 CPU and Memory Space

| 2. CPU and Memory Space                                                | 2-1  |

|------------------------------------------------------------------------|------|

| 2.1 General Description                                                | 2-1  |

| 2.2 CPU nX-U16/100                                                     |      |

| 2.2.1 Wait Mode and No-wait Mode                                       |      |

| 2.2.2 Notes When Executing SB/RB Instruction                           |      |

| 2.2.3 Notes on the Description of Read-modify-write                    |      |

| 2.3 Coprocessor                                                        |      |

| 2.3.1 Multiplier/Divider                                               |      |

| 2.3.2 List of Coprocessor General-purpose Registers                    |      |

| 2.3.2.1 A, B, C, D Registers (CR0 to CR7)                              |      |

| 2.3.2.2 Operation Mode Register (CR8), Operation Status Register (CR9) |      |

| 2.3.2.3 Coprocessor ID Register (CR15)                                 |      |

| 2.3.3 How to Use Multiplier/Divider                                    |      |

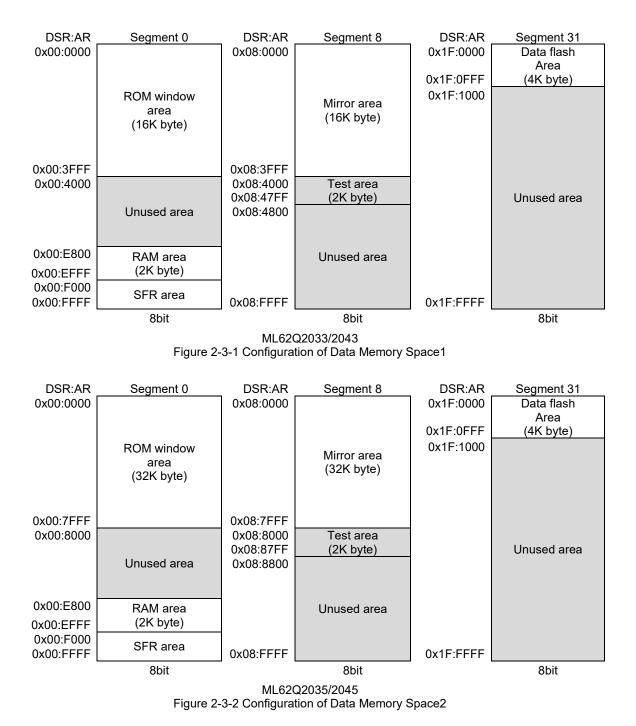

| 2.4 Memory Space                                                       |      |

| 2.5 Program Memory Space                                               |      |

| 2.6 Data Memory Space                                                  |      |

| 2.7 Description of Registers                                           |      |

| 2.7.1 List of Registers                                                |      |

| 2.7.2 Data Segment Register (DSR)                                      |      |

| 2.7.3 Flash Remap Address Register (REMAPADD)                          |      |

| 2.7.4 Reserved register 1                                              |      |

| 2.7.5 Reserved register 2                                              |      |

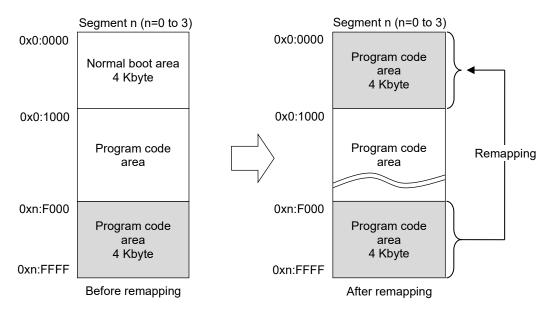

| 2.8 Remapping Function                                                 |      |

| 2.8.1 Description of Remapping Function                                |      |

| 2.8.2 Software Remap                                                   |      |

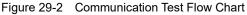

| 2.8.3 Code Option Remap                                                | 2-22 |

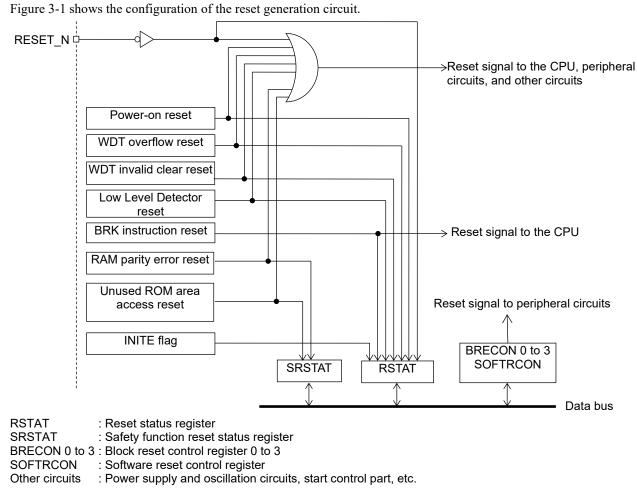

### **Chapter 3 Reset Function**

| 3. Reset Function                                    | 3-1 |

|------------------------------------------------------|-----|

| 3.1 General Description                              |     |

| 3.1.1 Features                                       |     |

| 3.1.2 Configuration                                  |     |

| 3.1.3 List of Pins                                   |     |

| 3.2 Description of Registers                         |     |

| 3.2.1 List of Registers                              |     |

| 3.2.2 Reset Status Register (RSTAT)                  |     |

| 3.2.3 Safety Function Reset Status Register (SRSTAT) | 3-5 |

| 3.3 Description of Operation                         |     |

| 3.3.1 Operation of Reset Function                    |     |

| 3.3.2 System Reset Mode                              | 3-7 |

| 3.3.3 Reset Input Pin Reset                          | 3-7 |

| FEUL62Q2045 Contents-1                               |     |

#### ML62Q2033/35/43/45 User's Manual Contents

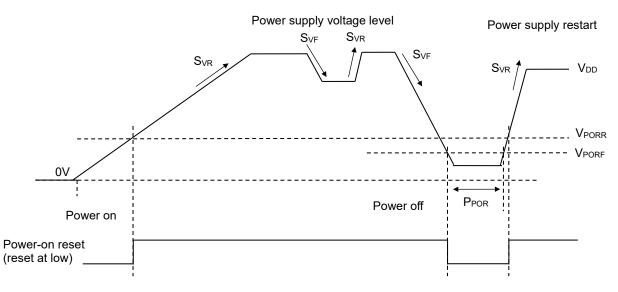

| 3.3.4 Power-on Reset                                                                                                      |     |

|---------------------------------------------------------------------------------------------------------------------------|-----|

| Chapter 4 Power Management                                                                                                |     |

| 4. Power Management                                                                                                       | 4-1 |

| 4.1 General Description                                                                                                   |     |

| 4.1.1 Features                                                                                                            |     |

| 4.1.2 Configuration                                                                                                       |     |

| 4.1.3 List of Pins                                                                                                        |     |

| 4.2 Description of Registers                                                                                              |     |

| 4.2.1 List of Registers                                                                                                   |     |

| 4.2.2 Stop Code Acceptor (STPACP)                                                                                         |     |

| 4.2.3 Standby Control Register (SBYCON)                                                                                   |     |

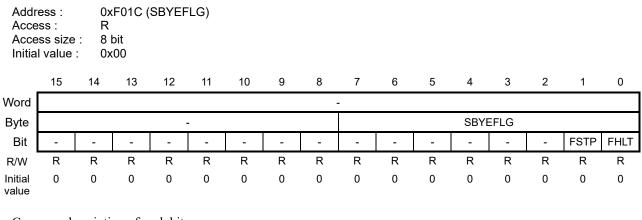

| 4.2.4 Standby Prohibition Flag Register (SBYEFLG)                                                                         |     |

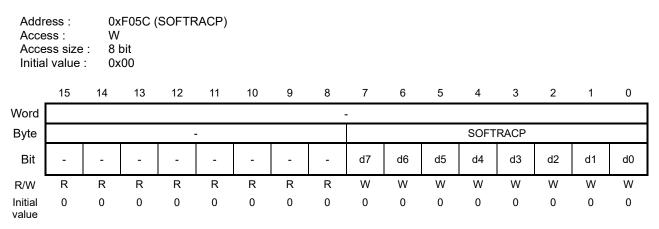

| 4.2.5 Software Reset Acceptor (SOFTRACP)                                                                                  |     |

| 4.2.6 Software Reset Control Register (SOFTRCON)                                                                          |     |

| 4.2.7 Block Clock Control Register 0 (BCKCON0)                                                                            |     |

| 4.2.8 Block Clock Control Register 1 (BCKCON1)                                                                            |     |

| 4.2.9 Block Clock Control Register 2 (BCKCON2)                                                                            |     |

| 4.2.10 Block Clock Control Register 3 (BCKCON2)                                                                           |     |

| 4.2.10 Block Coltrol Register 9 (BERCON9)                                                                                 |     |

|                                                                                                                           |     |

| 4.2.12 Block Reset Control Register 1 (BRECON1)                                                                           |     |

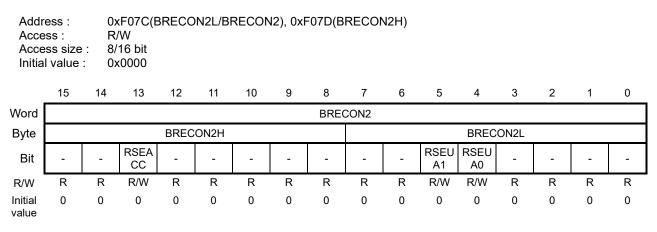

| <ul><li>4.2.13 Block Reset Control Register 2 (BRECON2)</li><li>4.2.14 Block Reset Control Register 3 (BRECON3)</li></ul> |     |

|                                                                                                                           |     |

| 4.3 Description of Operation                                                                                              |     |

| 4.3.1 Program Run Mode                                                                                                    |     |

| 4.3.2 Standby Mode                                                                                                        |     |

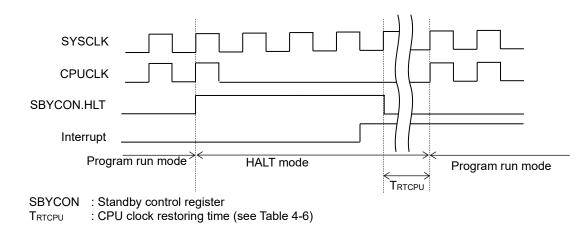

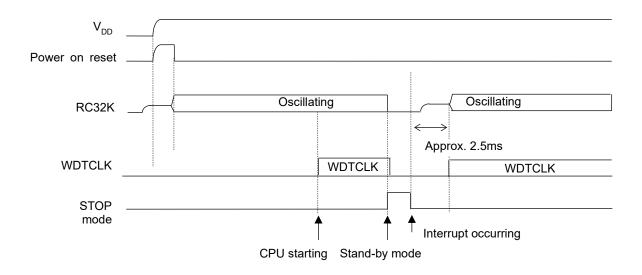

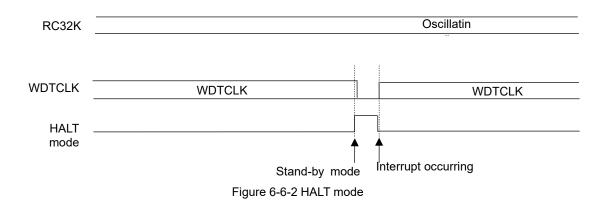

| 4.3.2.1 HALT Mode                                                                                                         |     |

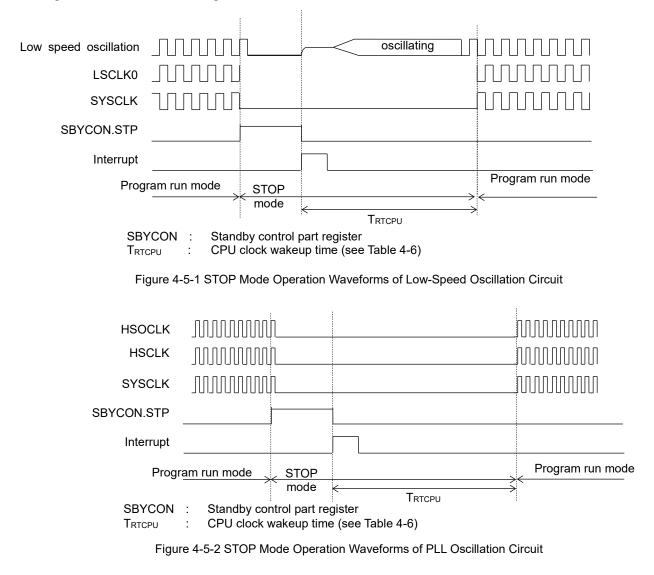

| 4.3.2.2 STOP Mode                                                                                                         |     |

| 4.3.2.3 Note of entering to the standby mode                                                                              |     |

| 4.3.2.4 Note on Return Operation from Standby Mode                                                                        |     |

| 4.3.2.5 Operation of Each Function in Standby Mode                                                                        |     |

| 4.3.2.6 Wake-up Time from Standby Mode                                                                                    |     |

| 4.3.3 Block Control Function                                                                                              |     |

| 4.3.4 Internal Power Supply Voltage                                                                                       |     |

| Chapter 5 Interrupts                                                                                                      |     |

| 5. Interrupt                                                                                                              |     |

| 5.1 General Description                                                                                                   |     |

| 5.1.1 Features.                                                                                                           |     |

| 5.2 Description of Registers                                                                                              |     |

| 5.2.1 List of Registers                                                                                                   |     |

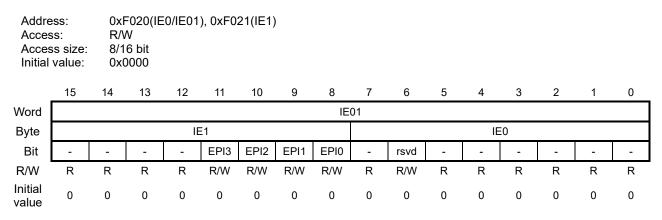

| 5.2.2 Interrupt Enable Register 01 (IE01)                                                                                 |     |

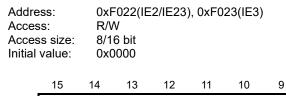

| 5.2.3 Interrupt Enable Register 23 (IE23)                                                                                 |     |

| 5.2.4 Interrupt Enable Register 45 (IE45)                                                                                 |     |

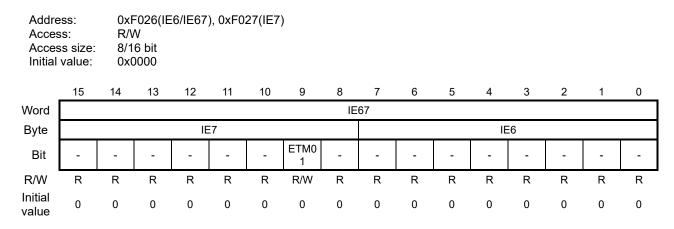

| 5.2.5 Interrupt Enable Register 67 (IE67)                                                                                 |     |

| 5.2.6 Interrupt Request Register 01 (IRQ01)                                                                               |     |

| 5.2.7 Interrupt Request Register 23 (IRQ23)                                                                               |     |

| 5.2.8 Interrupt Request Register 45 (IRQ45)                                                                               |     |

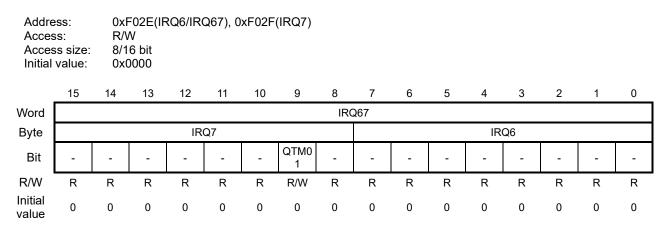

| 5.2.9 Interrupt Request Register 67 (IRQ67)                                                                               |     |

| 5.2.10 Interrupt Level Control Enable Register (ILEN)                                                                     |     |

| 5.2.10 Interrupt Level Control Enable Register (ILEN)                                                                     |     |

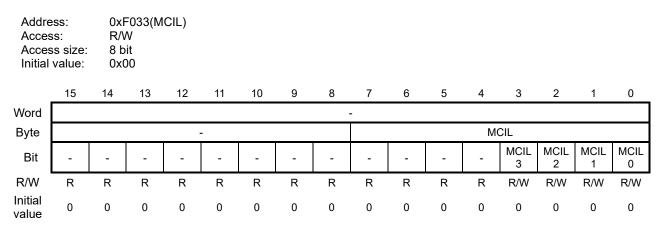

| 5.2.12 Masking Interrupt Level Register (MCIL)                                                                            |     |

|                                                                                                                           |     |

| 5.2.13 Interrupt Level Control Register 0 (ILC0)                                                                          |     |

| 5.2.14 Interrupt Level Control Register 1 (ILC1)                                                                          |     |

| 5.2.15 Interrupt Level Control Register 2 (ILC2)                                                                          |     |

| 5.2.16 Interrupt Level Control Register 3 (ILC3)                                                                          |     |

| 5.2.17 Interrupt Level Control Register 4 (ILC4)                                                                          |     |

5.2.18 Interrupt Level Control Register 5 (ILC5)

5-21

5.2.19 Interrupt Level Control Register 6 (ILC6)

5-22

#### ML62Q2033/35/43/45 User's Manual Contents

| 5.2.20 Interrupt Level Control Register 7 (ILC7)                             |  |

|------------------------------------------------------------------------------|--|

| 5.3 Description of Operation                                                 |  |

| 5.3.1 Maskable Interrupt Processing                                          |  |

| 5.3.2 Non-Maskable Interrupt Processing                                      |  |

| 5.3.3 Software Interrupt Processing                                          |  |

| 5.3.4 Notes on Interrupt Routine (with Interrupt Level Control Disabled)     |  |

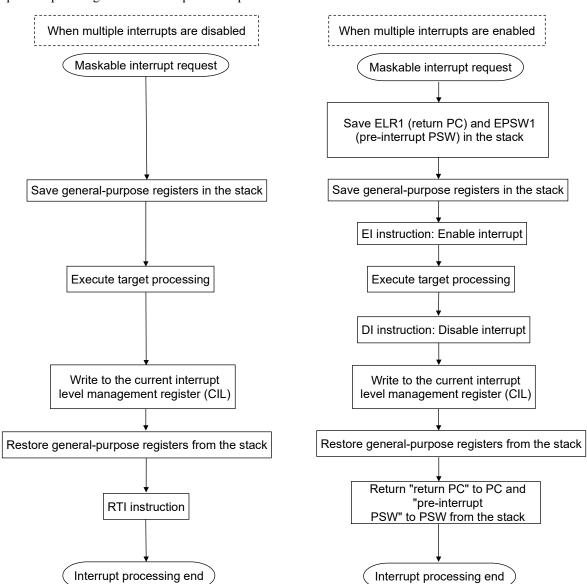

| 5.3.5 Flow Charts When Interrupt Level Control Is Enabled                    |  |

| 5.3.6 How To Write Interrupt Processing When Interrupt Level Control Enabled |  |

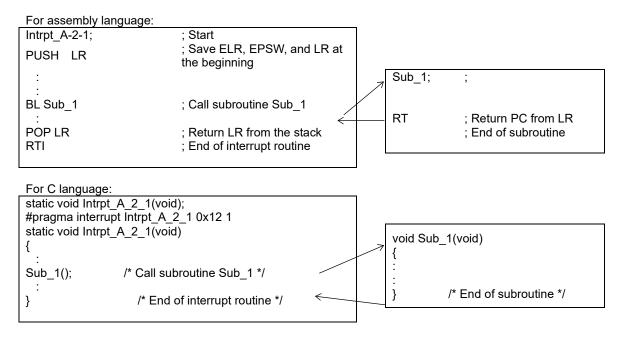

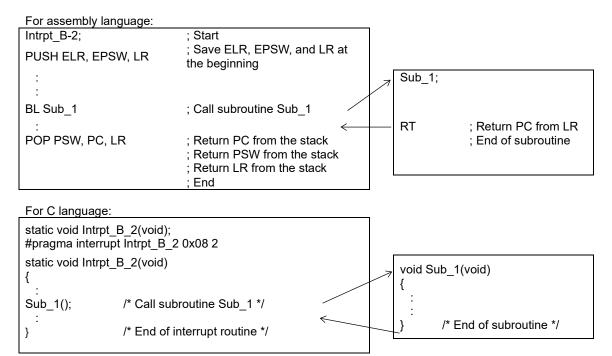

| 5.3.6.1 Description of Interrupt Function to Disable Multiple Interrupts     |  |

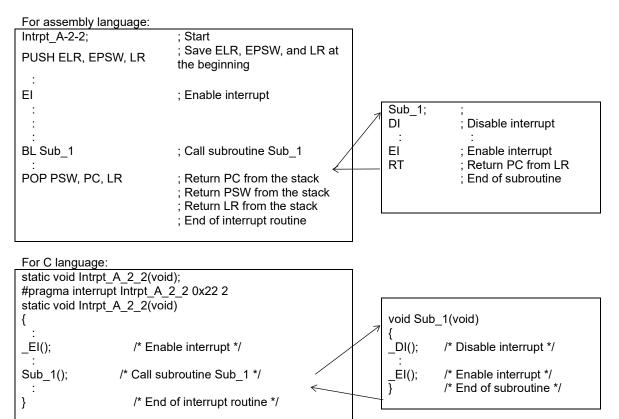

| 5.3.6.2 Description of Interrupt Function to Enable Multiple Interrupts      |  |

| 5.3.7 Interrupt Disable State                                                |  |

| 5.3.8 Writing to IRQ01/IRQ23/IRQ45/IRQ67                                     |  |

| 5.3.9 16-bit timer 0 Interrupt                                               |  |

|                                                                              |  |

#### **Chapter 6 Clock generation Circuit**

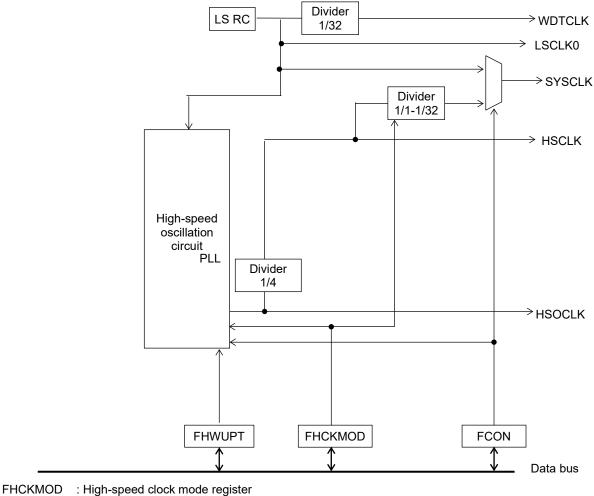

| 6. Clock Generation Circuit                                   | 6-1  |

|---------------------------------------------------------------|------|

| 6.1 General Description                                       | 6-1  |

| 6.1.1 Features                                                | 6-1  |

| 6.1.2 Configuration<br>6.1.3 List of Pins                     |      |

| 6.1.3 List of Pins                                            | 6-3  |

| 6.2 Description of Registers                                  | 6-4  |

| 6.2 Description of Registers                                  | 6-4  |

| 6.2.2 High-Speed Clock Mode Register (FHCKMOD)                | 6-5  |

| 6.2.3 Clock Control Register (FCONW)                          | 6-6  |

| 6.2.4 High-Speed Clock Wake-up Time Setting Register (FHWUPT) | 6-7  |

| 6.3 Description of Operation                                  | 6-8  |

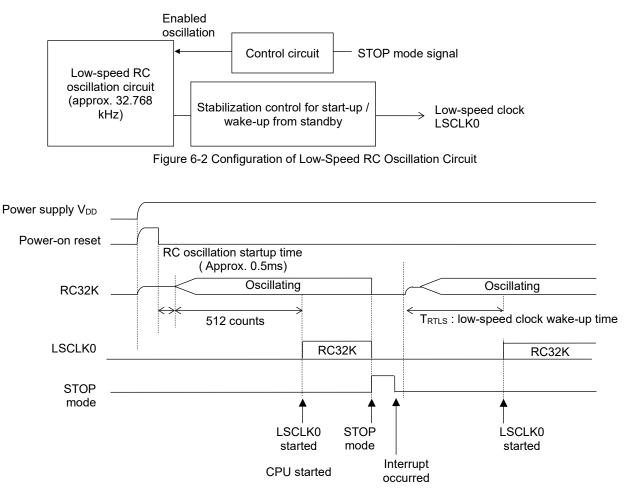

| 6.3.1 Low-Speed Clock                                         | 6-8  |

| 6.3.1.1 Low-Speed RC Oscillation Circuit                      | 6-8  |

| 6.3.2 High-speed Clock                                        | 6-9  |

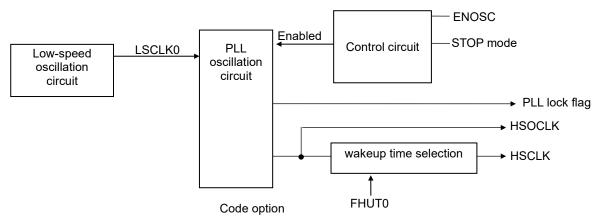

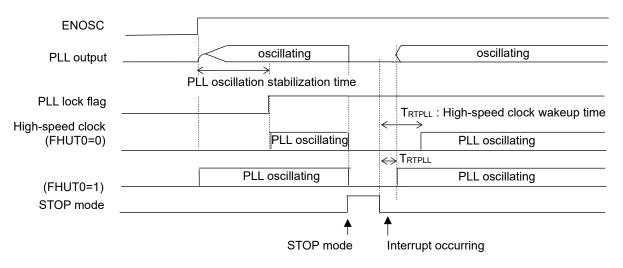

| 6.3.2.1 PLL Oscillation Circuit                               | 6-9  |

| 6.3.2.2 High-speed Clock Control                              | 6-10 |

| 6.3.3 WDT Clock (WDTCLK)                                      | 6-11 |

| 6.3.4 System Clock                                            |      |

|                                                               |      |

#### Chapter 7 (Skip number)

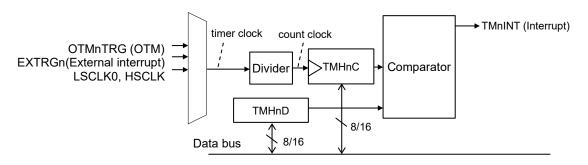

### Chapter 8 16-Bit Timer

| 8. 16-Bit Timer                                    | 8-1 |

|----------------------------------------------------|-----|

| 8.1 General Description                            |     |

| 8.1.1 Features                                     |     |

| 8.1.2 Configuration                                |     |

| 8.2 Description of Registers                       |     |

| 8.2.1 List of Registers                            | 8-3 |

| 8.2.2 16-Bit Timer n Data Register (TMHnD :n=0)    |     |

| 8.2.3 16-Bit Timer n Counter Register (TMHnC :n=0) |     |

| 8.2.4 16-Bit Timer n Mode Register (TMHnMOD :n=0)  |     |

| 8.2.5 16-Bit Timer Start Register (TMHSTR)         |     |

| 8.2.6 16-Bit Timer Stop Register (TMHSTP)          |     |

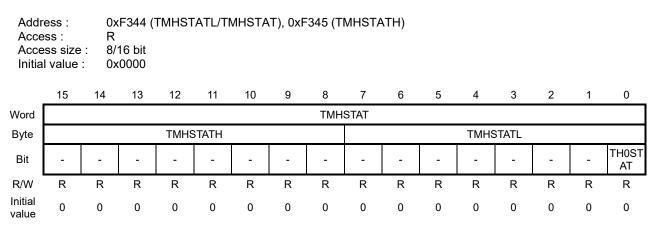

| 8.2.7 16-Bit Timer Status Register (TMHSTAT)       |     |

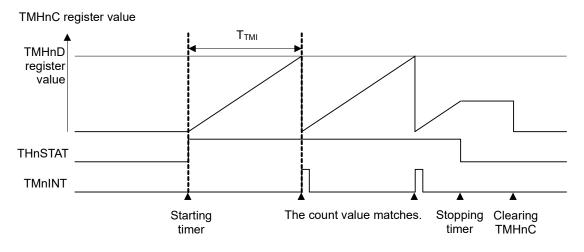

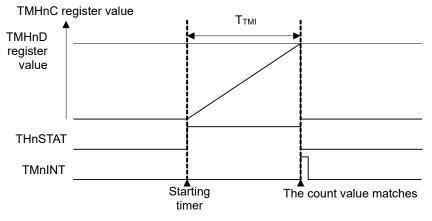

| 8.3 Description of Operation                       |     |

| 8.3.1 Operation Mode                               |     |

| 8.3.1.1 Repeat Mode                                |     |

| 8.3.1.2 One-shot Mode                              |     |

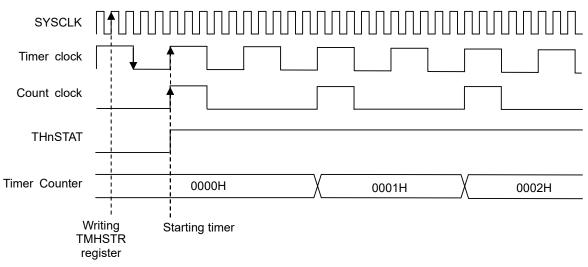

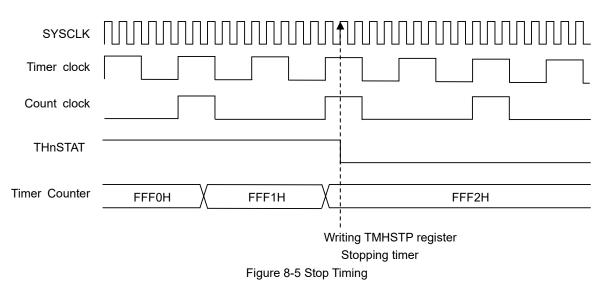

| 8.3.2 Start/Stop Timing                            |     |

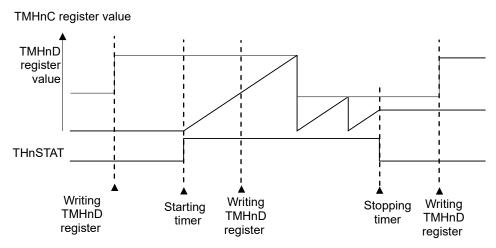

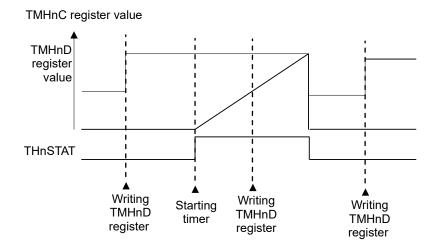

| 8.3.3 TMHnD Register Update Timing                 |     |

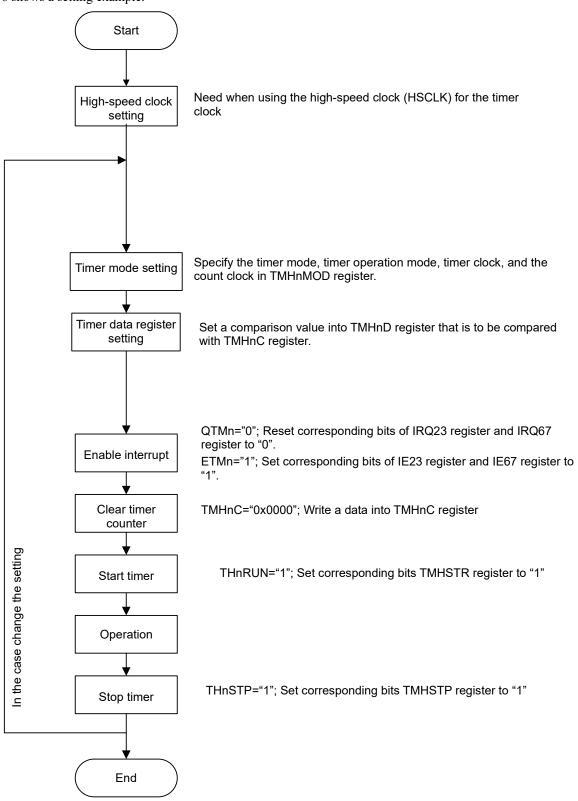

| 8.3.4 Setting Example                              |     |

#### **Chapter 9 Operational timer**

FEUL62Q2045

#### ML62Q2033/35/43/45 User's Manual Contents

| 9. Operational timer                                                                     |      |

|------------------------------------------------------------------------------------------|------|

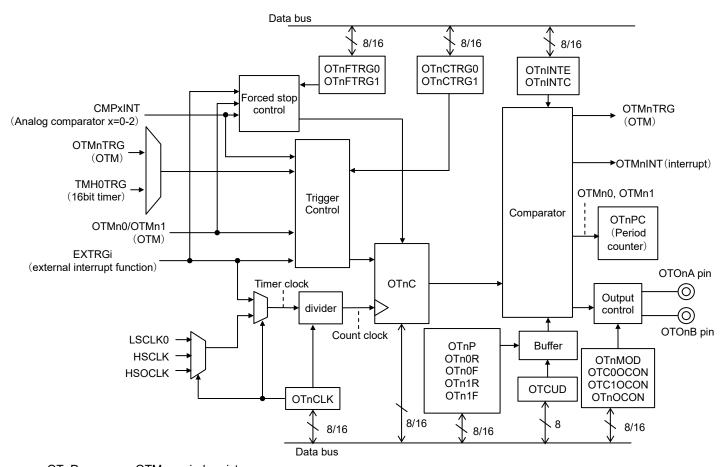

| 9.1 General Description                                                                  |      |

| 9.1.1 Features                                                                           |      |

| 9.1.2 Configuration                                                                      |      |

| 9.1.3 Pin list                                                                           |      |

| 9.2 Register description                                                                 |      |

| 9.2.1 List of register                                                                   |      |

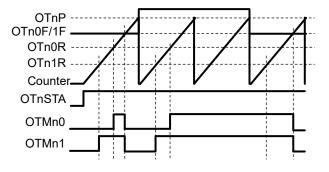

| 9.2.2 OTMn cycle register OTnP: n=0 to 5)                                                |      |

| 9.2.3 OTMn0 Rise Point register (OTn0R:n=0 to 5)                                         |      |

| 9.2.4 OTMn0 Fall Point register (OTn0F: n=0 to 5)                                        |      |

| 9.2.5 OTMn1 Rise Point register (OTn1R:n=0, 1, 4, 5)                                     |      |

| 9.2.6 OTMn1 Fall Point register (OTn1F:n=0, 1, 4, 5)                                     |      |

| 9.2.7 OTMn counter register (OTnC: n=0 to 5)                                             | 9-15 |

| 9.2.8 OTMn status register (OTnSTAT: n=0 to 5)                                           |      |

| 9.2.9 OTMn mode register (OTnMOD: n=0 to 5)                                              |      |

| 9.2.10 OTMn Output logic control register (OTnOCON: n=0 to 5)                            |      |

| 9.2.11 OTMn cycle stop timing register (OTnSCLR: n=0 to 5)                               |      |

| 9.2.12 OTMn clock register (OTnCLK: n=0 to 5)                                            |      |

| 9.2.13 OTMn Counter control trigger register 0 register (OTnCTRG0:n=0 to 5)              |      |

| 9.2.14 OTMn Counter control trigger 1 register (OTnCTRG1:n=0 to 5)                       |      |

| 9.2.15 OTMn Forced stop control trigger 0 register (OTnFTRG0: n=0 to 5)                  |      |

| 9.2.16 OTMn Forced stop control trigger 1 register (OTnFTRG1: n=0 to 5)                  |      |

| 9.2.17 OTMn interrupt enable register (OTnINTE:n=0 to 5)                                 |      |

| 9.2.18 OTMn interrupt status register (OTnINTE: n=0 to 5)                                |      |

| 9.2.19 OTMn interrupt clear register L/H (OTNINTCL, OTNINTCH : n=0 to 5)                 |      |

|                                                                                          |      |

| 9.2.20 OTM common update register (OTCUD)                                                |      |

| 9.2.21 OTM Common control register (OTCCON)<br>9.2.22 OTM Common start register (OTCSTR) |      |

| 9.2.23 OTM Common stor register (OTCSTR)                                                 |      |

| 9.2.23 OTM Common stop register (OTCSTP)                                                 |      |

| 9.2.25 OTM Common break control register (OTCBRK)                                        |      |

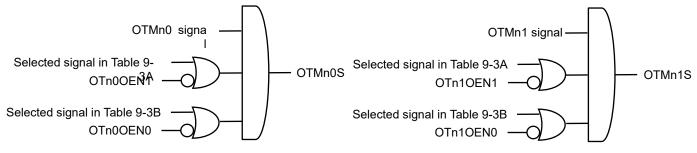

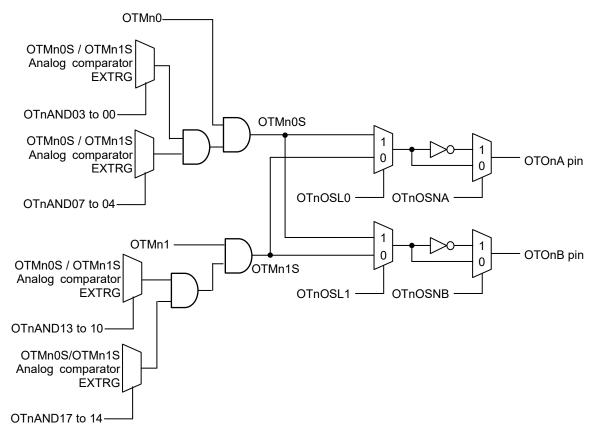

| 9.2.26 OTM common OTMn0 output control register (OTC00CON)                               |      |

| 9.2.27 OTM common OTMn1 output control register (OTC10CON)                               |      |

| 9.2.28 OTM Common cycle interlocking control register (OTCPC)                            |      |

| 9.3 Description of operation                                                             |      |

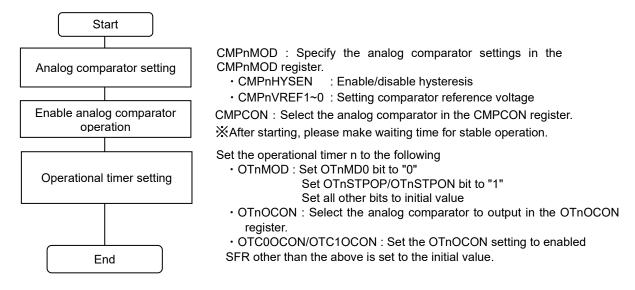

| 9.3.1 Common sequence (Initial settings common to all modes)                             |      |

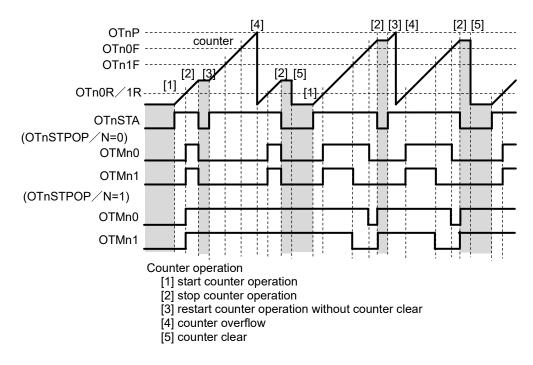

| 9.3.2 Counter operation (Common to all modes)                                            |      |

| 9.3.2.1 Count start/stop by software                                                     |      |

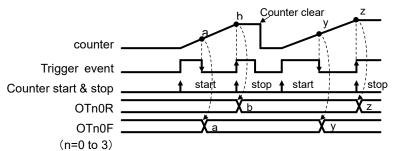

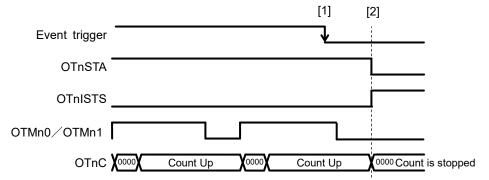

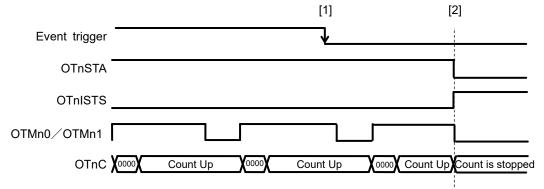

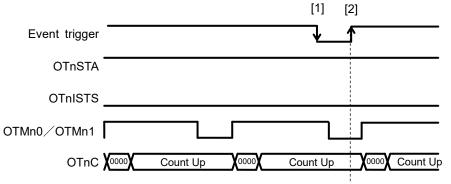

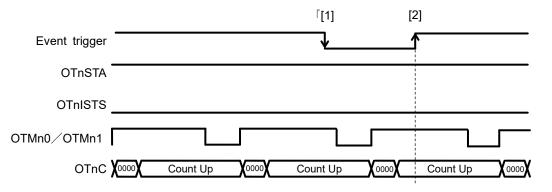

| 9.3.2.2 Start/Stop by Trigger event                                                      |      |

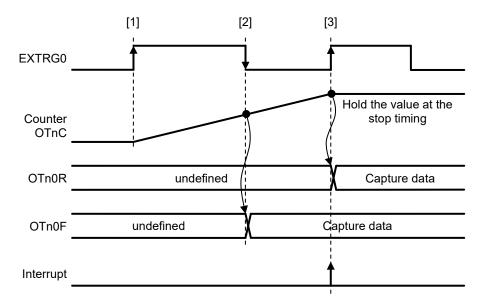

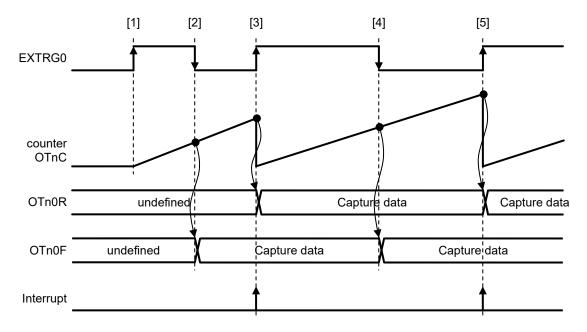

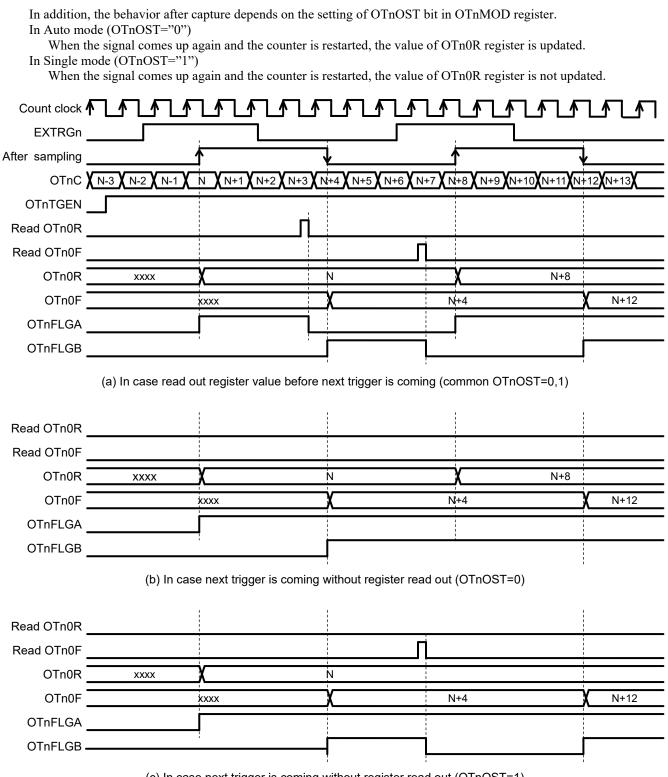

| 9.3.3 CAPTURE mode operation                                                             |      |

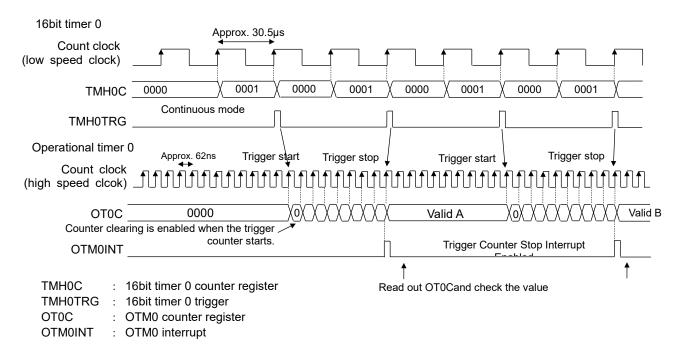

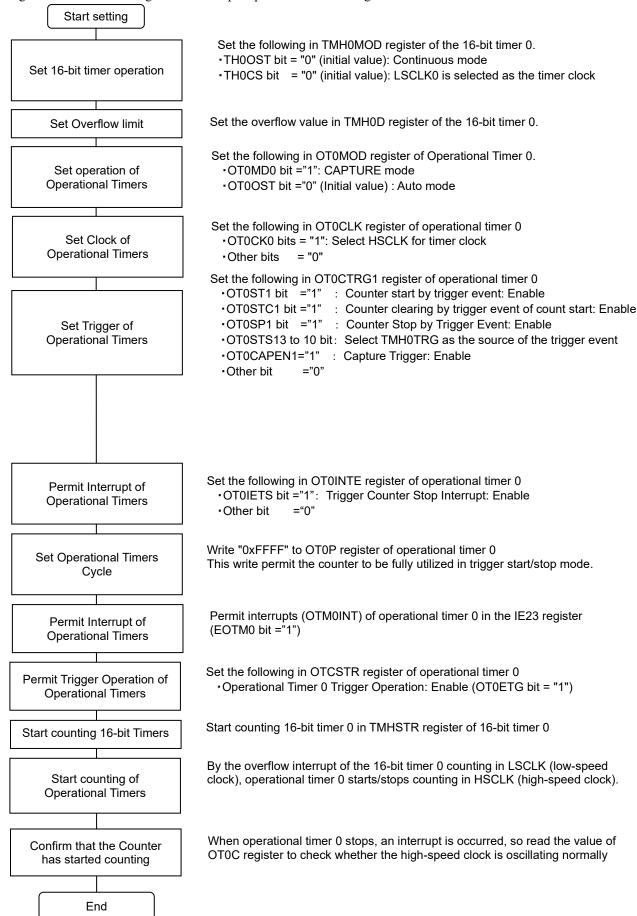

| 9.3.3.1 Example of CAPTURE mode operation                                                | 9-49 |

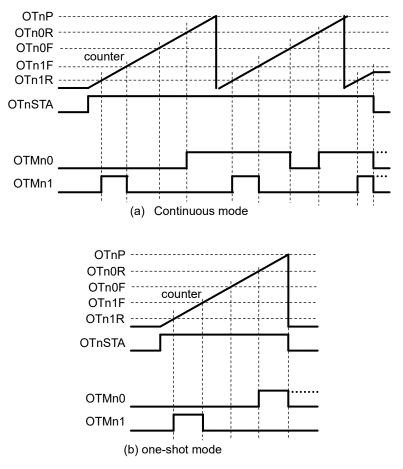

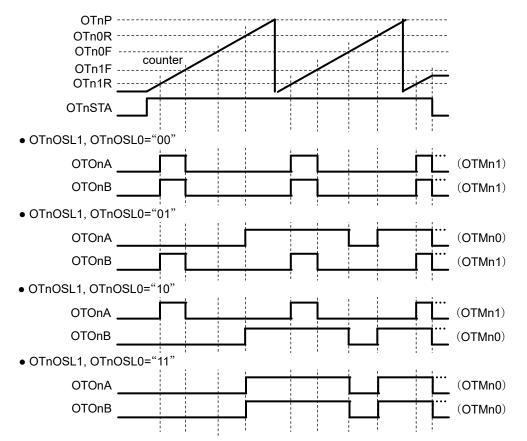

| 9.3.4 PWM mode operation                                                                 |      |

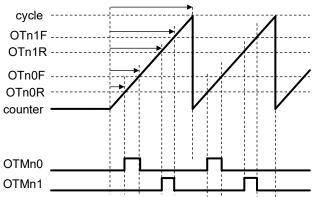

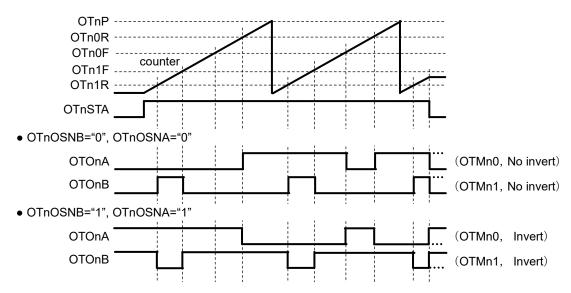

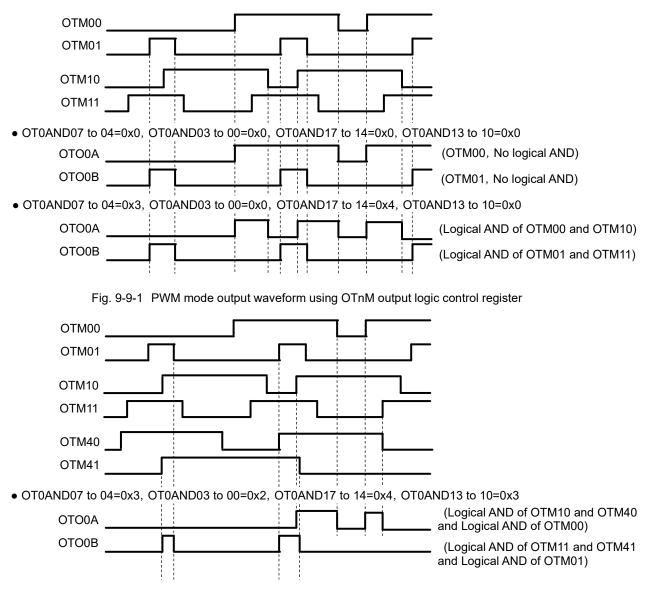

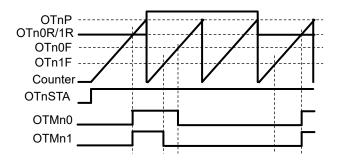

| 9.3.4.1 PWM mode output waveform                                                         |      |

| 9.3.5 PWM duty setting                                                                   |      |

| 9.3.5.1 Output waveform control when $Duty = 100\%$ , 0%                                 |      |

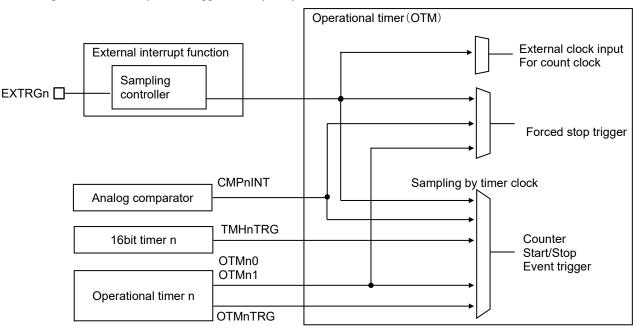

| 9.3.6 Control of External clock input / Event trigger / Forced stop trigger              |      |

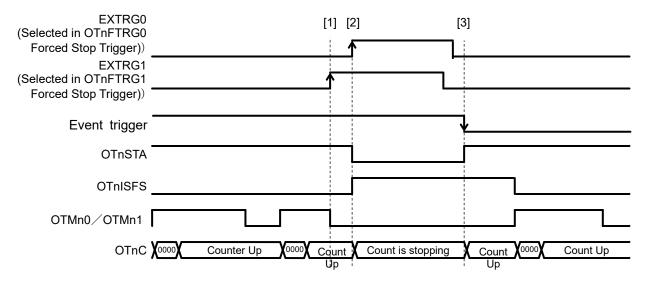

| 9.3.6.1 Start/Stop operation by event trigger                                            |      |

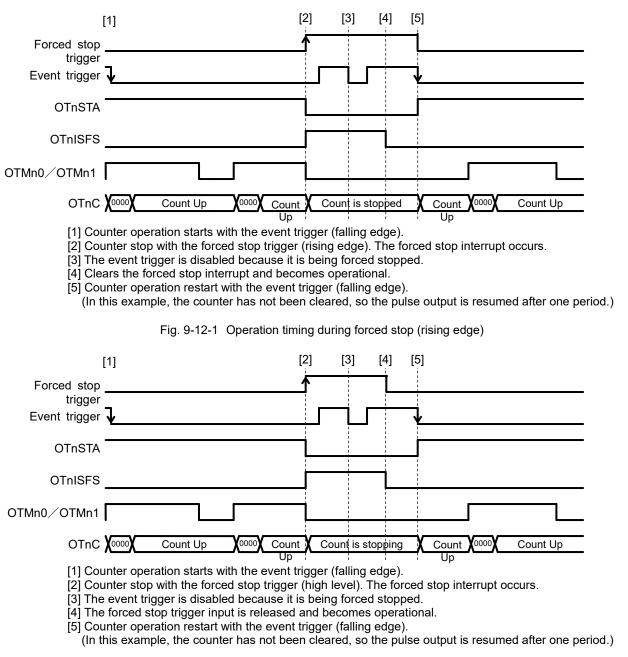

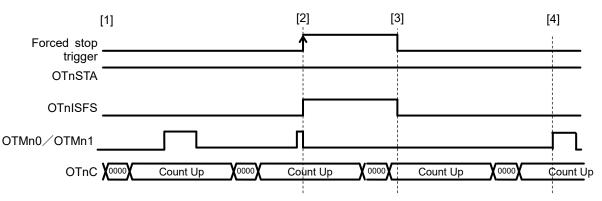

| 9.3.6.3 Forced stop operation (Counter count stop, waveform output stop)                 |      |

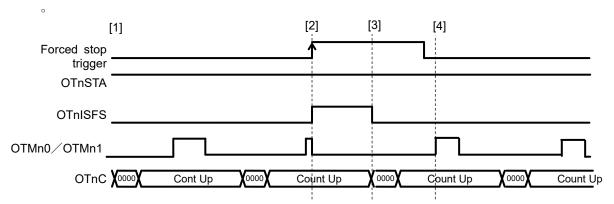

| 9.3.6.4 Forced stop operation (Counter count continues, waveform output stop)            |      |

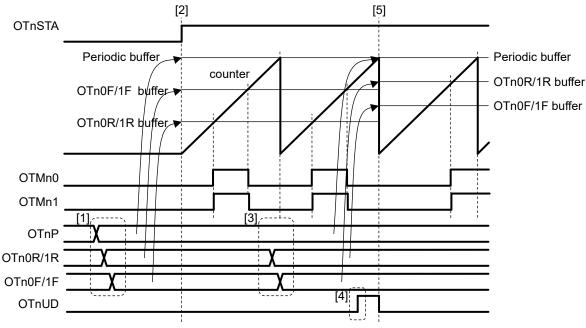

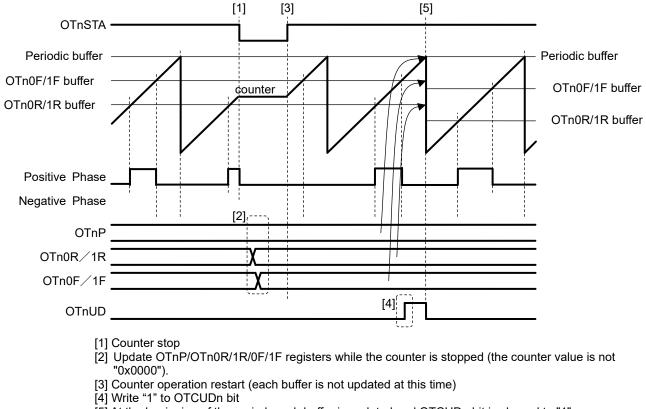

| 9.3.7 Changing Cycle and Duty during Operation                                           |      |

| 9.3.8 Cycle stop function                                                                |      |

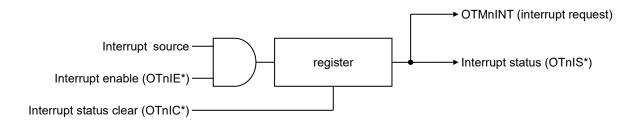

| 9.3.9 Interrupt                                                                          |      |

| 9.3.10 Clock Mutual Monitoring Function                                                  |      |

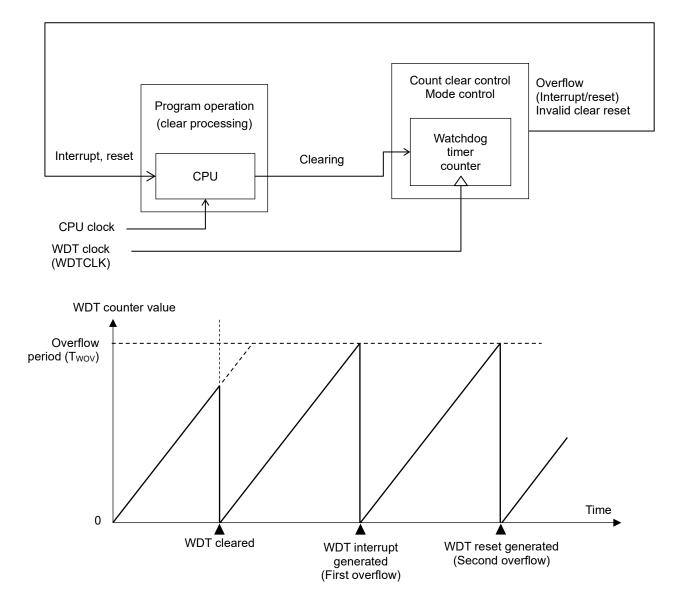

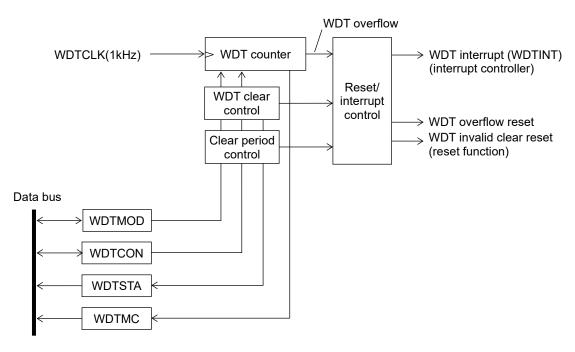

### Chapter 10 Watchdog Timer

#### ML62Q2033/35/43/45 User's Manual Contents

| 10. Watchdog Timer                                                          |  |

|-----------------------------------------------------------------------------|--|

| 10.1 General Description                                                    |  |

| 10. Watchdog Timer         10.1 General Description         10.1.1 Features |  |

| 10.1.2 Configuration                                                        |  |

| 10.2 Description of Registers                                               |  |

| 10.2.1 List of Registers                                                    |  |

| 10.2.2 Watchdog timer control register (WDTCON)                             |  |

| 10.2.3 Watchdog Timer Mode Register (WDTMOD)                                |  |

| 10.2.4 Watchdog Timer Counter Register (WDTMC)                              |  |

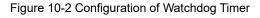

| 10.2.5 Watchdog Timer Status Register (WDTSTA)                              |  |

| 10.3 Description of Operation                                               |  |

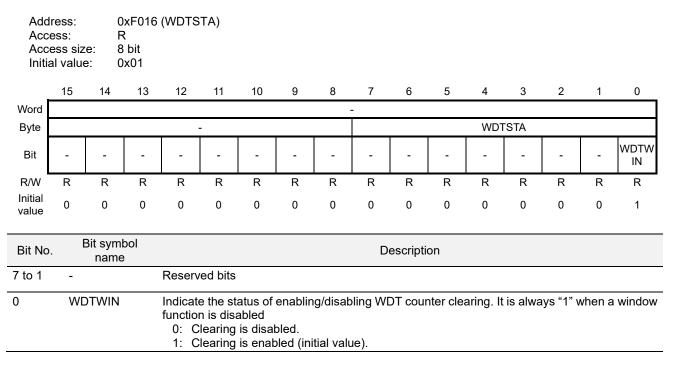

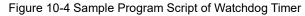

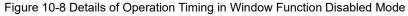

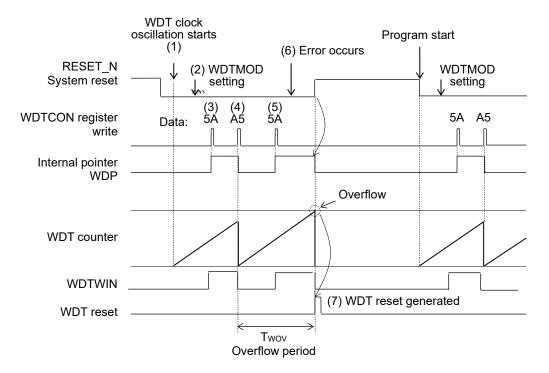

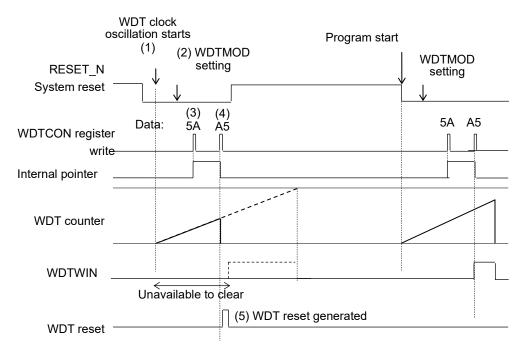

| 10.3.1 How to Clear WDT Counter                                             |  |

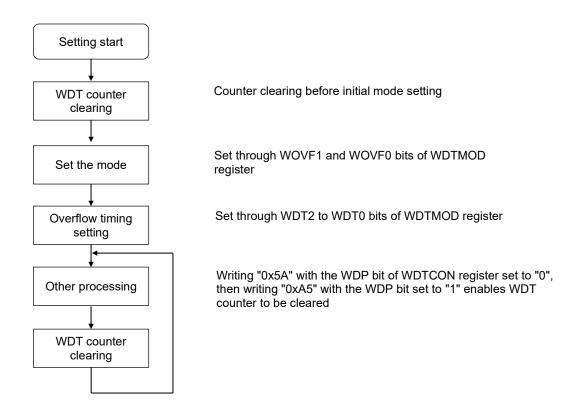

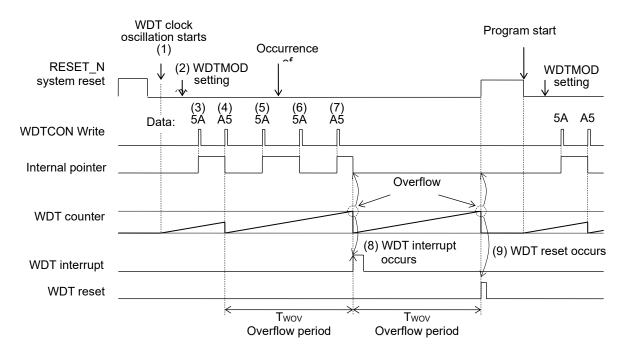

| 10.3.2 Window Function Disabled Mode                                        |  |

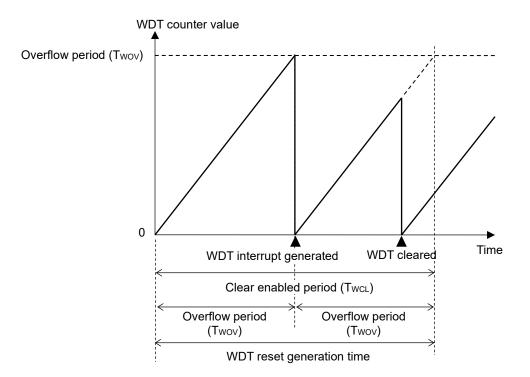

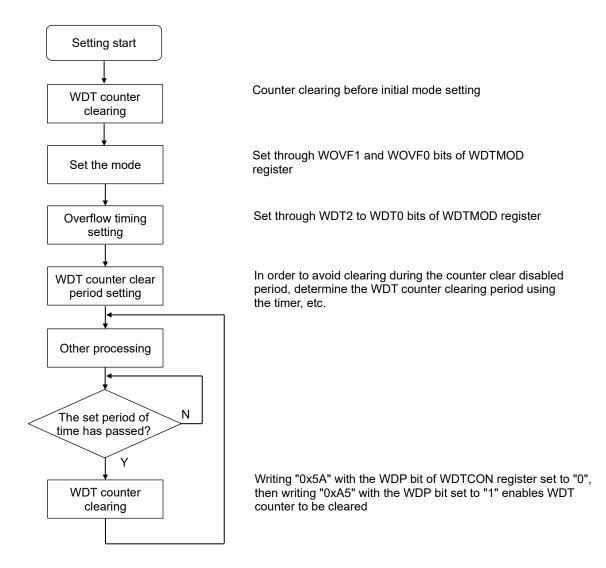

| 10.3.3 Window Function Enabled Mode                                         |  |

|                                                                             |  |

### Chapter 11 (Skip number)

### Chapter 12 (Skip number)

### Chapter 13 I<sup>2</sup>C Bus

| 13. I <sup>2</sup> C Bus                                            | 13-1 |

|---------------------------------------------------------------------|------|

| 13.1 General Description                                            |      |

| 13.1.1 Features                                                     |      |

| 13.1.2 Configuration                                                |      |

| 13.1.3 List of Pins                                                 |      |

| 13.2 Description of Registers                                       |      |

| 13.2.1 List of Registers                                            |      |

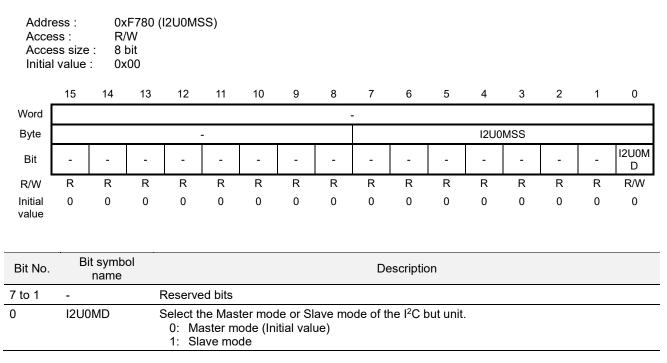

| 13.2.2 I <sup>2</sup> C Bus Unit 0 Mode Register (I2U0MSS)          |      |

| 13.3 Description of Registers for Master function                   |      |

| 13.3.1 I <sup>2</sup> C Bus Unit 0 Receive Register (I2U0RD)        |      |

| 13.3.2 I <sup>2</sup> C Bus Unit 0 Slave Address Register (I2U0SA)  |      |

| 13.3.3 I <sup>2</sup> C Bus Unit 0 Transmit Data Register (I2U0TD)  |      |

| 13.3.4 I <sup>2</sup> C Bus Unit 0 Control Register (I2U0CON)       |      |

| 13.3.5 I <sup>2</sup> C Bus Unit 0 Mode Register (I2U0MOD)          |      |

| 13.3.6 I <sup>2</sup> C Bus Unit 0 Status Register (I2U0STR)        |      |

| 13.3.7 I <sup>2</sup> C Bus Unit 0 Status Clear Register (I2U0SCLR) |      |

| 13.4 Description of Registers for Slave function                    |      |

| 13.4.1 I <sup>2</sup> C Bus Unit 0 Receive Register (I2U0RD)        |      |

| 13.4.2 I <sup>2</sup> C Bus Unit 0 Slave Address Register (I2U0SA)  |      |

| 13.4.3 I <sup>2</sup> C Bus Unit 0 Transmit Data Register (I2U0TD)  |      |

| 13.4.4 I <sup>2</sup> C Bus Unit 0 Control Register (I2U0CON)       |      |

| 13.4.5 I <sup>2</sup> C Bus Unit 0 Mode Register (I2U0MOD)          |      |

| 13.4.6 I <sup>2</sup> C Bus Unit 0 Status Register (I2U0STR)        |      |

| 13.4.7 I <sup>2</sup> C Bus Unit 0 Status Clear Register (I2U0SCLR) |      |

| 13.5 Description of Operation for Master function                   |      |

| 13.5.1 Control Procedures                                           |      |

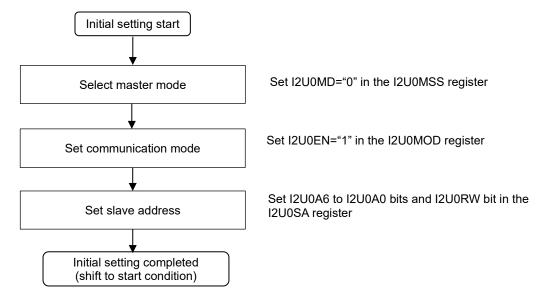

| 13.5.1.1 Initial Setting of Communication Operation                 |      |

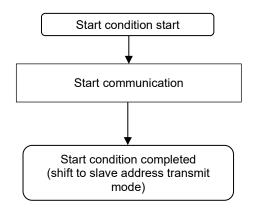

| 13.5.1.2 Start Condition                                            |      |

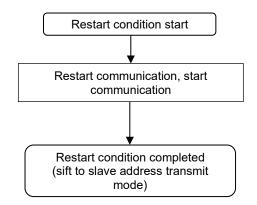

| 13.5.1.3 Restart Condition                                          |      |

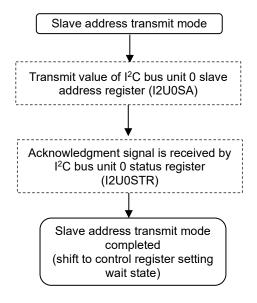

| 13.5.1.4 Slave Address Transmission Mode                            |      |

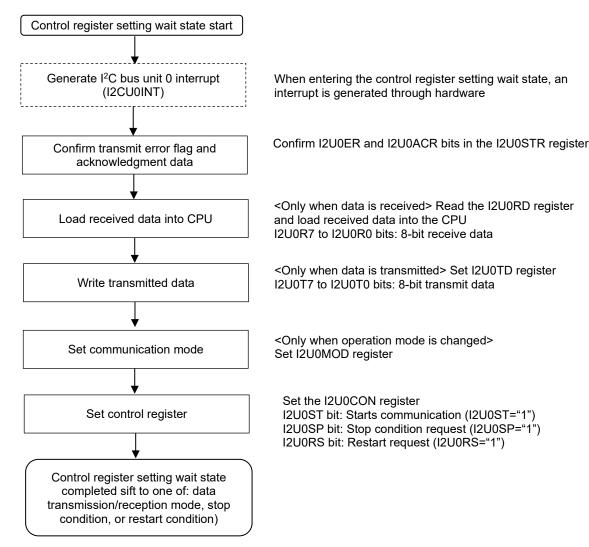

| 13.5.1.5 Control Register Setting Wait State                        |      |

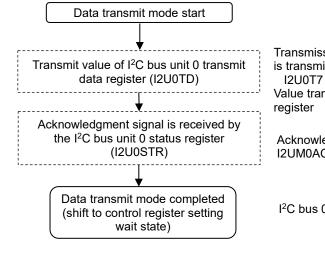

| 13.5.1.6 Data Transmission Mode                                     |      |

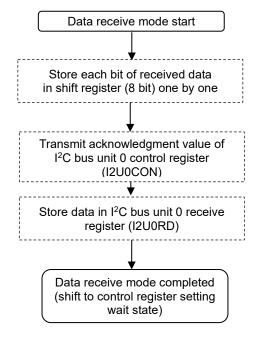

| 13.5.1.7 Data Reception Mode                                        |      |

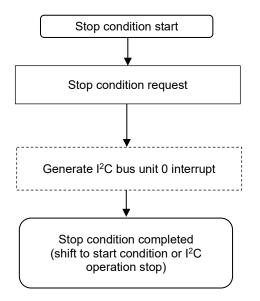

| 13.5.1.8 Stop Condition                                             |      |

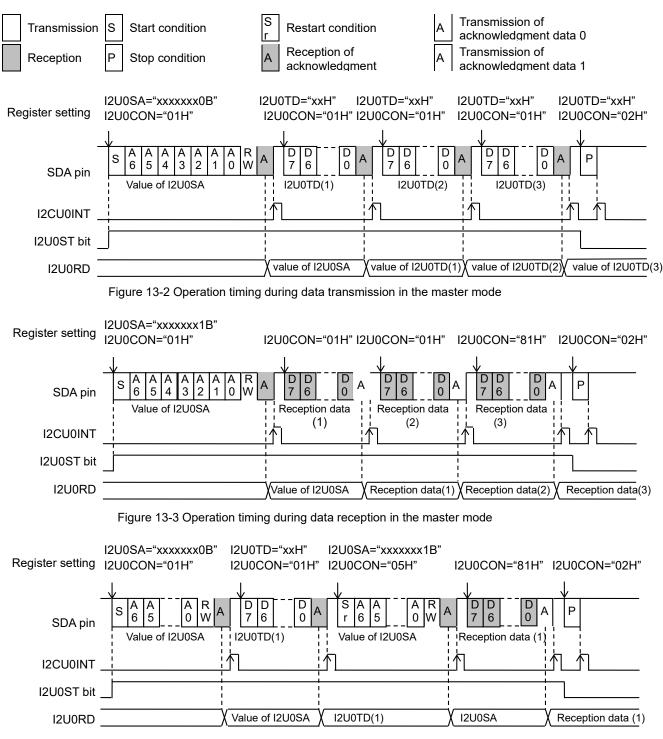

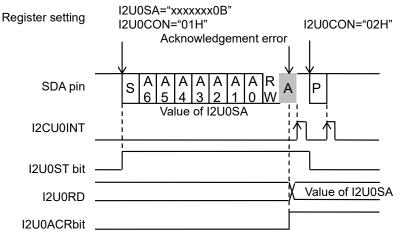

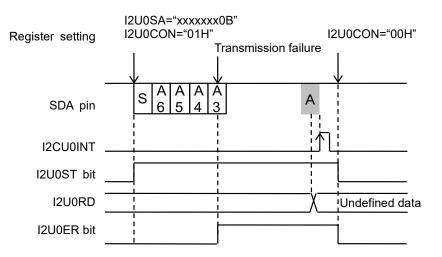

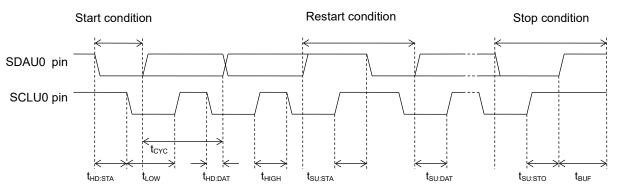

| 13.5.2 Communication Operation Timing                               |      |

| 13.5.3 Interrupt                                                    |      |

| 13.5.4 Operation Waveforms                                          |      |

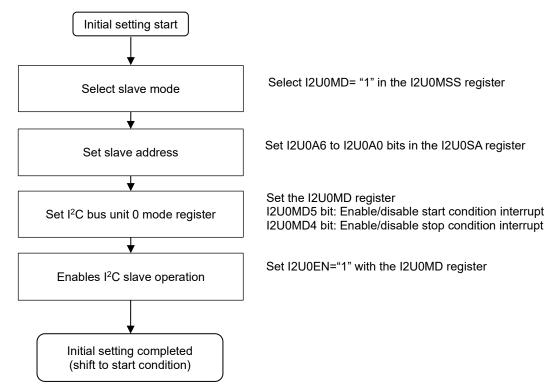

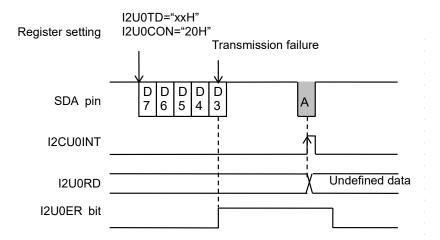

| 13.6 Description of Operation for Slave function                    |      |

| 13.6.1 Procedures                                                   |      |

|                                                                     |      |

#### ML62Q2033/35/43/45 User's Manual Contents

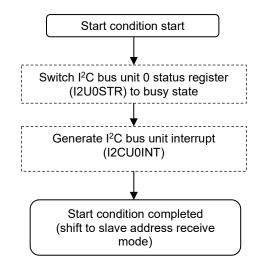

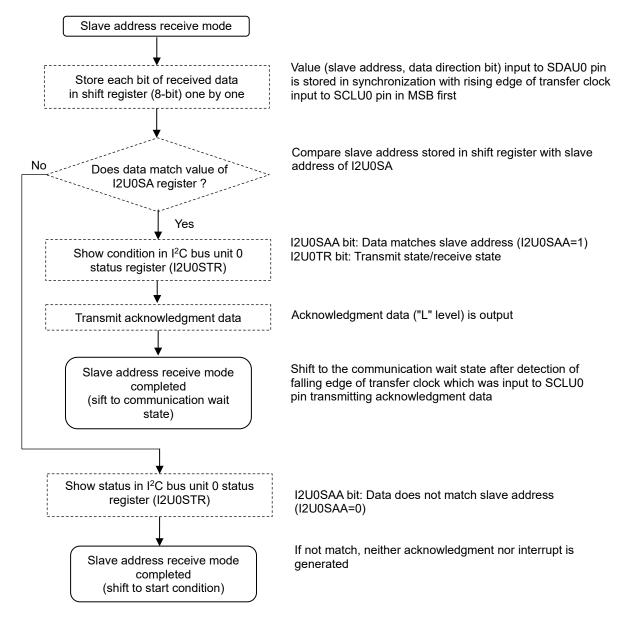

| 13.6.1.1 Initial Setting of Communication Operation13-2913.6.1.2 Start Condition13-29 |

|---------------------------------------------------------------------------------------|

|                                                                                       |

| 13.6.1.3 Slave Address Reception Mode                                                 |

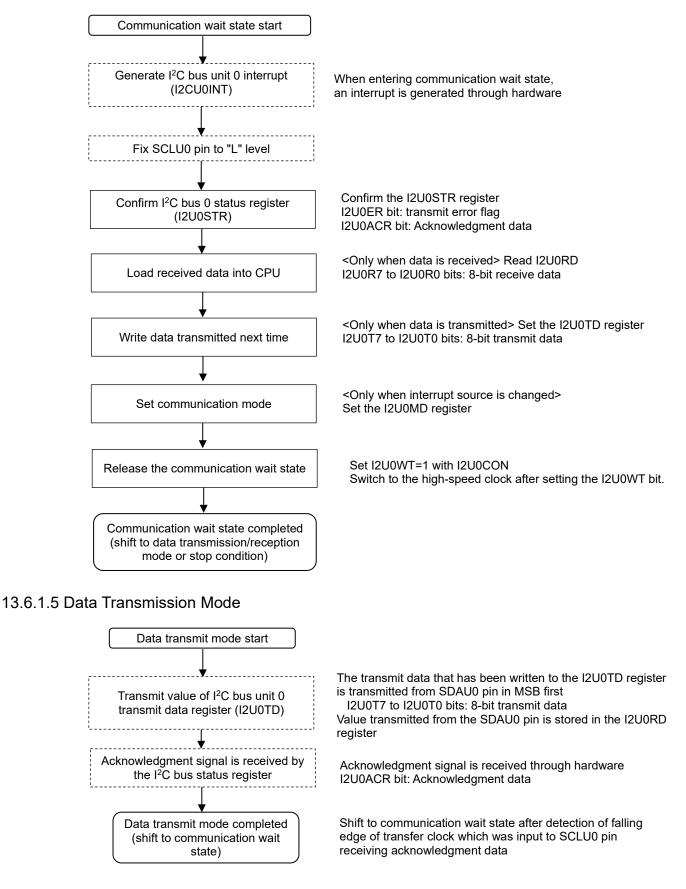

| 13.6.1.4 Communication Wait State                                                     |

| 13.6.1.5 Data Transmission Mode                                                       |

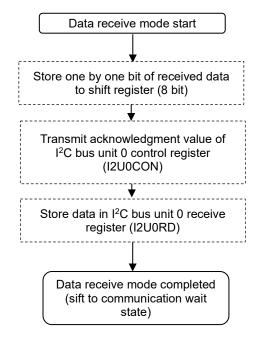

| 13.6.1.6 Data Reception Mode                                                          |

| 13.6.1.7 Stop Condition                                                               |

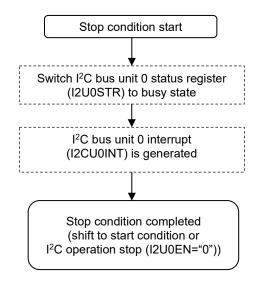

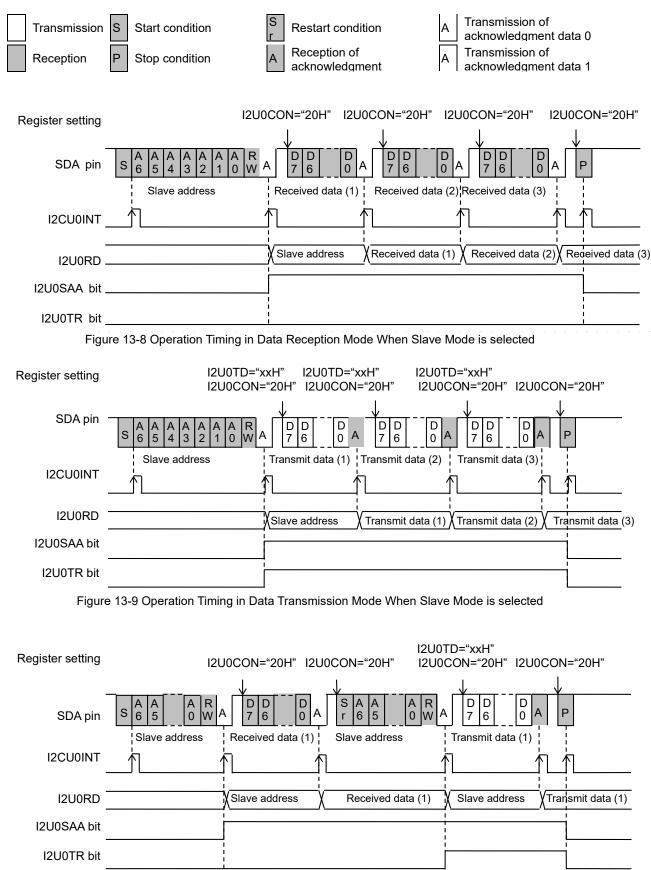

| 13.6.2 Communication Operation Timing                                                 |

| 13.6.3 Interrupt                                                                      |

#### Chapter 14 UART

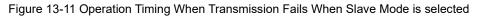

| 14. UART                                                                                 | 14-1 |

|------------------------------------------------------------------------------------------|------|

| 14.1 General Description                                                                 | 14-1 |

| 14.1.1 Features                                                                          | 14-1 |

| 14.1.2 Configuration                                                                     | 14-1 |

| 14.1.3 List of Pins                                                                      |      |

| 14.2 Description of Registers                                                            |      |

| 14.2.1 List of Registers                                                                 |      |

| 14.2.2 UARTn Reception Buffer (UAnBUF0)                                                  | 14-4 |

| 14.2.3 UARTn Transmission Buffer (UAnBUF1)                                               |      |

| 14.2.4 UARTn Status Register (UAnSTAT)                                                   |      |

| 14.2.5 UARTn Status Clear Register (UAnSTAC)                                             |      |

| 14.2.6 UARTn Control Register (UAnCON)                                                   | 14-7 |

| 14.2.7 UARTn Mode Register (UAnMOD)                                                      |      |

| 14.2.8 UARTn Interrupt Enable Register (UAnINTE)                                         |      |

| 14.2.9 UARTn Baud Rate Register (UAnBRT)                                                 |      |

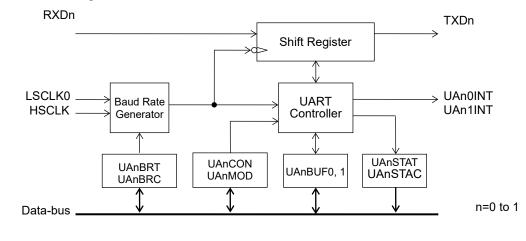

| 14.2.10 UARTn Baud Rate Adjustment Register (UAnBRC)                                     |      |

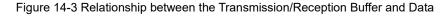

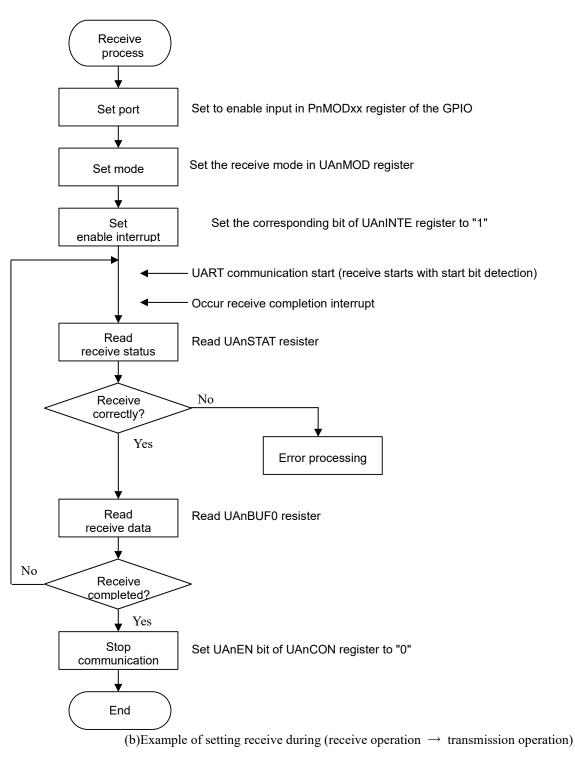

| 14.3 Description of Operation                                                            |      |

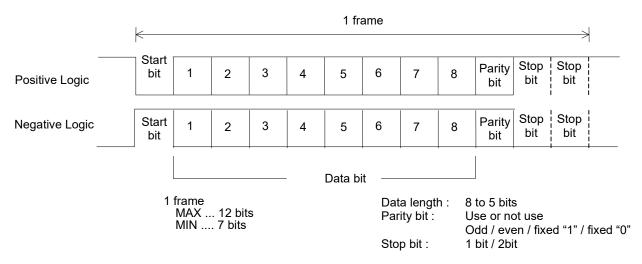

| 14.3.1 Frame Format                                                                      |      |

| 14.3.2 Data Direction                                                                    |      |

| 14.3.3 Baud Rate                                                                         |      |

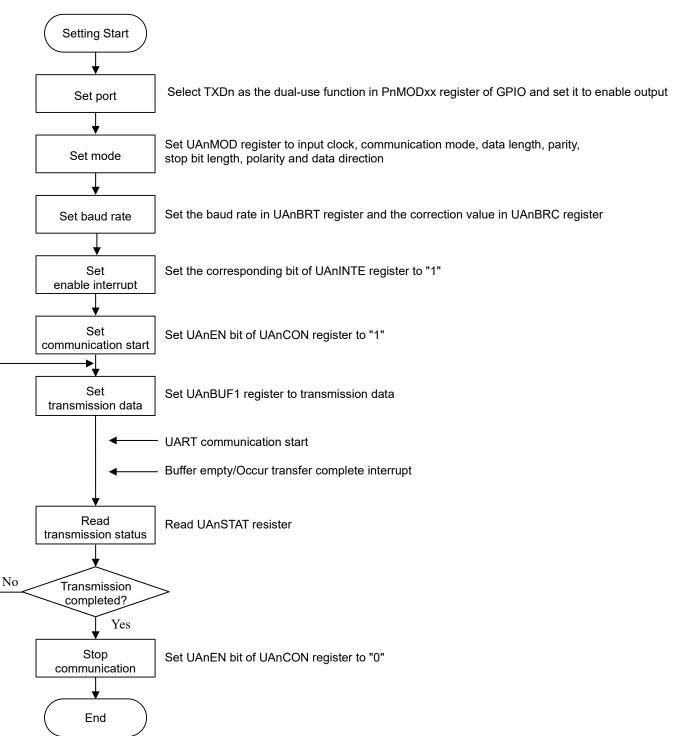

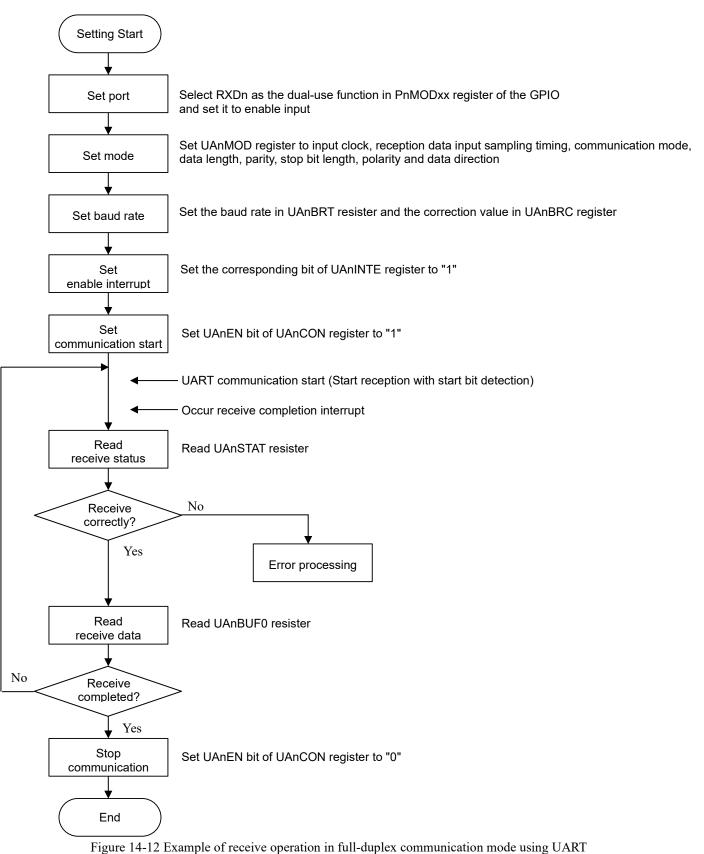

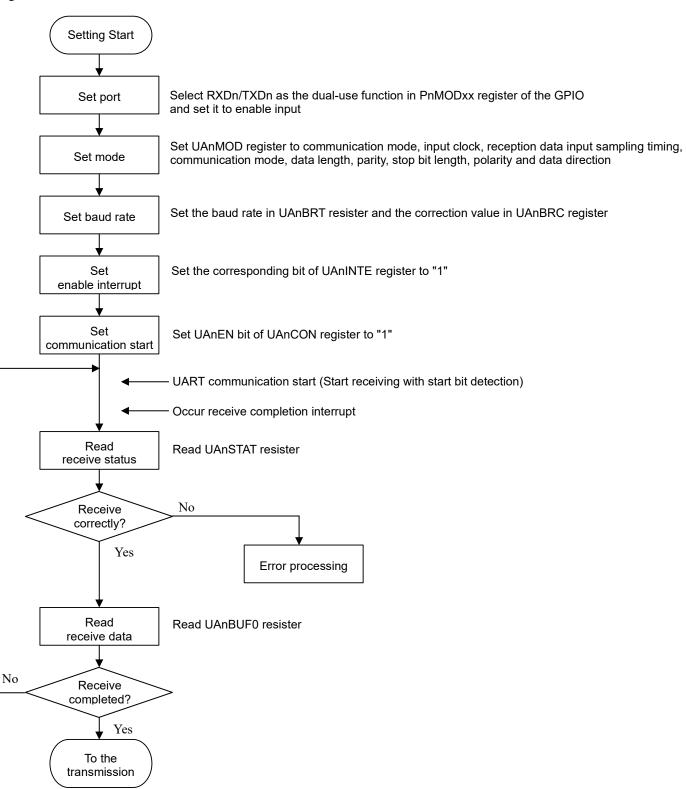

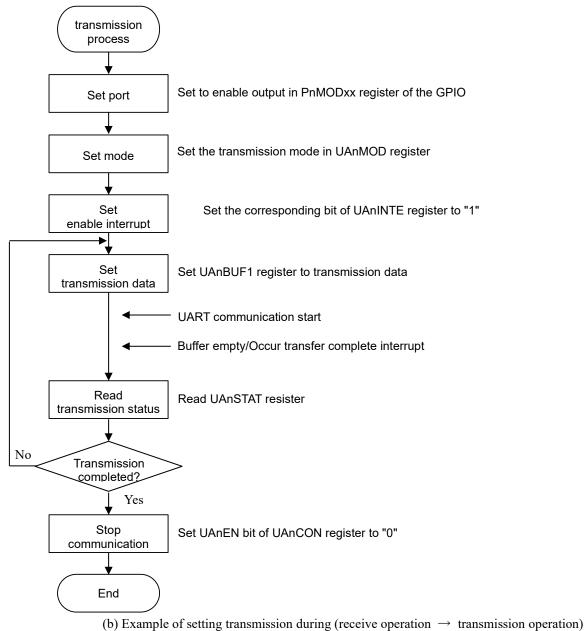

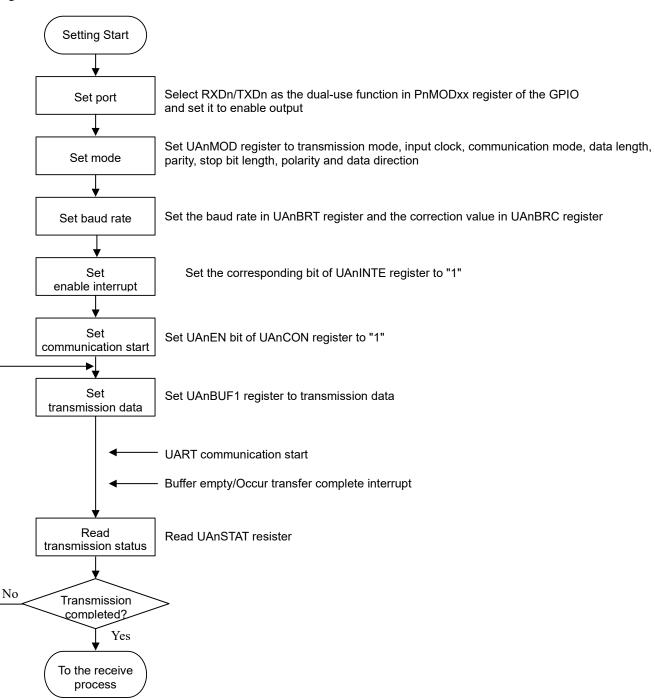

| 14.3.4 Transmission Operation(Common to full-duplex and half-duplex communication modes) |      |

| 14.3.5 Reception Operation (Common to full-duplex and half-duplex communication modes)   |      |

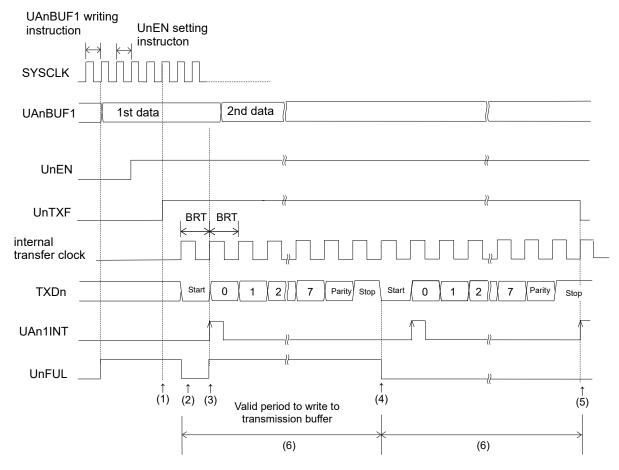

| 14.3.5.1 Detection of Start Bit                                                          |      |

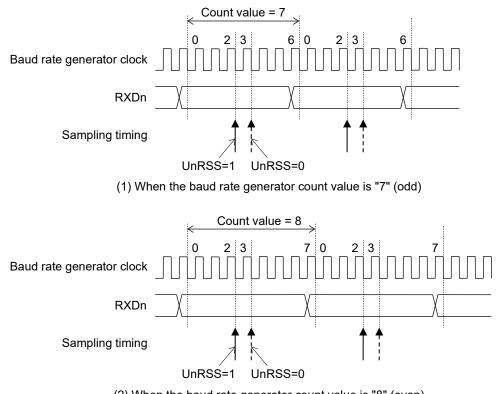

| 14.3.5.2 Sampling Timing                                                                 |      |

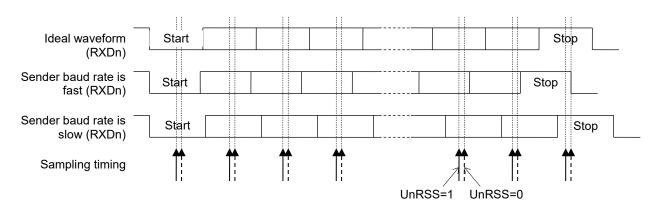

| 14.3.5.3 Receiving Margin                                                                |      |

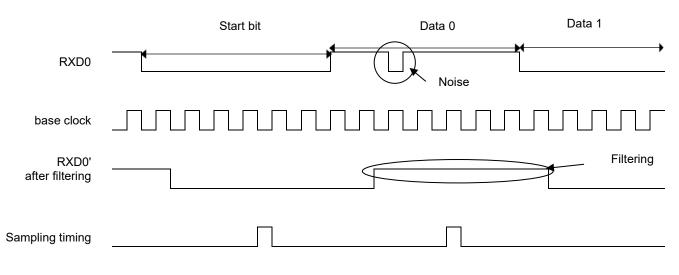

| 14.3.5.4 Reception Filter                                                                |      |

| 14.3.6 Interrupt                                                                         |      |

| 14.3.7 Example of Setting                                                                |      |

|                                                                                          |      |

### Chapter 15 (Skip number)

### Chapter 16 (Skip number)

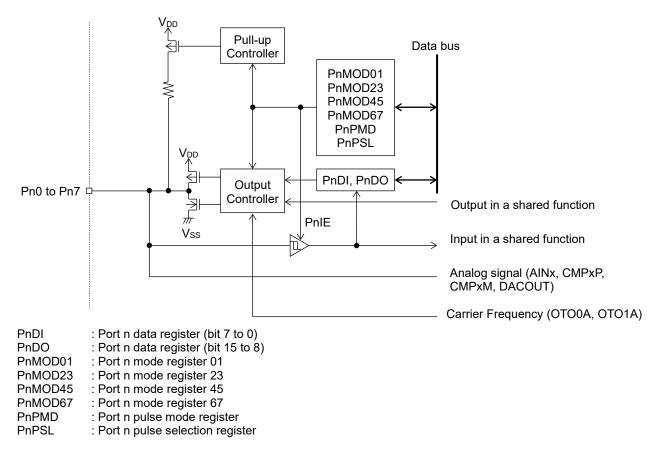

### Chapter 17 GPIO

| 17. GPIO                                          |       |

|---------------------------------------------------|-------|

| 17.1 General Description                          |       |

| 17.1.1 Features                                   |       |

| 17.1.2 Configuration<br>17.1.3 List of Pins       |       |

| 17.1.3 List of Pins                               |       |

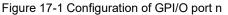

| 17.2 Description of Registers                     |       |

| 17.2.1 List of Registers                          |       |

| 17.2.2 Port n Data Register (PnD:n=0 to 2)        |       |

| 17.2.3 Port 0 Mode Register 01 (P0MOD01)          |       |

| 17.2.4 Port n Mode Register 01 (PnMOD01: n=1, 2)  |       |

| 17.2.5 Port n Mode Register 23 (PnMOD23:n=0 to 2) |       |

| 17.2.6 Port n Mode Register 45 (PnMOD45: n=0, 1)  |       |

| 17.2.7 Port n Mode Register 67 (PnMOD67:n=0, 1)   |       |

| 17.2.8 Port n Pulse Mode Register (PnPMD:n=1, 2)  | 17-17 |

|                                                   |       |

#### ML62Q2033/35/43/45 User's Manual Contents

| 17.2.9 Port n Pulse Selection Register (PnPSL:n=1, 2)        |  |

|--------------------------------------------------------------|--|

| 17.3 Description of Operation                                |  |

| 17.3.1 Input                                                 |  |

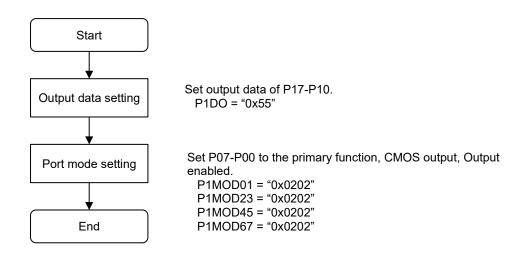

| 17.3.2 Output                                                |  |

| 17.3.3 Primary Functions Other than Input/Output Function    |  |

| 17.3.4 Shared Function                                       |  |

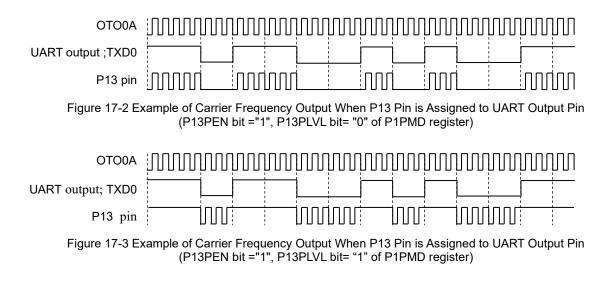

| 17.3.5 Carrier Frequency Output                              |  |

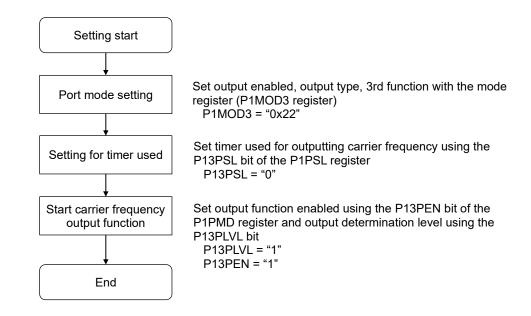

| 17.3.5.1 Carrier Frequency Output Operation                  |  |

| 17.3.5.2 Carrier Frequency Output Function Setting Procedure |  |

| 17.3.6 Port Output Level Test                                |  |

| 17.3.7 Port Setting Example                                  |  |

| 17.3.8 Notes for using P00/TEST0 pin                         |  |

|                                                              |  |

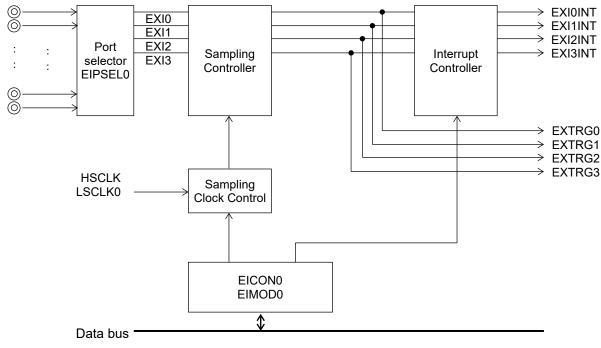

#### **Chapter 18 External Interrupt Function**

| 18. External Interrupt Function                               |  |

|---------------------------------------------------------------|--|

| 18.1 General Description                                      |  |

| 18.1.1 Features                                               |  |

| 18.1.2 Configuration                                          |  |

| 18.1.3 List of Pins                                           |  |

| 18.2 Description of Registers                                 |  |

| 18.2.1 List of Registers                                      |  |

| 18.2.2 External Interrupt Control Register 0 (EICON0)         |  |

| 18.2.3 External Interrupt Mode Register 0 (EIMOD0)            |  |

| 18.2.4 External Interrupt Port Selection Register 0 (EIPSEL0) |  |

| 18.3 Description of Operation                                 |  |

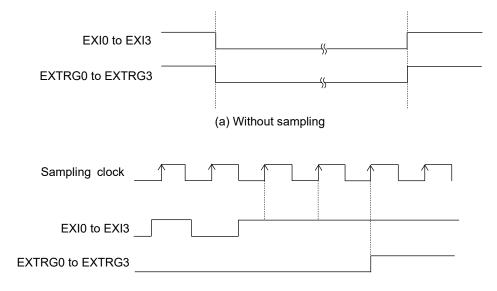

| 18.3.1 Interrupt Request Timing                               |  |

| 18.3.2 External Trigger Signal                                |  |

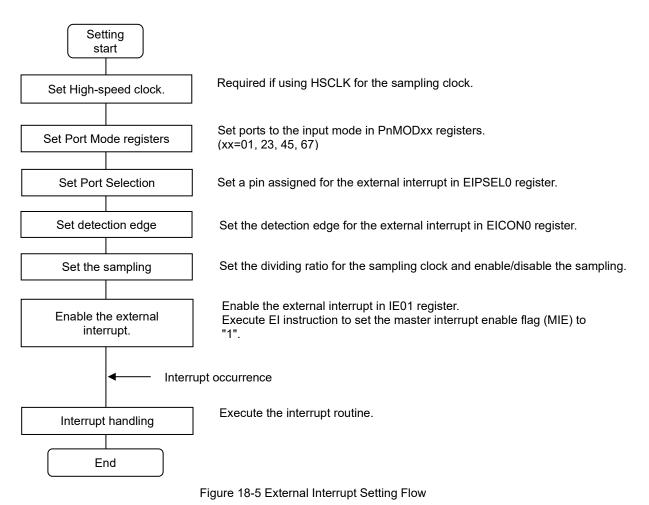

| 18.3.3 External Interrupt Setting Flow                        |  |

|                                                               |  |

#### Chapter 19 (Skip number)

#### **Chapter 20 Analog Comparator**

| 20. Analog Comparator                                   |  |

|---------------------------------------------------------|--|

| <b>20. Analog Comparator</b>                            |  |

| 20.1.1 Features                                         |  |

| 20.1.2 Configuration                                    |  |

| 20.1.3 List of Pins                                     |  |

| 20.2 Description of Registers                           |  |

| 20.2.1 List of Registers                                |  |

| 20.2.2 Comparator Control Register (CMPCON)             |  |

| 20.2.3 Comparator n Mode Register (CMPnMOD: n=0,1,2)    |  |

| 20.2.4 Comparator Status Register(CMPSTA)               |  |

| 20.3 Description of Operation                           |  |

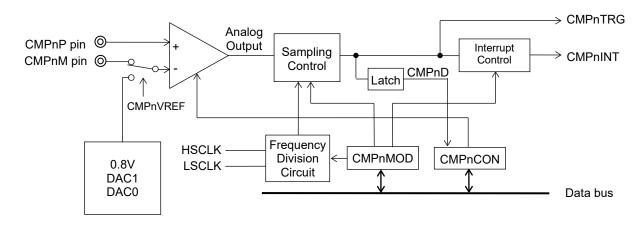

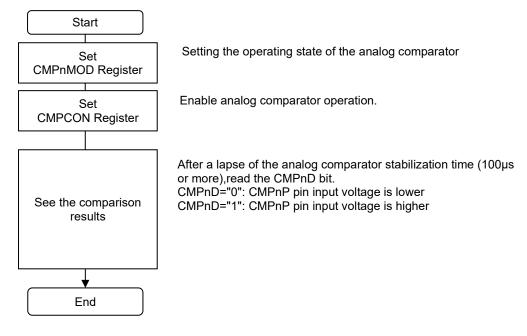

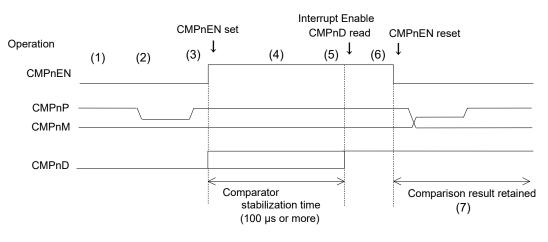

| 20.3.1 Analog Comparator Operation                      |  |

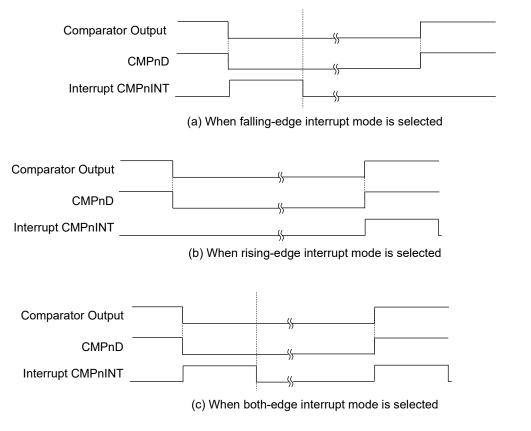

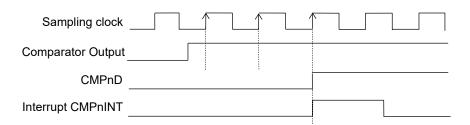

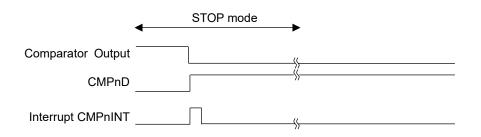

| 20.3.2 Interrupt Request                                |  |

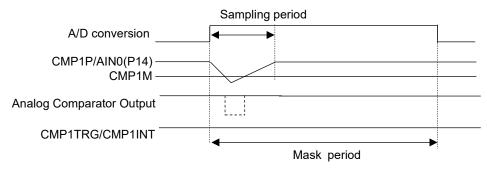

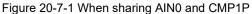

| 20.3.3 Operation when sharing AINn pin and pin          |  |

| 20.3.4 To output the analog comparator result from GPIO |  |

|                                                         |  |

#### Chapter 21 D/A Converter

| 21. D/A Converter                                      |  |

|--------------------------------------------------------|--|

| 21.1 General Description                               |  |

| 21.1.1 Features                                        |  |

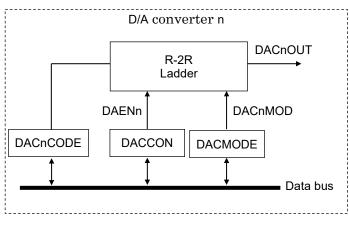

| 21.1.2 Configuration                                   |  |

| 21.1.3 List of Pins                                    |  |

| 21.2 Description of Registers                          |  |

| 21.2.1 List of Registers                               |  |

| 21.2.2 D/A Converter Control Register (DACCON)         |  |

| 21.2.3 D/A Converter 0 Code Register (DACCODE) (n=0,1) |  |

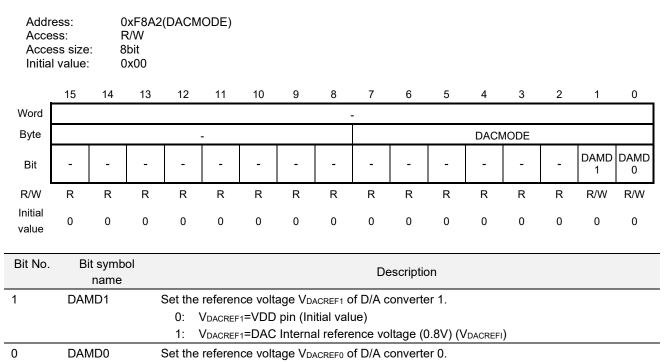

| 21.2.4 D/A Converter Mode Register (DACMODE)           |  |

|                                                        |  |

#### ML62Q2033/35/43/45 User's Manual Contents

|                                                                                    | 21 (  |

|------------------------------------------------------------------------------------|-------|

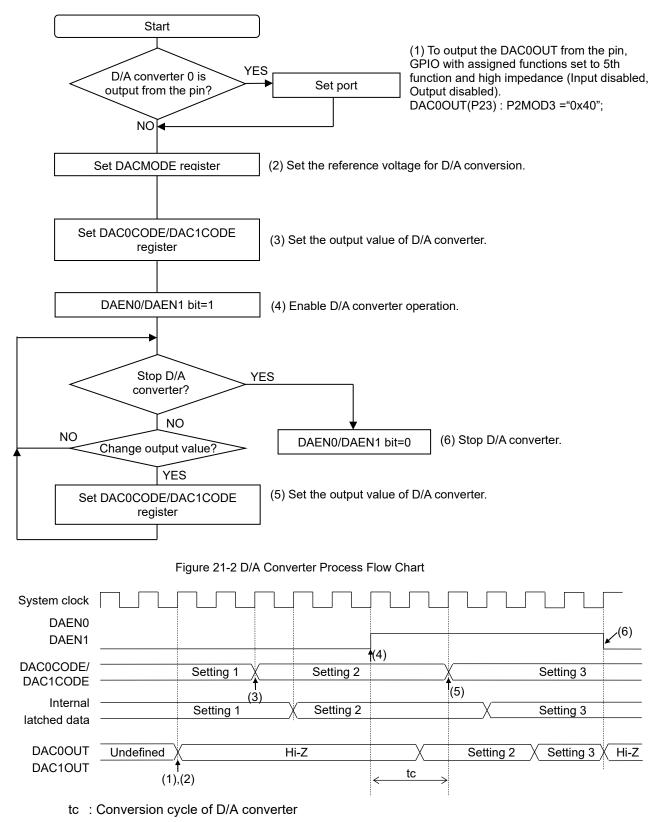

| 21.3 Description of Operation                                                      |       |

| 21.3.1 D/A Converter Operation                                                     |       |

|                                                                                    |       |

| Chapter 22 LOW Level Detector                                                      | 22.1  |

| 22. Low Level Detector                                                             |       |

| 22.1 General Description                                                           |       |

| 22.1.1 Features                                                                    |       |

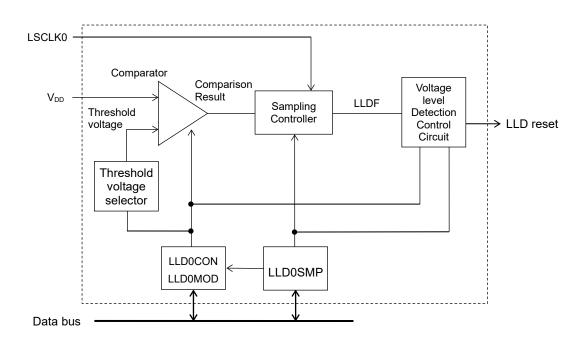

| 22.1.2 Configuration                                                               |       |

| 22.2 Description of Registers                                                      |       |

| 22.2.1 List of Registers                                                           |       |

| 22.2.2 Low Level Detector control register (LLD0CON)                               |       |

| 22.2.3 Low Level Detector mode register (LLD0MOD)                                  |       |

| 22.2.4 Low Level Detector sampling register (LLD0SMP)                              |       |

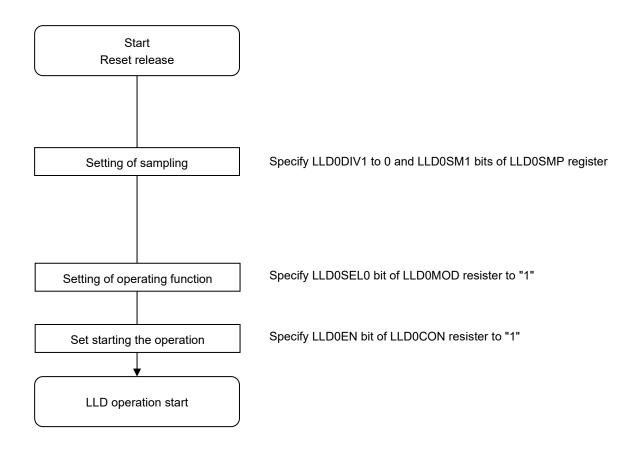

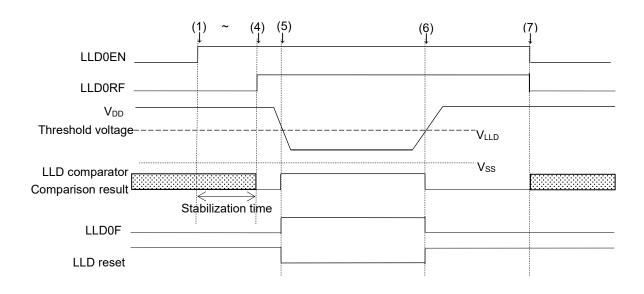

| 22.3 Description of Operation                                                      |       |

| 22.3.1 Operation setting procedure                                                 |       |

| 22.3.1.1 Reset Output                                                              |       |

|                                                                                    |       |

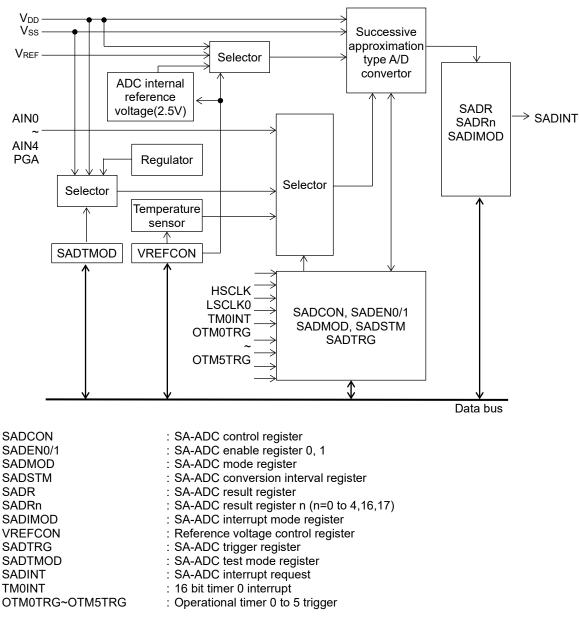

| Chapter 23 Successive Approximation Type A/D Converter                             |       |

| 23. Successive Approximation Type A/D Converter                                    |       |

| 23.1 General Description                                                           |       |

| 23.1.1 Features                                                                    |       |

| 23.1.2 Configuration                                                               |       |

| 23.1.3 List of Pins                                                                |       |

| 23.2 Description of Registers                                                      |       |

| 23.2.1 List of Registers                                                           |       |

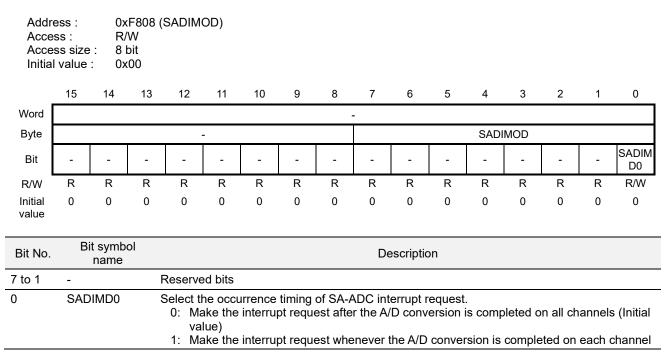

| 23.2.2 SA-ADC Mode Register (SADMOD)                                               |       |

| 23.2.3 SA-ADC Control Register (SADCON)                                            |       |

| 23.2.4 SA-ADC Conversion Interval Register (SADSTM)                                |       |

| 23.2.5 Reference Voltage Control Register (VREFCON)                                |       |

| 23.2.6 SA-ADC Interrupt Mode Register (SADIMOD)                                    |       |

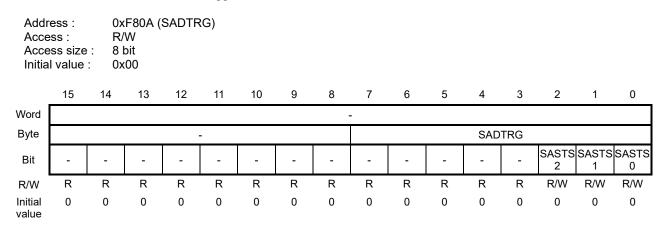

| 23.2.7 SA-ADC Trigger Register (SADTRG)                                            |       |

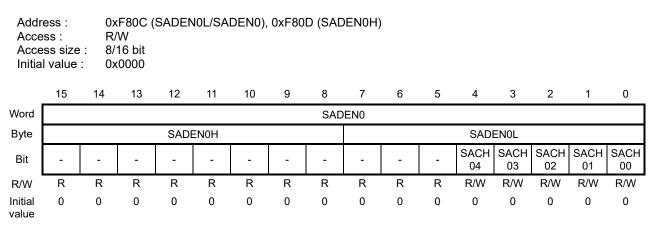

| 23.2.8 SA-ADC Enable Register 0 (SADEN0)                                           |       |

| 23.2.9 SA-ADC Enable Register 1 (SADEN1)                                           |       |

| 23.2.10 SA-ADC Result Register (SADR)                                              | 23-14 |

| 23.2.10 SA-ADC Result Register (SADR)                                              |       |

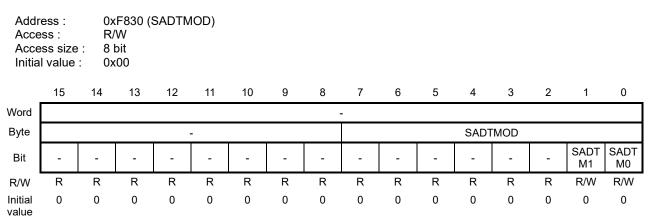

| 23.2.12 SA-ADC Test Mode Register II (SADTMOD)                                     |       |

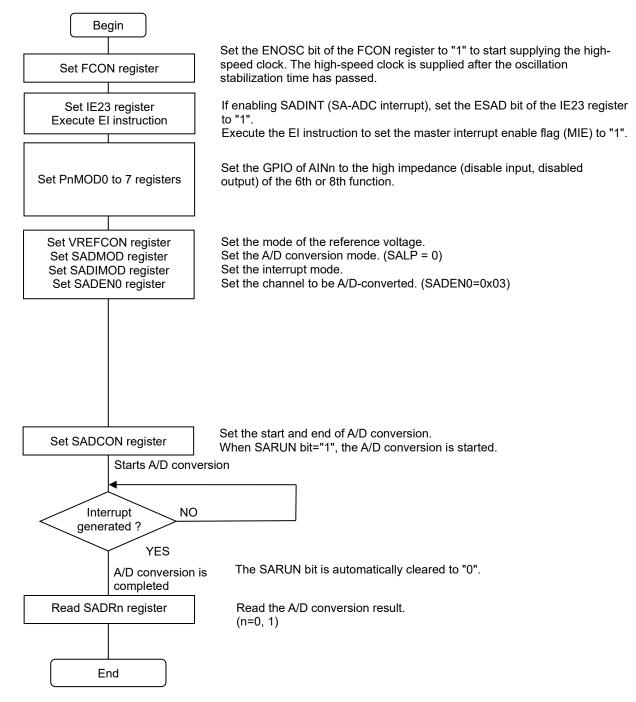

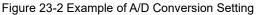

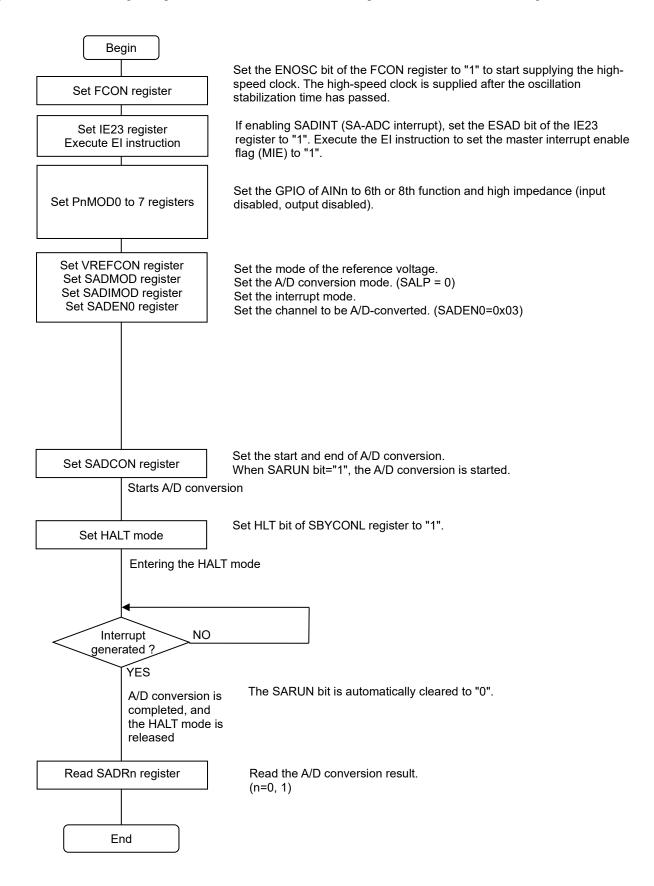

| 23.3 Description of Operation                                                      |       |

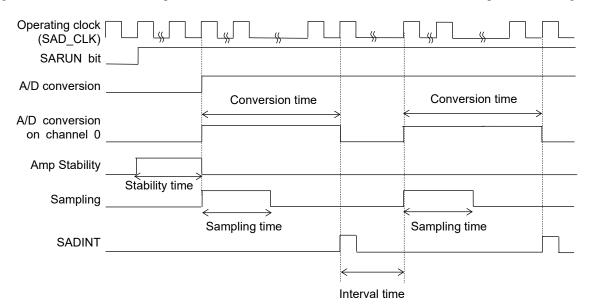

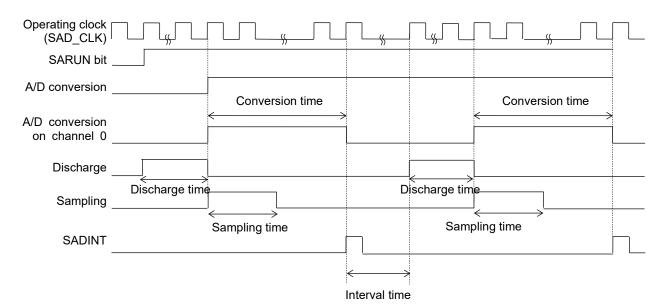

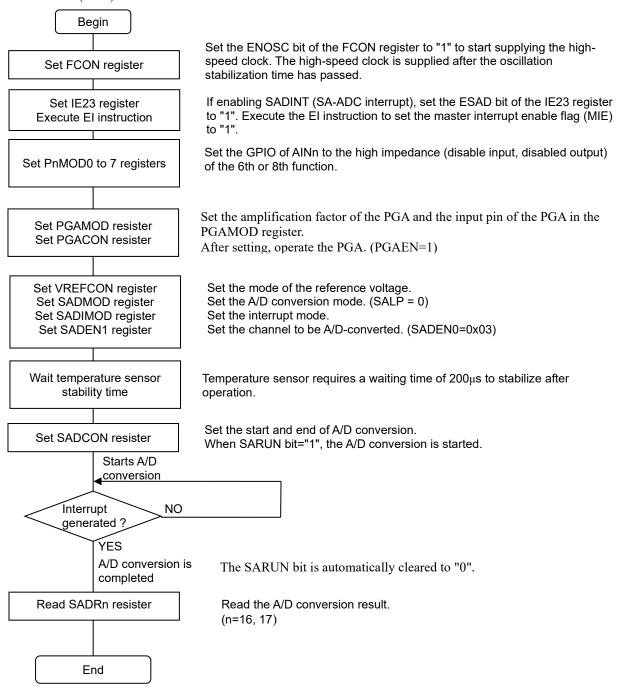

| 23.3.1 Operation of Successive Approximation Type A/D Converter                    |       |

|                                                                                    |       |

| 23.3.2 How to test the Successive Approximation Type A/D Converter                 |       |

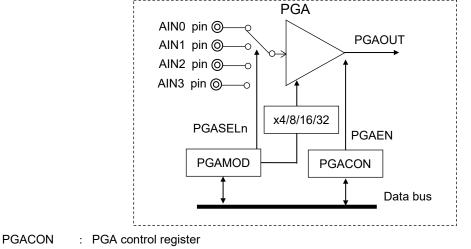

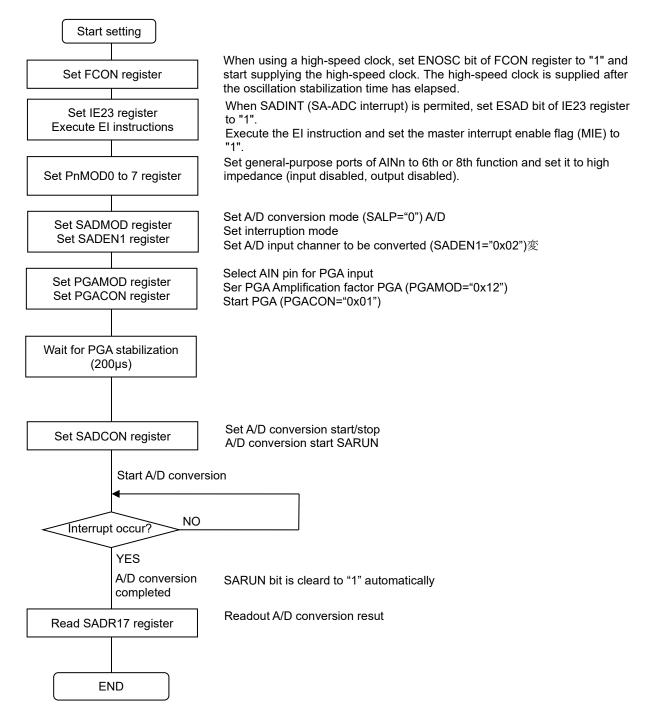

| 23.5 PGA in Successive Approximation A/D Converter/Temperature Conversion Function |       |

|                                                                                    |       |

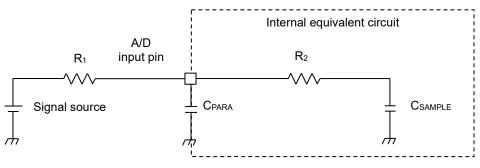

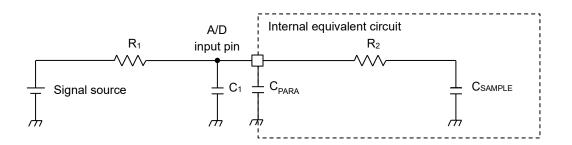

| 23.4.1 Sampling Time Setting                                                       |       |

| 23.4.2 Noise Suppression                                                           |       |

| Chanter 24 DCA                                                                     |       |

| Chapter 24 PGA                                                                     | 24.1  |

| 24. PGA.                                                                           |       |

| 24.1 General description                                                           |       |

| 24.1.1 Features.                                                                   |       |

| 24.1.2 Configuration                                                               |       |

| 24.1.3 Pin list                                                                    |       |

| 24.2 Register description                                                          |       |

| 24.2.1 List of register                                                            |       |

| 24.2.2 PGA Control Register (PGACON)                                               |       |

| 24.2.3 PGA Mode register (PGAMOD)                                                  |       |

| 24.3 Features                                                                      |       |

| 24.3.1 PGA Operation                                                               |       |

### Chapter 25 (Skip number)

#### ML62Q2033/35/43/45 User's Manual Contents

#### Chapter 26 Flash Memory 26 Flash Memory

| 26. Flash Memory                                                        |  |

|-------------------------------------------------------------------------|--|

| 26.1 General Description                                                |  |

| 26.1.1 List of Pins                                                     |  |

| 26.2 Register Description                                               |  |

| 26.2.1 List of Registers                                                |  |

| 26.2.2 Flash Address Register (FLASHA)                                  |  |

| 26.2.3 Flash Segment Register (FLASHSEG)                                |  |

| 26.2.4 Flash Data Register 0 (FLASHD0)                                  |  |

| 26.2.5 Flash Control Register (FLASHCON)                                |  |

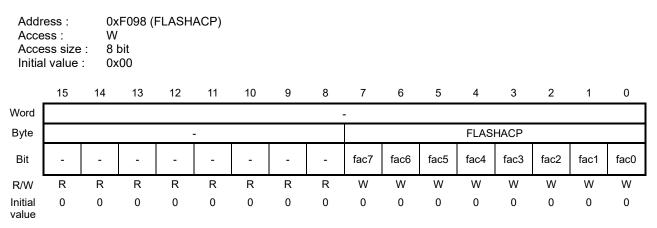

| 26.2.6 Flash Acceptor (FLASHACP)                                        |  |

| 26.2.7 Flash Self Register (FLASHSLF)                                   |  |

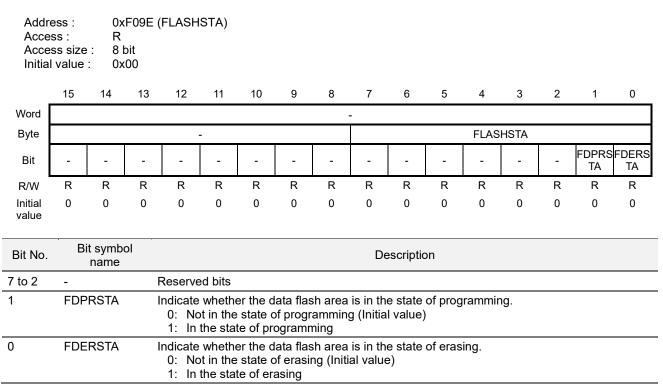

| 26.2.8 Flash Status Register (FLASHSTA)                                 |  |

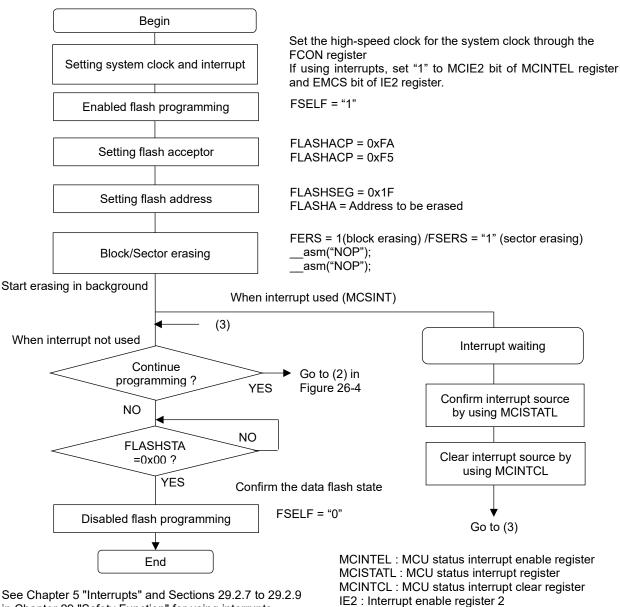

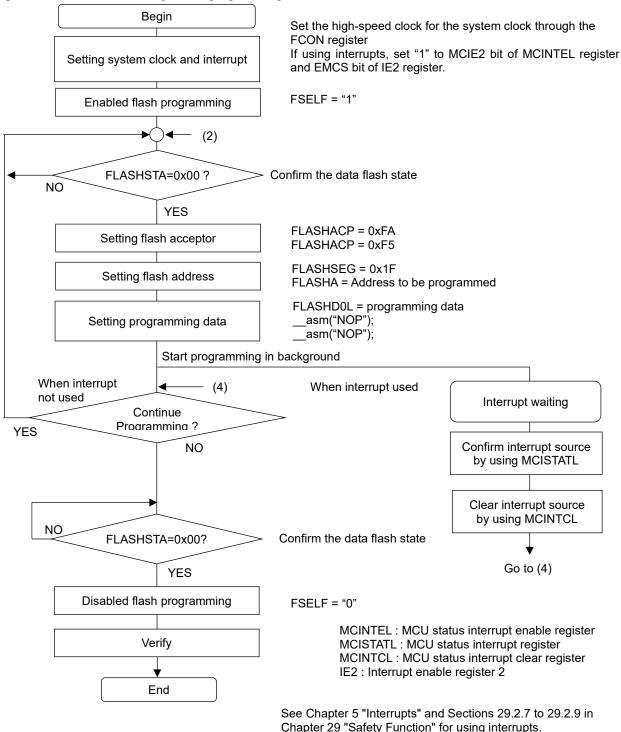

| 26.3 Self-programming                                                   |  |

| 26.3.1 Notes on Debugging Self-programming Code                         |  |

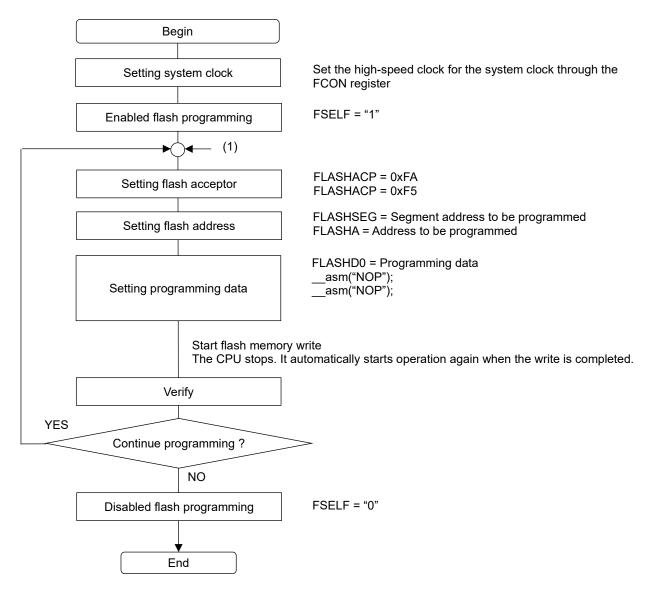

| 26.3.2 Programming Program Memory Space                                 |  |

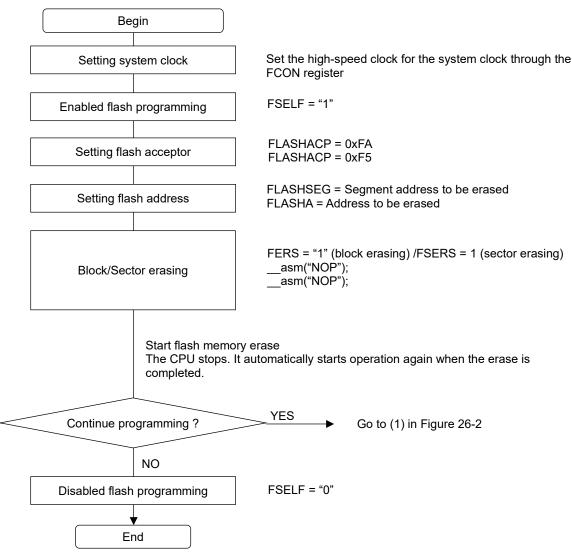

| 26.3.3 Programming Data Flash Area                                      |  |

| 26.3.4 Notes on use of self-programming                                 |  |

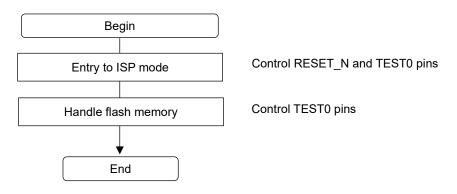

| 26.4 In-System Programming Function                                     |  |

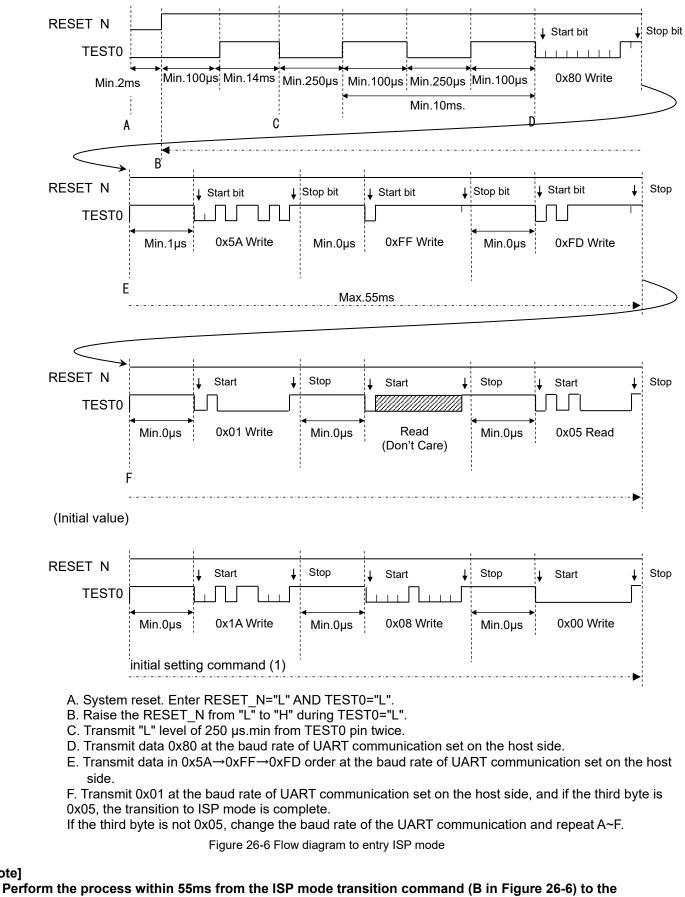

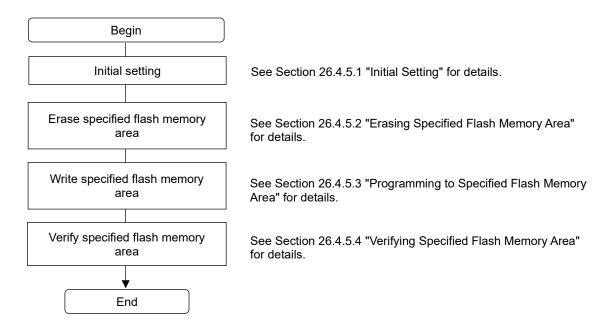

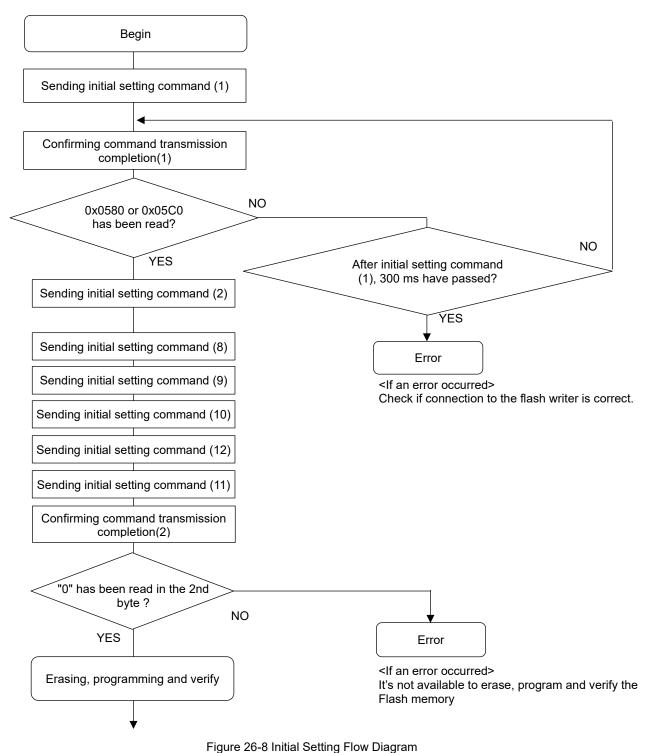

| 26.4.1 Programming Procedure                                            |  |

| 26.4.2 Communication Method                                             |  |

| 26.4.3 Control Command                                                  |  |

| 26.4.4 How to Entry ISP Mode                                            |  |

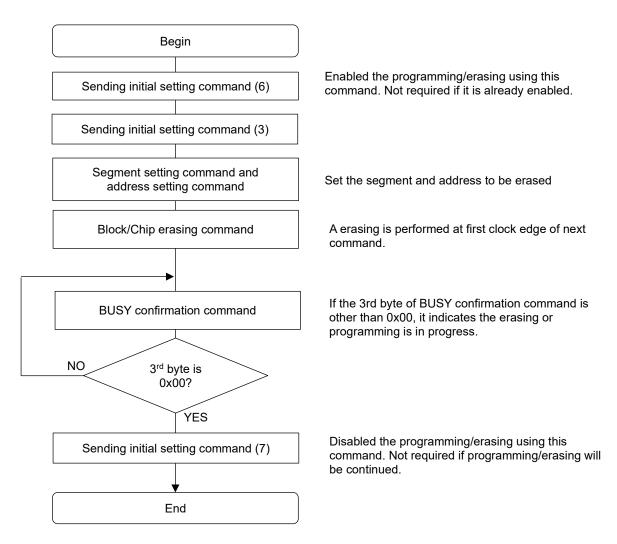

| 26.4.5 Handling the Flash Memory                                        |  |

| 26.4.5.1 Initial Setting                                                |  |

| 26.4.5.2 Erasing Data in Specified Flash Memory Area                    |  |

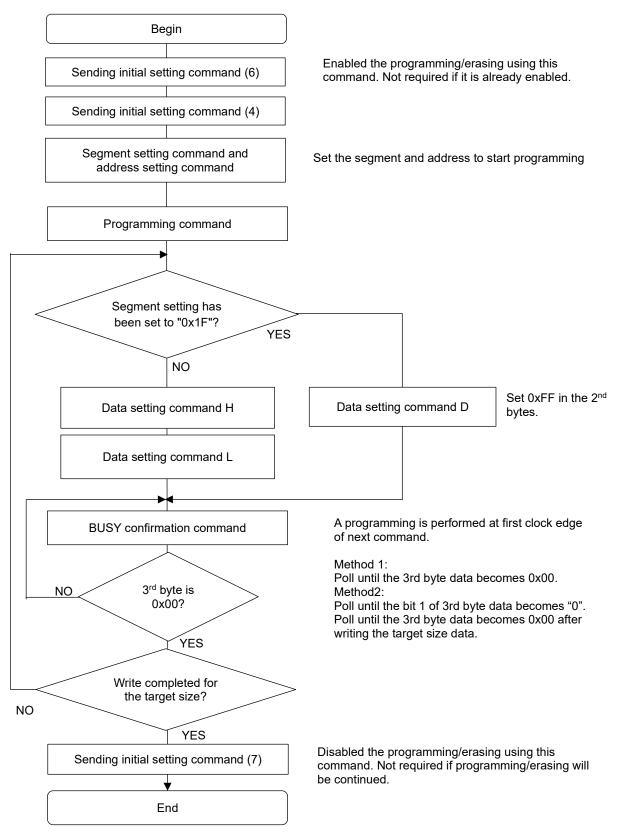

| 26.4.5.3 Programming to Specified Flash Memory Area                     |  |

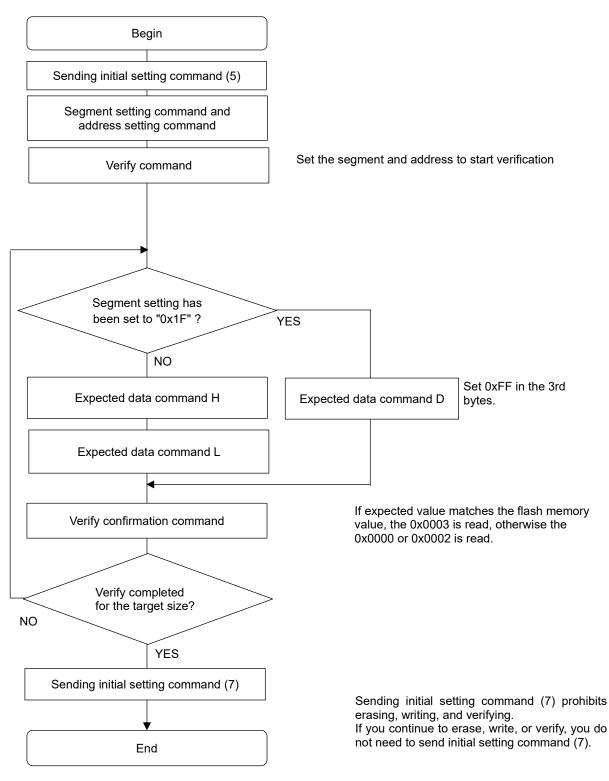

| 26.4.5.4 Verifying data in Specified Flash Memory Area                  |  |

| 26.4.6 Advanced Control of Flash Memory Erasing/Programming             |  |

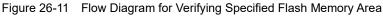

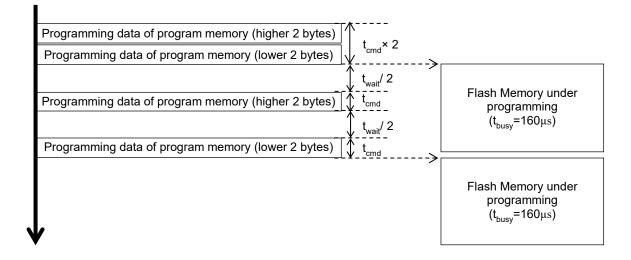

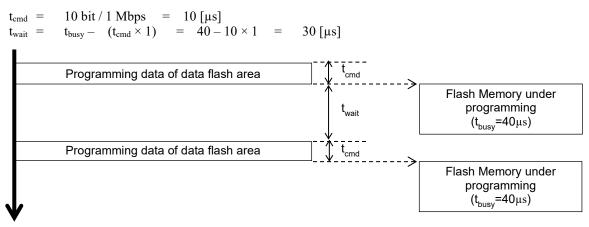

| 26.4.6.1 Timing to transmit command of Advanced Control                 |  |

| 26.4.6.2 Timeout during advanced control                                |  |

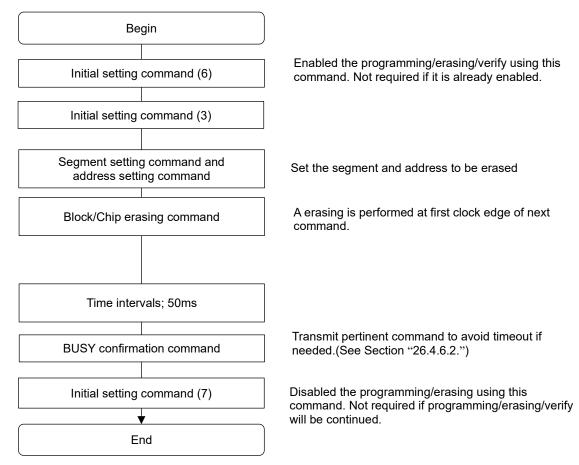

| 26.4.6.3 Erasing Data in Specified Flash Memory Area (Advanced control) |  |

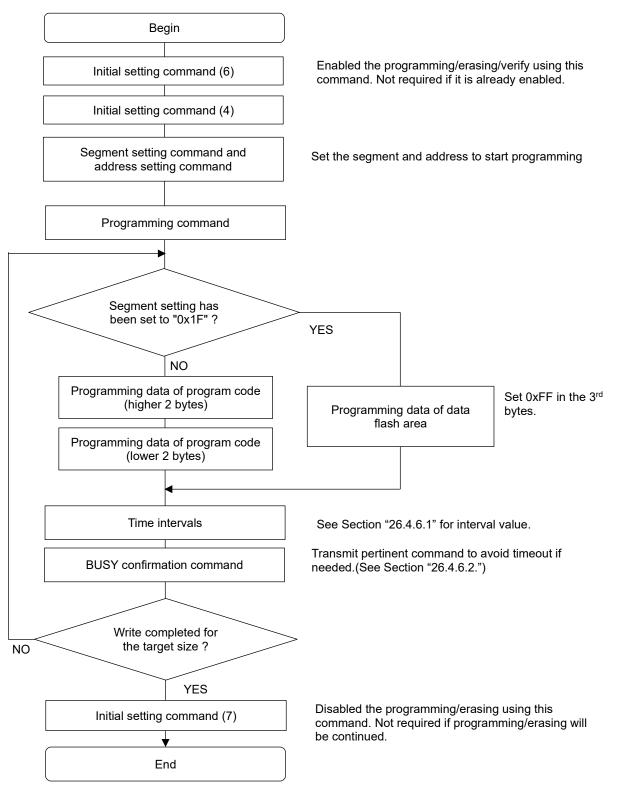

| 26.4.6.4 Programming to Specified Flash Memory Area (Advanced control)  |  |

#### Chapter 27 (Skip number)

| Chapter 28 On-Chip Debug Function                                             |  |

|-------------------------------------------------------------------------------|--|

| 28. On-Chip Debug Function                                                    |  |

| 28.1 General Description                                                      |  |

| 28.1.1 Features                                                               |  |

| 28.1.2 Configuration                                                          |  |

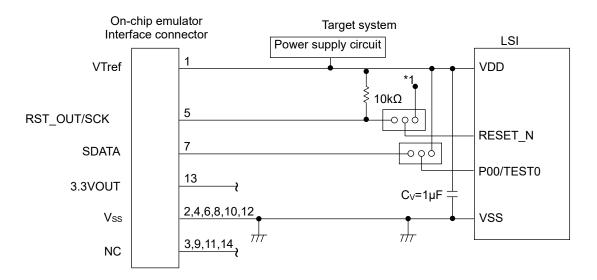

| 28.1.2.1 Using Power Supply of Target System (V <sub>DD</sub> =4.5V to 5.5V)  |  |

| 28.1.3 List of Pins                                                           |  |

| 28.2 How to Use On-chip Debug Function                                        |  |

| 28.3 Precautions.                                                             |  |

| 28.4 Operation of Peripheral Circuits during breaks in the on-chip debug mode |  |

| 28.5 Reset in the On-Chip Debug Tool                                          |  |

#### **Chapter 29 Safety Function**

| 29. Safety Function                                 |  |

|-----------------------------------------------------|--|

| 29.1 General Description                            |  |

| 29.1.1 Features                                     |  |

| 29.2 Description of Registers                       |  |

| 29.2.1 List of Registers                            |  |

| 29.2.2 RAM Guard Setting Register (RAMGD)           |  |

| 29.2.3 SFR Guard Setting Register 0 (SFRGD0)        |  |

| 29.2.4 SFR Guard Setting Register 1 (SFRGD1)        |  |

| 29.2.5 RAM Parity Setting Register (RASFMOD)        |  |

| 29.2.6 Communication Test Setting Register (COMFT0) |  |

|                                                     |  |

#### ML62Q2033/35/43/45 User's Manual Contents

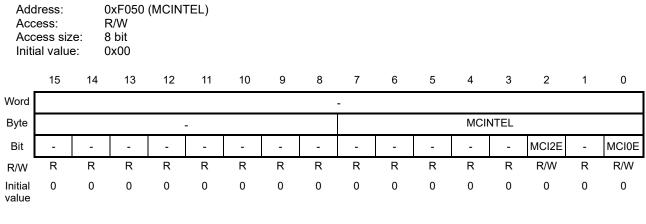

| 29.2.7 MCU Status Interrupt Enable Register (MCINTEL)               |  |

|---------------------------------------------------------------------|--|

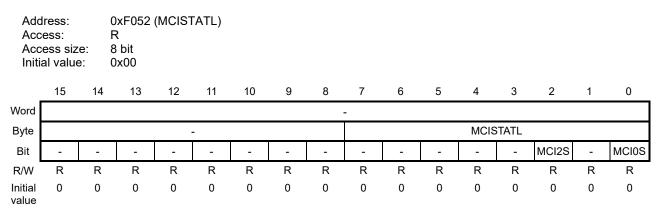

| 29.2.8 MCU Status Interrupt Register (MCISTATL)                     |  |

| 29.2.9 MCU Status Interrupt Clear Register L/H (MCINTCLL, MCINTCLH) |  |

| 29.3 Description of Operation                                       |  |

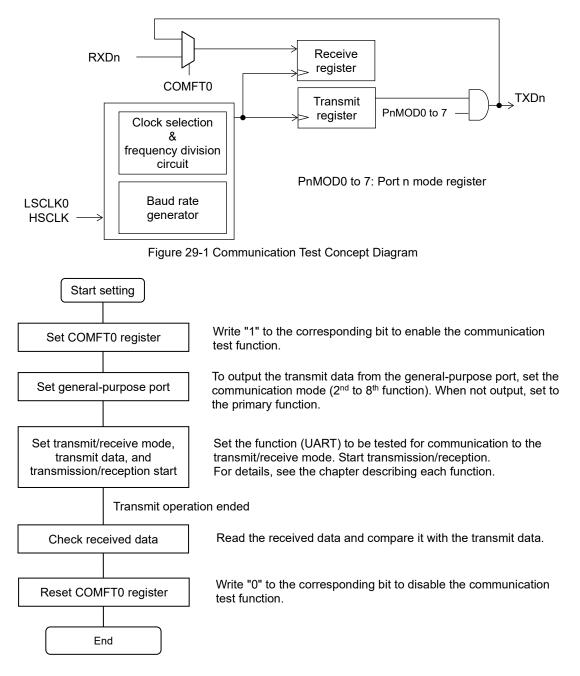

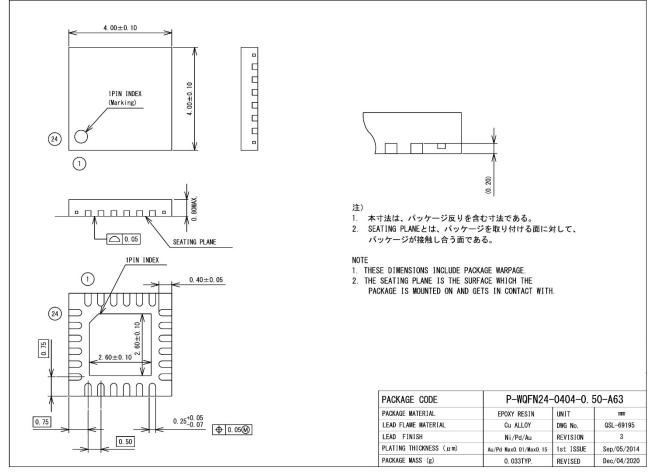

| 29.3.1 Communication Function Self-Test                             |  |

| 29.3.2 Unused ROM Area Access Reset Function                        |  |

| 29.3.3 Clock Mutual Monitoring Function                             |  |

| 29.3.4 WDT Counter Read                                             |  |

| 29.3.5 Port Output Level Test                                       |  |

| 29.3.6 Successive Approximation Type A/D Converter Test             |  |

### Chapter 30 Code Option

| 30. Code Option                 |  |

|---------------------------------|--|

| 30.1 General Description        |  |

| 30.1.1 Function List            |  |

| 30.2 Description of Code Option |  |

| 30.2.1 Reading from SFRs        |  |

| 30.2.2 Code Option 0 (CODEOP0)  |  |

| 30.2.3 Code Option 1 (CODEOP1)  |  |

| 30.2.4 Code Option 2 (CODEOP2)  |  |

| 30.3 Code Option Data Setting   |  |

| 30.4 Branch Trace Function      |  |

### **Chapter 31 Auxiliary Function**

| 31. Auxiliary Function                      |  |

|---------------------------------------------|--|

| 31.1 General Description                    |  |

| 31.2 Description of Registers               |  |

| 31.2.1 List of Registers                    |  |

| 31.2.2 Product ID Register 0,1 (PID0, PID1) |  |

| 31.3 Description of Operation               |  |

| 31.3.1 How to Confirm Unique ID             |  |

|                                             |  |

### Appendix

| Appendix A Register List               | A-1 |

|----------------------------------------|-----|

| Appendix B Package Dimensions          |     |

| Appendix C Instruction Execution Cycle |     |

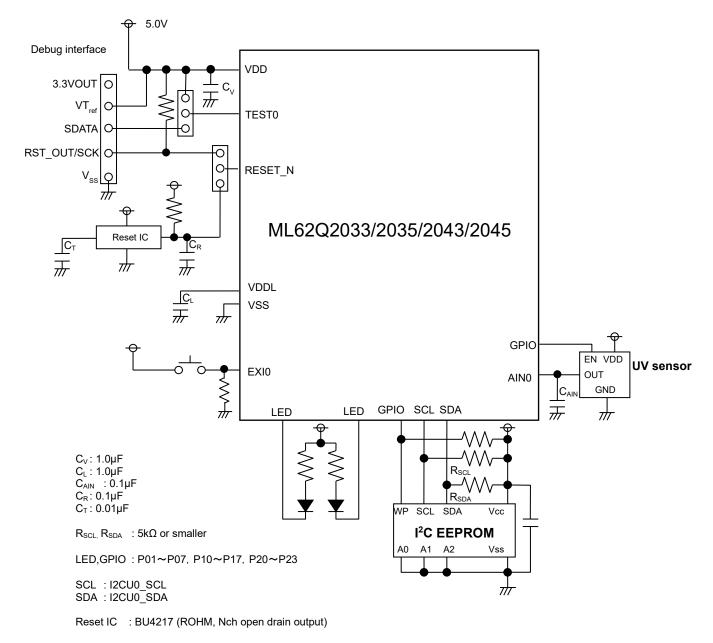

| Appendix D Application Circuit Example |     |

| Appendix E List of Notes               |     |

| Appendix D Dist of Protes              |     |

### **Revision History**

| te vision instory |               |

|-------------------|---------------|

| Revision History  | . <b>R-</b> 1 |

# **Chapter 1 Overview**

### 1. Overview

ML62Q2033/2035/2043/2045 are high performance CMOS 16-bit microcontrollers equipped with an 16-bit CPU nX-U16/100 and integrated with program memory (Flash memory), data memory (RAM), data Flash (Erase unit:128byte, Write unit:1byte) and rich peripheral functions such as the multiplier/divider, Clock generator, Operational timer (PWM, capture), Timer, General Purpose Ports, UART, I2C bus interface unit(Master, Slave), Successive approximation type 12bit A/D converter, 8bit D/A converter, PGA (Programable Gain Amp) and so on.

The CPU nX-U16/100 is capable of efficient instruction execution in 1-instruction 1-clock mode by pipeline architecture parallel processing.

The built-in on-chip debug function enables debugging and programming the software. Also, ISP (In-System Programming) function supports the Flash programming in production line.

#### Applications

Consumer and Industrial equipment (e.g., Household appliances, Housing equipment, Office equipment, Measurement instrumentation, etc.)

Note:

This product cannot be applicable for automotive use, automatic train control systems, and railway safety systems. Please contact ROHM sales office in advance if contemplating the integration of this product into applications that requires high reliability, such as transportation equipment for ships and railways, communication equipment for trunk lines, traffic signal equipment, power transmission systems, core systems for financial terminals and various safety control devices.

#### • Product list

Table1-1 shows the combination of ML62Q2033/2035/2043/2045 memory variations and package type.

| Program | Data memory | Data   | 20pin     | 24pin     |  |  |  |  |  |  |  |

|---------|-------------|--------|-----------|-----------|--|--|--|--|--|--|--|

| memory  | (RAM)       | Flash  | TSSOP20   | WQFN24    |  |  |  |  |  |  |  |

| 32Kbyte | 2Kbyte      | 4Kbyto | ML62Q2035 | ML62Q2045 |  |  |  |  |  |  |  |

| 16Kbyte | 2Kbyte      | 4Kbyte | ML62Q2033 | ML62Q2043 |  |  |  |  |  |  |  |

Table 1-1 Product List

### 1.1 Features

- CPU

- 16-bit RISC CPU : nX-U16/100 (A35 core)

- Instruction system : 16-bit length instructions

- Instruction set : Transfer, arithmetic operations, comparison, logic operations,

- multiplication/division, bit manipulations, bit logic operations, jump, conditional jump, call return stack, manipulations, arithmetic shift, and so on

- Built-in On-chip debug function (connect to the ROHM on-chip debug emulator)

- Minimum instruction execution time: 1 count of system clock Approximately 30.5µs/62.5ns (at 32.768kHz/16MHz system clock)

- Coprocessor for multiplication and division

- Signed or Unsigned is selectable

| Signed of Chargeled is selectable                    |                       |                        |  |  |  |  |  |  |  |  |

|------------------------------------------------------|-----------------------|------------------------|--|--|--|--|--|--|--|--|

| Parameter                                            | Expression            | Operation time [cycle] |  |  |  |  |  |  |  |  |

| Multiplication                                       | 16bit × 16bit         | 4                      |  |  |  |  |  |  |  |  |

| Division                                             | 32bit ÷ 16bit         | 8                      |  |  |  |  |  |  |  |  |

| DIVISION                                             | 32bit ÷ 32bit         | 16                     |  |  |  |  |  |  |  |  |

| Multiply-accumulate (non-saturating, non-saturating) | 16bit × 16bit + 32bit | 4                      |  |  |  |  |  |  |  |  |

- Operating voltage and temperature

- Operating voltage  $: V_{DD} = 4.5 \text{ to } 5.5 \text{V}$

- Operating temperature: -40°C to +105°C

- Flash memory

| Parameter                    | Program memory area | Data Flash memory area |  |  |

|------------------------------|---------------------|------------------------|--|--|

| Erase/Write count            | 100cycles           | 10,000cycles           |  |  |

| Write unit                   | 16bit (2byte)       | 8bit (1byte)           |  |  |

| Erase unit                   | 16Kbyte/1Kbyte      | all area/128byte       |  |  |

| Erase/Write temperature (Ta) | 0°C to +40°C        | -40°C to +85°C         |  |  |

- Background Operation (CPU can work while erasing and rewriting to the Data Flash memory area.)

- The built-in on-chip debug function and ISP (In-System Programming) function enable Flash programming This product uses Super Flash® technology licensed from Silicon Storage Technology, Inc.

- Super Flash® is a registered trademark of Silicon Storage Technology, Inc.

- Data RAM area

- Rewrite unit: 8bit/16bit (1byte/2byte)

High-speed system clock (HSCLK)

- Parity check function is available (interrupt or reset is generatable at Parity error)

- Clock generation circuit

- Low-speed clock (LSCLK0)

- Internal low-speed RC oscillation (RC32K) : Approx. 32.768kHz - High-speed source clock (HSOCLK)

- : Available for PWM generation circuit clock

- PLL oscillation

: 64MHz : 16MHz, generated by dividing HSOCLK

- Reset

- System Resets by reset input pin, Power-On Reset, Low Level Detector (LLD) reset, Watchdog timer (WDT) overflow, WDT invalid clear, RAM parity error reset, and Program Counter error reset (instruction access to unused ROM area)

- Software reset by BRK instruction (reset CPU only) \_

- Reset the peripherals individually/collectively by software

- Power management

- Two stand-by mode.

- STOP mode (All clocks are stopped)

- HALT mode (clocks for System are stopped)

- Individual clock input control to the peripheral blocks by software

- Clock gear: High-speed system clock frequency is changeable dynamically

- (1/1, 1/2, 1/4, 1/8, 1/16, 1/32 of HSCLK)

• Interrupt controller

- I/O port

- Non-maskable interrupt source : 1 (Internal sources: WDT)

- Maskable interrupt sources : 22 (included the external interrupt 4 sources)

- Four step interrupt levels

- External interrupt ports (EXI)

: 4 (selectable from Max.8 pins) with sampling filter

- and edge (rise, fall, both) selection.

- General-purpose ports (GPIO)

- : Max. 20 (Including pins for shared functions)

- Carrier frequency output function (for IR communication)

- Watchdog timer (WDT): 1 channel

- Overflow period : 8selectable (7.8, 15.6, 31.3, 62.5, 125, 500, 2000, 8000ms)

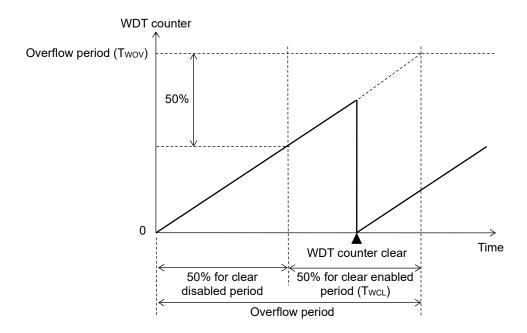

- Selectable window function (enable or disable): configurable clear enable period (50% or 75% of overflow period) with invalid clear. When disable, interrupts the first overflow and resets the second overflow. When enable, reset occurs for the first overflow.

- Selectable WDT operation : select Enable or Disable by code option

- Selectable operation during HALT mode (Continue counting/Stop counting)

- WDT counter operation monitoring function (Readable WDT counter)

- Operational timer: 6 channels

- Various modes (Continuous, One shot, capture, and PWM mode)

- Event trigger (external terminal, 16bit timer, operational timer, comparator) input is available

- Selectable counter clock from various sources (LSCLK0, HSCLK (16MHz), HSOCLK (64MHz), divided by 1 to 8 of external pin input)

- Logic AND output with several channel output (Operational timer output, comparator output, and external pin input) is available

- 16-bit General timers: 1 channel

- Selectable counter clock from various sources (LSCLK, HSCLK (16MHz), and external clock divided by 1 to 8)

- UART (Half-duplex/Full-duplex communication mode): 2 channels

- Selectable from 5 to 8bit length, parity or no parity, odd parity or even parity, 1 stop bit or 2 stop bits, Positive logic or Negative logic, LSB first or MSB first

- Sampling filter for receiving data and start bit

- Built-in baud rate generator (HSCLK@16MHz: 300bps to 2Mbps, LSCLK: up to 2400bps)

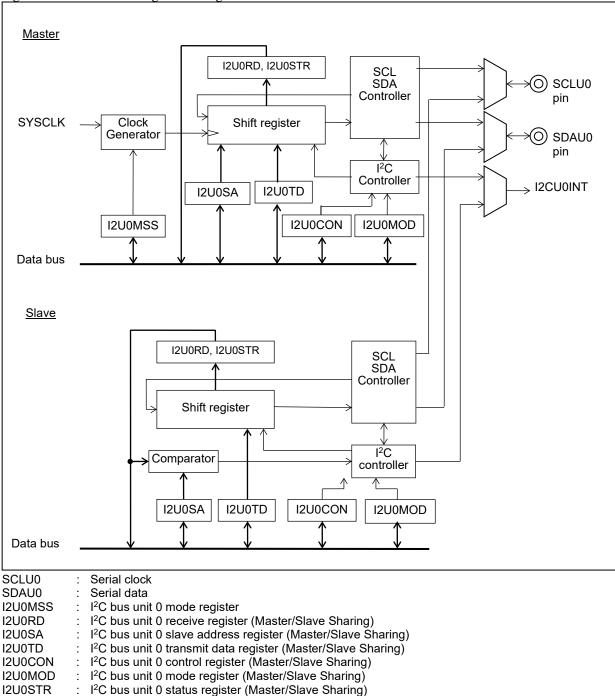

- I<sup>2</sup>C bus: 1 channel

- Select from Master mode or Slave mode: 1channel. Master mode only: 1channel

- Standard mode (100kbps), fast mode (400kbps) and 1Mbps mode (1Mbps)

- 7bit address format

- Master mode: Handshake (Clock synchronization), 10bit Master address format is supported

- Slave mode: Clock stretch function,

- Successive approximation type 12bit A/D converter (SA-ADC): input 5 channels

- Conversion time: Min. 1.375µs / ch (When the conversion clock frequency is 16MHz)

- Reference voltages (V<sub>ADCREF</sub>) are selectable from VDD pin input voltage or Internal reference voltage (V<sub>ADCREF</sub>, Approx. 2.5V)

- Dedicated result register for each channel

- Interrupt by Continuous conversion and Trigger start

- Programable-Gain-Amp (PGA): 1 channel

- Amplification factor : 4/ 8/16/ 32

- Voltage input pin is selectable (AIN0/ AIN1/ AIN2/ AIN3)

- Analog comparator (CMP): 3 channels

- Selectable interrupt from the comparator output (rising edge or falling edge) and sampling

- Selectable reference voltage (V<sub>CMPREFn n=0 to 2</sub>) from external pin input, internal reference voltage (0.8V) (V<sub>CMPREFI</sub>), and D/A converter

- D/A converter (DAC): 2 channels

- Resolution : 8 bit

- Output impedance :10kΩ (Typ.)

- R-2R ladder type

- Reference voltages (V<sub>DACREF</sub>) are selectable from VDD pin input voltage or Internal reference voltage (0.8V) (V<sub>DACREF</sub>)

- \_

- Low Level Detector (LLD): 1 channel

- Reset generating

- Sampling filter

- Low power operation

- Safety Function

- RAM/SFR guard

- RAM parity error detection

- ROM unused area access reset (instruction access)

- WDT counter monitoring

- SA-ADC test

- Communication loop back test (UART, I<sup>2</sup>C bus(master))

- GPIO test

- Shipping package

| Package              | Body size                     | Pin pitch | Packing form and Product name                |                                              |  |  |  |  |

|----------------------|-------------------------------|-----------|----------------------------------------------|----------------------------------------------|--|--|--|--|

|                      | (including lead)<br>[mm × mm] | [mm]      | Tray                                         | Tape & Reel                                  |  |  |  |  |

| 20 pin plastic TSSOP | 6.5 × 4.4<br>(6.5 × 6.4)      | 0.65      | ML62Q2033-xxxTDZWARZ<br>ML62Q2035-xxxTDZWARZ | ML62Q2033-xxxTDZWATZ<br>ML62Q2035-xxxTDZWATZ |  |  |  |  |

| 24 pin plastic WQFN  | 4.0 × 4.0<br>( - )            | 0.50      | ML62Q2043-xxxGDZW5AY<br>ML62Q2045-xxxGDZW5AY | ML62Q2043-xxxGDZW5BY<br>ML62Q2045-xxxGDZW5BY |  |  |  |  |

xxx: ROM code number, (NNN: ROM code is blank)

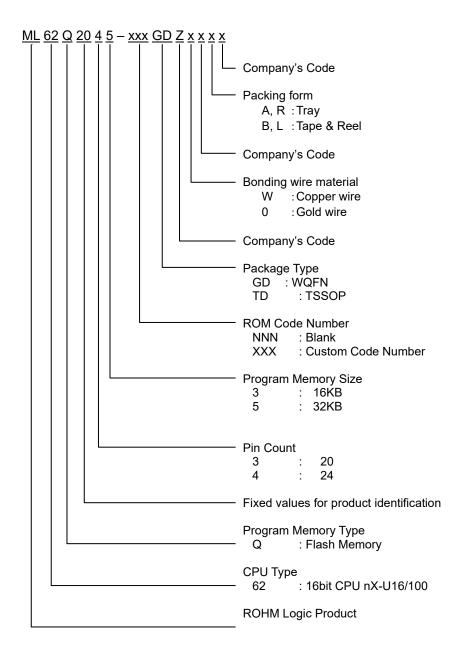

### 1.1.1 How To Read The Part Number

Figure 1-1 Part Number

## 1.1.2 Main Function List

| Table 1-2 Main Function List |           |           |                 |                                       |                                                  |                        |                           |                               |                                    |                  |                              |                                |                     |           |                                    |                                          |                        |                    |          |  |

|------------------------------|-----------|-----------|-----------------|---------------------------------------|--------------------------------------------------|------------------------|---------------------------|-------------------------------|------------------------------------|------------------|------------------------------|--------------------------------|---------------------|-----------|------------------------------------|------------------------------------------|------------------------|--------------------|----------|--|

|                              | Pin       |           |                 |                                       |                                                  | Interrupt              |                           |                               | Timer                              |                  |                              | Communication                  |                     | Analog    |                                    |                                          |                        |                    |          |  |

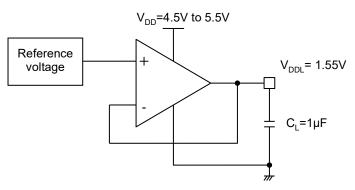

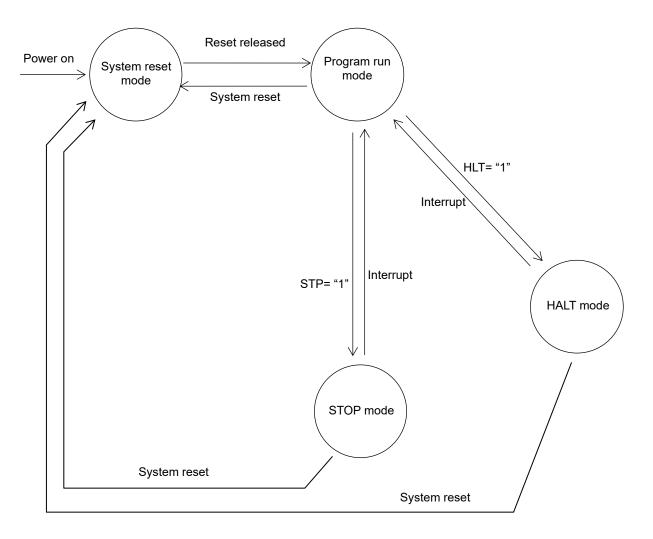

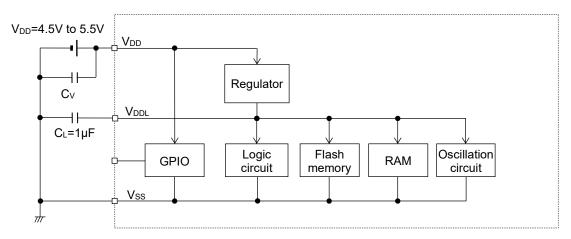

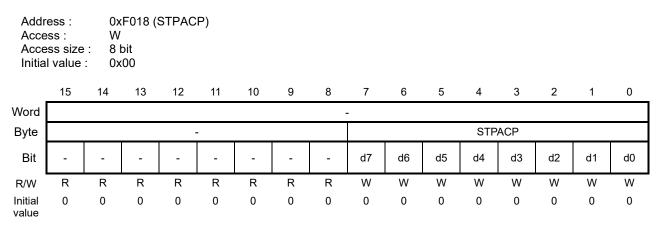

| Part number                  | Total pin | Power pin | Reset Input pin | General purpose I/O pin <sup>∗1</sup> | General purpose I/O pin (LED drive is supported) | External interrupt pin | External interrupt source | Non maskable interrupt source | Internal maskable interrupt source | 16bit Timer [ch] | 16bit operational Timer [ch] | 16bit operational Timer [Port] | Watchdog Timer [ch] | UART [ch] | l²C bus unit (Master / Slave) [ch] | 12bit Successive type A/D converter [ch] | Analog Comparator [ch] | D/A converter [dh] | PGA [ch] |  |