Dear customer

ROHM Co., Ltd. ("ROHM"), on the 1st day of April, 2024, has absorbed into merger with 100%-owned subsidiary of LAPIS Technology Co., Ltd.

Therefore, all references to "LAPIS Technology Co., Ltd.", "LAPIS Technology" and/or "LAPIS" in this document shall be replaced with "ROHM Co., Ltd." Furthermore, there are no changes to the documents relating to our products other than the company name, the company trademark, logo, etc.

Thank you for your understanding.

ROHM Co., Ltd. April 1, 2024

FEUL62Q2500-04

## ML62Q2500 Group User's Manual

Issue Date: Mar. 26, 2024

#### <u>Notes</u>

1) When using LAPIS Technology Products, refer to the latest product information and ensure that usage conditions (absolute maximum ratings\*1, recommended operating conditions, etc.) are within the ranges specified. LAPIS Technology disclaims any and all liability for any malfunctions, failure or accident arising out of or in connection with the use of LAPIS Technology Products outside of such usage conditions specified ranges, or without observing precautions. Even if it is used within such usage conditions specified ranges, semiconductors can break down and malfunction due to various factors. Therefore, in order to prevent personal injury, fire or the other damage from break down or malfunction of LAPIS Technology Products, please take safety at your own risk measures such as complying with the derating characteristics, implementing redundant and fire prevention designs, and utilizing backups and fail-safe procedures.

\*1: Absolute maximum ratings: a limit value that must not be exceeded even momentarily.

- 2) The Products specified in this document are not designed to be radiation tolerant.

- 3) Descriptions of circuits, software and other related information in this document are provided only to illustrate the standard operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. And the peripheral conditions must be taken into account when designing circuits for mass production. LAPIS Technology disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, and other related information.

- 4) No license, expressly or implied, is granted hereby under any intellectual property rights or other rights of LAPIS Technology or any third party with respect to LAPIS Technology Products or the information contained in this document (including but not limited to, the Product data, drawings, charts, programs, algorithms, and application examples, etc.). Therefore, LAPIS Technology shall have no responsibility whatsoever for any dispute, concerning such rights owned by third parties, arising out of the use of such technical information.

- 5) LAPIS Technology intends our Products to be used in a way indicated in this document. Please be sure to contact a ROHM sales office if you consider the use of our Products in different way from original use indicated in this document. For use of our Products in medical systems, please be sure to contact a LAPIS Technology representative and must obtain written agreement. Do not use our Products in applications which may directly cause injuries to human life, and which require extremely high reliability, such as aerospace equipment, nuclear power control systems, and submarine repeaters, etc. LAPIS Technology disclaims any and all liability for any losses and damages incurred by you or third parties arising by using the Product for purposes not intended by us without our prior written consent.

- 6) All information contained in this document is subject to change for the purpose of improvement, etc. without any prior notice. Before purchasing or using LAPIS Technology Products, please confirm the latest information with a ROHM sales office. LAPIS Technology has used reasonable care to ensure the accuracy of the information contained in this document, however, LAPIS Technology shall have no responsibility for any damages, expenses or losses arising from inaccuracy or errors of such information.

- Please use the Products in accordance with any applicable environmental laws and regulations, such as the RoHS Directive. LAPIS Technology shall have no responsibility for any damages or losses resulting non-compliance with any applicable laws or regulations.

- 8) When providing our Products and technologies contained in this document to other countries, you must abide by the procedures and provisions stipulated in all applicable export laws and regulations, including without limitation the US Export Administration Regulations and the Foreign Exchange and Foreign Trade Act.

- 9) Please contact a ROHM sales office if you have any questions regarding the information contained in this document or LAPIS Technology's Products.

- 10) This document, in part or in whole, may not be reprinted or reproduced without prior consent of LAPIS Technology.

(Note) "LAPIS Technology" as used in this document means LAPIS Technology Co., Ltd.

Copyright 2022 - 2024 LAPIS Technology Co., Ltd.

## LAPIS Technology Co., Ltd.

2-4-8 Shinyokohama, Kouhoku-ku, Yokohama 222-8575, Japan https://www.lapis-tech.com/en/

LTSZ08023 • 01 • 002

### Notes for product usage

Notes on this page are applicable to the all LAPIS Technology microcontroller products. For individual notes on each LAPIS Technology microcontroller product, refer to [Note] in the chapters of each user's manual.

The individual notes of each user's manual take priority over those contents in this page if they are different.

#### 1. HANDLING OF UNUSED INPUT PINS

Fix the unused input pins to the power pin or GND to prevent to cause the device performing wrong operation or increasing the current consumption due to noise, etc. If the handlings for the unused pins are described in the chapters, follow the instruction.

#### 2. STATE AT POWER ON

At the power on, the data in the internal registers and output of the ports are undefined until the power supply voltage reaches to the recommended operating condition and "L" level is input to the reset pin.

On LAPIS Technology microcontroller products that have the power on reset function, the data in the internal registers and output of the ports are undefined until the power on reset is generated.

Be careful to design the application system does not work incorrectly due to the undefined data of internal registers and output of the ports.

#### 3. ACCESS TO UNUSED MEMORY

If reading from unused address area or writing to unused address area of the memory, the operations are not guaranteed.

#### 4. CHARACTERISTICS DIFFERENCE BETWEEN THE PRODUCT

Electrical characteristics, noise tolerance, noise radiation amount, and the other characteristics are different from each microcontroller product.

When replacing from other product to LAPIS Technology microcontroller products, please evaluate enough the apparatus/system which implemented LAPIS Technology microcontroller products.

#### 5. USE ENVIRONMENT

When using LAPIS Technology microcontroller products in a high humidity environment and an environment where dew condensation, take moisture-proof measures.

### Preface

This manual describes the operation of the hardware of the 16-bit microcontroller ML62Q2500 Group.

See the relevant manuals listed in supplementary volume; "MCU Relevant Documents list" as necessary.

| Classification | Notation               | Description                                                                                                          |  |  |  |  |  |

|----------------|------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Numeric value  | XXh, XXH, 0xXX         | Indicates a hexadecimal number.                                                                                      |  |  |  |  |  |

| Unit           | word, W                | 1 word = 16 bits                                                                                                     |  |  |  |  |  |

|                | byte, B                | 1 byte = 8 bits                                                                                                      |  |  |  |  |  |

|                | nibble, N              | 1 nibble = 4 bits                                                                                                    |  |  |  |  |  |

|                | mega-, M               | 10 <sup>6</sup>                                                                                                      |  |  |  |  |  |

|                | kilo-, K               | 2 <sup>10</sup> = 1024                                                                                               |  |  |  |  |  |

|                | kilo-, k               | 10 <sup>3</sup> = 1000                                                                                               |  |  |  |  |  |

|                | milli-, m              | 10 <sup>-3</sup>                                                                                                     |  |  |  |  |  |

|                | micro-, μ              | 10 <sup>-6</sup>                                                                                                     |  |  |  |  |  |

|                | nano-, n               | 10 <sup>-9</sup>                                                                                                     |  |  |  |  |  |

|                | second, s (lower case) | second                                                                                                               |  |  |  |  |  |

| Terminology    | "H" level              | Indicates high level voltage $V_{IH}$ and $V_{OH}$ as specified by the electrical characteristics in the data-sheet. |  |  |  |  |  |

|                | "L" level              | Indicates low level voltage $V_{IL}$ and $V_{OL}$ as specified by the electrical characteristics in the data-sheet.  |  |  |  |  |  |

|                | SFR                    | Special function register. It is control register for system or peripherals.                                         |  |  |  |  |  |

### Notation

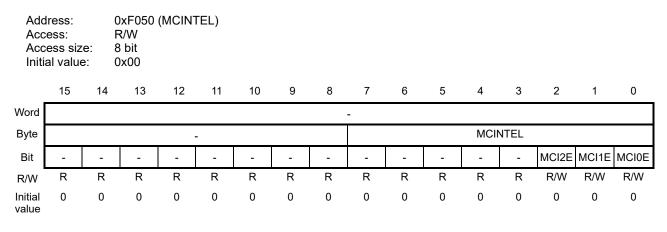

• Register description

"R/W" indicates that Read/Write attribute. "R" indicates that data can be read and "W" indicates that data can be written. "R/W" indicates that data can be read or written.

MSB: The highest bit of 16-bit register LSB: The lowest bit of 16-bit register

Registers that have a word symbol allow the word-access. If writing or reading the registers not using the word symbol, specify the even number addresses.

|                  | F    |                 |           | Invalio   | l bit: Tl | his bit re | eturns "  | 0" for re | eading   | and writ | ting to f | his bit i | is ignore | ed. |   |            |

|------------------|------|-----------------|-----------|-----------|-----------|------------|-----------|-----------|----------|----------|-----------|-----------|-----------|-----|---|------------|

|                  |      |                 |           |           |           |            | v         | Vord syı  | mbol na  | ame      |           |           |           |     |   |            |

|                  | į    |                 | В         | yte sym   | ibol na   | me         |           |           |          |          |           |           |           |     |   |            |

|                  |      | Bit symt        | ool nam   | ne i      |           |            |           |           |          |          |           |           |           |     |   |            |

|                  |      | :<br> <br> <br> | 40        | 10        |           | 10         | 0         |           | 7        | 0        | -         |           | 0         | 0   |   | 0          |

| <i>.</i> . Г     | 15   | 14              | 13        | 12        | 11        | 10         | 9         | 8         | 7        | 6        | 5         | 4         | 3         | 2   | 1 | 0          |

| Word             | <br> |                 |           |           |           |            |           | FHCK      | MOD      |          |           |           |           |     |   |            |

| Byte             |      |                 |           | FHCK      | NODH      |            |           |           | FHCKMODL |          |           |           |           |     |   |            |

| Bit              | ÷    | OUTC<br>2       | OUTC<br>1 | OUTC<br>0 | _         | SYSC<br>2  | SYSC<br>1 | SYSC<br>0 | _        | _        | -         | _         | _         | _   | _ | HOS<br>CM0 |

| R/W              | R    | R/W             | R/W       | R/W       | R         | R/W        | R/W       | R/W       | R        | R        | R         | R         | R         | R   | R | R/W        |

| Initial<br>value | 0    | 1               | 0         | 0         | 0         | 1          | 0         | 0         | 0        | 0        | 0         | 0         | 0         | 0   | 0 | 0          |

|                  |      |                 |           |           |           |            |           |           |          |          |           |           |           |     |   |            |

|                  |      |                 |           |           |           |            |           |           |          |          |           |           |           |     |   |            |

Initial value after the system reset

## **Chapter 1 Overview**

#### • Please see the "Notes" and the "Notes for product usage" in this document.

#### 1. Overview

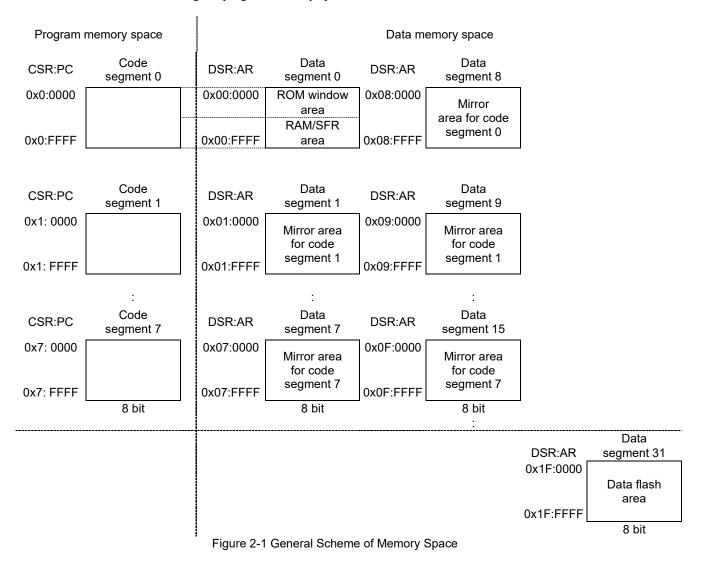

ML62Q2500 Group is a high performance CMOS 16-bit microcontroller equipped with an 16-bit CPU nX-U16/100 and integrated with program memory(Flash memory), data memory(RAM), data Flash (Erase unit:128byte, Write unit:1byte) and rich peripheral functions such as the multiplier/divider, CRC generator, Clock generator, Timer, General Purpose Ports, UART, Synchronous serial port, I<sup>2</sup>C bus interface unit(Master, Slave), Voltage Level Supervisor(VLS), Successive approximation type 12bit A/D converter, Safety function (IEC60730/60335 Class B) and so on. The CPU nX-U16/100 is capable of efficient instruction execution in 1-instruction 1-clock mode by pipeline architecture

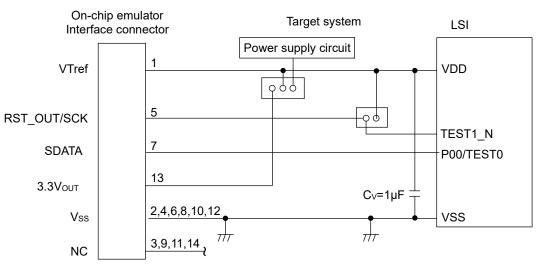

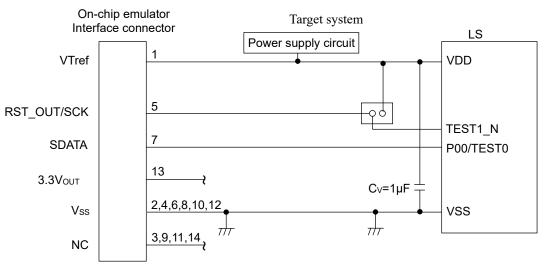

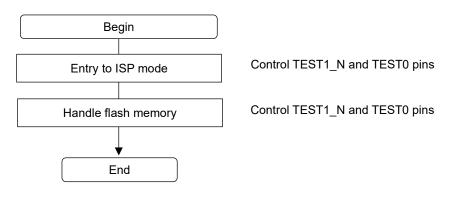

parallel processing. The built-in on-chip debug function enables debugging and programming the software. Also, ISP (In-System Programming) function supports the Flash programming in production line.

• Applications

Consumer and Industrial equipment (e.g., Household appliances, Housing equipment, Office equipment, Measurement instrumentation, etc)

#### [NOTE]

This product cannot be applicable for automotive use, automatic train control systems, and railway safety systems. Please contact ROHM sales office in advance if contemplating the integration of this product into applications that requires high reliability, such as transportation equipment for ships and railways, communication equipment for trunk lines, traffic signal equipment, power transmission systems, core systems for financial terminals and various safety control devices.

#### Product List

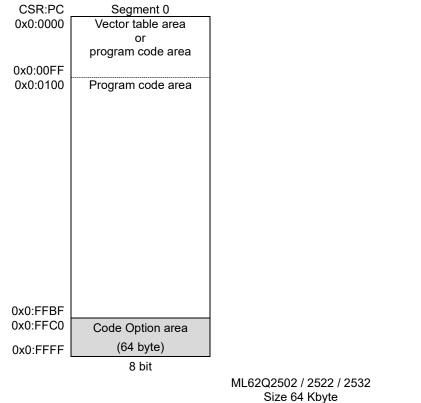

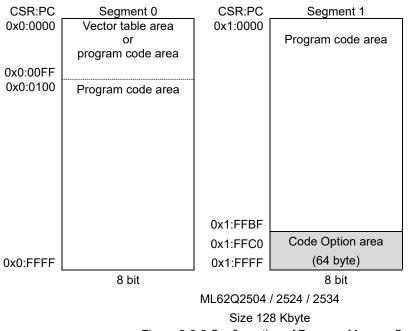

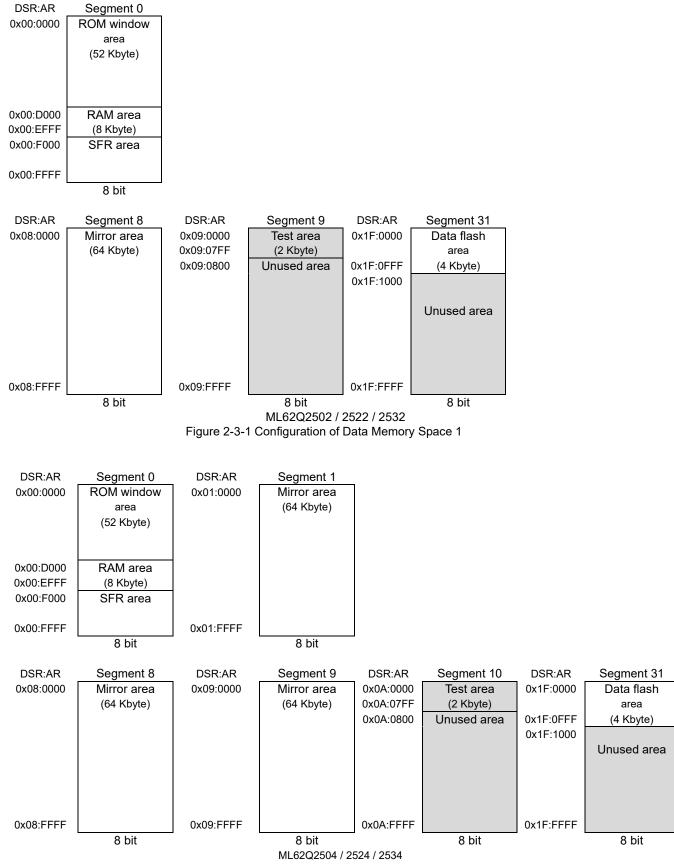

The ML62Q2500 Group has products as show in the Table 1-1 with multiple package and memory sizes combinations.

| Program memory | Data memory<br>(RAM) | Data Flash | 32pin<br>TQFP32<br>WQFN32 | 40pin<br>WQFN40 | 48pin<br>TQFP48<br>WQFN48 |  |  |  |  |  |  |

|----------------|----------------------|------------|---------------------------|-----------------|---------------------------|--|--|--|--|--|--|

| 128Kbyte       | 8Kbyte               | 4Kbyte     | ML62Q2504                 | ML62Q2524       | ML62Q2534                 |  |  |  |  |  |  |

| 64Kbyte        | orbyte               | 4NDyte     | ML62Q2502                 | ML62Q2522       | ML62Q2532                 |  |  |  |  |  |  |

#### Table 1-1 Product List

#### 1.1 Features

- CPU

- 16-bit RISC CPU: nX-U16/100 (A35 core)

- Instruction system: 16-bit length instructions

- Instruction set: Transfer, arithmetic operations, comparison, logic operations, multiplication/division, bit manipulations, bit logic operations, jump, conditional jump, call return stack manipulations, arithmetic shift, and so on

- Built-in On-chip debug function (connect to the LAPIS Technology on-chip-debug emulator)

- Minimum instruction execution time : 1 count of system clock Approximately 30.5µs/62.5ns/41.6ns (at 32.768kHz/16 MHz/24MHz system clock)

- Coprocessor for multiplication and division

- Signed or Unsigned is selectable

| Parameter                                            | Expression            | Operation time [cycle] |

|------------------------------------------------------|-----------------------|------------------------|

| Multiplication                                       | 16bit × 16bit         | 4                      |

| Division                                             | 32bit ÷ 16bit         | 8                      |

|                                                      | 32bit ÷ 32bit         | 16                     |

| Multiply-accumulate (non-saturating, non-saturating) | 16bit × 16bit + 32bit | 4                      |

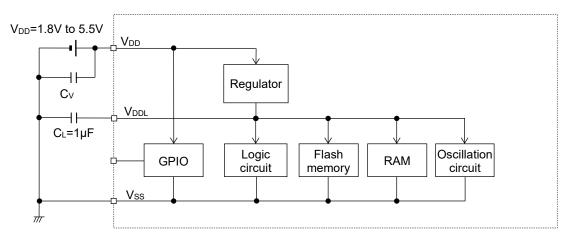

- Operating voltage and temperature

- Operating voltage:  $V_{DD} = 1.8$  to 5.5 V

- Operating temperature: -40 °C to +105 °C

- Flash memory

| Parameter               | Program memory area | Data Flash memory area |

|-------------------------|---------------------|------------------------|

| Erase/Write count       | 100 cycles          | 10,000 cycles          |

| Write unit              | 32bit(4byte)        | 8bit(1byte)            |

| Erase unit              | 16Kbyte/1Kbyte      | all area/128byte       |

| Erase/Write temperature | 0 °C to +40 °C      | -40 °C to +85 °C       |

- Background Operation (CPU can work while erasing and rewriting to the Data Flash memory area.)

- The built-in on-chip debug function and ISP (In-System Programming) function enable Flash programming This product uses Super Flash<sup>®</sup> technology licensed from Silicon Storage Technology, Inc.

Super Flash<sup>®</sup> is a registered trademark of Silicon Storage Technology, Inc.

- Data RAM area

- Rewrite unit: 8bit/16bit (1byte/2byte)

- Parity check function is available (interrupt or reset is generatable at Parity error)

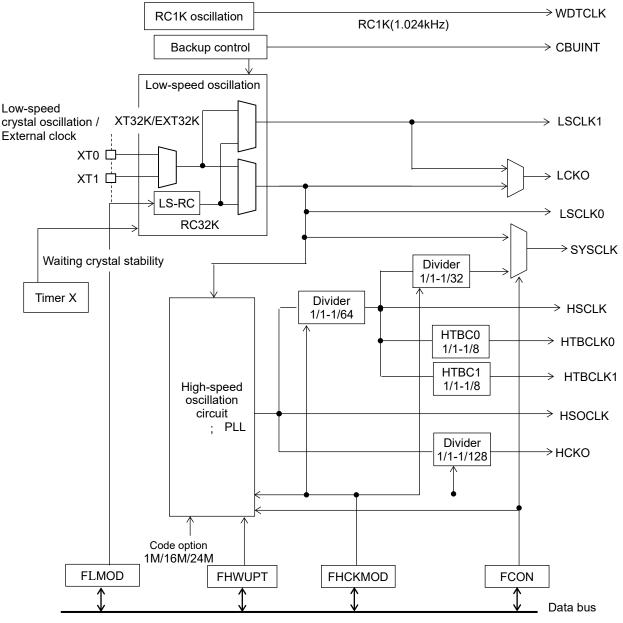

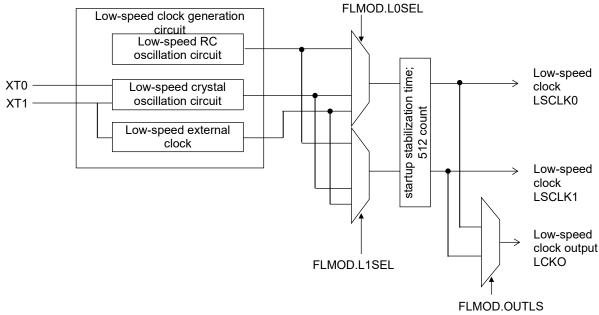

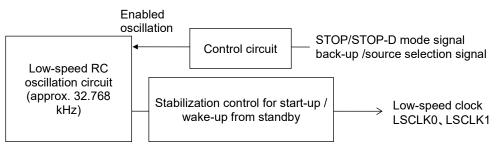

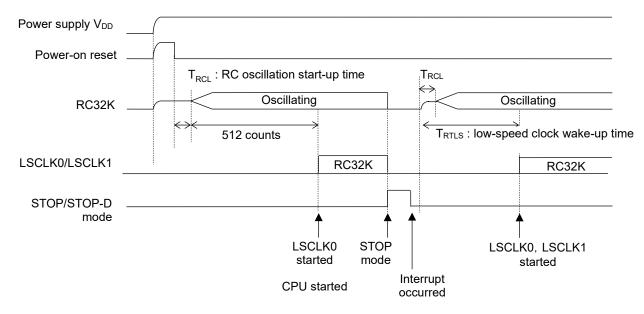

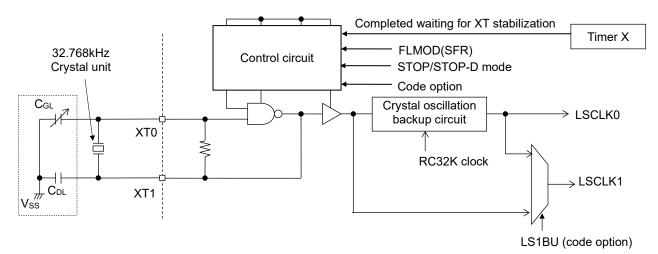

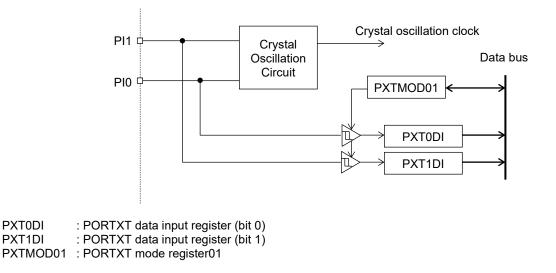

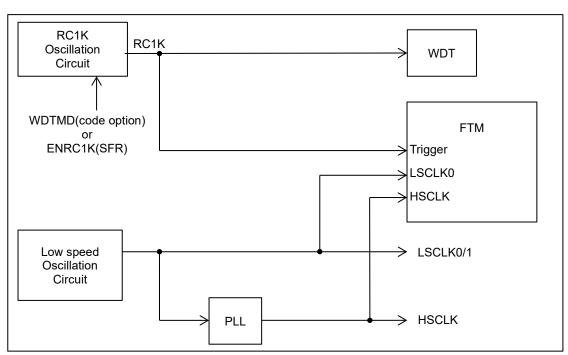

- Clock generation circuit

- Low-speed clock (LSCLK) : Approximately 32.768 kHz

- Internal low-speed RC oscillation (RC32K)

- External low-speed clock input (EXT32K)

- External low-speed crystal oscillation (XT32K)

4 selectable crystal oscillation mode (Tough, Normal, Low power and Ultra low power mode)

Tough mode is largest oscillation allowance to make highest resistance against leakage between the pins. Low power mode is smallest oscillation allowance to make lower power consumption.

- High-speed clock (HSCLK)

- PLL oscillation: 3 selectable oscillation frequency (24MHz ,16MHz and 1MHz) by code option

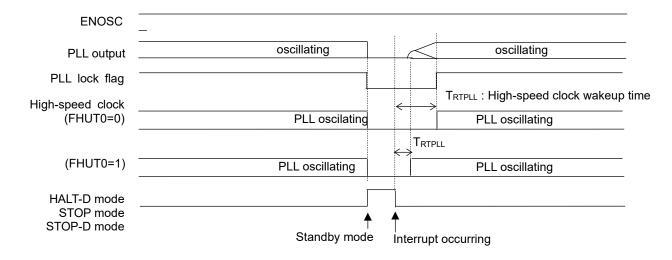

- Watch Dog Timer (WDT): built-in independent clock for WDT (RC1K: Approximately 1.024kHz)

- High-speed time base clock (HTBCLK)

- Generates a clock with a period of 2 to 8 times that of HSCLK as a peripheral clock.

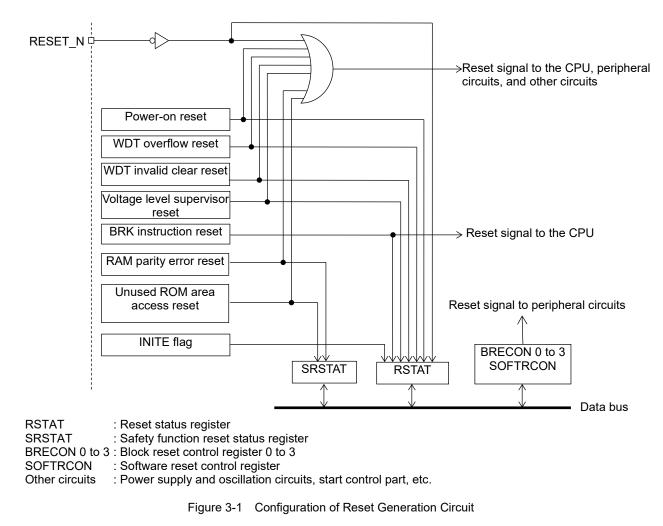

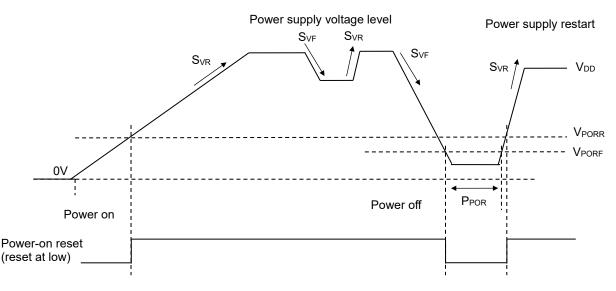

- Reset

- System Resets by reset input pin, Power-On Reset, voltage level supervisor (VLS), WDT overflow, WDT invalid clear, RAM parity error, and PC error (unused ROM area access (instruction access))

- Software reset by BRK instruction (reset CPU only)

- Reset the peripherals individually/collectively by software

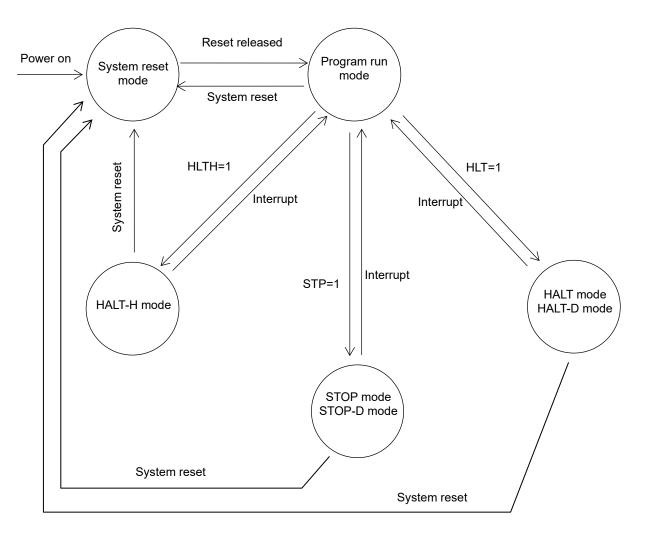

- Power management

- Optimal power management with various standby modes

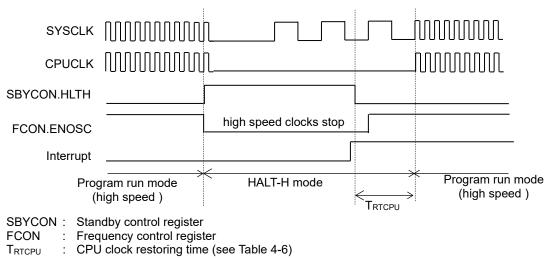

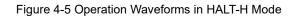

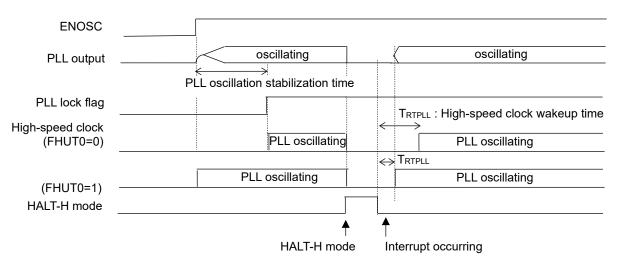

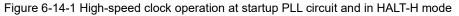

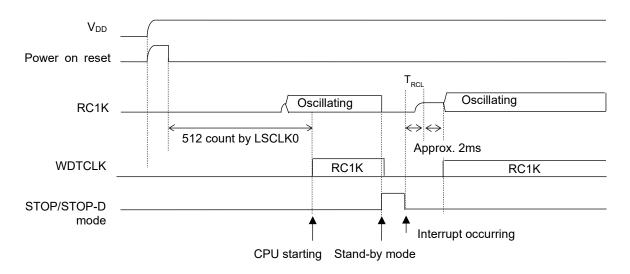

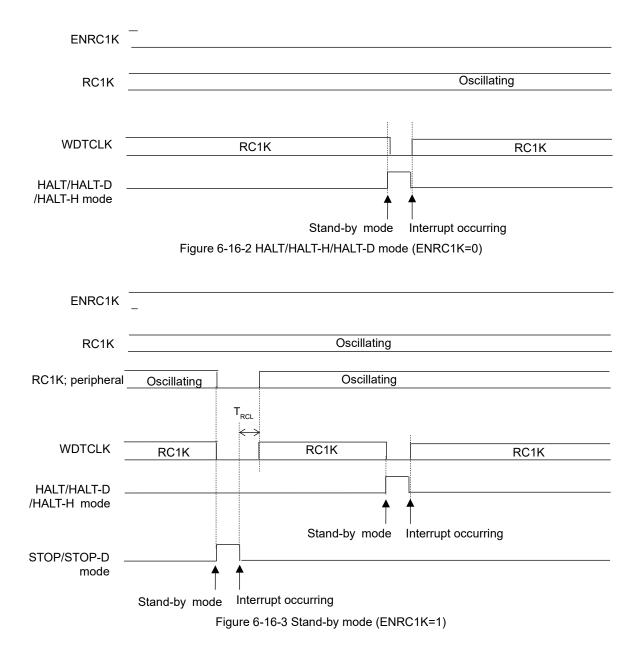

- STOP/STOP-D mode(All clocks are stopped), HALT-D mode(clocks for System and part of the peripheral block are stopped), HALT/HALT-H mode(clocks for System are stopped)

- HALT-D mode is suitable for long term standby, HALT-H mode is suitable for short term Intermittent operation standby

- Individual clock input control to the peripheral blocks by software

- High-speed clock frequency(HSCLK) is configurable (1/1, 1/2, 1/4, 1/8, 1/16, 1/32, 1/64 of PLL clock, Max 7steps)

- Clock gear: High-speed system clock frequency is changeable dynamically

- (1/1, 1/2, 1/4, 1/8, 1/16, 1/32 of HSCLK, Max 6steps)

- Interrupt controller

- Non-maskable interrupt source: 1 (internal sources: WDT)

- Maskable interrupt sources: 34 (included the external interrupt 8 sources)

- Four step interrupt levels

- External interrupt ports: 8 (selectable from max.24 pins) with sampling filter and edge (rise, fall, both) selection

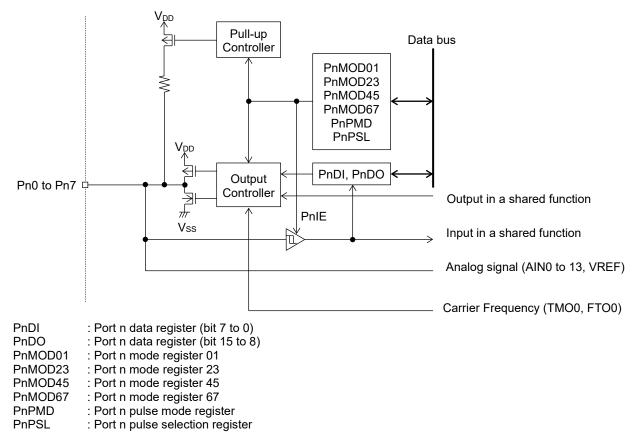

- General-purpose ports (GPIO)

- I/O port: Max. 40 (Including pins for shared functions)

- Input port: Max. 3(Including one pin for shared on-chip debug and two pins for shared low speed crystal oscillation)

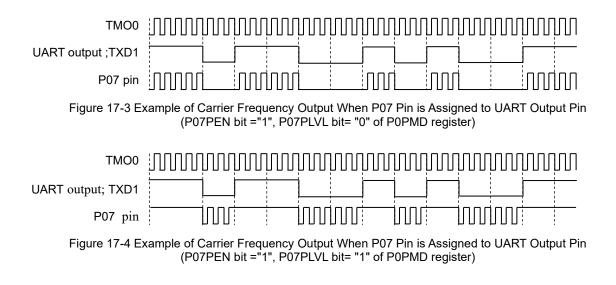

: 1 channel

- Carrier frequency output function (for IR communication)

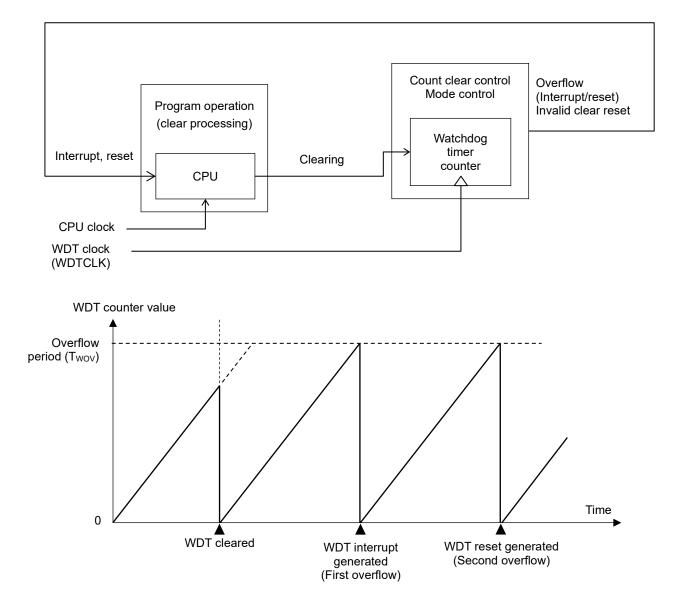

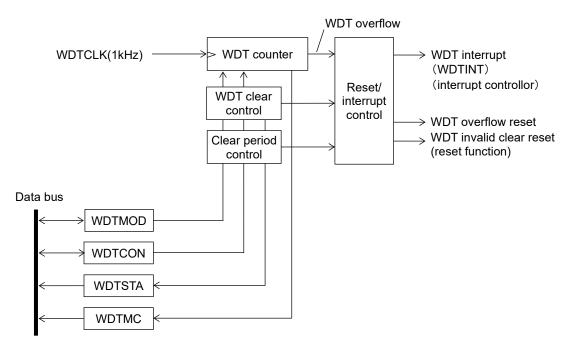

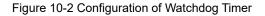

- Watchdog timer (WDT)

- Overflow period: 8selectable (7.8, 15.6, 31.3, 62.5, 125, 500, 2000, 8000[ms])

- Selectable WDT operation: select enable or disable by code option

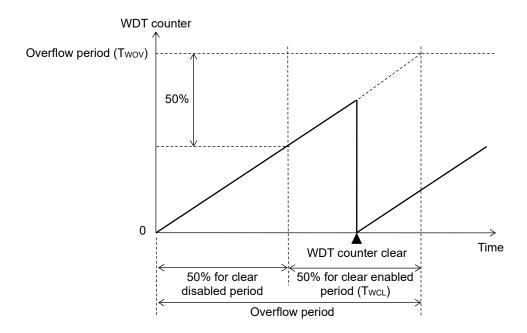

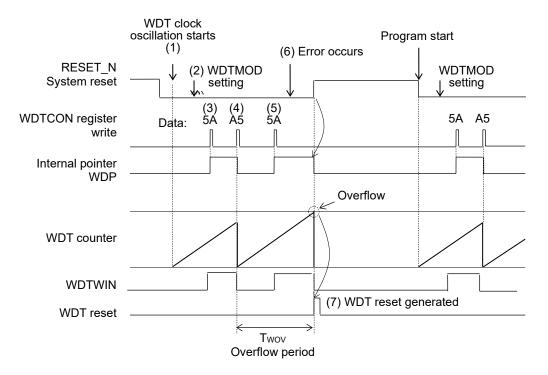

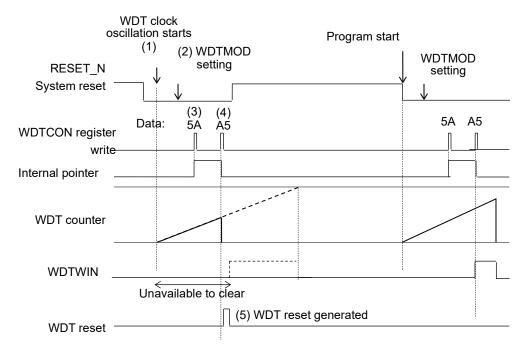

- Selectable window function (enable or disable): configurable clear enable period (50% or 75% of overflow period) with invalid clear. When disable, Interrupts the first overflow and resets the second overflow. When enable, reset occurs for the first overflow.

- Selectable operation in HALT/HALT-H mode and HALT-D mode(Continue counting/Stop counting)

- Readable WDT counter: WDT counter monitor function

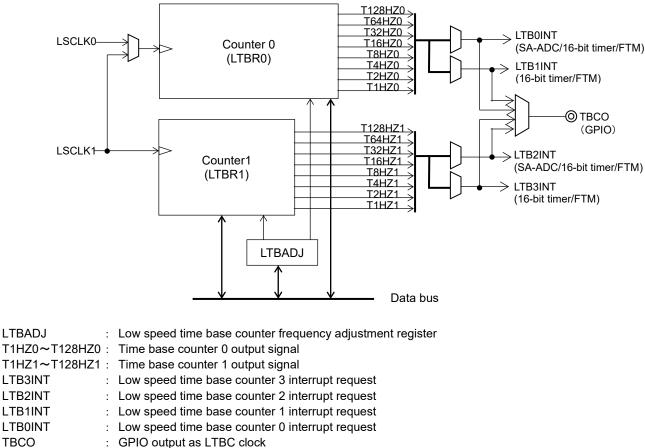

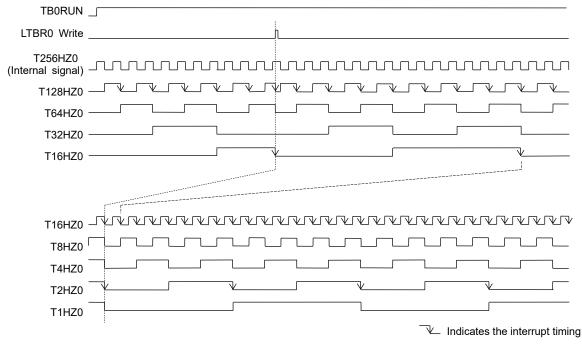

- Low-speed Time base counter(LTBC) : 2 channels

- Generate 8 frequency (128, 64, 32, 16, 8, 4, 2, 1[Hz]) internal pulse signals by dividing the Low-speed clock (LSCLK)

- 4 interrupts are generatable from 8 different frequencies internal pulse signals

- One of internal pulse signals selected to interrupt can be output from general purpose port (TBCO)

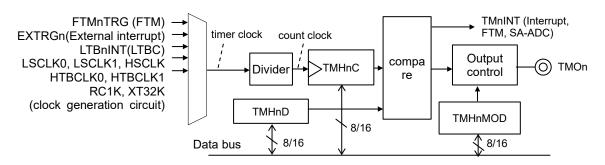

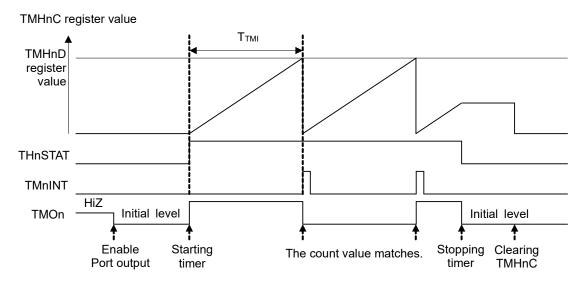

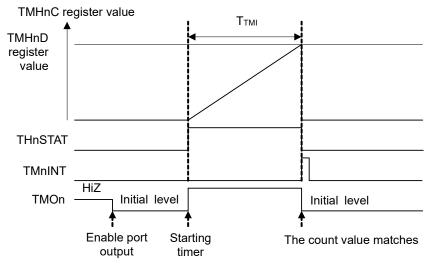

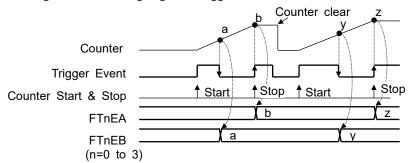

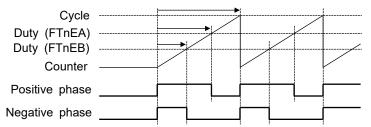

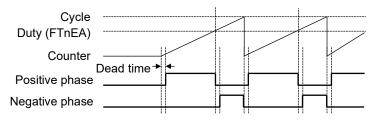

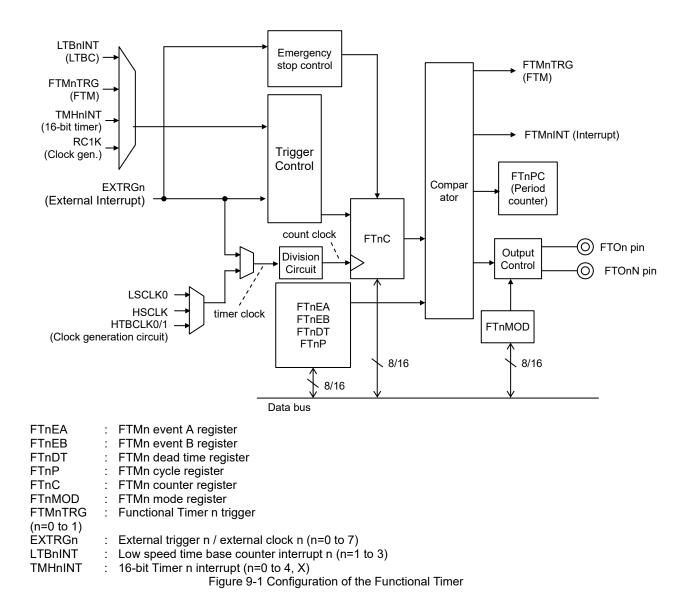

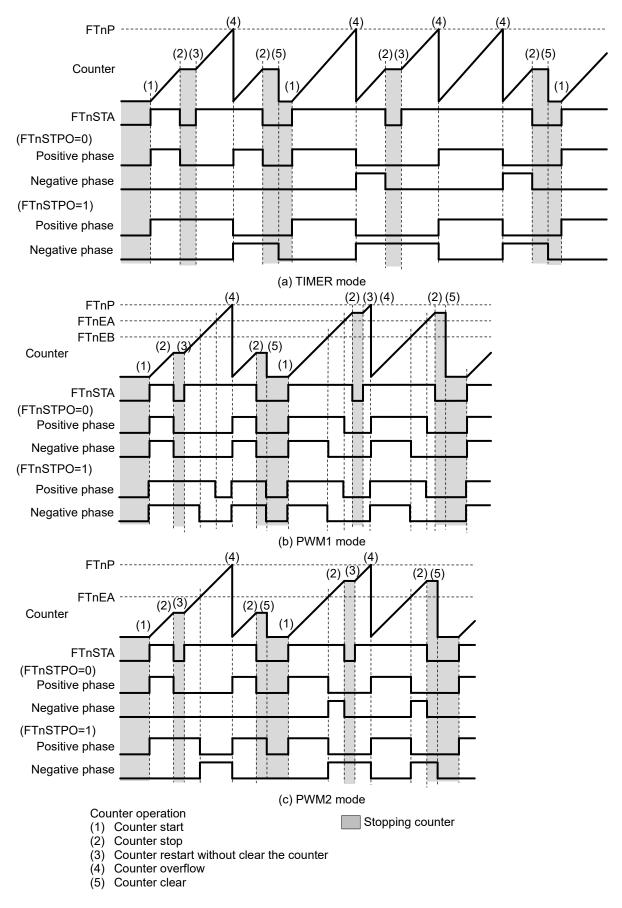

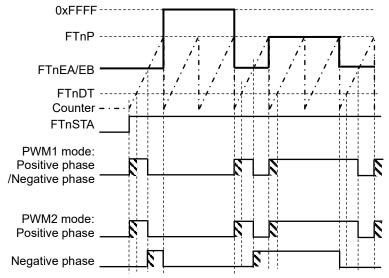

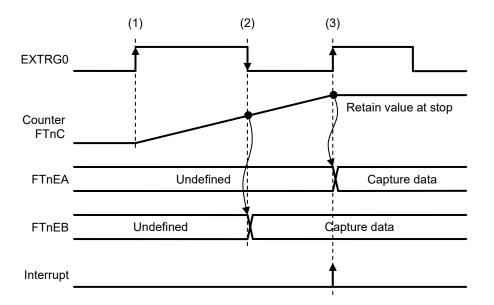

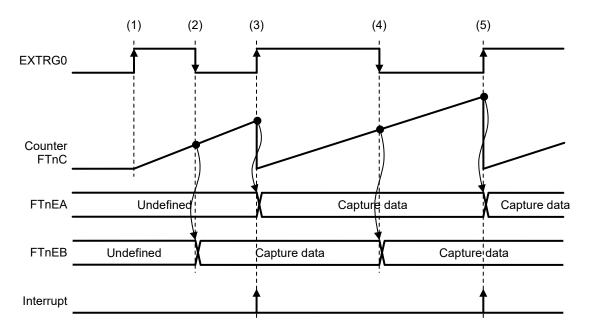

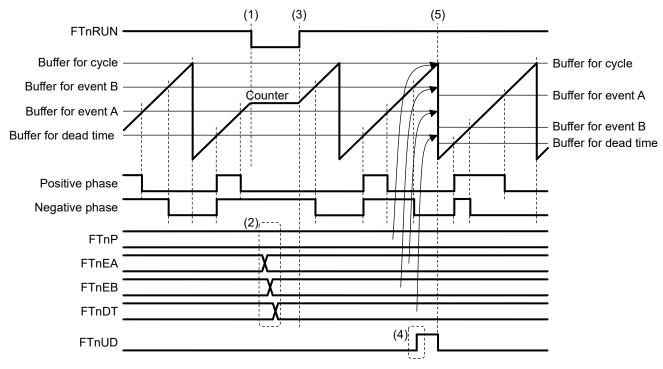

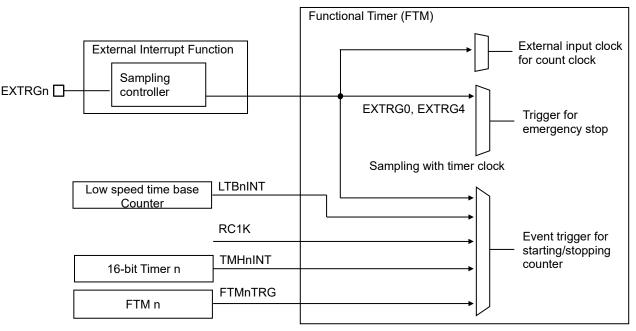

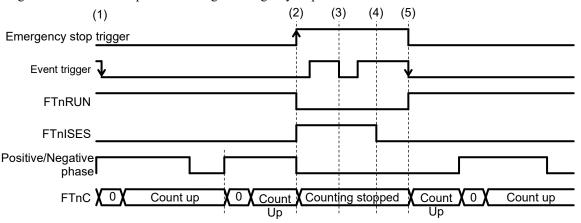

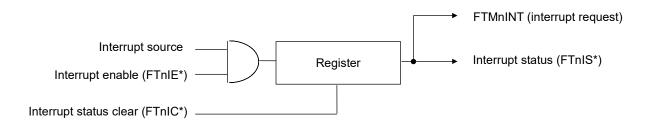

- Functional timer

#### : 2 channels

- Various modes (Continuous, One shot, capture, PWM with the same period and different duties, and complementary PWM output with the dead time)

- Event trigger (external pin, 16bit timer, functional timer, LTBC, RC1K)

- Selectable counter clock from various sources (divided by 1 to 8 of LSCLK, HSCLK, HTBCLK, external clock)

- 16-bit General timers

#### : 6 channels

Timer output (toggled by overflow)

Selectable counter clock from various sources (divided by 1 to 8 of LSCLK, HSCLK, HTBCLK, LTBC, RC1K, and external clock)

: 2 channels (with FIFO: 1 channel, without FIFO: 1 channel)

- Timer X is shared with waiting for the stability of low-speed crystal oscillation

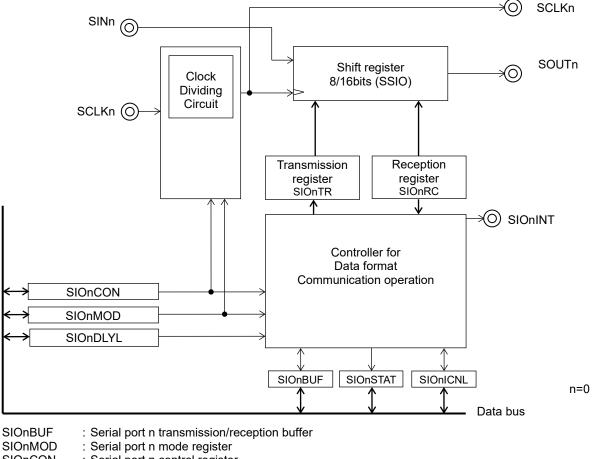

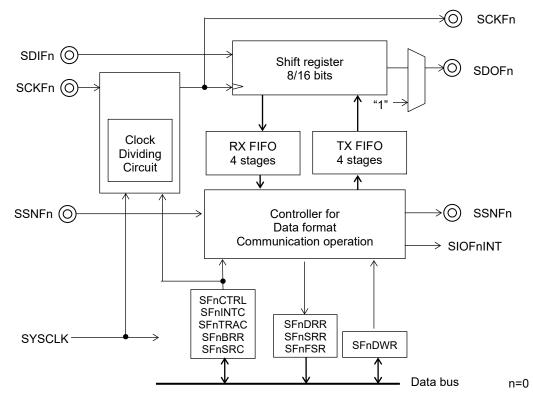

- Synchronous Serial Port

- FIFO: 4steps for each transmitting and receiving

- Selectable from Master and Slave

- Selectable from LSB first or MSB first

- Selectable 8-bit length or 16-bit length

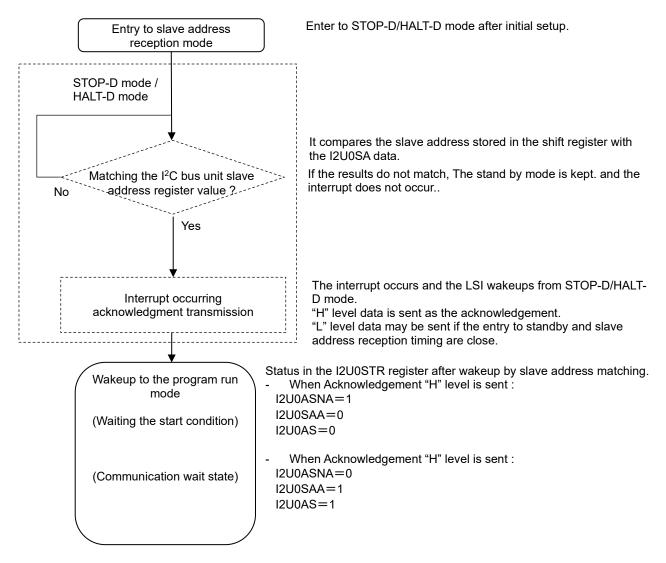

- UART (Full-duplex communication mode): 3 channels

- Selectable from 5 to 8bit length, parity or no parity, odd parity or even parity, 1 stop bit or 2 stop bits, Positive logic or Negative logic, LSB first or MSB first

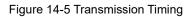

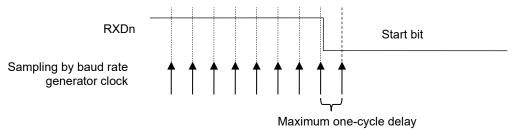

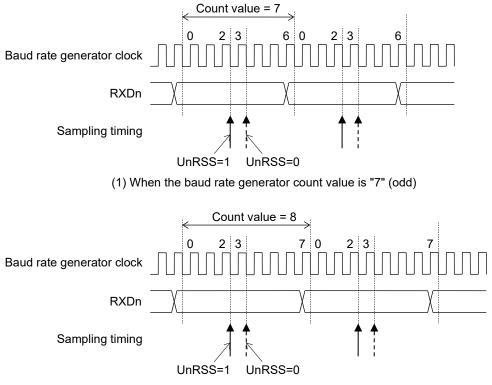

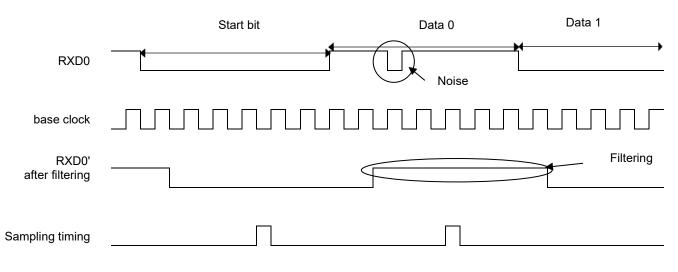

- Sampling filter for receiving data and start bit

- Built-in baud rate generator (HSCLK(16MHz): 300bps to 2Mbps, LSCLK: up to 4800bps)

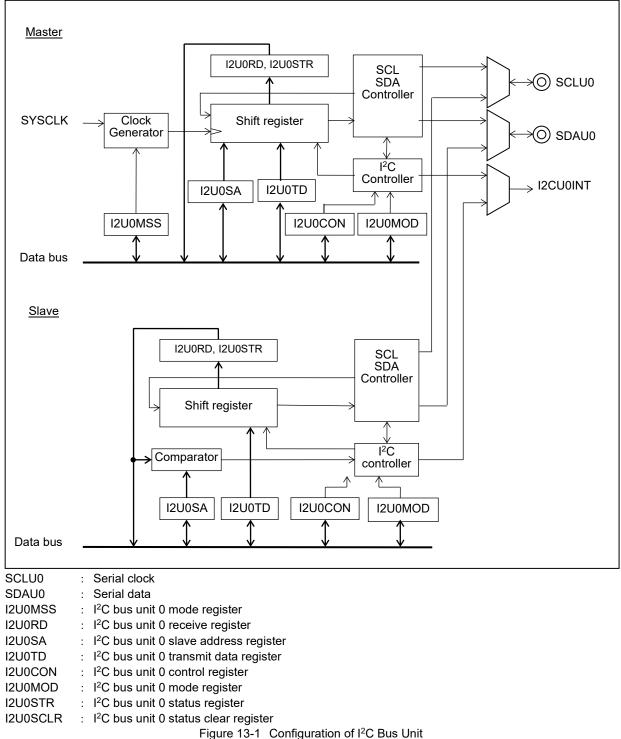

• I<sup>2</sup>C bus

#### : 2 channels

- Selectable from Master mode or Slave mode: 1channel. Master mode only: 1channel

- Standard mode (100 kbps), fast mode (400 kbps) and 1Mbps mode(1Mbps)

- 7bit address format

- Master mode: Handshake (Clock synchronization), 10bit slave address format is supported

- Slave mode: Clock stretch function

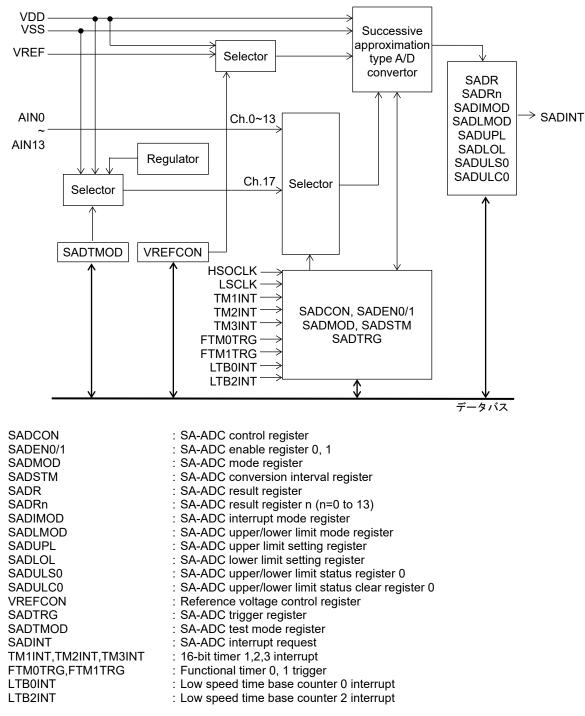

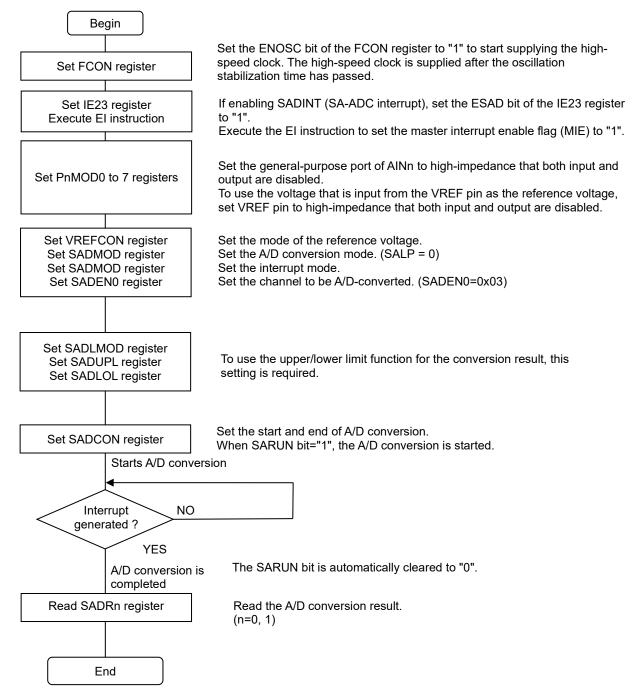

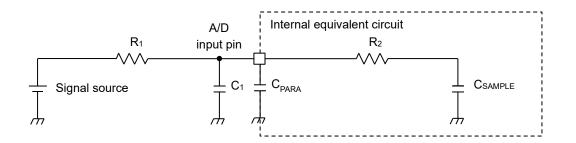

- Successive approximation type 12bit A/D converter (SA-ADC): input 14 channels

- Conversion time: Min. 1.375µs/ch (When the V<sub>DD</sub> is higher than 2.7V and the conversion clock is 16MHz)

- Reference voltages are selectable from VDD pin input voltage or External reference voltage (VREF pin)

- dedicated result register for each channel

- Continuous conversion, Trigger start, Interrupt determining by upper limit or lower limit threshold of conversion result

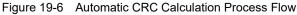

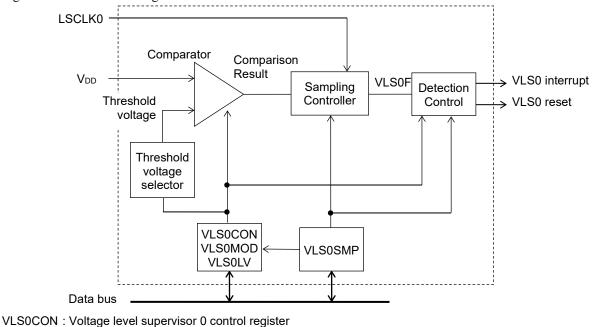

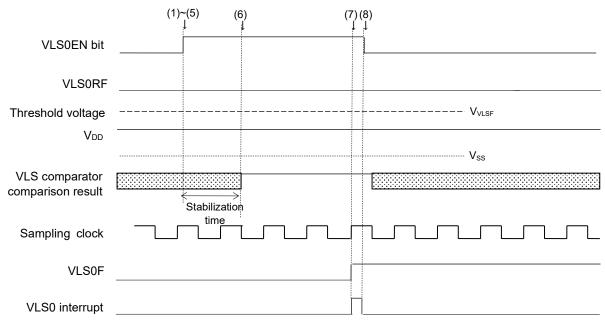

- Voltage Level Supervisor (VLS) : 1 channel

- Threshold voltage: selectable from 15 levels (1.85V to 4.00V)

- Functional Voltage level detection reset (VLS reset) or Functional Voltage level detection interrupt (VLS0 interrupt) is generable

- Equipped with single mode / with sampling filter / low consumption operation

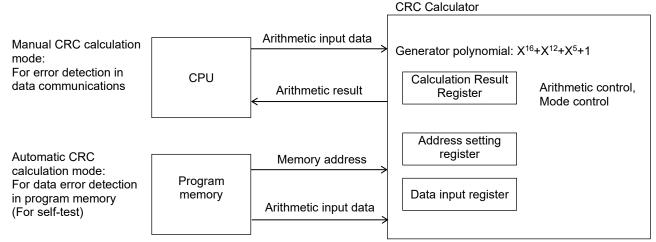

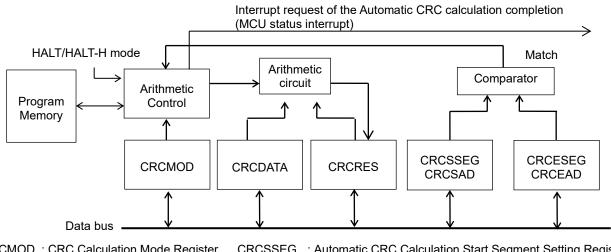

- CRC (Cyclic Redundancy Check) generator

- Generation equation:  $X^{16}+X^{12}+X^{5}+1$

- Selectable from LSB first or MSB first

- Built-in automatic program memory CRC calculation mode in HALT mode

- Safety Function

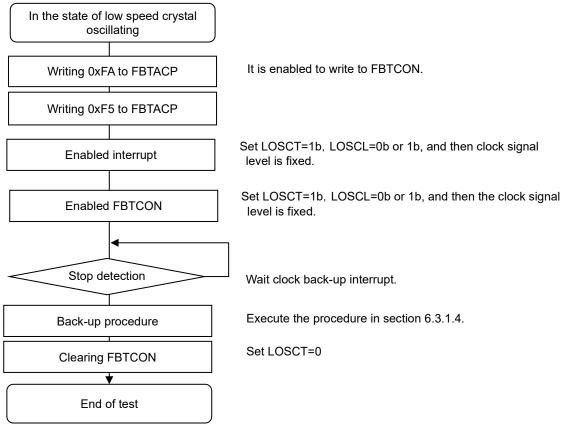

- Automatic switching to the internal low-speed RC oscillation in case the low-speed crystal oscillation stopped

- RAM/SFR guard

- Automatic program memory CRC calculation

- RAM parity error detection

- ROM unused area access reset (instruction access)

- Clock mutual monitoring, WDT counter monitoring

- SA-ADC test

- Communication loop back test (UART, Synchronous serial port, I<sup>2</sup>C bus(master))

- GPIO test

- Shipping package

| Deskers        | Body size                     | Pin pitch | Packing form and Product name |                      |  |  |  |  |

|----------------|-------------------------------|-----------|-------------------------------|----------------------|--|--|--|--|

| Package        | (including lead)<br>[mm × mm] | [mm]      | Tray                          | Tape & Reel          |  |  |  |  |

| 32 pin plastic | 7.0 × 7.0                     | 0.80      | ML62Q2502-xxxTBZWAX           | ML62Q2502-xxxTBZWBX  |  |  |  |  |

| TQFP           | (9.0 × 9.0)                   |           | ML62Q2504-xxxTBZWAX           | ML62Q2504-xxxTBZWBX  |  |  |  |  |

| 48 pin plastic | 7.0 × 7.0                     | 0.50      | ML62Q2532-xxxTBZWAX           | ML62Q2532-xxxTBZWBX  |  |  |  |  |

| TQFP           | (9.0 × 9.0)                   |           | ML62Q2534-xxxTBZWAX           | ML62Q2534-xxxTBZWBX  |  |  |  |  |

| 32 pin plastic | 5.0 × 5.0                     | 0.50      | ML62Q2502-xxxGDZW5AX          | ML62Q2502-xxxGDZW5BX |  |  |  |  |

| WQFN           | (-)                           |           | ML62Q2504-xxxGDZW5AX          | ML62Q2504-xxxGDZW5BX |  |  |  |  |

| 40 pin plastic | 6.0 × 6.0                     | 0.50      | ML62Q2522-xxxGDZW5AX          | ML62Q2522-xxxGDZW5BX |  |  |  |  |

| WQFN           | (-)                           |           | ML62Q2524-xxxGDZW5AX          | ML62Q2524-xxxGDZW5BX |  |  |  |  |

| 48 pin plastic | 7.0 × 7.0                     | 0.50      | ML62Q2532-xxxGDZW5AX          | ML62Q2532-xxxGDZW5BX |  |  |  |  |

| WQFN           | ( - )                         |           | ML62Q2534-xxxGDZW5AX          | ML62Q2534-xxxGDZW5BX |  |  |  |  |

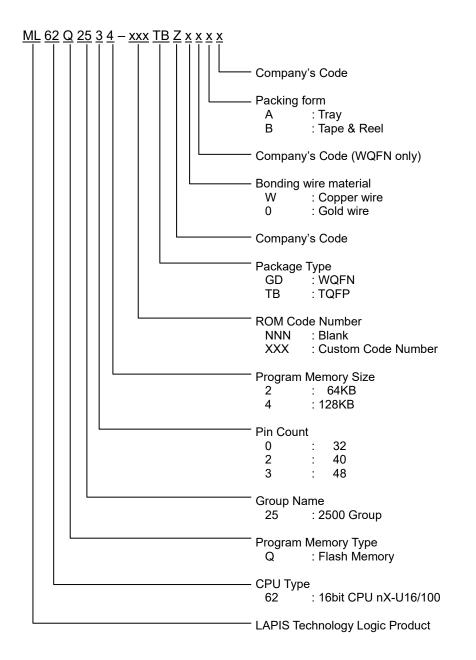

### 1.1.1 How To Read The Part Number

Figure 1-1 Part Number

### 1.1.2 Main Function List

|                        | Table     |           |                 |                  |                               |                                                      |                        |                           |                               | n Fur                              | nctio            | n Li                        | st                            |                     |                        |                                        |                                     |                       |                                                   |                                               |                                          |                               |

|------------------------|-----------|-----------|-----------------|------------------|-------------------------------|------------------------------------------------------|------------------------|---------------------------|-------------------------------|------------------------------------|------------------|-----------------------------|-------------------------------|---------------------|------------------------|----------------------------------------|-------------------------------------|-----------------------|---------------------------------------------------|-----------------------------------------------|------------------------------------------|-------------------------------|

|                        |           | Pin       |                 |                  |                               |                                                      | Interrupt Timer        |                           |                               |                                    |                  | Communication               |                               |                     |                        | Ana                                    | alog                                |                       |                                                   |                                               |                                          |                               |

| art number             | Total pin | Power pin | Reset Input pin | Debug Input port | General Purpose Input port *1 | General Puroise I/O port<br>(LED drive is supported) | External interrupt pin | External interrupt source | Non maskable interrupt source | Internal maskable interrupt source | 16bit Timer [ch] | 16bit Functional Timer [ch] | 16bit Functional Timer [Port] | Watchdog Timer [ch] | Time base counter [ch] | Synchronous serial (without FIFO) [ch] | Synchronous serial (with FIFO) [ch] | Full-duplex UART [ch] | I <sup>2</sup> C bus interface (Master only) [ch] | I <sup>2</sup> C bus unit (Master/Slave) [ch] | 12bit Successive type A/D converter [ch] | Voltage Level Supervisor [ch] |

| ML62Q2502<br>ML62Q2504 | 32        |           |                 |                  |                               | 24                                                   | 16                     |                           |                               |                                    |                  |                             |                               |                     |                        |                                        |                                     |                       |                                                   |                                               |                                          |                               |

| ML62Q2504              |           |           |                 |                  |                               |                                                      |                        |                           |                               |                                    |                  |                             |                               |                     |                        |                                        |                                     |                       |                                                   |                                               |                                          |                               |

| ML62Q2524              | 40        | 3         | 1               | 1                | 3                             | 32                                                   | 19                     | 8                         | 1                             | 26                                 | 6                | 2                           | 4                             | 1                   | 2                      | 1                                      | 1                                   | 3                     | 1                                                 | 1                                             | 14                                       | 1                             |

| ML62Q2532              | 48        |           |                 |                  |                               | 40                                                   | 24                     |                           |                               |                                    |                  |                             |                               |                     |                        |                                        |                                     |                       |                                                   |                                               |                                          |                               |

| ML62Q2534              |           |           |                 |                  |                               | _                                                    |                        |                           |                               | L                                  |                  |                             |                               |                     |                        |                                        |                                     |                       |                                                   |                                               |                                          |                               |

\*1: Shared with pins for crystal oscillation and debug input.

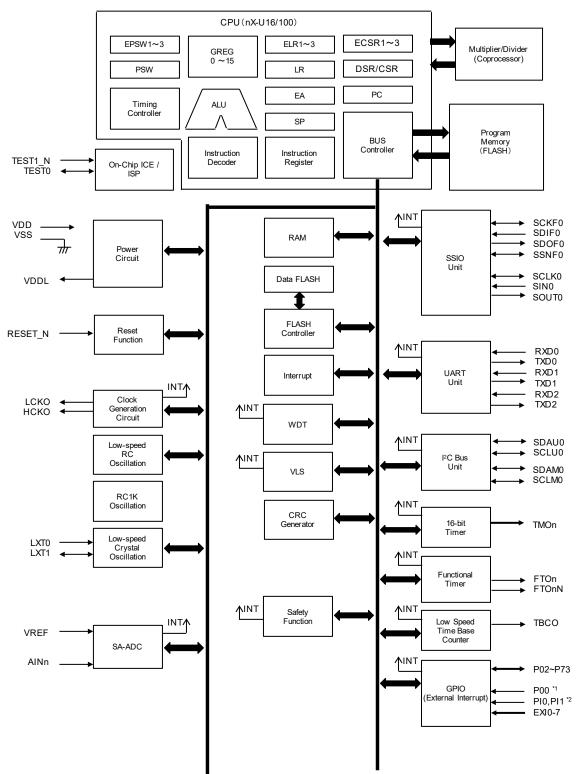

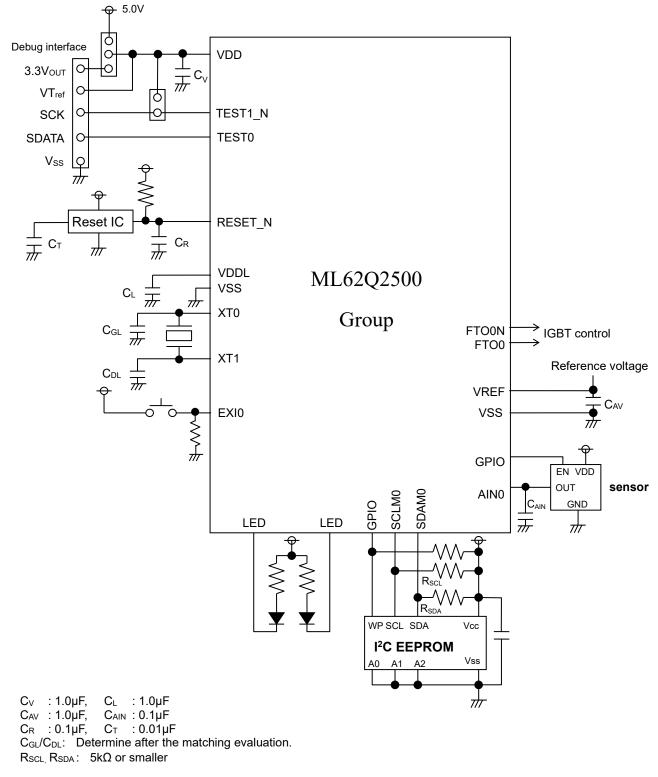

### 1.2 Block Diagram

\*1 : Not available as the input port when connecting to the on-chip debug emulator.

\*2 : Not available as the input port when connecting to the crystal resonator.

Figure 1-2 Block Diagram of ML62Q2500 group

1.3 Pin

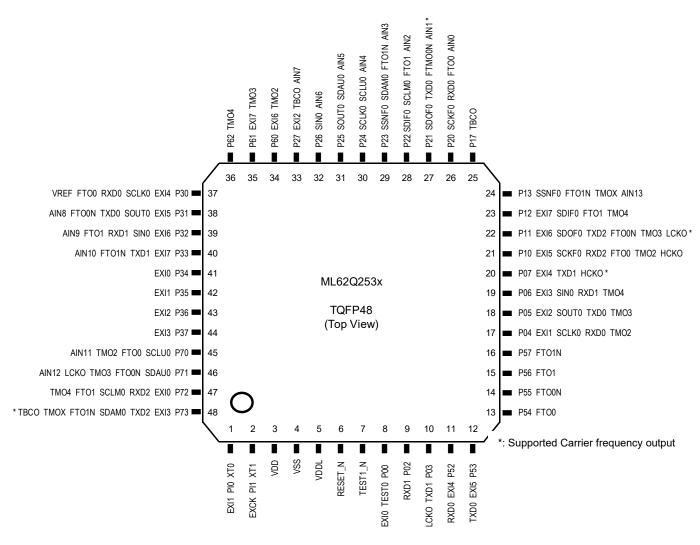

1.3.1 Pin Layout

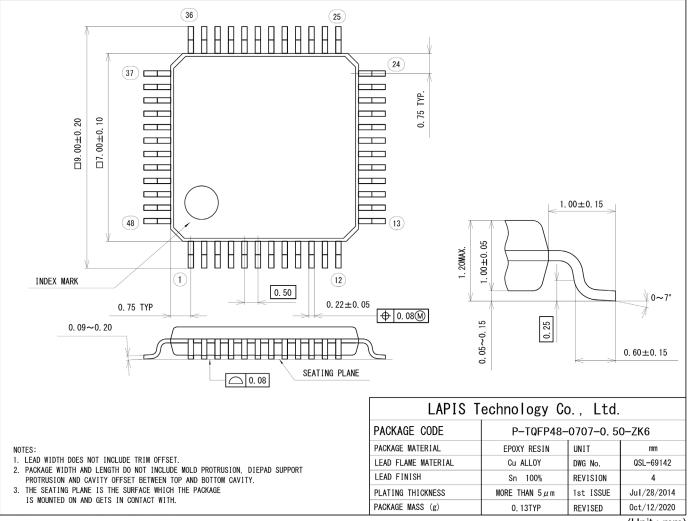

1.3.1.1 ML62Q2534/2532 : 48 pin TQFP

Figure 1-3-1 48 pin TQFP

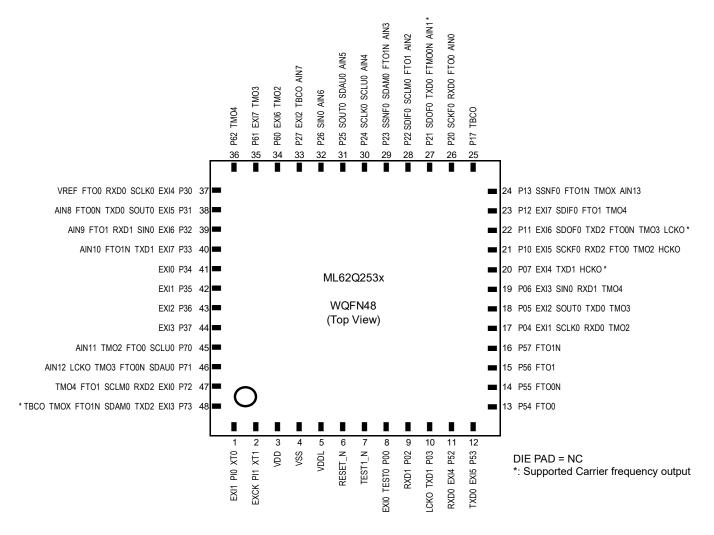

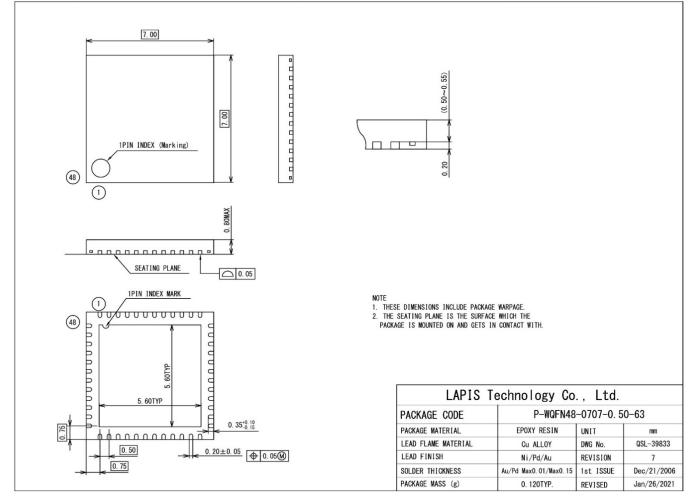

### 1.3.1.2 ML62Q2534/2532 : 48 pin WQFN

Figure 1-3-2 48 pin WQFN

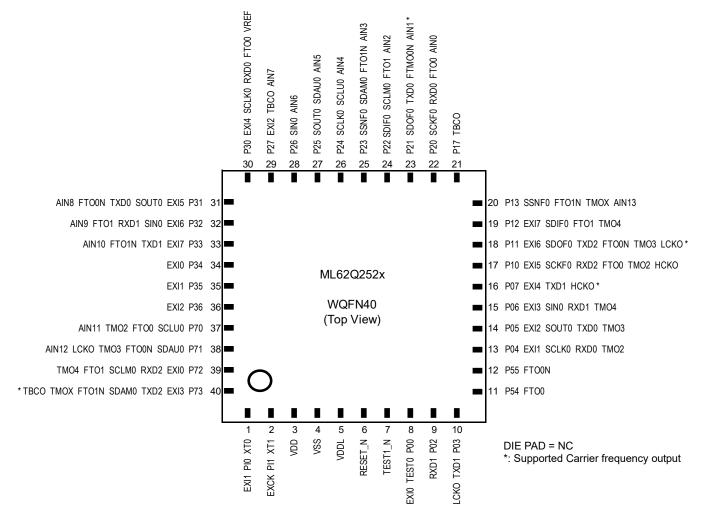

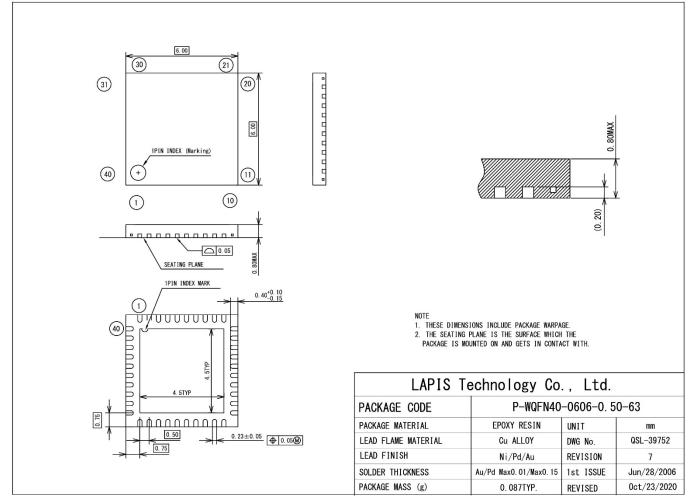

### 1.3.1.3 ML62Q2524/2522 : 40 pin WQFN

Figure 1-3-3 40 pin WQFN

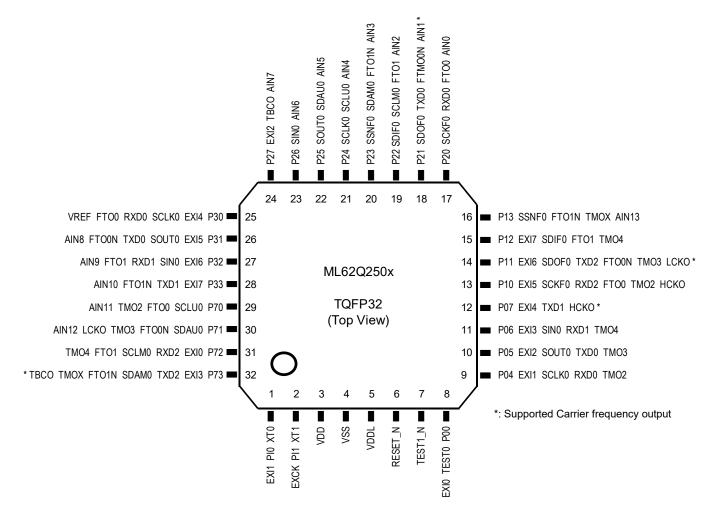

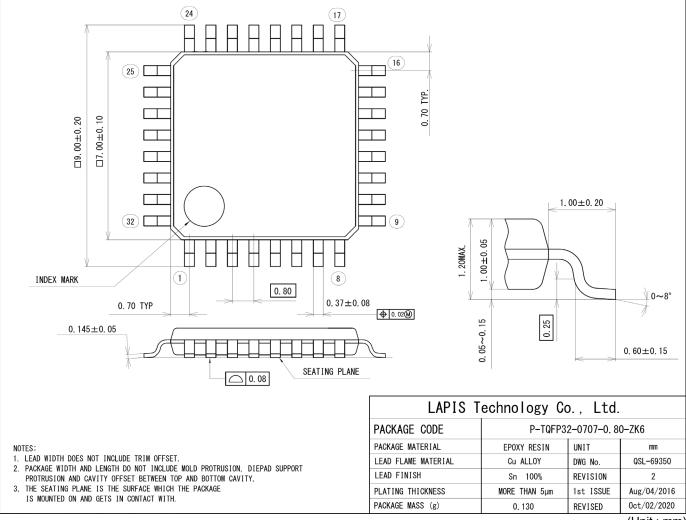

### 1.3.1.4 ML62Q2504/2502 : 32 pin TQFP

Figure 1-3-4 32 pin TQFP

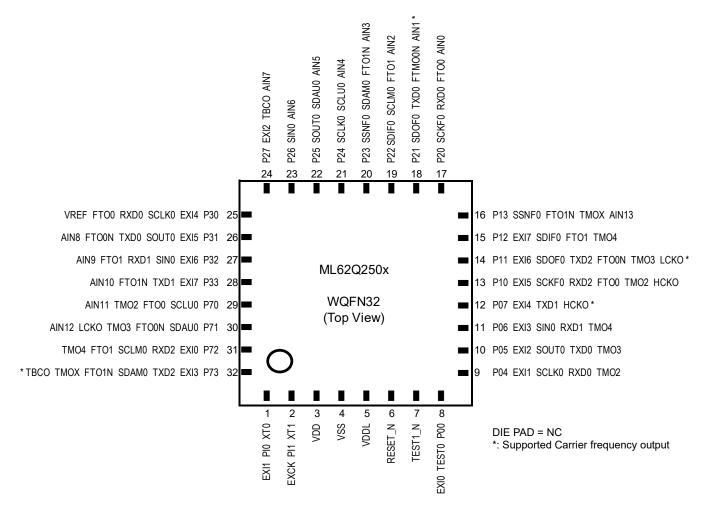

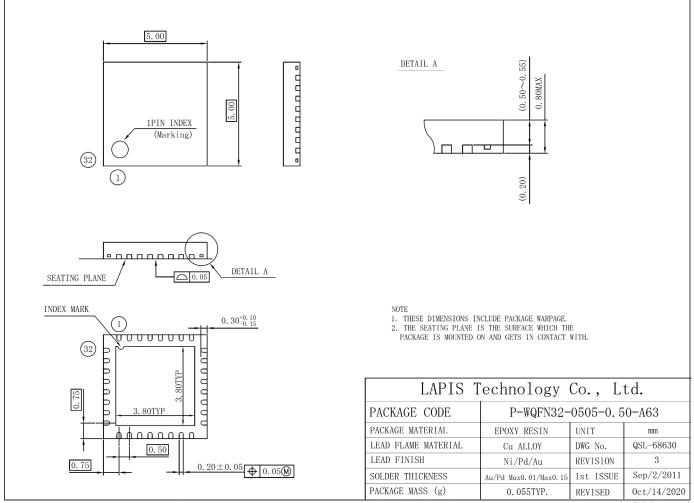

### 1.3.1.5 ML62Q2504/2502 : 32 pin WQFN

Figure 1-3-5 32 pin WQFN

### 1.3.2 Pin List

Table 1-3 shows the pin list of ML62Q2500 group.

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6 <sup>th</sup> 7 <sup>th</sup> nction         function           imer         CLKOUT<br>LTBC**           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           MO2         —           MO3         —           MO4         —           —         HCKO           MO3         LCKO           MO4         —           —         HCKO           MO3         LCKO |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | imer         CLKOUT<br>LTBC**                                                                           MO2            MO4             HCKO           MO2         HCKO           MO3         LCKO           MO4                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Imer         LTBC**           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           MO2         —           MO3         —           MO4         —           —         HCKO           MO3         LCKO           MO3         LCKO                                                                                                                              |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Imer         LTBC**           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           MO2         —           MO3         —           MO4         —           —         HCKO           MO3         LCKO           MO3         LCKO                                                                                                                              |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Imer         LTBC**           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           MO2         —           MO3         —           MO4         —           —         HCKO           MO3         LCKO           MO3         LCKO                                                                                                                              |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MO2            MO3            MO4             HCKO           MO3         LCKO           MO3         LCKO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           MO2         —           MO3         —           MO4         —           —         HCKO           MO2         HCKO           MO3         LCKO           MO3         LCKO                                                                                                                                                                                                                                                                     |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           MO2         —           MO3         —           MO4         —           —         HCKO           MO2         HCKO           MO3         LCKO           MO3         LCKO                                                                                                                                                                                                                                                                     |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           —         —           MO2         —           MO3         —           MO4         —           —         HCKO           MO2         HCKO           MO3         LCKO           MO3         LCKO                                                                                                                                                                                                                                                                     |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —         —           —         —           —         —           —         —           —         —           —         LCKO           MO2         —           MO3         —           MO4         —           —         HCKO           MO2         HCKO           MO3         LCKO           MO3         LCKO                                                                                                                                                                                                                                                                                                                                                          |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —         —           —         —           —         —           —         —           —         —           —         LCKO           MO2         —           MO3         —           MO4         —           —         HCKO           MO2         HCKO           MO3         LCKO           MO3         LCKO                                                                                                                                                                                                                                                                                                                                                          |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | LCKO           MO2            MO3            MO4            -         HCKO           MO2         HCKO           MO3         LCKO           MO4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6       6       6       RESET_N       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -<                                                                                                                                                                   | LCKO           MO2            MO3            MO4            -         HCKO           MO2         HCKO           MO3         LCKO           MO4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7       7       7       TEST1 N       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -<                                                                                                                                                                   | LCKO           MO2            MO3            MO4            -         HCKO           MO2         HCKO           MO3         LCKO           MO4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | LCKO           MO2            MO3            MO4            -         HCKO           MO2         HCKO           MO3         LCKO           MO4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | LCKO           MO2            MO3            MO4            -         HCKO           MO2         HCKO           MO3         LCKO           MO4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | LCKO           MO2            MO3            MO4            -         HCKO           MO2         HCKO           MO3         LCKO           MO4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | MO2         —           MO3         —           MO4         —           —         HCKO           MO2         HCKO           MO3         LCKO           MO4         —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | MO3         —           MO4         —           —         HCKO           MO2         HCKO           MO3         LCKO           MO4         —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | MO4         —           —         HCKO           MO2         HCKO           MO3         LCKO           MO4         —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12       16       20       P07       •       EXI4       -       -       TXD1       -       -       -         13       17       21       P10       -       EXI5       -       SCKF0-0       RXD2       -       FT00       TN         14       18       22       P11       •       EXI6       -       SDOF0-0       TXD2       -       FT00N       TN         15       19       23       P12       -       EXI7       -       SDIF0-0       -       -       FT01       TN         16       20       24       P13       -       -       AIN13       SSNF0-0       -       -       FT01N       TN         -       21       25       P17       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <td>—HCKOMO2HCKOMO3LCKOMO4—</td>                                                                                                                       | —HCKOMO2HCKOMO3LCKOMO4—                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | MO2 HCKO<br>MO3 LCKO<br>MO4 —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MO3 LCKO<br>MO4 —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

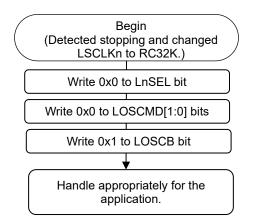

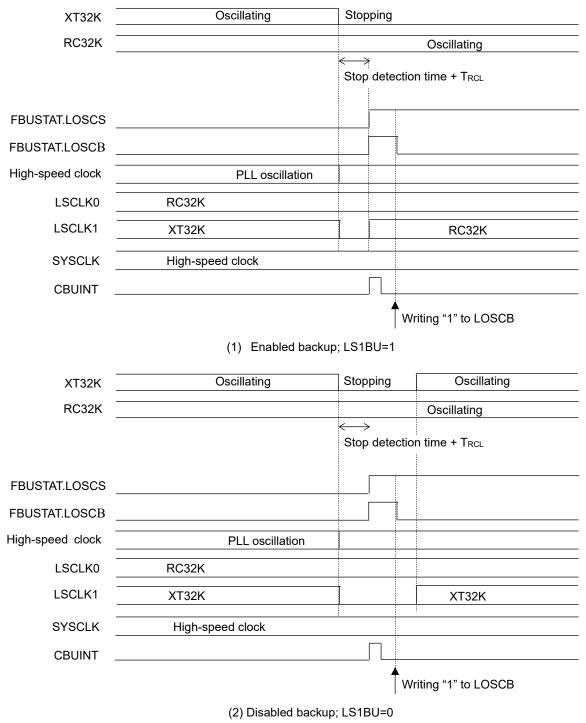

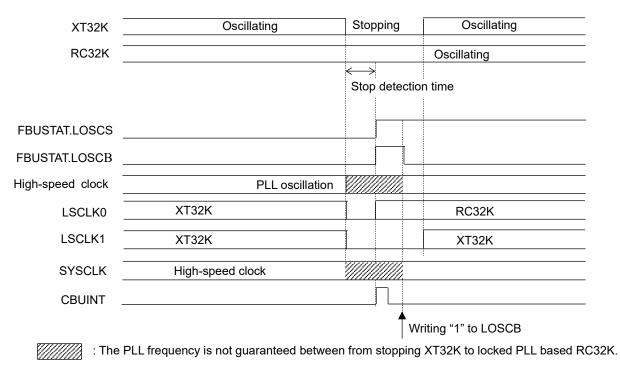

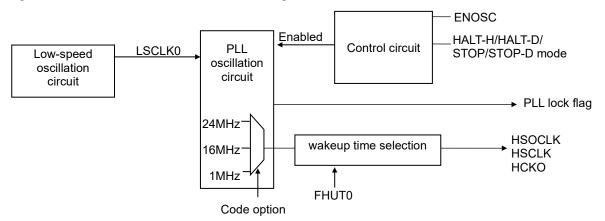

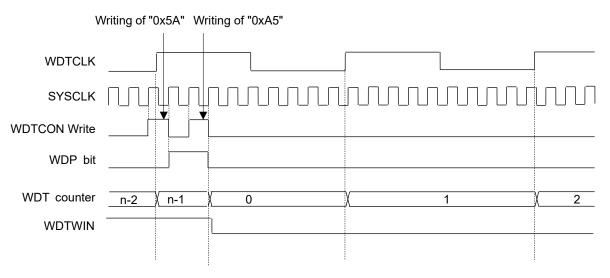

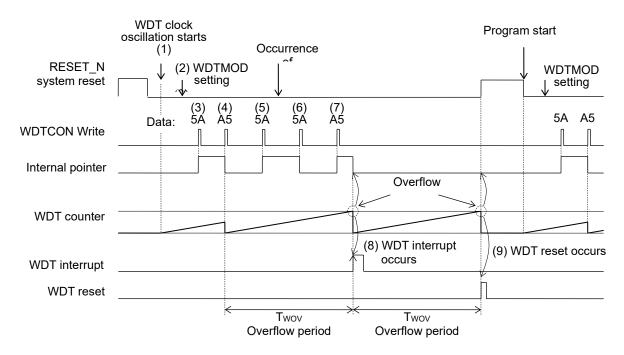

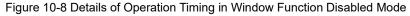

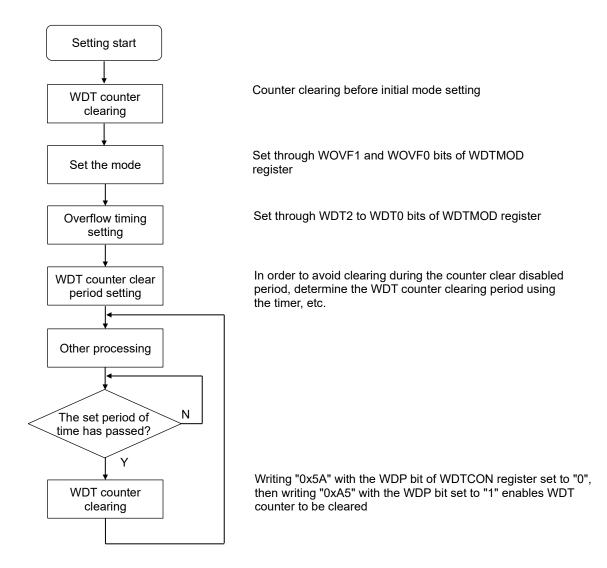

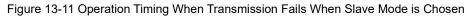

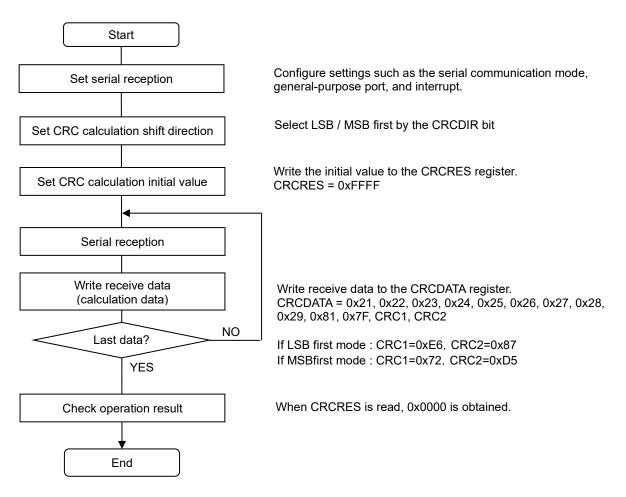

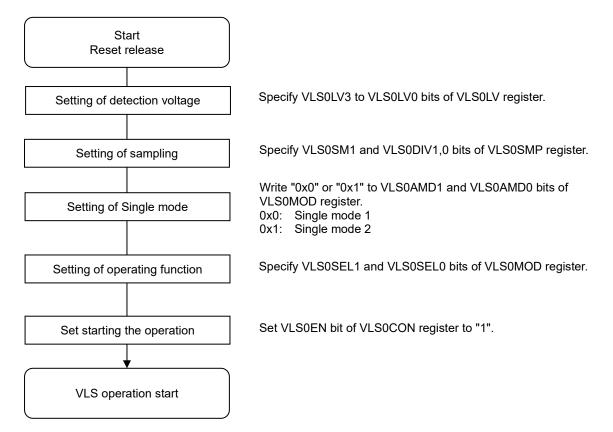

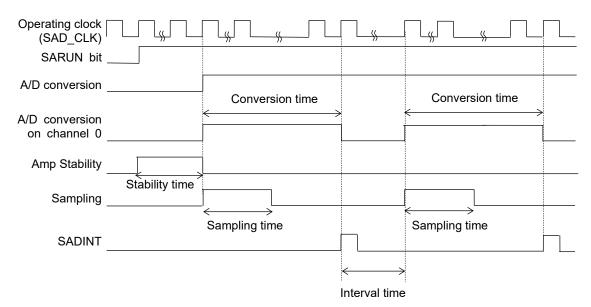

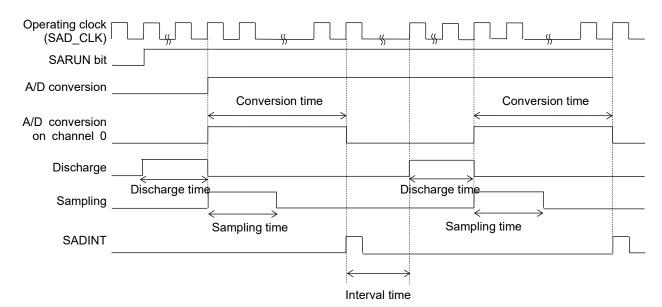

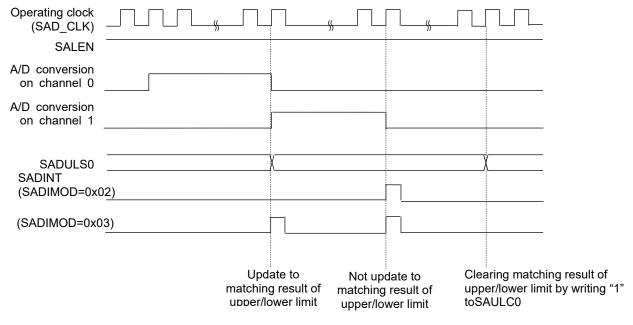

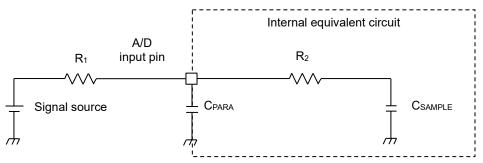

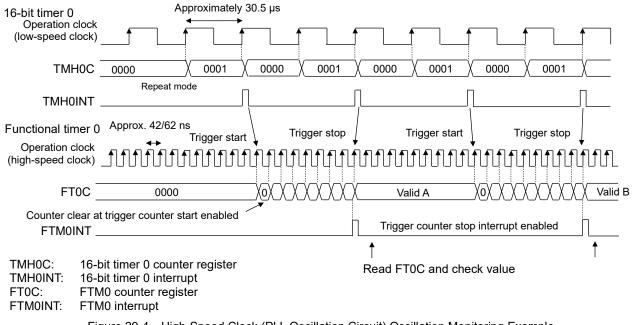

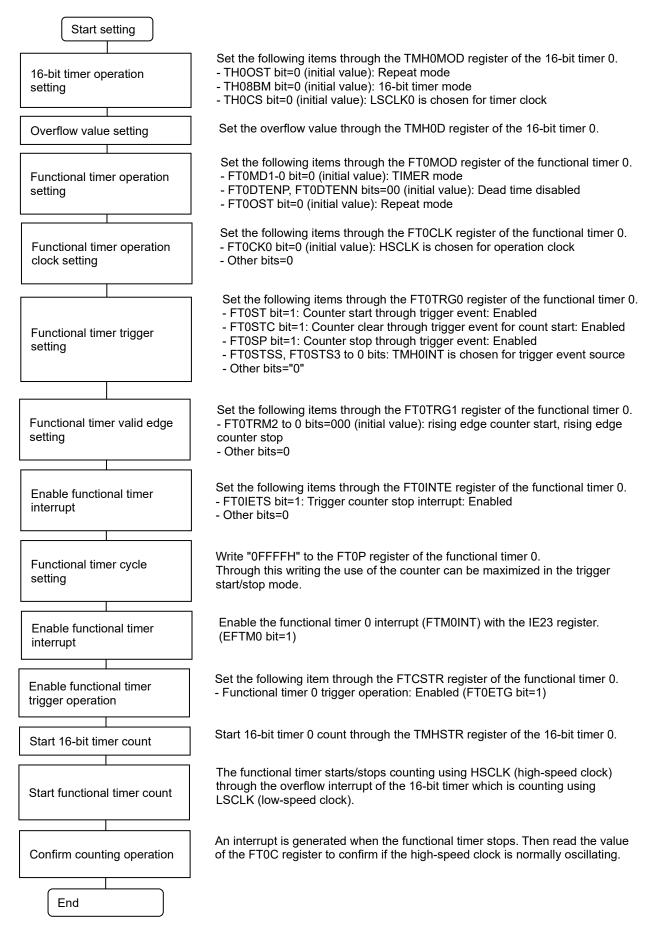

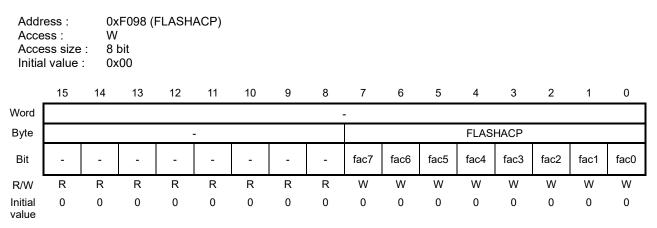

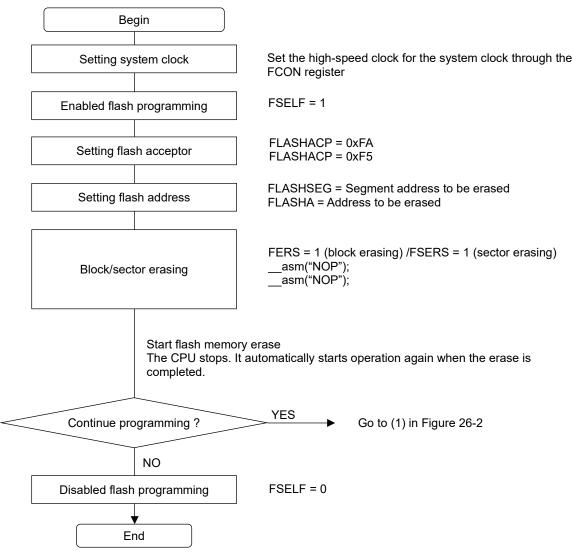

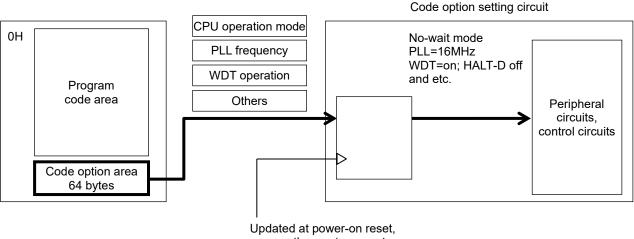

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MO4 —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |