# Dear customer

ROHM Co., Ltd. ("ROHM"), on the 1st day of April, 2024, has absorbed into merger with 100%-owned subsidiary of LAPIS Technology Co., Ltd.

Therefore, all references to "LAPIS Technology Co., Ltd.", "LAPIS Technology" and/or "LAPIS" in this document shall be replaced with "ROHM Co., Ltd." Furthermore, there are no changes to the documents relating to our products other than the company name, the company trademark, logo, etc.

Thank you for your understanding.

ROHM Co., Ltd. April 1, 2024

# ML62Q2700 Group User's Manual

Issue Date: Mar. 26, 2024

#### Notes

- 1) When using LAPIS Technology Products, refer to the latest product information and ensure that usage conditions (absolute maximum ratings\*1, recommended operating conditions, etc.) are within the ranges specified. LAPIS Technology disclaims any and all liability for any malfunctions, failure or accident arising out of or in connection with the use of LAPIS Technology Products outside of such usage conditions specified ranges, or without observing precautions. Even if it is used within such usage conditions specified ranges, semiconductors can break down and malfunction due to various factors. Therefore, in order to prevent personal injury, fire or the other damage from break down or malfunction of LAPIS Technology Products, please take safety at your own risk measures such as complying with the derating characteristics, implementing redundant and fire prevention designs, and utilizing backups and fail-safe procedures.

- \*1: Absolute maximum ratings: a limit value that must not be exceeded even momentarily.

- 2) The Products specified in this document are not designed to be radiation tolerant.

- 3) Descriptions of circuits, software and other related information in this document are provided only to illustrate the standard operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. And the peripheral conditions must be taken into account when designing circuits for mass production. LAPIS Technology disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, and other related information.

- 4) No license, expressly or implied, is granted hereby under any intellectual property rights or other rights of LAPIS Technology or any third party with respect to LAPIS Technology Products or the information contained in this document (including but not limited to, the Product data, drawings, charts, programs, algorithms, and application examples, etc.). Therefore, LAPIS Technology shall have no responsibility whatsoever for any dispute, concerning such rights owned by third parties, arising out of the use of such technical information.

- 5) LAPIS Technology intends our Products to be used in a way indicated in this document. Please be sure to contact a ROHM sales office if you consider the use of our Products in different way from original use indicated in this document. For use of our Products in medical systems, please be sure to contact a LAPIS Technology representative and must obtain written agreement. Do not use our Products in applications which may directly cause injuries to human life, and which require extremely high reliability, such as aerospace equipment, nuclear power control systems, and submarine repeaters, etc. LAPIS Technology disclaims any and all liability for any losses and damages incurred by you or third parties arising by using the Product for purposes not intended by us without our prior written consent.

- 6) All information contained in this document is subject to change for the purpose of improvement, etc. without any prior notice. Before purchasing or using LAPIS Technology Products, please confirm the latest information with a ROHM sales office. LAPIS Technology has used reasonable care to ensure the accuracy of the information contained in this document, however, LAPIS Technology shall have no responsibility for any damages, expenses or losses arising from inaccuracy or errors of such information.

- 7) Please use the Products in accordance with any applicable environmental laws and regulations, such as the RoHS Directive. LAPIS Technology shall have no responsibility for any damages or losses resulting non-compliance with any applicable laws or regulations.

- 8) When providing our Products and technologies contained in this document to other countries, you must abide by the procedures and provisions stipulated in all applicable export laws and regulations, including without limitation the US Export Administration Regulations and the Foreign Exchange and Foreign Trade Act.

- 9) Please contact a ROHM sales office if you have any questions regarding the information contained in this document or LAPIS Technology's Products.

- 10) This document, in part or in whole, may not be reprinted or reproduced without prior consent of LAPIS Technology.

(Note) "LAPIS Technology" as used in this document means LAPIS Technology Co., Ltd.

Copyright 2023 – 2024 LAPIS Technology Co., Ltd.

# LAPIS Technology Co., Ltd.

2-4-8 Shinyokohama, Kouhoku-ku, Yokohama 222-8575, Japan https://www.lapis-tech.com/en/

LTSZ08023 • 01 • 002

# Notes for product usage

Notes on this page are applicable to the all LAPIS Technology microcontroller products. For individual notes on each LAPIS Technology microcontroller product, refer to [Note] in the chapters of each user's manual.

The individual notes of each user's manual take priority over those contents in this page if they are different.

#### 1. HANDLING OF UNUSED INPUT PINS

Fix the unused input pins to the power pin or GND to prevent to cause the device performing wrong operation or increasing the current consumption due to noise, etc. If the handlings for the unused pins are described in the chapters, follow the instruction.

## 2. STATE AT POWER ON

At the power on, the data in the internal registers and output of the ports are undefined until the power supply voltage reaches to the recommended operating condition and "L" level is input to the reset pin.

On LAPIS Technology microcontroller products that have the power on reset function, the data in the internal registers and output of the ports are undefined until the power on reset is generated.

Be careful to design the application system does not work incorrectly due to the undefined data of internal registers and output of the ports.

## 3. ACCESS TO UNUSED MEMORY

If reading from unused address area or writing to unused address area of the memory, the operations are not guaranteed.

## 4. CHARACTERISTICS DIFFERENCE BETWEEN THE PRODUCT

Electrical characteristics, noise tolerance, noise radiation amount, and the other characteristics are different from each microcontroller product.

When replacing from other product to LAPIS Technology microcontroller products, please evaluate enough the apparatus/system which implemented LAPIS Technology microcontroller products.

## 5. USE ENVIRONMENT

When using LAPIS Technology microcontroller products in a high humidity environment and an environment where dew condensation, take moisture-proof measures.

# Preface

This manual describes the operation of the hardware of the 16-bit microcontroller ML62Q2700 Group.

See the relevant manuals listed in supplementary volume; "MCU Relevant Documents list" as necessary.

# **Notation**

| Classification | Notation               | Description                                                                                                                        |

|----------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Numeric value  | XXh, XXH, 0xXX         | Indicates a hexadecimal number.                                                                                                    |

| Unit           | word, W                | 1 word = 16 bits                                                                                                                   |

|                | byte, B                | 1 byte = 8 bits                                                                                                                    |

|                | nibble, N              | 1 nibble = 4 bits                                                                                                                  |

|                | mega-, M               | 10 <sup>6</sup>                                                                                                                    |

|                | kilo-, K               | 2 <sup>10</sup> = 1024                                                                                                             |

|                | kilo-, k               | 10 <sup>3</sup> = 1000                                                                                                             |

|                | milli-, m              | 10-3                                                                                                                               |

|                | micro-, µ              | 10 <sup>-6</sup>                                                                                                                   |

|                | nano-, n               | 10 <sup>-9</sup>                                                                                                                   |

|                | second, s (lower case) | second                                                                                                                             |

| Terminology    | "H" level              | Indicates high level voltage V <sub>IH</sub> and V <sub>OH</sub> as specified by the electrical characteristics in the data-sheet. |

|                | "L" level              | Indicates low level voltage $V_{\text{IL}}$ and $V_{\text{OL}}$ as specified by the electrical characteristics in the data-sheet.  |

|                | SFR                    | Special function register. It is control register for system or peripherals.                                                       |

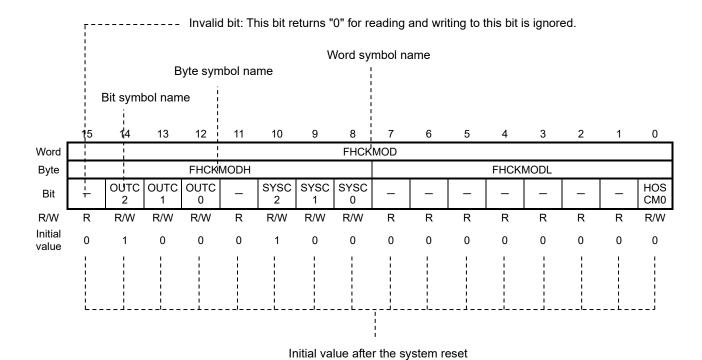

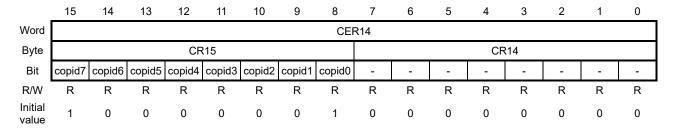

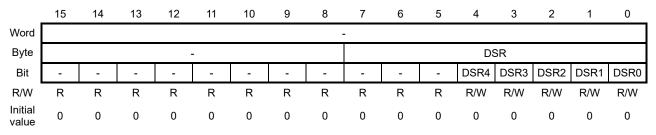

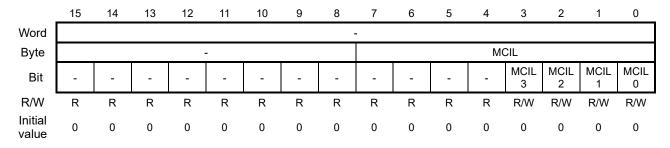

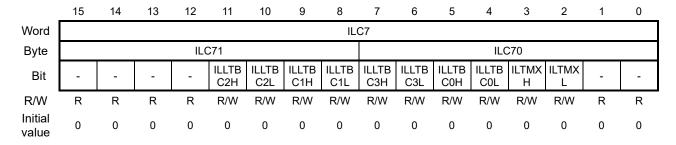

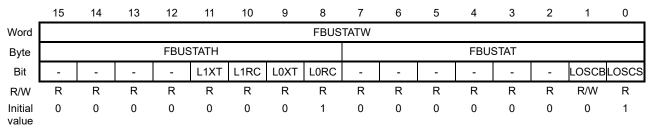

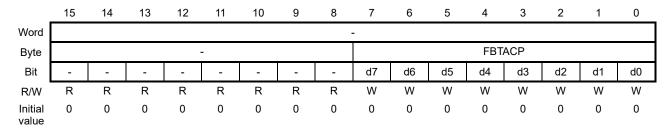

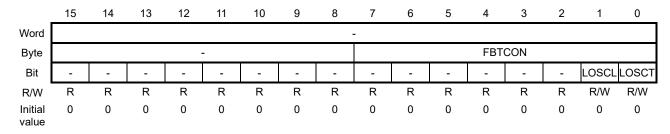

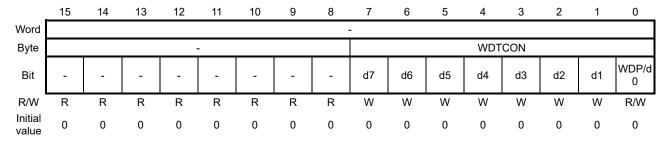

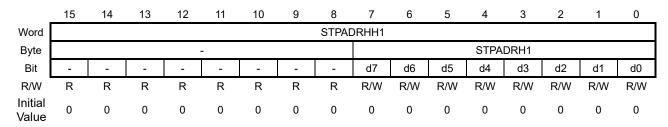

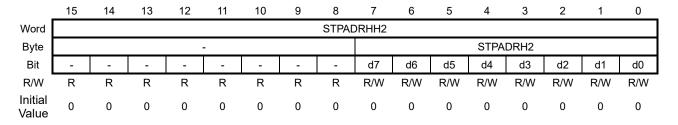

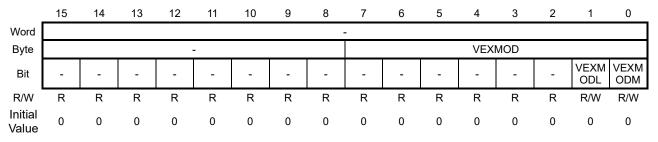

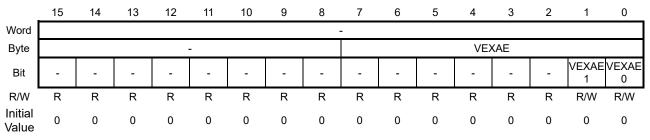

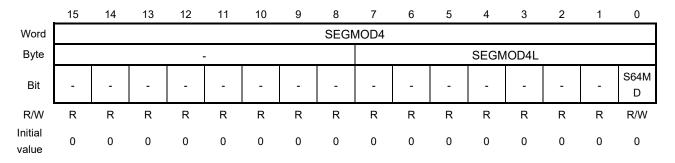

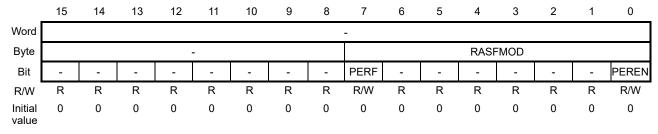

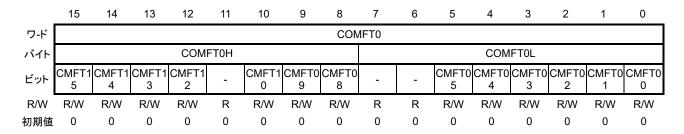

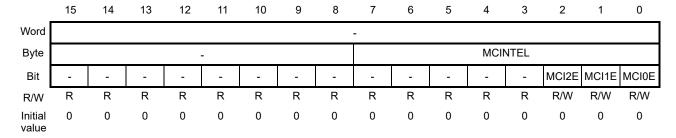

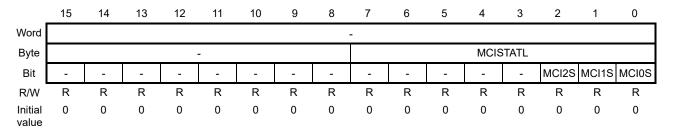

## • Register description

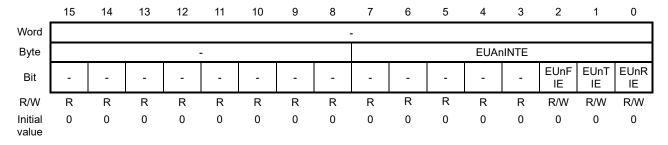

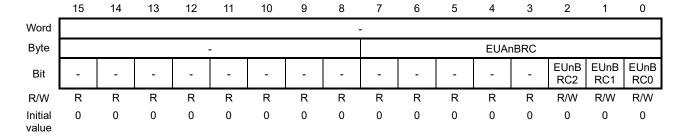

"R/W" indicates that Read/Write attribute. "R" indicates that data can be read and "W" indicates that data can be written. "R/W" indicates that data can be read or written.

MSB: The highest bit of 16-bit register LSB: The lowest bit of 16-bit register

Registers that have a word symbol allow the word-access. If writing or reading the registers not using the word symbol, specify the even number addresses.

· Please see the "Notes" and the "Notes for product usage" in this document.

## 1. Overview

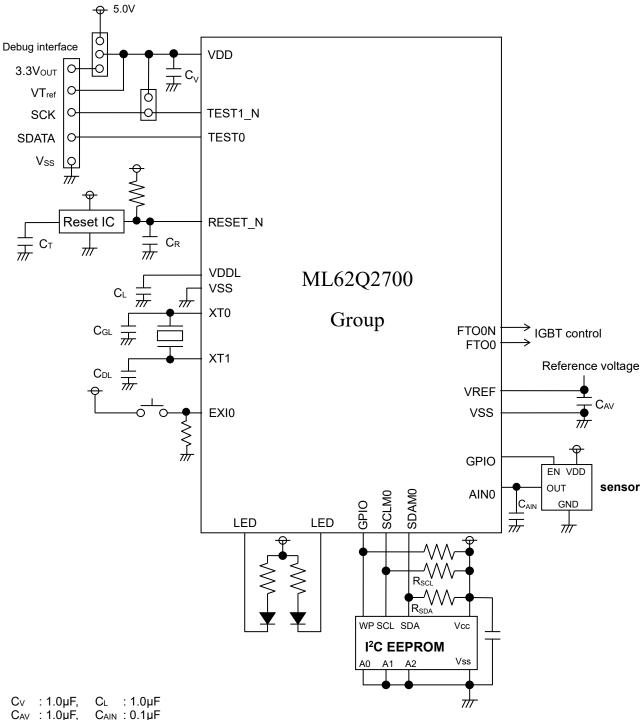

ML62Q2700 Group is a high performance CMOS 16-bit microcontroller equipped with an 16-bit CPU nX-U16/100 and integrated with program memory(Flash memory), data memory(RAM), data Flash (Erase unit:128byte, Write unit:1byte) and rich peripheral functions such as the multiplier/divider, CRC generator, Clock generator, Timer, General Purpose Ports, UART, Synchronous serial port, I<sup>2</sup>C bus interface unit(Master, Slave), Voltage Level Supervisor(VLS), Successive approximation type 12bit A/D converter, Audio playback function, LCD driver, Safety function (IEC60730/60335 Class B) and so on.

The CPU nX-U16/100 is capable of efficient instruction execution in 1-instruction 1-clock mode by pipeline architecture parallel processing.

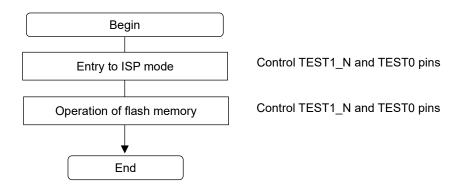

The built-in on-chip debug function enables debugging and programming the software. Also, ISP (In-System Programming) function supports the Flash programming in production line.

## Applications

Consumer and Industrial equipment (e.g., Household appliances, Housing equipment, Office equipment, Measurement instrumentation, etc)

## [NOTE]

This product cannot be applicable for automotive use, automatic train control systems, and railway safety systems. Please contact ROHM sales office in advance if contemplating the integration of this product into applications that requires high reliability, such as transportation equipment for ships and railways, communication equipment for trunk lines, traffic signal equipment, power transmission systems, core systems for financial terminals and various safety control devices.

#### Product List

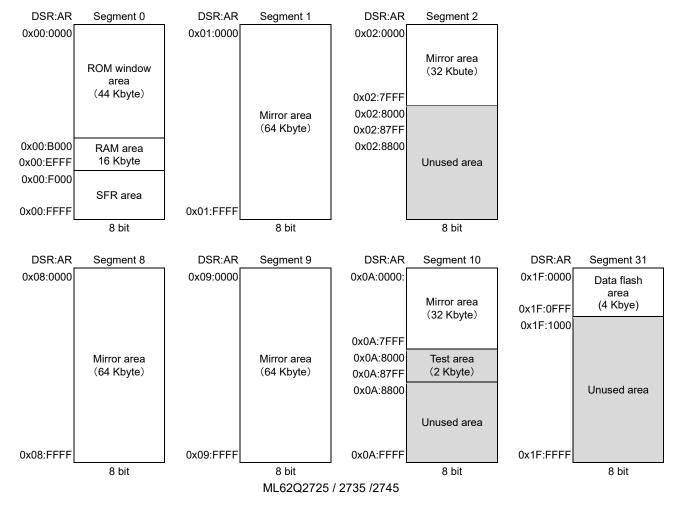

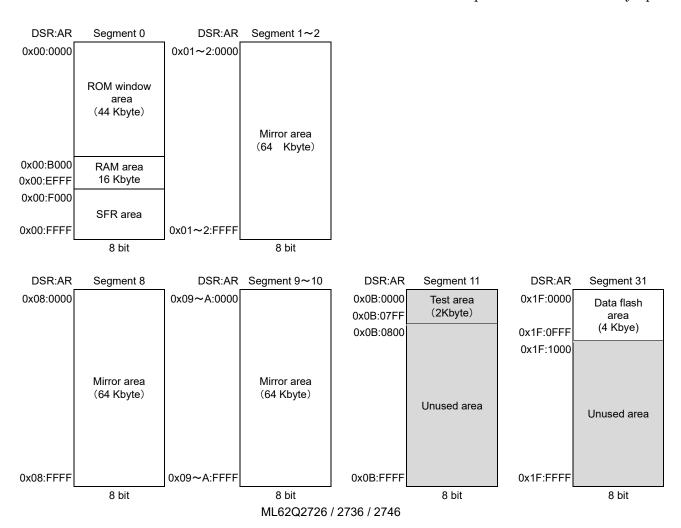

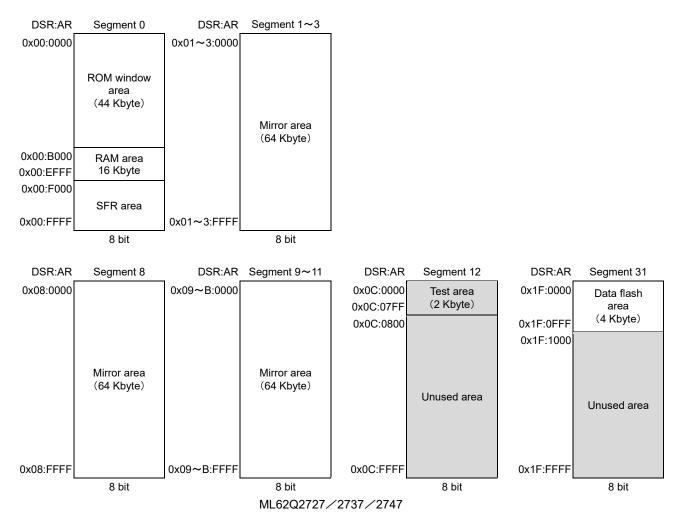

The ML62Q2700 Group has products as show in the Table 1-1 with multiple package and memory size combinations.

|   | Table ' | 1-1 Product Lis | t |

|---|---------|-----------------|---|

| _ |         | <b>50</b> ·     |   |

| Program<br>memory | Data<br>memory<br>(RAM) | Data<br>Flash | 48pin<br>TQFP48<br>WQFN48 | 52pin<br>TQFP52 | 64pin<br>QFP64<br>TQFP64 | 80pin<br>QFP80 | 100pin<br>QFP100<br>TQFP100 |

|-------------------|-------------------------|---------------|---------------------------|-----------------|--------------------------|----------------|-----------------------------|

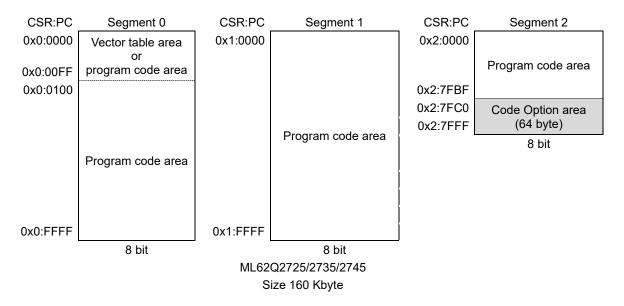

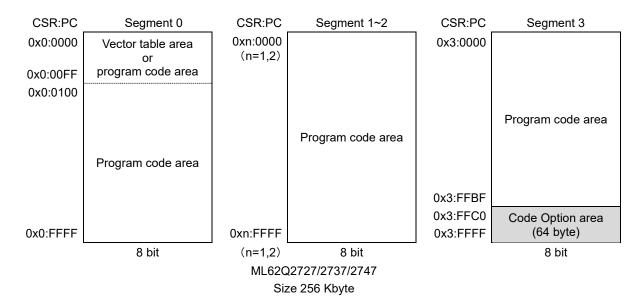

| 256Kbyte          |                         |               | -                         | -               | ML62Q2727                | ML62Q2737      | ML62Q2747                   |

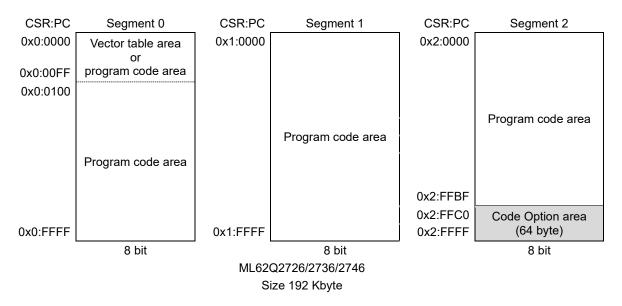

| 192Kbyte          | 16Kbyte                 |               | 1                         | 1               | ML62Q2726                | ML62Q2736      | ML62Q2746                   |

| 160Kbyte          |                         | 4Kbyte        | -                         | -               | ML62Q2725                | ML62Q2735      | ML62Q2745                   |

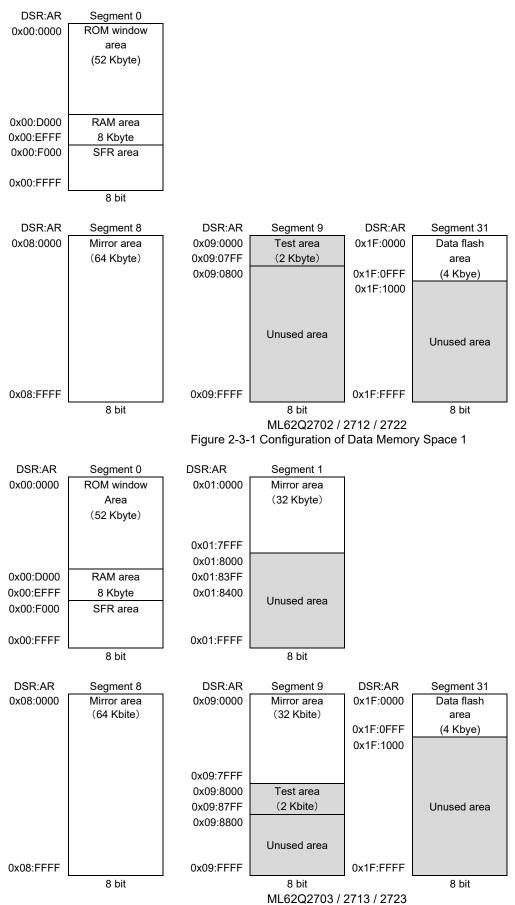

| 96Kbyte           | 8Kbyte                  |               | ML62Q2703                 | ML62Q2713       | ML62Q2723                | 1              | 1                           |

| 64Kbyte           | ortbyte                 |               | ML62Q2702                 | ML62Q2712       | ML62Q2722                | -              | -                           |

# 1.1 Features

CPU

16-bit RISC CPU : nX-U16/100 (A35 core)

Instruction system : 16-bit length instructions

Instruction set : Transfer, arithmetic operations, comparison, logic operations, multiplication/division,

bit manipulations, bit logic operations, jump, conditional jump, call return stack

manipulations, arithmetic shift, and so on

Built-in On-chip debug function (connect to the Lapis Technology on-chip debug emulator)

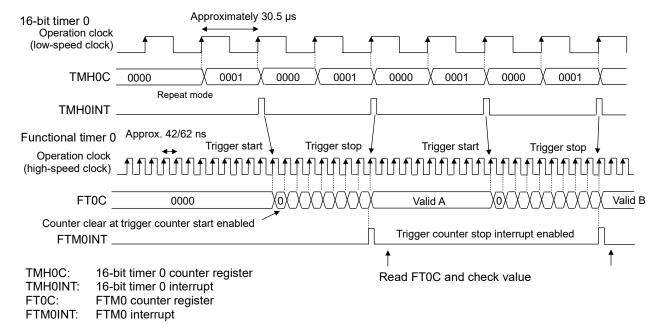

Minimum instruction execution time: 1 count of system clock

Approximately 30.5µs/62.5ns/41.6ns (at 32.768 kHz/16 MHz/24MHz system clock)

## Coprocessor for multiplication and division

- Signed or Unsigned is selectable

| Parameter                            | Expression            | Operation time [cycle] |

|--------------------------------------|-----------------------|------------------------|

| Multiplication                       | 16bit × 16bit         | 4                      |

| Division                             | 32bit ÷ 16bit         | 8                      |

|                                      | 32bit ÷ 32bit         | 16                     |

| Multiply-accumulate (non-saturating) | 16bit × 16bit + 32bit | 4                      |

• Operating voltage and temperature

Operating voltage: V<sub>DD</sub> = 1.8 to 5.5 V

Operating temperature: -40 °C to +105 °C

#### Flash memory

| Parameter               | Program memory area | Data Flash memory area |  |  |  |

|-------------------------|---------------------|------------------------|--|--|--|

| Erase/Write count       | 100 cycles          | 10,000 cycles          |  |  |  |

| Write unit              | 32bit(4byte)        | 8bit(1byte)            |  |  |  |

| Erase unit              | 16Kbyte/1Kbyte      | all area/128byte       |  |  |  |

| Erase/Write temperature | 0 °C to +40 °C      | -40 °C to +85 °C       |  |  |  |

- Background Operation (CPU can work while erasing and rewriting to the Data Flash memory area.)

- The built-in on-chip debug function and ISP (In-System Programming) function enable Flash programming

This product uses Super Flash® technology licensed from Silicon Storage Technology, Inc.

Super Flash® is a registered trademark of Silicon Storage Technology, Inc.

- Data RAM area

- Rewrite unit: 8bit/16bit (1byte/2byte)

- Parity check function is available (interrupt or reset is generatable at Parity error)

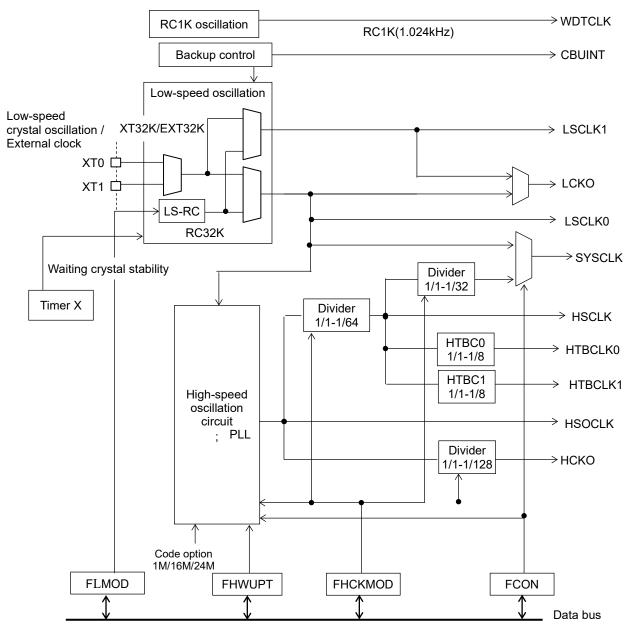

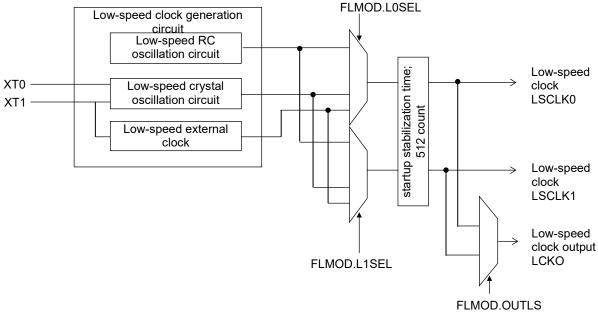

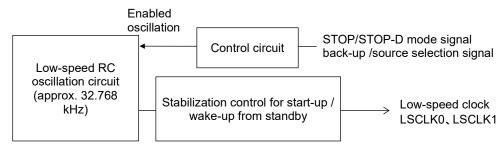

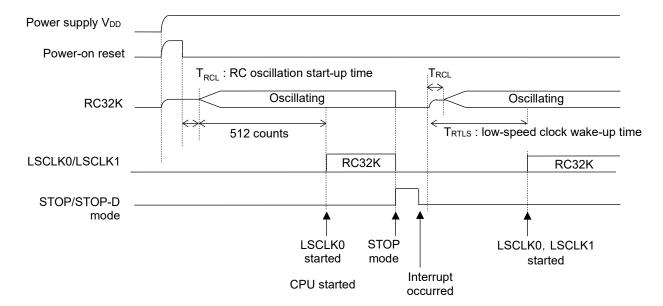

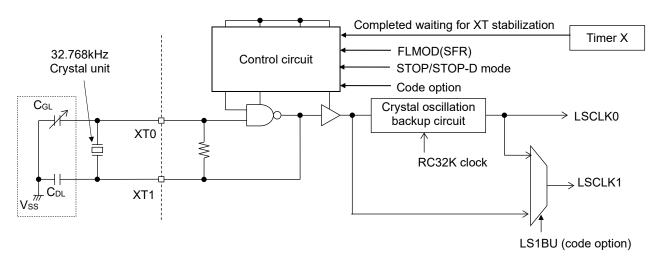

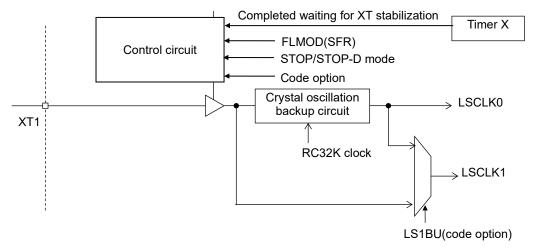

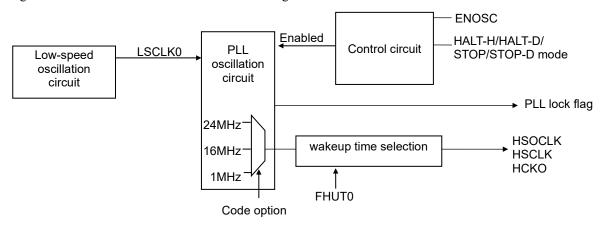

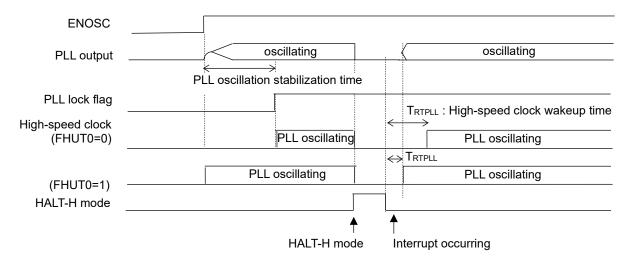

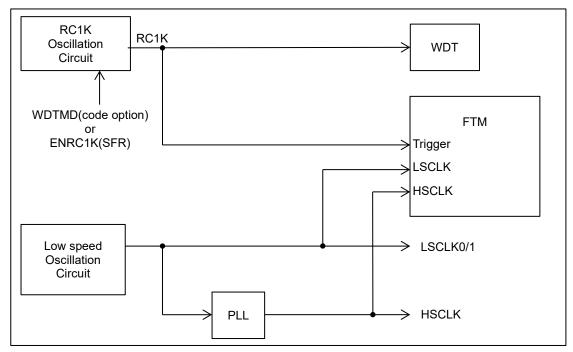

- Clock generation circuit

- Low-speed clock (LSCLK)

Internal low-speed RC oscillation (RC32K) : Approx. 32.768 kHz External low-speed clock input (EXT32K) : Approx. 32.768 kHz External low-speed crystal oscillation (XT32K) : Approx. 32.768 kHz,

Selectable 4 mode (Tough, Normal, Low power mode, and Ultra low power mode)

High-speed clock (HSCLK)

PLL oscillation: selectable 3 oscillation frequency (24MHz ,16MHz and 1MHz) by code option

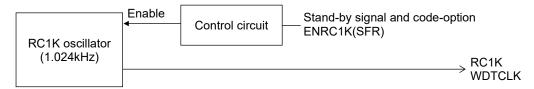

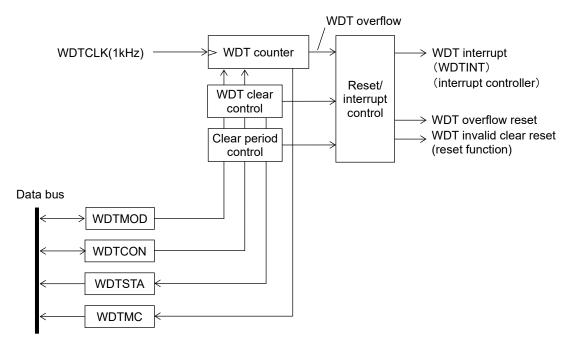

- Built-in dedicated clock generator (RC1K: Approx. 1.024kHz) for Watch Dog Timer (WDT)

- High-speed time base clock (HTBCLK)

Generates a clock with a period of 2 to 8 times that of HSCLK as a peripheral clock.

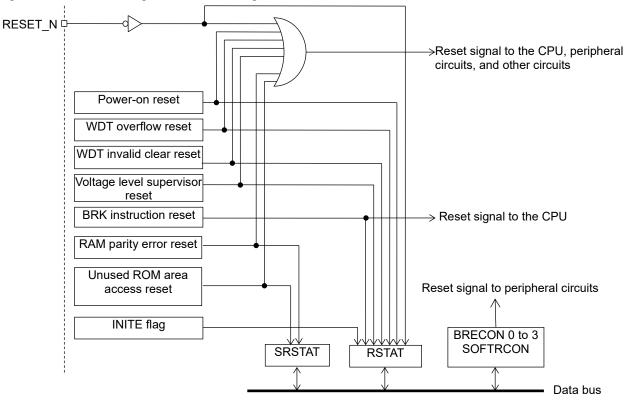

#### Reset

- System resets by reset input pin, Power-On Reset, voltage level supervisor (VLS), WDT overflow, WDT invalid clear, RAM parity error, and PC error (unused ROM area access (instruction access))

- Software reset by BRK instruction (reset CPU only)

- Reset the peripherals individually/collectively by software

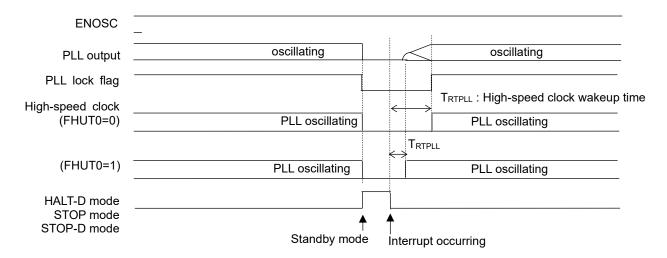

## • Power management

- Optimal power management with various standby modes

- STOP/STOP-D mode (All clocks are stopped), HALT-D mode (clocks for System and part of the peripheral block are stopped), HALT/HALT-H mode (clocks for System are stopped)

- HALT-D mode is suitable for long term standby, HALT-H mode is suitable for short term Intermittent operation standby

- Individual clock input control to the peripheral blocks by software

- High-speed clock frequency (HSCLK) is configurable (1/1, 1/2, 1/4, 1/8, 1/16, 1/32, 1/64 of PLL clock, Max. 7steps)

- Clock gear: High-speed system clock frequency is changeable dynamically

- (1/1, 1/2, 1/4, 1/8, 1/16, 1/32 of HSCLK, Max 6steps)

## Interrupt controller

Non-maskable interrupt source : 1 (Internal sources: WDT)

Maskable interrupt sources

: Max. 50 (included the external interrupt 9 sources)

Four step interrupt levels

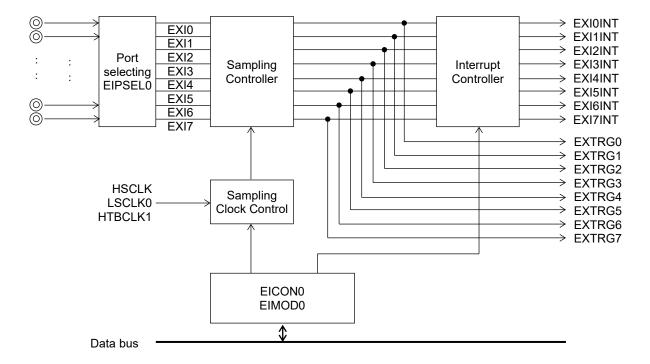

- External interrupt ports (EXI) : 8 (selectable from Max.32 pins) with sampling filter

and edge (rise, fall, both) selection.

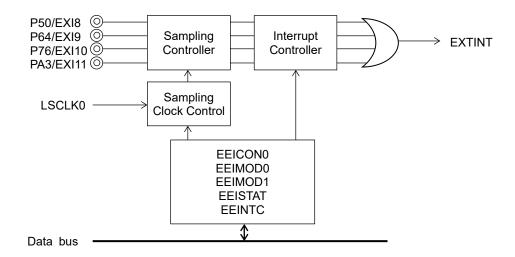

- Expanded external interrupt ports : Max. 4 with sampling filter and edge(rise, fall, both)selection

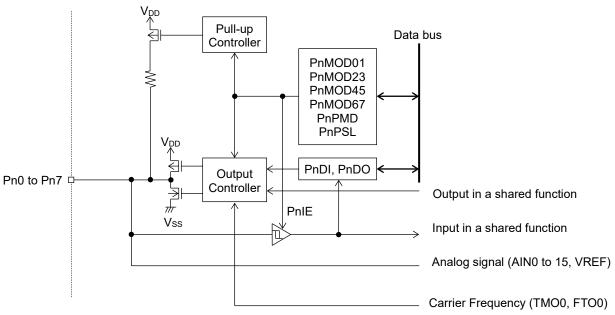

## • General-purpose ports (GPIO)

- I/O port : Max. 92 (Including pins for shared functions)

- Input port : 3 (Including one pin for shared on-chip debug and two pins for shared low speed crystal oscillation)

- Carrier frequency output function (for IR communication)

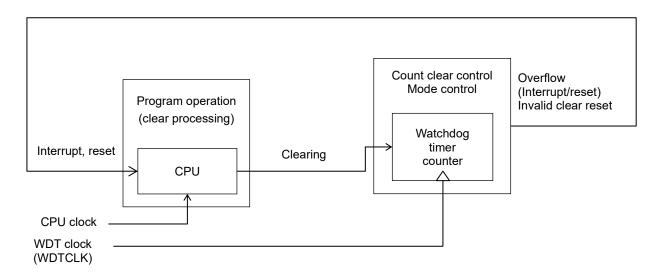

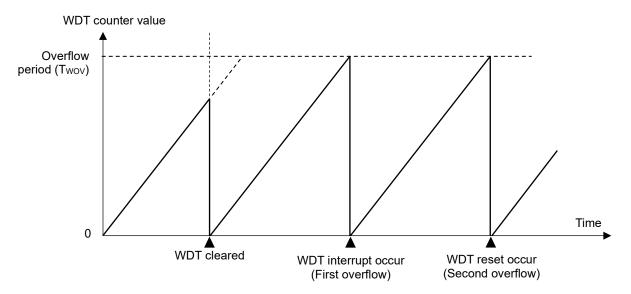

- Watchdog timer (WDT): 1 channel

- Overflow period: 8selectable (7.8, 15.6, 31.3, 62.5, 125, 500, 2000, 8000ms)

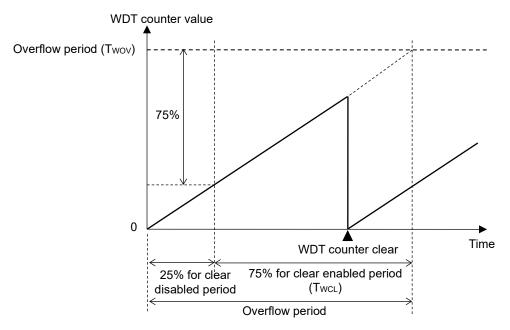

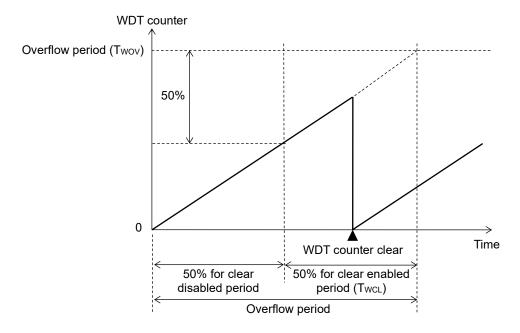

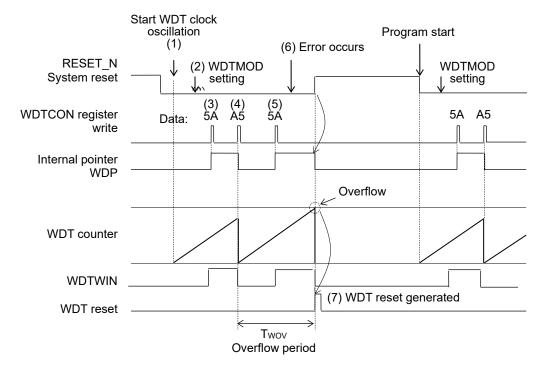

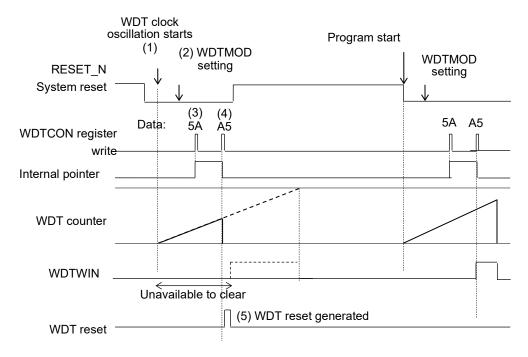

- Selectable window function (enable or disable):

- configurable clear enable period (50% or 75% of overflow period) with invalid clear

When disable, Interrupts the first overflow and resets the second overflow

When enable, reset occurs for the first overflow

- Selectable WDT operation: select Enable or Disable by code option

- Selectable operation during HALT/HALT-H mode and HALT-D mode (Continue counting/Stop counting)

- WDT counter operation monitoring function (Readable WDT counter)

- Low-speed Time base counter (LTBC): 2 channels

- Generate 8 frequency (128, 64, 32, 16, 8, 4, 2, 1Hz) internal pulse signals by dividing the Low-speed clock (LSCLK)

- 4 interrupts are generatable from 8 different frequencies internal pulse signals

- One of internal pulse signals selected to interrupt can be output from general purpose port (TBCO)

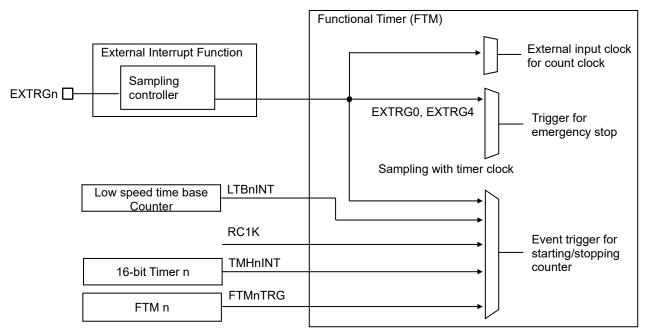

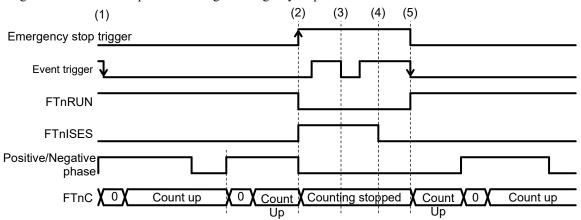

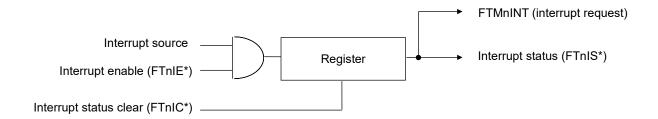

- Functional timer : Max. 8 channels

- Various modes (Continuous, One shot, capture, PWM with the same period and different duties, and complementary PWM output with the dead time)

- Event trigger (external pin, 16bit timer, functional timer, LTBC, RC1K)

- Selectable counter clock from various sources (divided by 1 to 8 of LSCLK, HSCLK, HTBCLK, and external clock)

- 16-bit General timers: Max. 8 channels

- Timer output (toggled by overflow)

- Selectable counter clock from various sources (divided by 1 to 8 of LSCLK, HSCLK, HTBCLK, LTBC, RC1K, and external clock)

- Timer X is shared with waiting for the stability of low-speed crystal oscillation

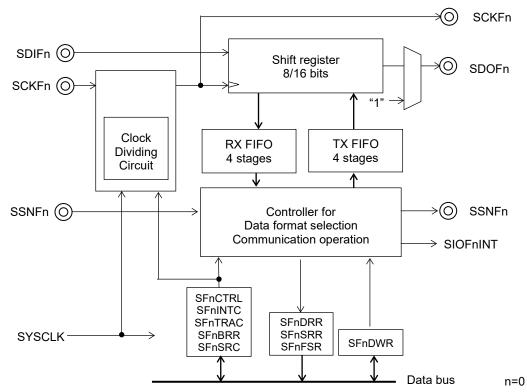

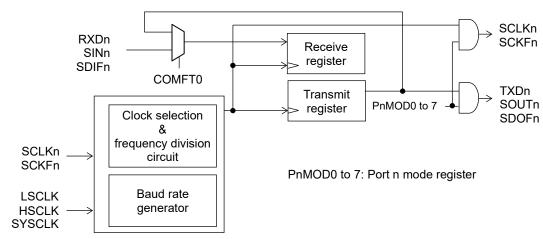

- Synchronous Serial Port: Max. 7 channels (with FIFO: 1 channel, without FIFO: Max. 6 channels)

- FIFO: 4steps for each transmitting and receiving

- Selectable from Master and Slave

- Selectable from LSB first or MSB first

- Selectable 8-bit length or 16-bit length

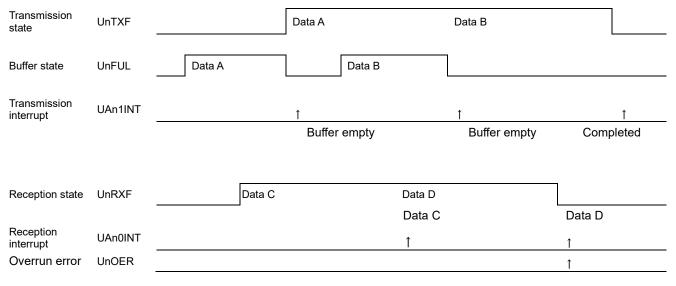

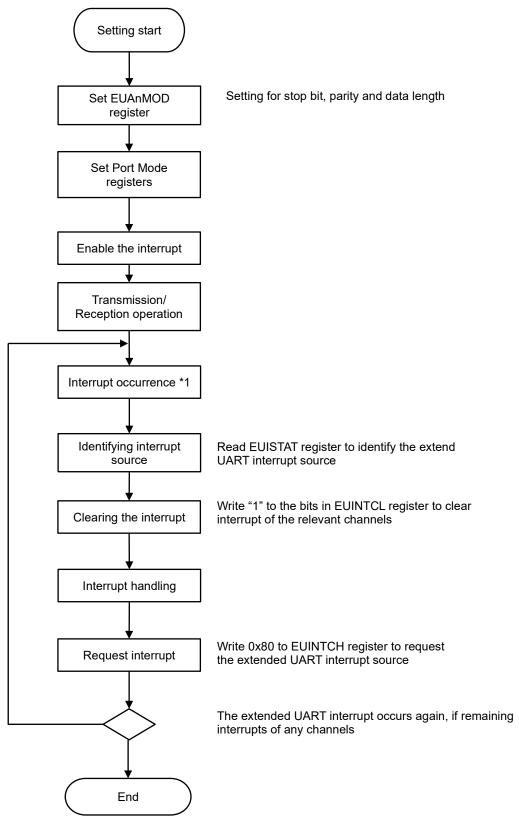

- UART (Full-duplex communication mode): Max. 6 channels

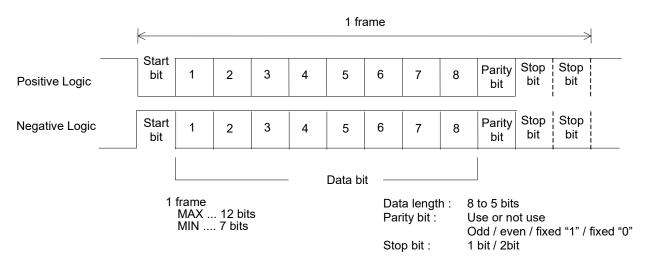

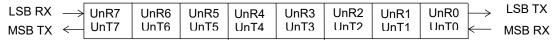

- Selectable from 5 to 8bit length, parity or no parity, odd parity or even parity, 1 stop bit or 2 stop bits, Positive logic or Negative logic, LSB first or MSB first

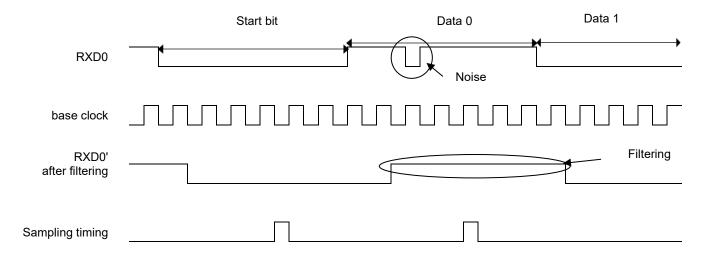

- Sampling filter for receiving data and start bit

- Built-in baud rate generator

- 1bps to 4,800bps (Clock frequency is 32.768kHz)

- 300bps to 2Mbps (Clock frequency is 16MHz)

- 600bps to 3Mbps (Clock frequency is 24MHz)

- I<sup>2</sup>C bus: 3 channels

- Select from Master mode or Slave mode: 1 channel. Master mode only: 2 channels

- Standard mode (100kbps), fast mode (400kbps) and 1Mbps mode(1Mbps)

- 7bit address format

- Master mode: Handshake (Clock synchronization), 10bit slave address format is supported

- Slave mode : Clock stretch function

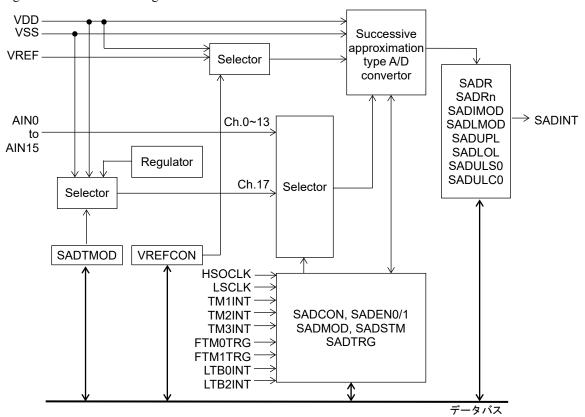

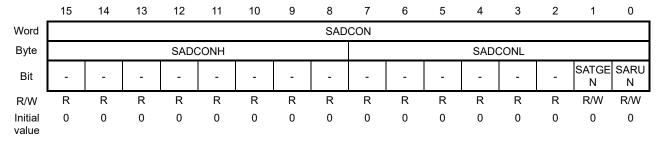

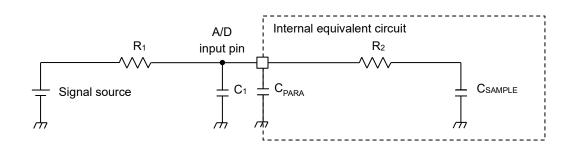

- Successive approximation type 12bit A/D converter (SA-ADC): input 14 channels

- Conversion time: Min. 1.375μs / ch (When the VDD is higher than 2.7V and the conversion clock is 16MHz)

- Reference voltages are selectable from VDD pin input voltage or External reference voltage (VREF pin)

- dedicated result register for each channel

- Continuous conversion, Trigger start, Interrupt determining by upper limit or lower limit threshold of conversion result

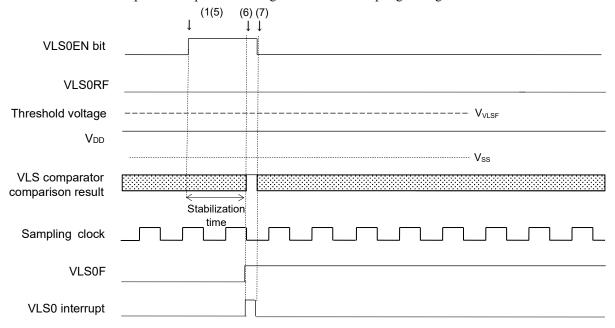

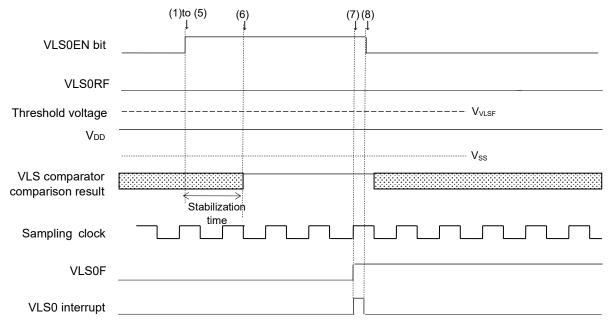

- Voltage Level Supervisor (VLS): 1 channel

- Threshold voltage: selectable from 15 level (from 1.85V to 4.00V)

- Functional Voltage level detection reset (VLS reset) or Functional Voltage level detection interrupt (VLS0 interrupt) is generatable

- Equipped with single mode / with sampling filter / low consumption operation

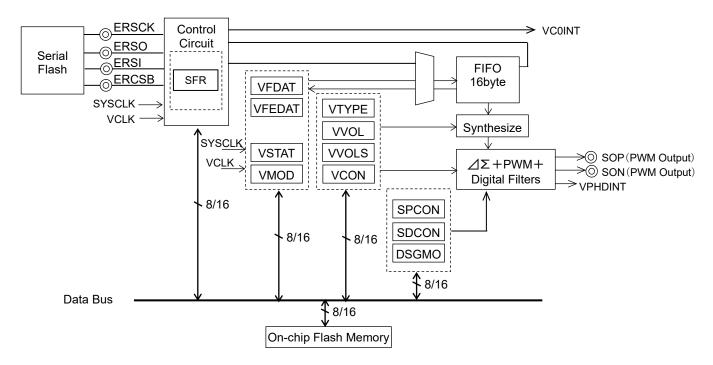

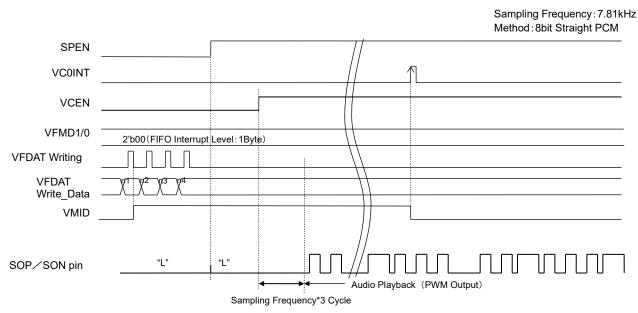

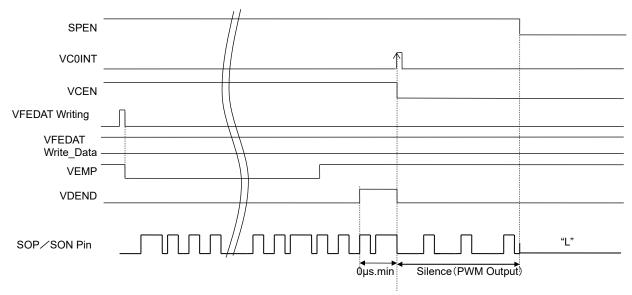

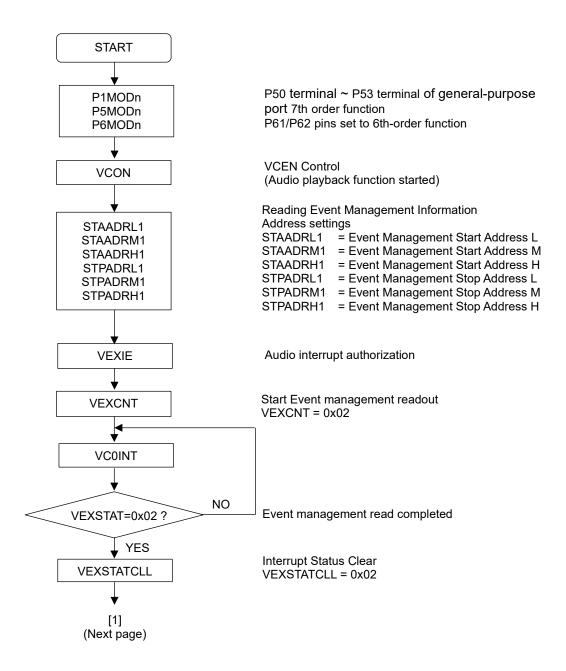

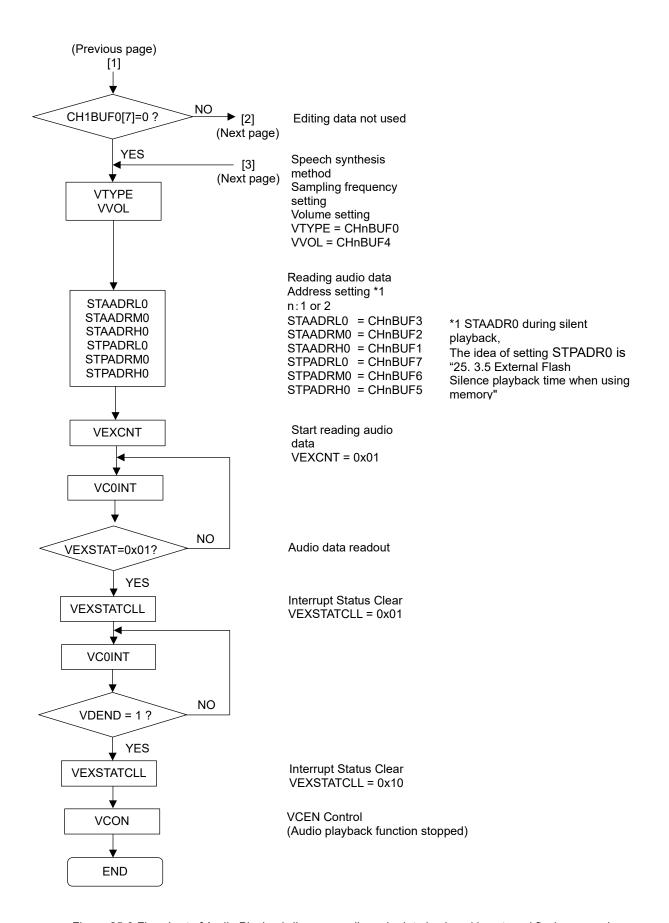

- Audio playback function: 1channel

- Audio synthesis method: 4bit ADPCM2, 8bit-non-linear PCM, 8bit Straight PCM, 16bit Straight PCM

- Sampling frequency: 7.81kHz, 15.63kHz, 31.25kHz, 10.42kHz, 20.83kHz, 6.25kHz, 12.50kHz, 25.00kHz.

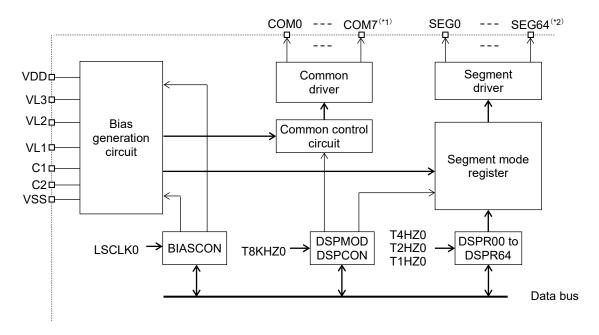

- LCD driver

- Max. 480 dots (60seg x 8 com) \*1

```

ML62Q2702/ML62Q2703:

```

$24 \text{seg} \times 8 \text{com} \text{ (com Max.)}, \quad 29 \text{seg} \times 3 \text{com} \text{ (seg Max.)}$

ML62Q2712/ML62Q2713:

$27 \text{seg} \times 8 \text{com (com Max.)}, \quad 32 \text{seg} \times 3 \text{com (seg Max.)}$

ML62Q2722/ML62Q2723/ML62Q2725/ML62Q2726/ML62Q2727:

$35 \text{seg} \times 8 \text{com}$  (com Max.),  $40 \text{seg} \times 3 \text{com}$  (seg Max.)

ML62Q2735/ML62Q2736/ML62Q2737:

$45 \text{seg} \times 8 \text{com (com Max.)}, 50 \text{seg} \times 3 \text{com (seg Max.)}$

ML62Q2745/ML62Q2746/ML62Q2747:

$60 \text{seg} \times 8 \text{com (com Max.)}, 65 \text{seg} \times 3 \text{com (seg Max.)}$

- \*1: Five pins are shared for common or segment, selectable by setting a SFR

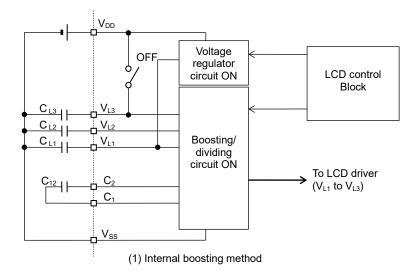

- 1/3 bias (built-in bias generation circuit)

- Frame frequency selection (Approx. 32Hz, 38Hz, 64Hz, 75Hz, 128Hz, and 150Hz)

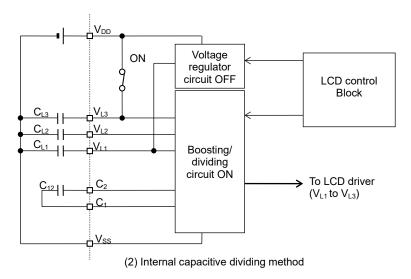

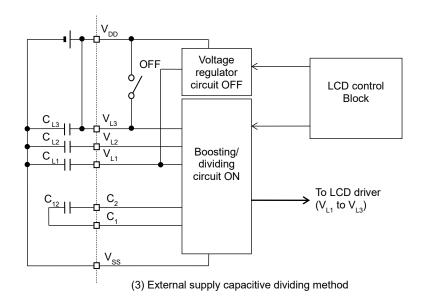

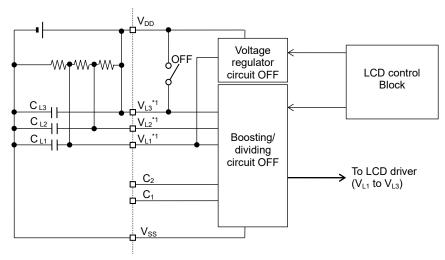

- Four bias generation modes (Internal voltage boost, External capacitive voltage divide, Internal capacitive voltage divide, and External supply voltages)

- Contrast adjustment (16 steps) is available in the Internal voltage boost mode.

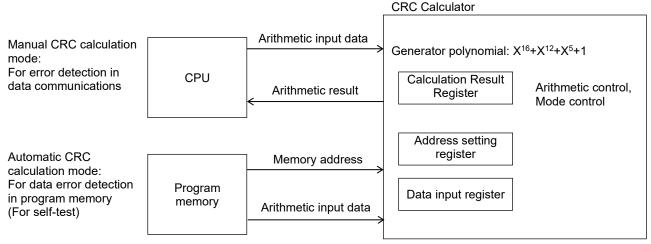

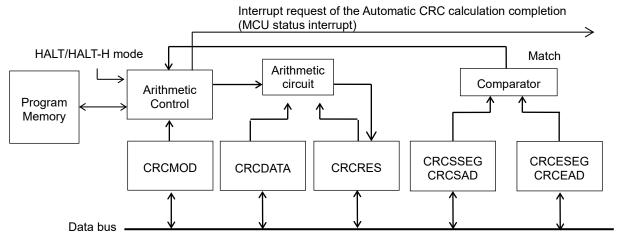

- CRC (Cyclic Redundancy Check) generator

- Generation equation:  $X^{16}+X^{12}+X^5+1$

- Selectable from LSB first or MSB first

- Built-in automatic program memory CRC calculation mode in HALT mode

- Safety Function

- Automatic switching to the internal low-speed RC oscillation in case the low-speed crystal oscillation stopped

- RAM/SFR guard

- Automatic program memory CRC calculation

- RAM parity error detection

- ROM unused area access reset (instruction access)

- Clock mutual monitoring, WDT counter monitoring

- SA-ADC test

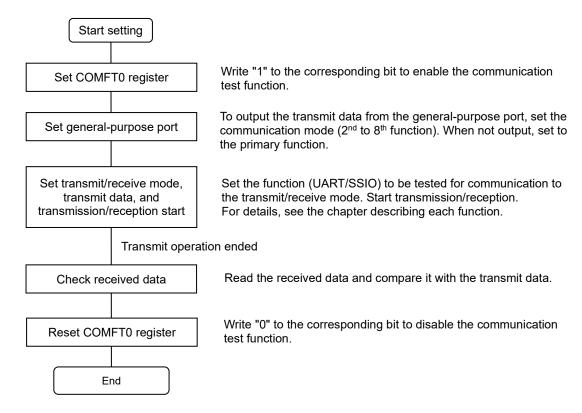

- Communication loop back test (UART, Synchronous serial port, I<sup>2</sup>C bus(master))

- GPIO test

## • Shipping package

| Package                 | Body size<br>(including lead) | Pin pitch | Produc                                                                                                          | t name                                                                                                          |

|-------------------------|-------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| 1 donage                | [mm × mm]                     | [mm]      | Tray                                                                                                            | Tape & Reel                                                                                                     |

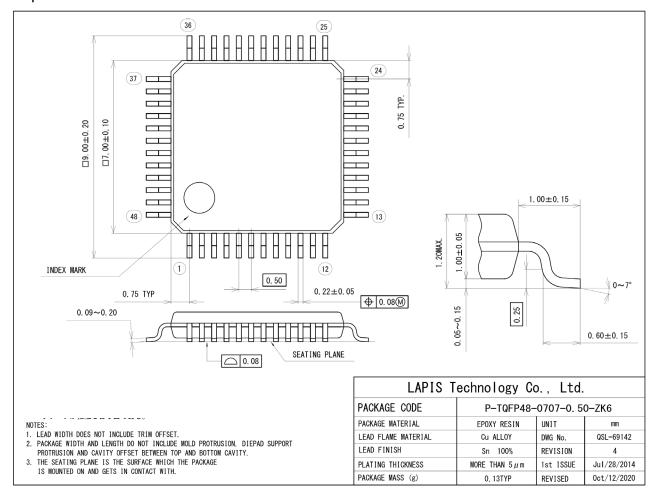

| 48 pin plastic<br>TQFP  | 7.0 × 7.0<br>(9.0 × 9.0)      | 0.50      | ML62Q2702-xxxTBZWAY<br>ML62Q2703-xxxTBZWAY                                                                      | ML62Q2702-xxxTBZWBY<br>ML62Q2703-xxxTBZWBY                                                                      |

| 48 pin plastic<br>WQFN  | 7.0 × 7.0<br>(-)              | 0.50      | ML62Q2702-xxxGDZW5AY<br>ML62Q2703-xxxGDZW5AY                                                                    | ML62Q2702-xxxGDZW5BY<br>ML62Q2703-xxxGDZW5BY                                                                    |

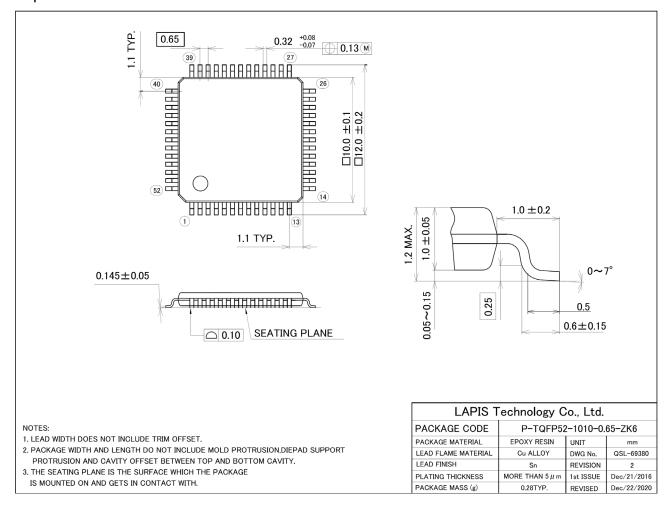

| 52 pin plastic<br>TQFP  | 10.0 × 10.0<br>(12.0 × 12.0)  | 0.65      | ML62Q2712-xxxTBZWAY<br>ML62Q2713-xxxTBZWAY                                                                      | ML62Q2712-xxxTBZWBY<br>ML62Q2713-xxxTBZWBY                                                                      |

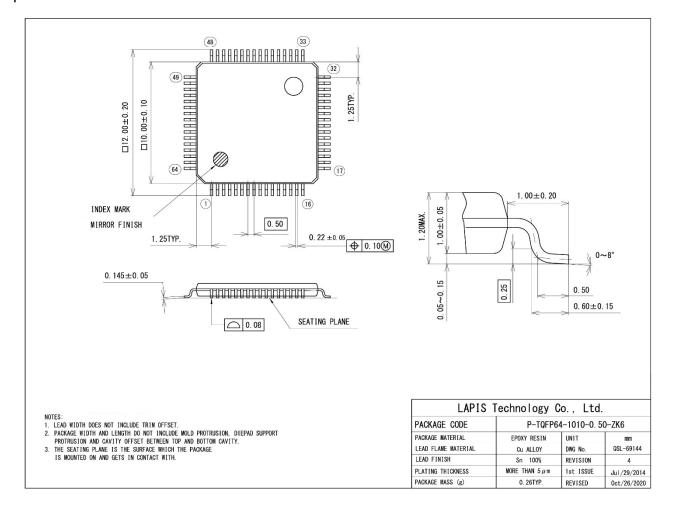

| 64 pin plastic<br>TQFP  | 10.0 × 10.0<br>(12.0 × 12.0)  | 0.50      | ML62Q2722-xxxTBZWAY<br>ML62Q2723-xxxTBZWAY<br>ML62Q2725-xxxTBZWAY<br>ML62Q2726-xxxTBZWAY<br>ML62Q2727-xxxTBZWAY | ML62Q2722-xxxTBZWBY<br>ML62Q2723-xxxTBZWBY<br>ML62Q2725-xxxTBZWBY<br>ML62Q2726-xxxTBZWBY<br>ML62Q2727-xxxTBZWBY |

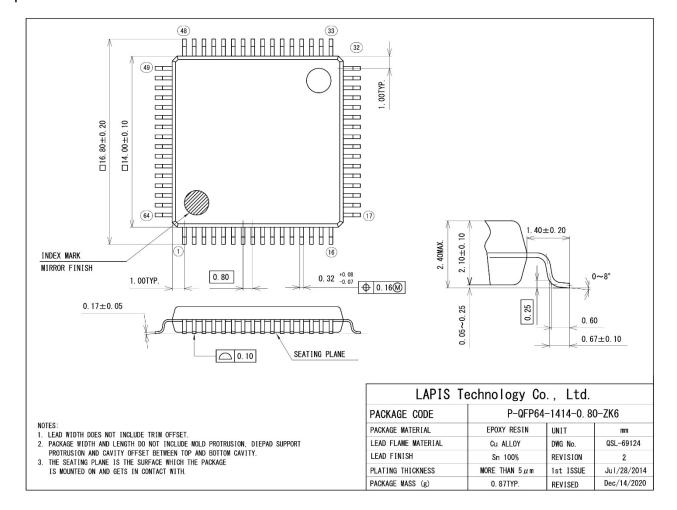

| 64 pin plastic<br>QFP   | 14.0 × 14.0<br>(16.0 × 16.0)  | 0.80      | ML62Q2722-xxxGAZWAY<br>ML62Q2723-xxxGAZWAY<br>ML62Q2725-xxxGAZWAY<br>ML62Q2726-xxxGAZWAY<br>ML62Q2727-xxxGAZWAY | -                                                                                                               |

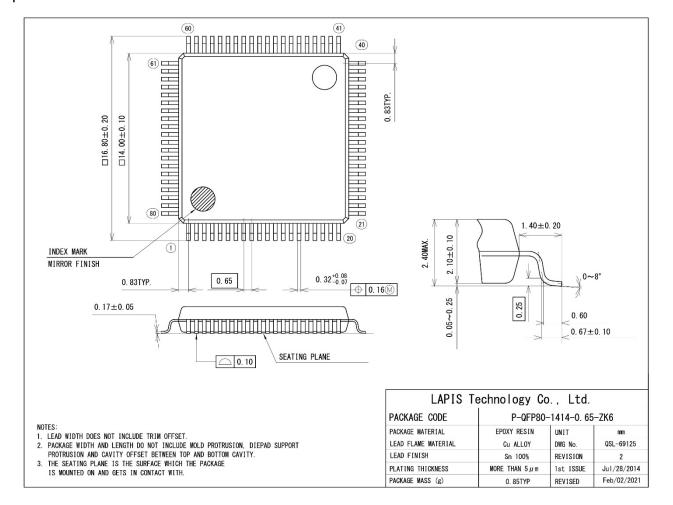

| 80 pin plastic<br>QFP   | 14.0 × 14.0<br>(16.0 × 16.0)  | 0.65      | ML62Q2735-xxxGAZWAY<br>ML62Q2736-xxxGAZWAY<br>ML62Q2737-xxxGAZWAY                                               | -                                                                                                               |

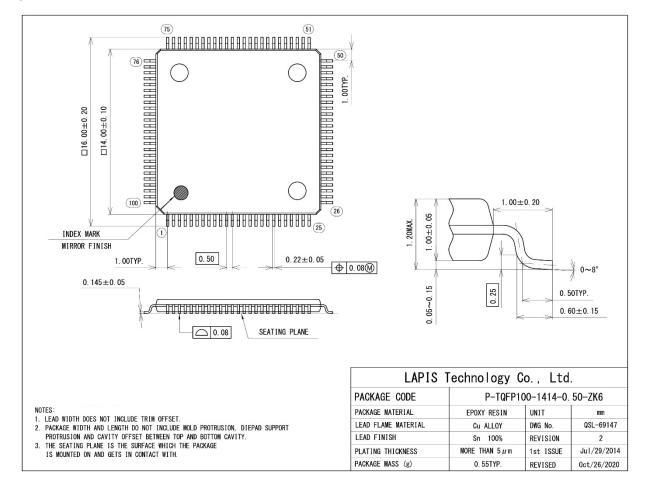

| 100 pin plastic<br>TQFP |                               |           | ML62Q2745-xxxTBZWAY<br>ML62Q2746-xxxTBZWAY<br>ML62Q2747-xxxTBZWAY                                               | -                                                                                                               |

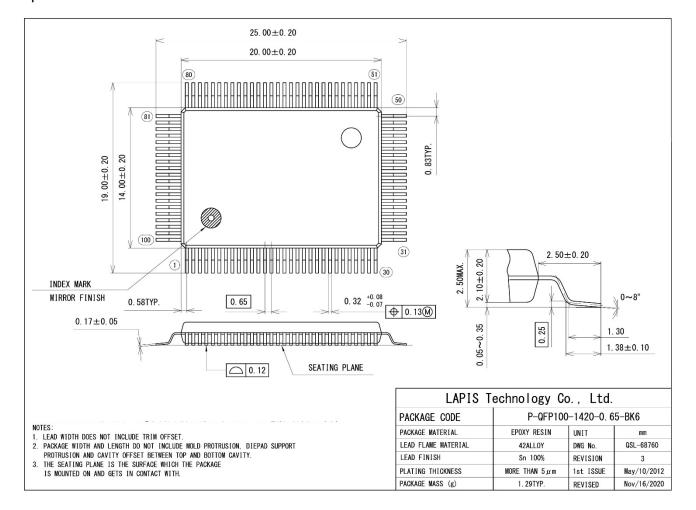

| 100 pin plastic<br>QFP  | 14.0 × 20.0<br>(19.0 × 25.0)  | 0.65      | ML62Q2745-xxxGAZWAY<br>ML62Q2746-xxxGAZWAY<br>ML62Q2747-xxxGAZWAY                                               | -                                                                                                               |

xxx: ROM code number, (NNN: ROM code is blank)

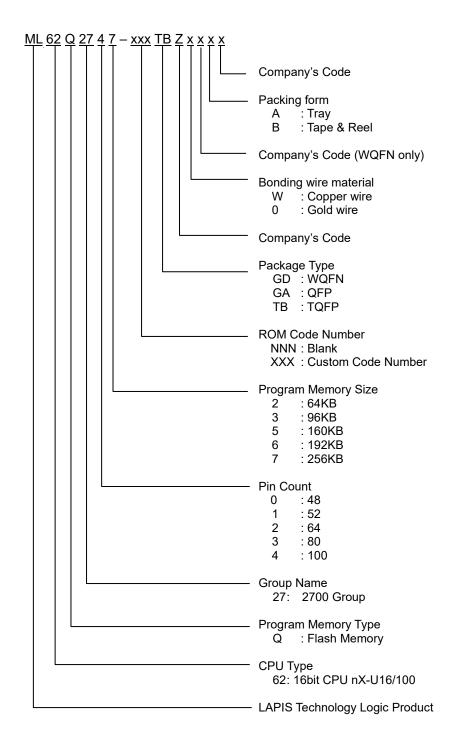

# 1.1.1 How To Read The Part Number

Figure 1-1 Part Number

# 1.1.2 Main Function List

Table 1-2 Main Function List

|             |                 |           |                 |                  |                              |                                                  | 18                                 | able              | 1-2                | ' IVI        | aın                    | -un                       | CUC                           | n L                                | IST              |                             |                               |                     |                        |                                        |                                     |                       |                                                   |                                               |                                          |                               |                         |

|-------------|-----------------|-----------|-----------------|------------------|------------------------------|--------------------------------------------------|------------------------------------|-------------------|--------------------|--------------|------------------------|---------------------------|-------------------------------|------------------------------------|------------------|-----------------------------|-------------------------------|---------------------|------------------------|----------------------------------------|-------------------------------------|-----------------------|---------------------------------------------------|-----------------------------------------------|------------------------------------------|-------------------------------|-------------------------|

|             |                 |           |                 |                  |                              | Pin                                              |                                    |                   |                    |              |                        | Int                       | erru                          | upt                                |                  | Т                           | ïme                           | er                  |                        | Сс                                     | mm                                  | nuni                  | icat                                              | ion                                           | Ana                                      | alog                          | Other                   |

| Part number | Total pin count | Power pin | Reset Input pin | Debug Input port | General purpose Input pin *1 | General purpose I/O pin (LED drive is supported) | LCD common/segment shared pin *2*3 | LCD common pin *3 | LCD segment pin *3 | LCD bias pin | External interrupt pin | External interrupt source | Non maskable interrupt source | Internal maskable interrupt source | 16bit Timer [ch] | 16bit Functional Timer [ch] | 16bit Functional Timer [Port] | Watchdog Timer [ch] | Time base counter [ch] | Synchronous serial (without FIFO) [ch] | Synchronous serial (with FIFO) [ch] | Full-duplex UART [ch] | I <sup>2</sup> C bus interface (Master only) [ch] | I <sup>2</sup> C bus unit (Master/Slave) [ch] | 12bit Successive type A/D converter [ch] | Voltage Level Supervisor [ch] | Audio playback function |

| ML62Q2702   | 48              |           |                 |                  |                              | 35                                               |                                    |                   | 24                 |              | 20                     |                           |                               |                                    |                  |                             |                               |                     |                        |                                        |                                     |                       |                                                   |                                               |                                          |                               |                         |

| ML62Q2703   | 70              |           |                 |                  |                              | 33                                               |                                    |                   | 27                 |              | 20                     |                           |                               | 32                                 |                  |                             |                               |                     |                        |                                        |                                     |                       |                                                   |                                               |                                          |                               |                         |

| ML62Q2712   | 52              |           |                 |                  |                              | 39                                               |                                    |                   | 27                 |              | 23                     |                           |                               | 02                                 | 6                | 6                           | 12                            |                     |                        | 2                                      |                                     | 2                     |                                                   |                                               |                                          |                               |                         |

| ML62Q2713   | 02              |           |                 |                  |                              | 0.0                                              |                                    |                   | ۷.                 |              | 23                     |                           |                               |                                    | ľ                |                             | 12                            |                     |                        | _                                      |                                     | _                     |                                                   |                                               |                                          |                               |                         |

| ML62Q2722   |                 | 3         |                 |                  |                              |                                                  |                                    |                   |                    |              |                        |                           |                               |                                    |                  |                             |                               |                     |                        |                                        |                                     |                       |                                                   |                                               | 12                                       |                               |                         |

| ML62Q2723   |                 |           |                 |                  |                              |                                                  |                                    |                   |                    |              |                        |                           |                               |                                    |                  |                             |                               |                     |                        |                                        |                                     |                       |                                                   |                                               |                                          |                               |                         |

| ML62Q2725   | 64              |           |                 |                  |                              | 51                                               |                                    |                   | 35                 |              | 32                     |                           |                               |                                    |                  |                             |                               |                     |                        |                                        |                                     |                       |                                                   |                                               |                                          |                               |                         |

| ML62Q2726   |                 |           | 1               | 1                | 3                            |                                                  | 5                                  | 3                 |                    | 5            |                        | 9                         | 1                             |                                    |                  |                             |                               | 1                   | 2                      |                                        | 1                                   |                       | 2                                                 | 1                                             |                                          | 1                             | 1                       |

| ML62Q2727   |                 |           |                 |                  |                              |                                                  |                                    |                   |                    |              |                        |                           |                               |                                    |                  |                             |                               |                     |                        |                                        |                                     |                       |                                                   |                                               |                                          |                               |                         |

| ML62Q2735   |                 |           |                 |                  |                              |                                                  |                                    |                   |                    |              |                        |                           |                               | 41                                 |                  |                             |                               |                     |                        |                                        |                                     |                       |                                                   |                                               |                                          |                               |                         |

| ML62Q2736   | 80              |           |                 |                  |                              | 65                                               |                                    |                   | 45                 |              |                        |                           |                               |                                    | 8                | 8                           | 16                            |                     |                        | 6                                      |                                     | 6                     |                                                   |                                               |                                          |                               |                         |

| ML62Q2737   |                 | 4         |                 |                  |                              |                                                  |                                    |                   |                    |              | 36                     |                           |                               |                                    |                  |                             |                               |                     |                        |                                        |                                     |                       |                                                   |                                               | 16                                       |                               |                         |

| ML62Q2745   |                 | 4         |                 |                  |                              |                                                  |                                    |                   |                    |              | 30                     |                           |                               |                                    |                  |                             |                               |                     |                        |                                        |                                     |                       |                                                   |                                               | 16                                       |                               |                         |

| ML62Q2746   | 100             |           |                 |                  |                              | 85                                               |                                    |                   | 60                 |              |                        |                           |                               |                                    |                  |                             |                               |                     |                        |                                        |                                     |                       |                                                   |                                               |                                          |                               |                         |

| ML62Q2747   |                 |           |                 |                  |                              |                                                  |                                    |                   |                    |              |                        |                           |                               |                                    |                  |                             |                               |                     |                        |                                        |                                     |                       |                                                   |                                               |                                          |                               |                         |

${\rm FEUL} 62{\rm Q}2700$ 1-7

<sup>\*1:</sup> Shared with pins for crystal oscillation and debug input.

\*2: The LCD common/segment shared pins are shared for common or segment, selectable by setting a SFR

<sup>\*3:</sup> All LCD drive pins are shared with general purpose I/O ports.

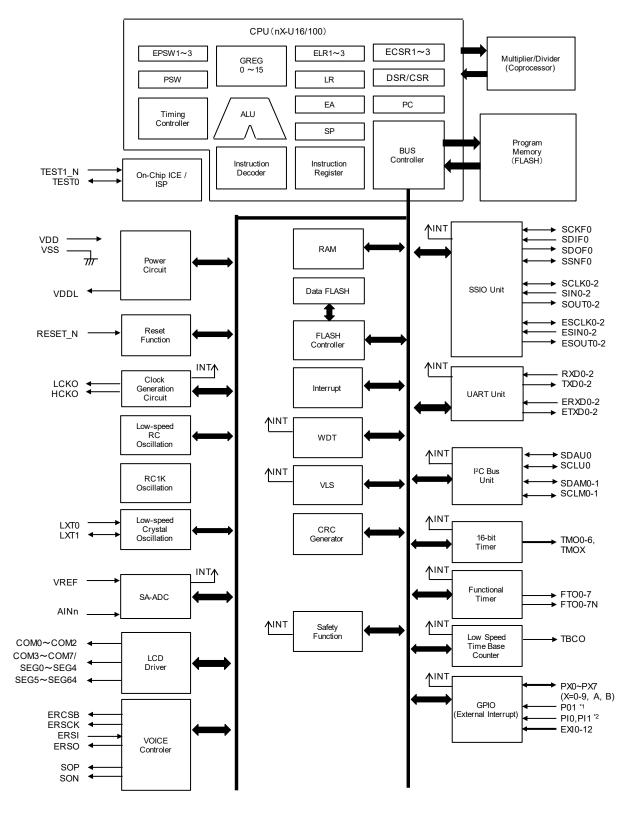

# 1.2 Block Diagram

- \*1 : Not available as the input port when connecting to the on-chip debug emulator.

- \*2 : Not available as the input port when connecting to the crystal resonator.

Figure 1-2 Block Diagram of ML62Q2700 group

- 1.3 Pin

- 1.3.1 Pin Layout

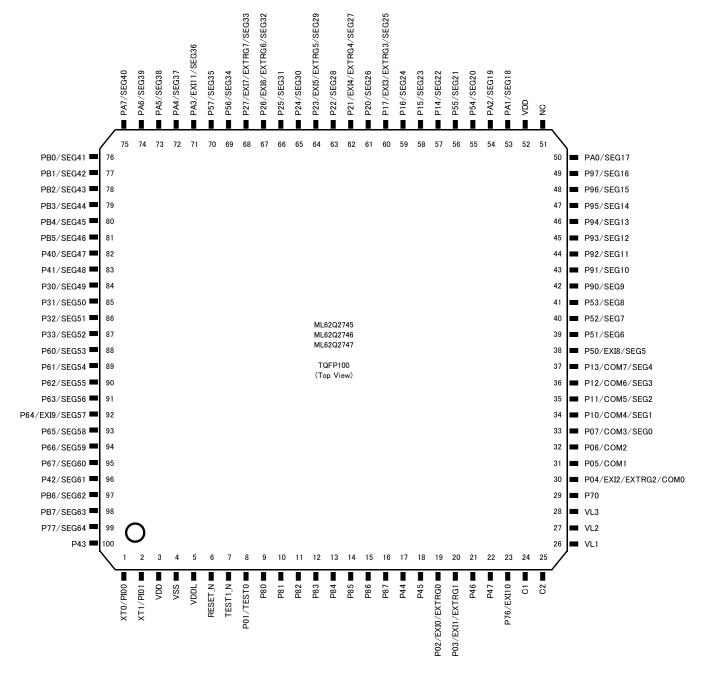

- 1.3.1.1 ML62Q2745/ML62Q2746/ML62Q2747: 100 pin TQFP

Figure 1-3-1 100 pin TQFP

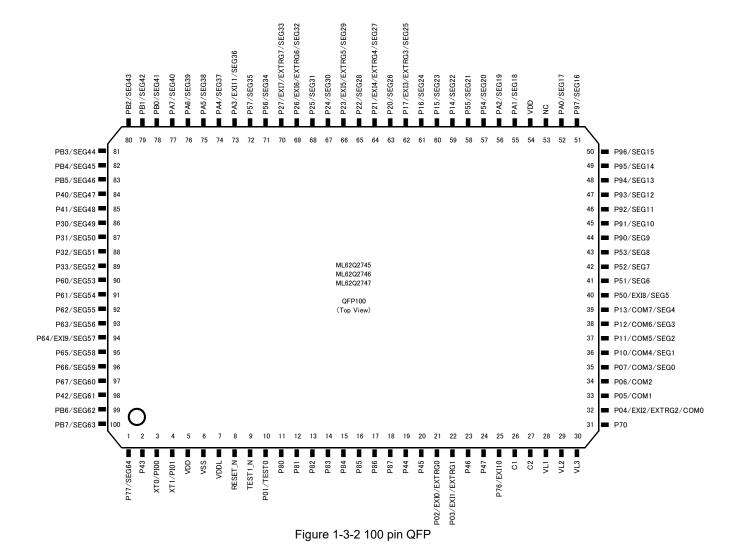

# 1.3.1.2 ML62Q2745/ML62Q2746/ML62Q2747: 100 pin QFP

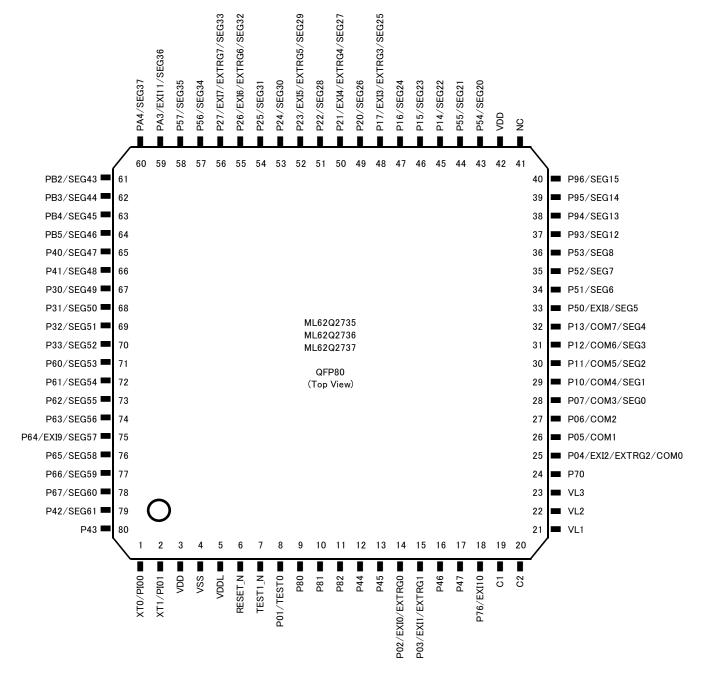

# 1.3.1.3 ML62Q2735/ML62Q2736/ ML62Q2737: 80 pin QFP

Figure 1-3-3 80 pin QFP

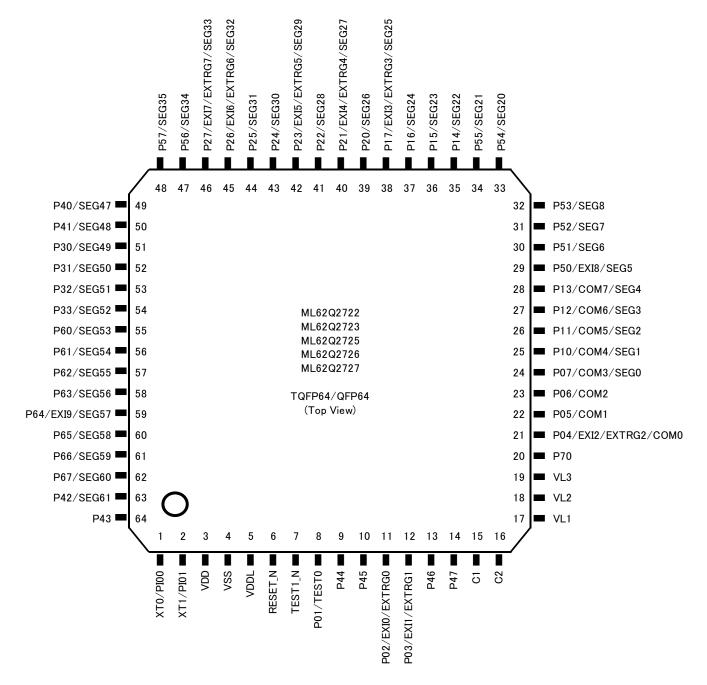

# 1.3.1.4 ML62Q2722/ML62Q2723/ML62Q2725/ ML62Q2726/ML62Q2727: 64 pin TQFP/QFP

Figure 1-3-4 64 pin TQFP/QFP

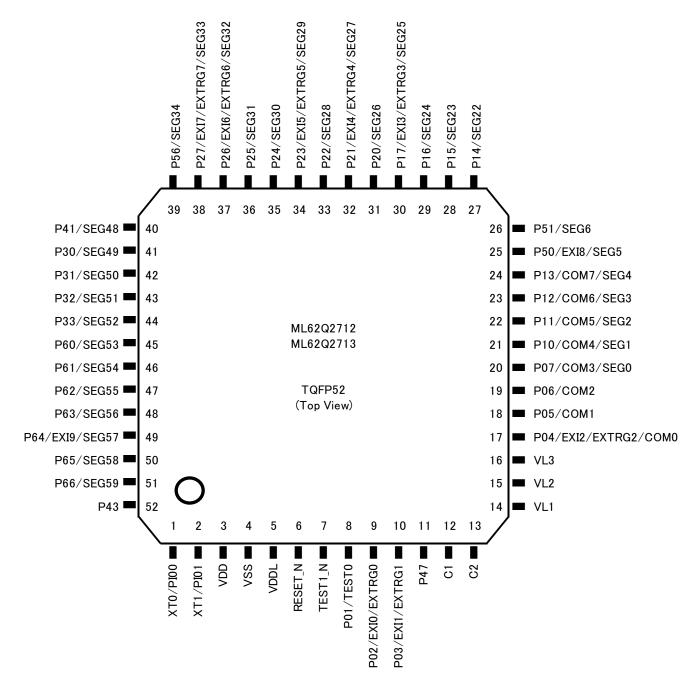

# 1.3.1.5 ML62Q2712/ML62Q2713 : 52 pin TQFP

Figure 1-3-5 52 pin TQFP

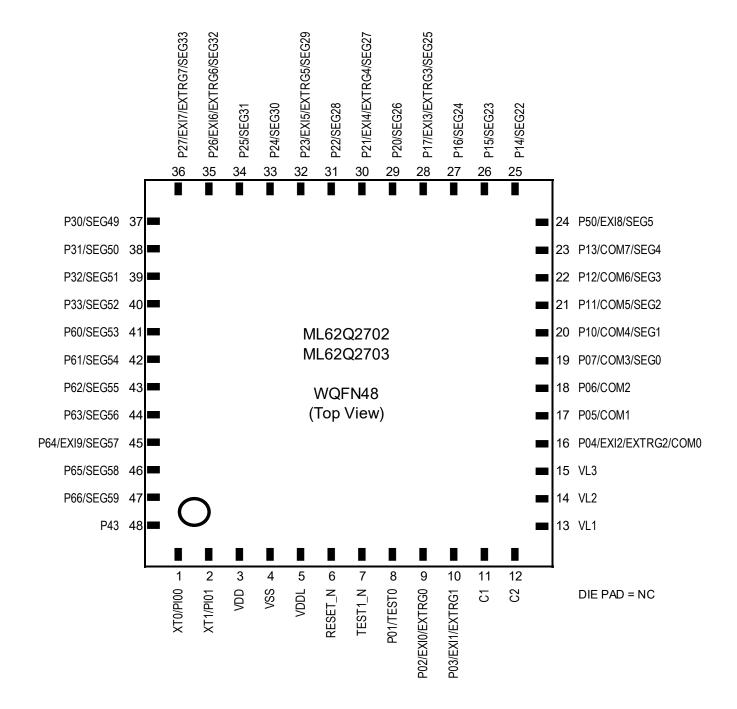

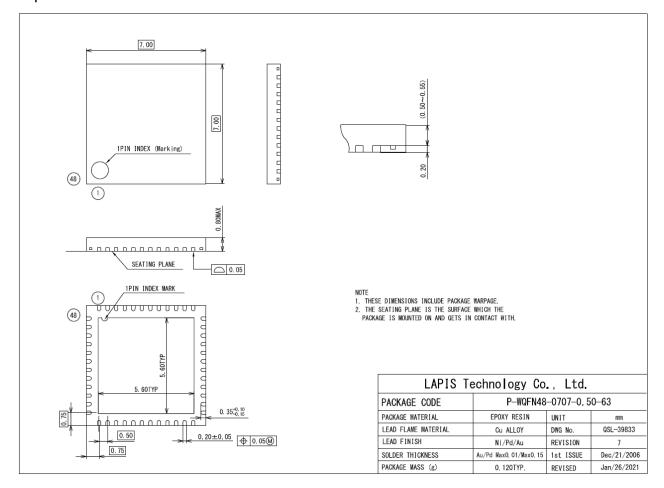

# 1.3.1.6 ML62Q2702/ML62Q2703: 48 pin WQFN

Figure 1-3-6 48 pin WQFN

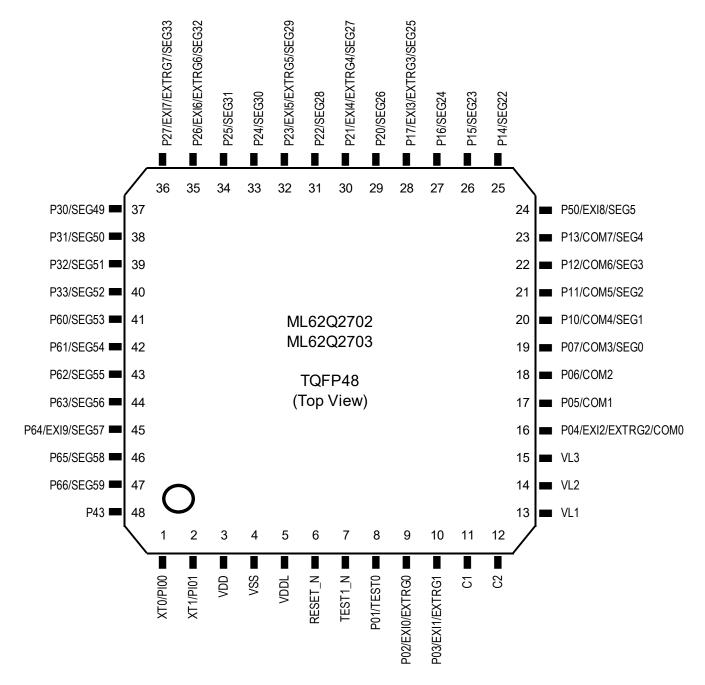

# 1.3.1.7 ML62Q2702/ML62Q2703: 48 pin TQFP

Figure 1-3-7 48 pin TQFP

# 1.3.2 Pin List

Table 1-3 shows the pin list of ML62Q2700 group.

|       | Table 1-3 ML62Q2700 Group Pin List (1/3) |       |       |         |        |                    |                               |                       |                       |                       |                       |                       |                       |                       |

|-------|------------------------------------------|-------|-------|---------|--------|--------------------|-------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

|       |                                          | Pin   | No.   |         |        |                    |                               | 1 <sup>st</sup> func. | 2 <sup>nd</sup> func. | 3 <sup>rd</sup> func. | 4 <sup>th</sup> func. | 5 <sup>th</sup> func. | 6 <sup>th</sup> func. | 7 <sup>th</sup> func. |

| 48Pin | 52Pin                                    | 64Pin | 80Pin | TQFP100 | QFP100 | LSI<br>Pin<br>name | Career<br>frequency<br>output | EXI/<br>LCD/<br>ADC   | SSIO                  | UART                  | l <sup>2</sup> C      | FTM                   | Timer                 | CLKOUT/<br>LTBC       |

| 3     | 3                                        | 3     | 3     | 3       | 5      | VDD                | -                             | -                     | -                     | -                     | -                     | -                     | -                     | -                     |

| -     | -                                        | -     | 42    | 52      | 54     | VDD                | -                             | -                     | -                     | -                     | -                     | -                     | -                     | -                     |

| 4     | 4                                        | 4     | 4     | 4       | 6      | VSS                | -                             | -                     | -                     | -                     | -                     | -                     | -                     | -                     |

| _     | -                                        | -     | 41    | 51      | 53     | NC                 | -                             | -                     | -                     | -                     | -                     | -                     | -                     | -                     |

| 5     | 5                                        | 5     | 5     | 5       | 7      | VDDL               | -                             | -                     | -                     | -                     | -                     | -                     | -                     | -                     |

| 1     | 1                                        | 1     | 1     | 1       | 3      | XT0                | -                             | PI00                  | -                     | -                     | -                     | -                     | -                     | -                     |

| 2     | 2                                        | 2     | 2     | 2       | 4      | XT1                | -                             | PI01                  | -                     | -                     | -                     | -                     | -                     | -                     |

| 6     | 6                                        | 6     | 6     | 6       | 8      | RESET_N            | -                             | -                     | -                     | -                     | -                     | -                     | -                     | -                     |

| 7     | 7                                        | 7     | 7     | 7       | 9      | TEST1_N            | -                             | -                     | -                     | -                     | -                     | -                     | -                     | -                     |

| 8     | 8                                        | 8     | 8     | 8       | 10     | P01/TEST0          |                               | -                     | -                     | -                     | -                     | -                     | -                     | -                     |

| 9     | 9                                        | 11    | 14    | 19      | 21     | P02                | -                             | EXI0                  | SIN0                  | RXD0                  | SCLU0                 | FTO0                  | -                     | LCKO                  |

| 10    | 10                                       | 12    | 15    | 20      | 22     | P03                | •                             | EXI1<br>AIN11         | SOUT0                 | TXD0                  | SDAU0                 | FTO0N                 | -                     | HCKO*1                |

| 16    | 17                                       | 21    | 25    | 30      | 32     | P04                | -                             | EXI2<br>COM0          | SCLK0                 | -                     | SCLU0                 | -                     | TMO0                  | -                     |

| 17    | 18                                       | 22    | 26    | 31      | 33     | P05                | -                             | COM1                  | SIN2*3                | -                     | -                     | -                     | -                     | -                     |

| 18    | 19                                       | 23    | 27    | 32      | 34     | P06                | -                             | COM2                  | SOUT2*3               | -                     | SDAM0                 | -                     | -                     | -                     |

| 19    | 20                                       | 24    | 28    | 33      | 35     | P07                | -                             | COM3<br>SEG0          | SCLK2*3               | RXD0                  | SCLM0                 | -                     | -                     | -                     |

| 20    | 21                                       | 25    | 29    | 34      | 36     | P10                | -                             | COM4<br>SEG1          | -                     | TXD0                  | -                     | -                     | -                     | -                     |

| 21    | 22                                       | 26    | 30    | 35      | 37     | P11                | •                             | EXI1<br>COM5<br>SEG2  | SCLK0                 | -                     | -                     | -                     | -                     | -                     |

| 22    | 23                                       | 27    | 31    | 36      | 38     | P12                | -                             | EXI6<br>COM6<br>SEG3  | SIN0                  | RXD0                  | -                     | -                     | TMO4                  | -                     |

| 23    | 24                                       | 28    | 32    | 37      | 39     | P13                | •                             | EXI7<br>COM7<br>SEG4  | SOUT0                 | TXD0                  | -                     | -                     | TMO1                  | ТМО3                  |

| 25    | 27                                       | 35    | 45    | 57      | 59     | P14                | -                             | EXI2<br>SEG22         | SDIF0                 | -                     | -                     | -                     | -                     | ERSI*2                |

| 26    | 28                                       | 36    | 46    | 58      | 60     | P15                | -                             | SEG23                 | SSNF0                 | -                     | SDAU0                 | -                     | -                     | ERCSB*2               |

| 27    | 29                                       | 37    | 47    | 59      | 61     | P16                | -                             | SEG24                 | SCLK1                 | SDOF0*2               | SCLU0                 | -                     | TMO5 <sup>*3</sup>    | ERSO*2                |

| 28    | 30                                       | 38    | 48    | 60      | 62     | P17                | -                             | EXI3<br>SEG25<br>AIN0 | -                     | RXD0                  | -                     | FTO1                  | -                     | -                     |

| 29    | 31                                       | 39    | 49    | 61      | 63     | P20                | •                             | SEG26<br>AIN1         | -                     | TXD0                  | -                     | FTO1N                 | -                     | ТВСО                  |

| 30    | 32                                       | 40    | 50    | 62      | 64     | P21                | -                             | EXI4<br>SEG27<br>AIN2 | SIN1                  | RXD1                  | -                     | FTO2                  | -                     | LCKO                  |

| 31    | 33                                       | 41    | 51    | 63      | 65     | P22                | •                             | AIN3<br>SEG28         | SOUT1                 | TXD1                  | SDAM0                 | FTO2N                 | -                     | HCKO*1                |

| 32    | 34                                       | 42    | 52    | 64      | 66     | P23                | -                             | EXI5<br>SEG29<br>VREF | SCLK1                 | -                     | SCLM0                 | -                     | TMO2                  | -                     |

| 33    | 35                                       | 43    | 53    | 65      | 67     | P24                | -                             | SEG30<br>AIN4         | SIN1                  | RXD1                  | -                     | -                     | -                     | -                     |

| 34    | 36                                       | 44    | 54    | 66      | 68     | P25                | •                             | SEG31<br>AIN5         | SOUT1                 | TXD1                  | -                     | -                     | -                     | -                     |

| 35    | 37                                       | 45    | 55    | 67      | 69     | P26                | -                             | EXI6<br>SEG32<br>AIN6 | -                     | RXD1                  | SDAU0                 | FTO3                  | -                     | -                     |

<sup>\*1:</sup> Assign each function; HCKO to only one LSI pin.

<sup>\*2:</sup> No assignment to ML62Q2747/ML62Q2746/ML62Q2745/ML62Q2737/ML62Q2736/ML62Q2735/ M62Q2727/ML62Q2726/ML62Q2725.

<sup>\*3:</sup> No assignment to ML62Q2723/ML62Q2713/ML62Q2703/ML62Q2722/ML62Q2712/ML62Q2702.

# LAPIS Technology Co., Ltd.

ML62Q2700 Group User's Manual Chapter 1 Overview

|       | Table 1-3 ML62Q2700 Group Pin List (2/3) |          |          |          |          |                    |                               |                       |                       |                       |                       |                       |                       |                           |

|-------|------------------------------------------|----------|----------|----------|----------|--------------------|-------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|---------------------------|

|       |                                          | Pin      | No.      |          |          |                    |                               | 1 <sup>st</sup> func. | 2 <sup>nd</sup> func. | 3 <sup>rd</sup> func. | 4 <sup>th</sup> func. | 5 <sup>th</sup> func. | 6 <sup>th</sup> func. | 7 <sup>th</sup> func.     |

| 48Pin | 52Pin                                    | 64Pin    | 80Pin    | TQFP100  | QFP100   | LSI<br>Pin<br>name | Career<br>frequency<br>output | EXI/<br>LCD/<br>ADC   | SSIO                  | UART                  | I <sup>2</sup> C      | FTM                   | Timer/<br>SOUND       | CLKOUT/<br>LTBC/<br>SFMIF |

| 36    | 38                                       | 46       | 56       | 68       | 70       | P27                | •                             | EXI7<br>SEG33<br>AIN7 | 36                    | 38                    | 46                    | 56                    | 68                    | 70                        |

| 37    | 41                                       | 51       | 67       | 84       | 86       | P30                | -                             | SEG49                 | ESIN1*3               | -                     | -                     | -                     | -                     | -                         |

| 38    | 42                                       | 52       | 68       | 85       | 87       | P31                | -                             | EXI1<br>SEG50         | ESOUT1*3              | -                     | -                     | -                     | -                     | ТВСО                      |

| 39    | 43                                       | 53       | 69       | 86       | 88       | P32                | -                             | SEG51                 | ESCLK1*3              | RXD1                  | -                     | -                     | -                     | -                         |

| 40    | 44                                       | 54       | 70       | 87       | 89       | P33                | •                             | EXI2<br>SEG52         | -                     | TXD1                  | -                     | -                     | ТМО3                  | -                         |

| -     | -                                        | 49       | 65       | 82       | 84       | P40                | -                             | SEG47                 | -                     | ETXD2*3               | -                     | -                     | -                     | -                         |

| -     | 40                                       | 50       | 66       | 83<br>96 | 85       | P41                | -                             | EXI0<br>SEG48         | -                     | ERXD2*3               | -                     | -                     | -                     | -                         |

| -     | -                                        | 63       | 79       |          | 98       | P42                | -                             | SEG61<br>EXI7         | -                     | ETXD0*3               | -                     | -                     | -                     | -                         |

| 48    | 52                                       | 64       | 80       | 100      | 2        | P43                | -                             | AIN10                 | -                     | -                     | -                     | -                     | -                     | TBCO                      |

| -     | -                                        | 9        | 12       | 17       | 19       | P44                | -                             | EXI2                  | -                     | ERXD1*3               | -                     | FTO3N                 | -                     | -                         |

| -     | -                                        | 10       | 13       | 18       | 20       | P45                | -                             | EXI3                  | -                     | ETXD1*3               | -                     | -                     | -                     | -                         |

| -     | -                                        | 13       | 16       | 21       | 23       | P46                | -                             | EXI4                  | -                     | -                     | SDAU0                 | FTO1N                 | -                     | -                         |

| -     | 11                                       | 14       | 17       | 22       | 24       | P47                | -                             | EXI5                  | SCLK0                 | -                     | SCLU0                 | FTO1                  | -                     | -                         |

| 24    | 25                                       | 29       | 33       | 38       | 40       | P50                | -                             | EXI8<br>SEG5          | SCKF0                 | -                     | -                     | -                     | -                     | ERSCK                     |

| -     | 26                                       | 30       | 34       | 39       | 41       | P51                | -                             | EXI3<br>SEG6<br>EXI4  | SDOF0                 | -                     | -                     | -                     | -                     | ERSO                      |

| -     | -                                        | 31       | 35       | 40       | 42       | P52                | -                             | SEG7<br>EXI5          | SDIF0                 | ERXD1*3               | -                     | -                     | -                     | ERSI                      |

| -     | -                                        | 32       | 36       | 41       | 43       | P53                | -                             | SEG8<br>EXI0          | SSNF0                 | ETXD1*3               | -                     | -                     | -                     | ERCSB                     |

| -     | -                                        | 33       | 43       | 55       | 57       | P54                | -                             | SEG20<br>EXI1         | SCKF0                 | RXD2*3                | -                     | FTO7*3                | TMOX                  | -                         |

| -     | -                                        | 34       | 44       | 56       | 58       | P55                | -                             | SEG21<br>SEG34        | SDOF0                 | TXD2*3                | -                     | FTO7N*3               | -                     | -                         |

| -     | 39                                       | 47       | 57       | 69       | 71       | P56                | -                             | AIN12*4<br>SEG35      | SIN2*3                | RXD2*3                | -                     | -                     | -                     | -                         |

| -     | -                                        | 48       | 58       | 70       | 72       | P57                | -                             | AIN13*4               | SOUT2*3               | TXD2*3                | -                     | -                     | -                     | -                         |

| 41    | 45                                       | 55       | 71       | 88       | 90       | P60                | -                             | SEG53                 | ESIN2*3               | -                     | SCLM1                 | -                     | -                     | -                         |

| 42    | 46                                       | 56       | 72       | 89       | 91       | P61                | -                             | SEG54                 | ESOUT2*3              | -                     | SDAM1                 | -                     | SOP                   | -                         |

| 43    | 47                                       | 57       | 73       | 90       | 92       | P62                | -                             | SEG55<br>EXI4         | ESCK2*3               | -                     | -                     | FTO4N                 | SON                   | -                         |

| 44    | 48                                       | 58       | 74       | 91       | 93       | P63                | -                             | SEG56<br>EXI9         | -                     | -                     | -                     | FTO4                  | -                     | -                         |

| 45    | 49                                       | 59       | 75       | 92       | 94       | P64                | -                             | SEG57<br>EXI5         | ESIN0*3               | ERXD0*3               | -                     | FTO5                  | -                     | -                         |

| 46    | 50                                       | 60       | 76       | 93       | 95       | P65                | -                             | SEG58<br>AIN8         | ESOUT0*3              | ETXD0*3               | -                     | FTO5N                 | -                     | -                         |

| 47    | 51                                       | 61       | 77       | 94       | 96       | P66                | -                             | SEG59<br>AIN9         | ESCLK0*3              | -                     | -                     | FTO6*3                | -                     | -                         |

| -     | -                                        | 62       | 78       | 95       | 97       | P67                | -                             | EXI6<br>SEG60         | -                     | ERXD0*3               | -                     | FTO6N*3               | -                     | -                         |

| -     | -                                        | 20       | 24       | 29       | 31       | P70                | -                             | EXI0                  | -                     | -                     | -                     | -                     | TMO6*3                | -                         |

| 15    | 16                                       | 19       | 23       | 28       | 30       | VL3                | -                             | -                     | -                     | -                     |                       |                       | -                     | -                         |

| 14    | 15                                       | 18       | 22       | 27       | 29       | VL2                | -                             | -                     | -                     | -                     |                       |                       | -                     | -                         |

| 13    | 14                                       | 17       | 21       | 26       | 28<br>27 | VL1<br>C2          | -                             | -                     | -                     | -                     | -                     | -                     | -                     | -                         |

| 11    | 13<br>12                                 | 16<br>15 | 20<br>19 | 25<br>24 | 26       | C2<br>C1           | -                             | -                     | -                     | -                     | -                     | -                     | -                     | -                         |

| -     | -                                        | -        | 18       | 23       | 25       | P76                | -                             | EXI10                 | -                     | -                     | -                     | -                     | -                     | -                         |

| -     | -                                        | -        | -        | 99       | 1        | P77                | -                             | SEG64                 | -                     | -                     | -                     | -                     | -                     | -                         |

|       |                                          |          |          |          |          |                    |                               |                       |                       |                       |                       |                       |                       |                           |

FEUL 62Q 27001-17

<sup>\*3:</sup> No assignment to ML62Q2723/ML62Q2713/ML62Q2703/ML62Q2722/ML62Q2712/ML62Q2702.

\*4: No assignment to ML62Q2727/ML62Q2726/ML62Q2725/ML62Q2723/ML62Q2713/ML62Q2703/ML62Q2722/ ML62Q2712/ML62Q2702.

Table 1-3 ML62Q2700 Group Pin List (3/3)

|       | Pin No. |       |       |         |        | 1 <sup>st</sup> func. | L62Q2700 G<br>2 <sup>nd</sup> func. | 3 <sup>rd</sup> func.   | 4 <sup>th</sup> func. | 5 <sup>th</sup> func. | 6 <sup>th</sup> func. | 7 <sup>th</sup> func. |       |                 |

|-------|---------|-------|-------|---------|--------|-----------------------|-------------------------------------|-------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-------|-----------------|

| 48Pin | 52Pin   | 64Pin | 80Pin | TQFP100 | QFP100 | LSI<br>Pin<br>name    | Career<br>frequency<br>output       | EXI/<br>LCD/<br>ADC     | SSIO                  | UART                  | I <sup>2</sup> C      | FTM                   | Timer | CLKOUT/<br>LTBC |

| -     | -       | -     | 9     | 9       | 11     | P80                   | -                                   | EXI6                    | ESIN1*3               | ERXD1*3               | -                     | -                     | -     | -               |

| -     | -       | -     | 10    | 10      | 12     | P81                   | -                                   | EXI7                    | ESOUT1*3              | ETXD1*3               | -                     | -                     | -     | -               |

| -     | -       | -     | 11    | 11      | 13     | P82                   | -                                   | -                       | ESCLK1*3              | -                     | -                     | -                     | -     | -               |

| -     | -       | -     | ı     | 12      | 14     | P83                   | -                                   | -                       | -                     | ERXD2*3               | -                     | -                     | ı     | -               |

| -     | •       | •     | ı     | 13      | 15     | P84                   | -                                   | -                       | ı                     | ETXD2*3               | -                     | -                     | ı     | -               |

| -     | -       | -     | -     | 14      | 16     | P85                   | -                                   | -                       | -                     | -                     | -                     | -                     | -     | -               |

| -     | -       | -     | -     | 15      | 17     | P86                   | -                                   | -                       | -                     | -                     | -                     | FTO7*3                | -     | -               |

| -     | -       | -     | -     | 16      | 18     | P87                   | -                                   | -                       | -                     | -                     | -                     | FTO7N*3               | -     | -               |

| -     | -       | -     | -     | 42      | 44     | P90                   | -                                   | SEG9                    | -                     | -                     | -                     | -                     | -     | -               |

| -     | -       | -     | -     | 43      | 45     | P91                   | -                                   | SEG10                   | -                     | -                     | -                     | -                     | -     | -               |

| -     | -       | -     | -     | 44      | 46     | P92                   | -                                   | SEG11                   | -                     | -                     | -                     | -                     | -     | -               |

| -     | -       | -     | 37    | 45      | 47     | P93                   | -                                   | SEG12                   | ESIN1*3               | ERXD1*3               | -                     | FTO6*3                | -     | -               |

| -     | -       | -     | 38    | 46      | 48     | P94                   | -                                   | SEG13                   | ESOUT1*3              | ETXD1*3               | -                     | FTO6N*3               | -     | -               |

| -     | -       | -     | 39    | 47      | 49     | P95                   | -                                   | SEG14                   | ESCLK1*3              | -                     | -                     | -                     | -     | -               |

| -     | -       | -     | 40    | 48      | 50     | P96                   | -                                   | SEG15                   | -                     | -                     | -                     | -                     | -     | -               |

| -     | -       | -     | -     | 49      | 51     | P97                   | -                                   | SEG16                   | -                     | -                     | -                     | -                     | -     | -               |

| -     | -       | -     | -     | 50      | 52     | PA0                   | -                                   | SEG17                   | -                     | -                     | -                     | -                     | -     | -               |

| -     | -       | -     | -     | 53      | 55     | PA1                   | -                                   | SEG18                   | -                     | -                     | -                     | -                     | -     | -               |

| -     | -       | -     | -     | 54      | 56     | PA2                   | -                                   | SEG19                   | -                     | -                     | -                     | -                     | -     | -               |

| -     | -       | -     | 59    | 71      | 73     | PA3                   | -                                   | EXI11<br>SEG36<br>AIN14 | SCLK2*3               | -                     | -                     | FTO7*3                | -     | -               |

| -     | -       | -     | 60    | 72      | 74     | PA4                   | -                                   | SEG37<br>AIN15          | -                     | -                     | -                     | FTO7N*3               | -     | -               |

| -     | -       | -     | -     | 73      | 75     | PA5                   | -                                   | SEG38                   | -                     | -                     | -                     | -                     | -     | -               |

| -     | -       | -     | -     | 74      | 76     | PA6                   | -                                   | SEG39                   | -                     | -                     | -                     | -                     | -     | -               |

| -     | -       | -     | -     | 75      | 77     | PA7                   | -                                   | SEG40                   | -                     | -                     | -                     | -                     | -     | -               |

| -     | -       | -     | -     | 76      | 78     | PB0                   | -                                   | SEG41                   | -                     | -                     | -                     | -                     | -     | -               |

| -     | -       | -     | -     | 77      | 79     | PB1                   | -                                   | SEG42                   | -                     | -                     | -                     | -                     | -     | -               |

| -     | -       | -     | 61    | 78      | 80     | PB2                   | -                                   | SEG43                   | ESIN2*3               | ERXD2*3               | -                     | -                     | -     | -               |

| -     | -       | -     | 62    | 79      | 81     | PB3                   | -                                   | SEG44                   | ESOUT2*3              | ETXD2*3               | -                     | -                     | -     | -               |

| -     | -       | -     | 63    | 80      | 82     | PB4                   | -                                   | SEG45                   | ESCLK2*3              | -                     | -                     | -                     | -     | -               |

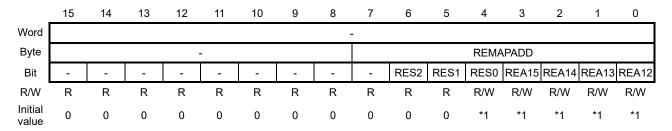

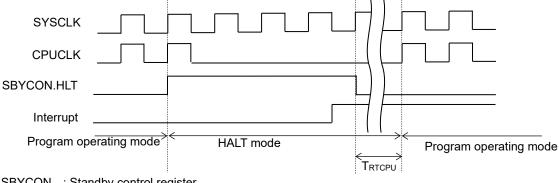

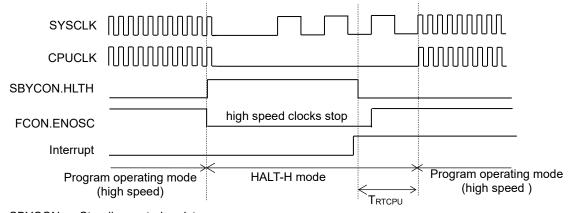

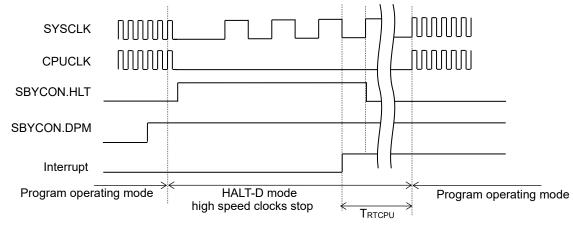

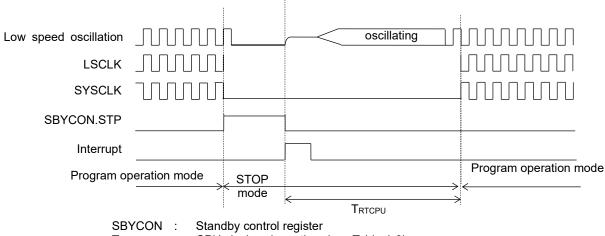

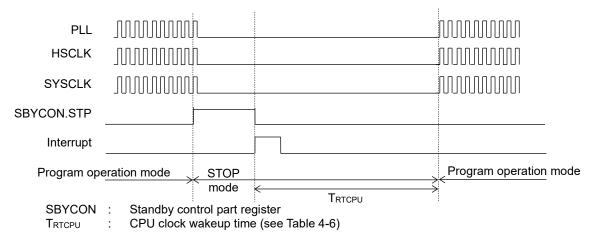

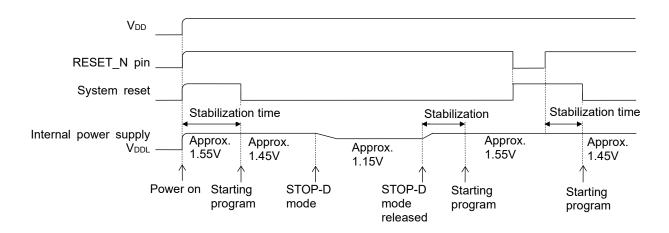

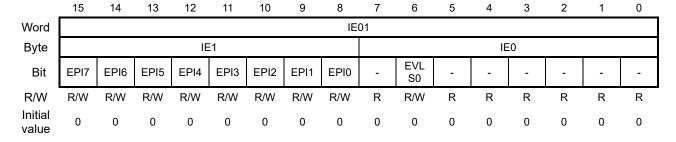

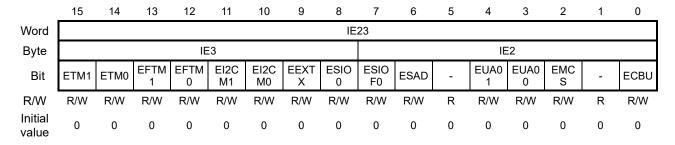

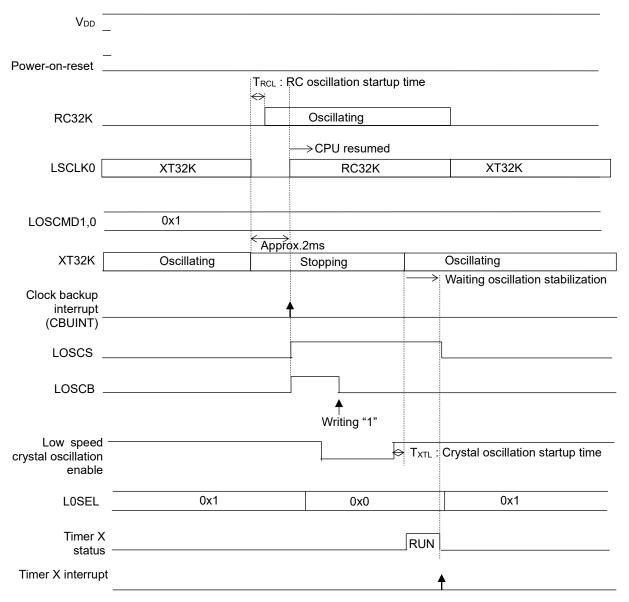

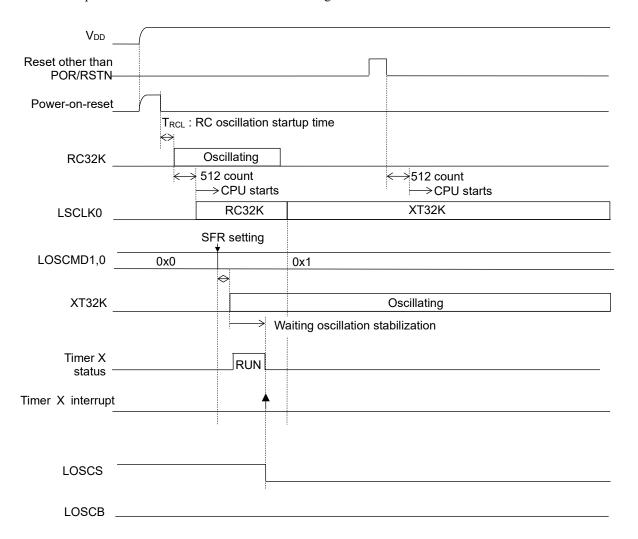

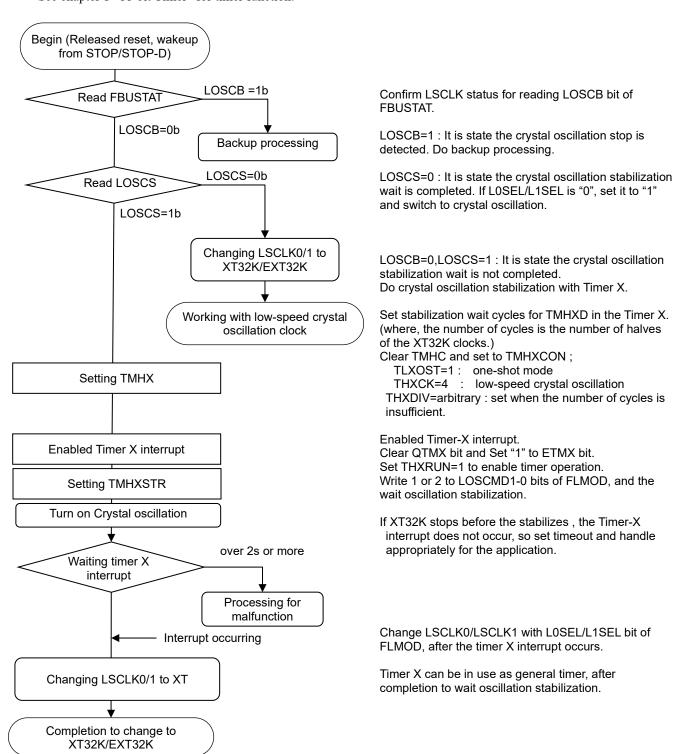

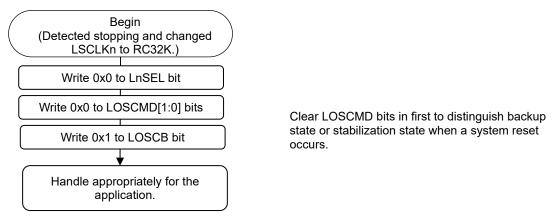

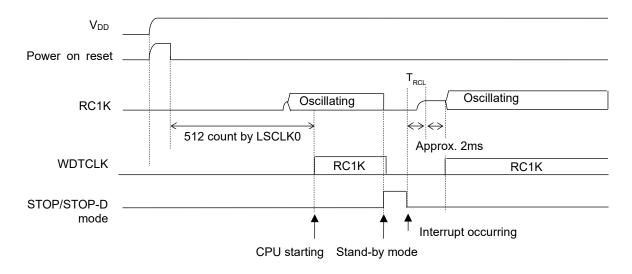

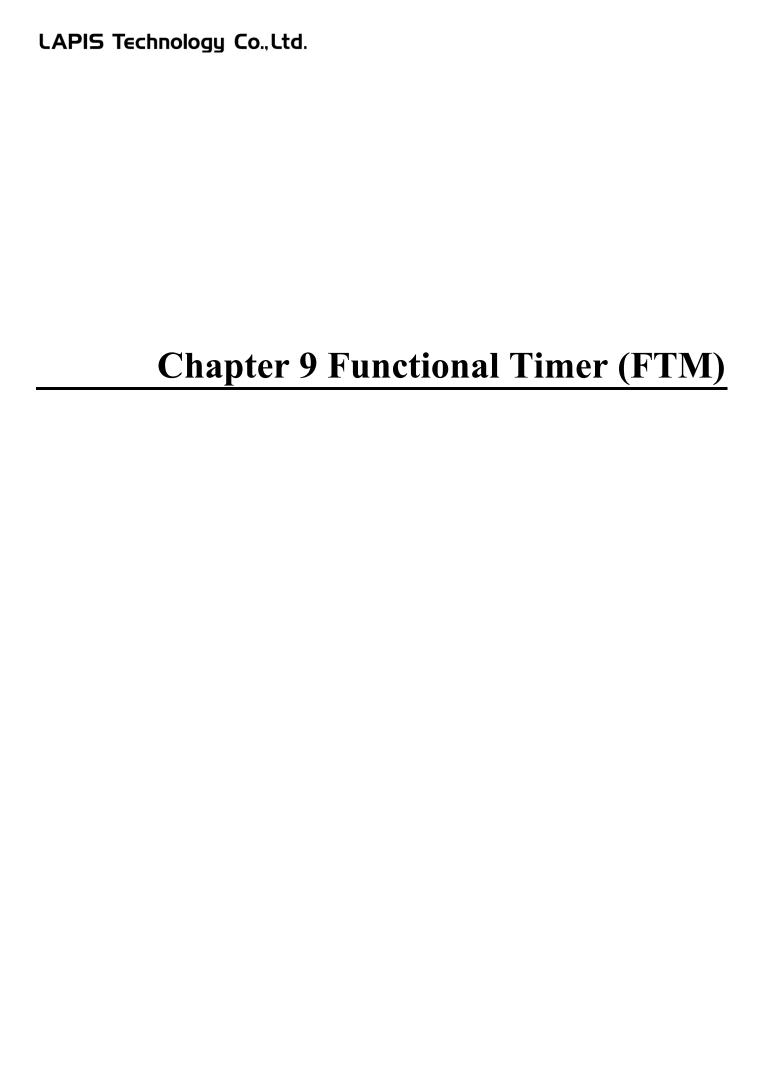

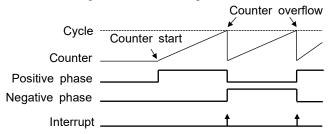

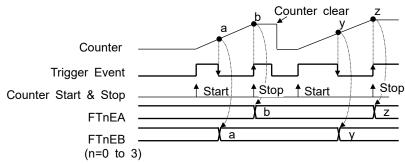

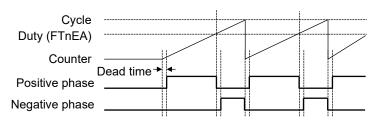

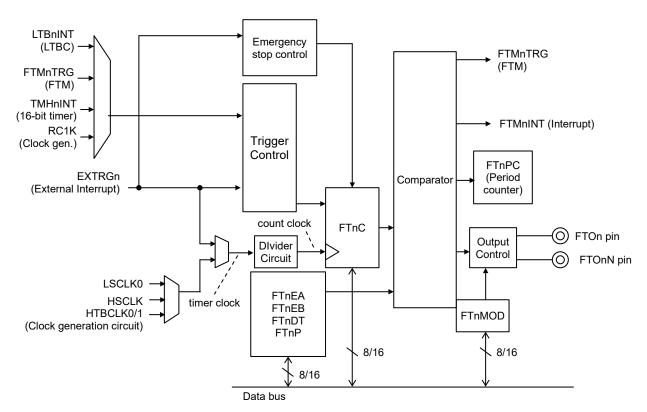

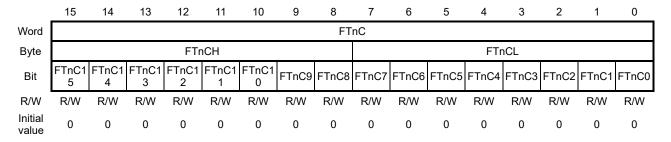

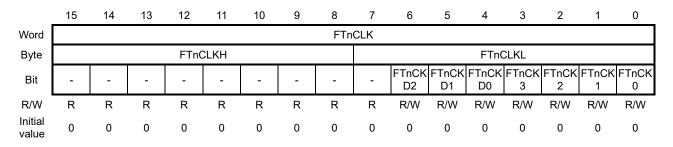

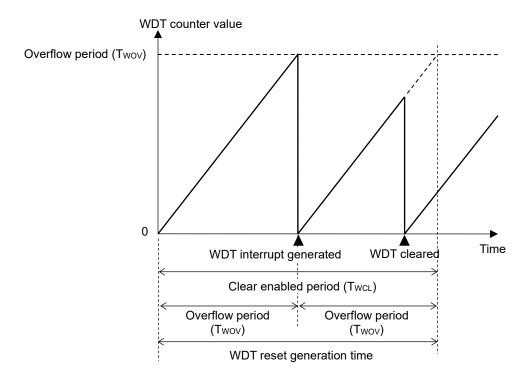

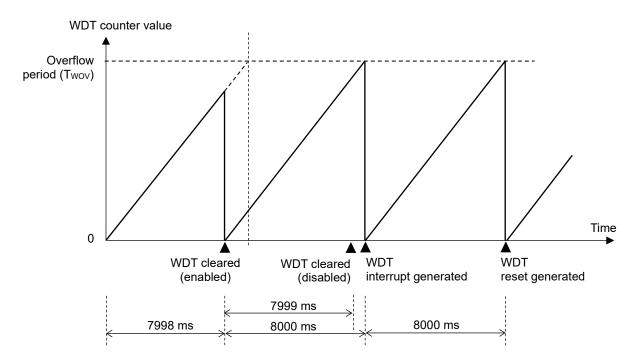

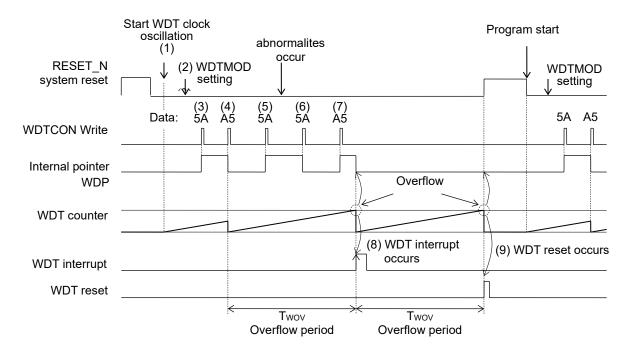

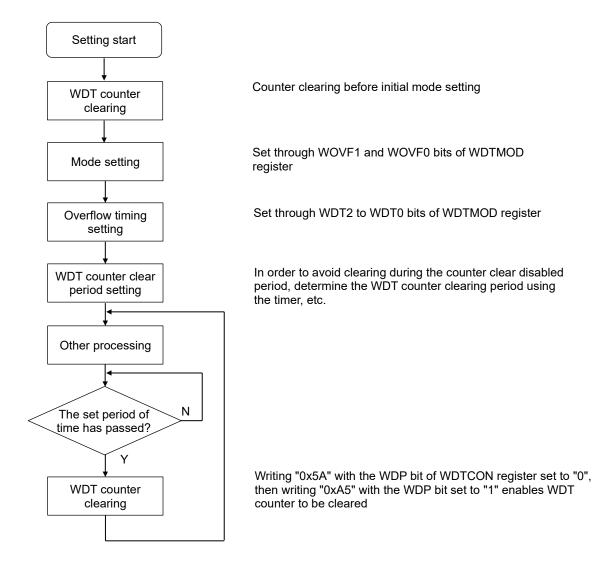

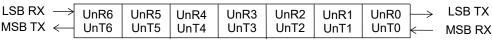

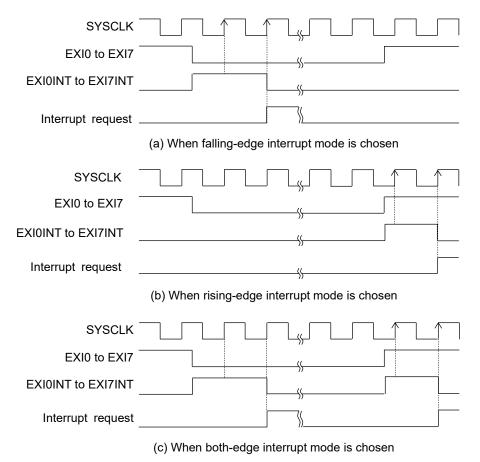

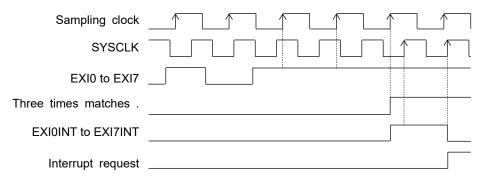

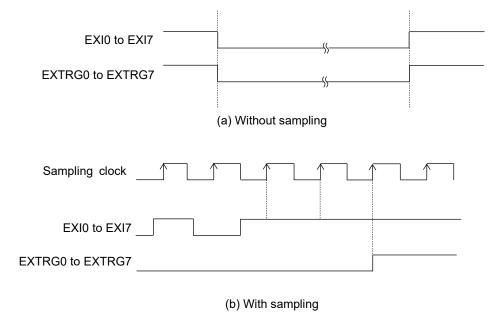

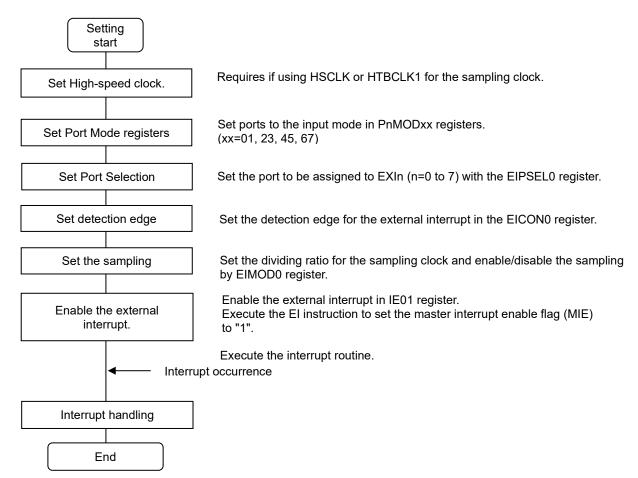

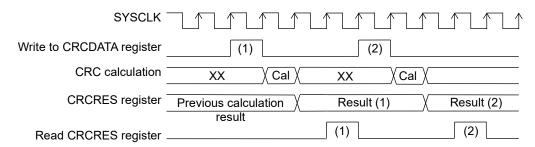

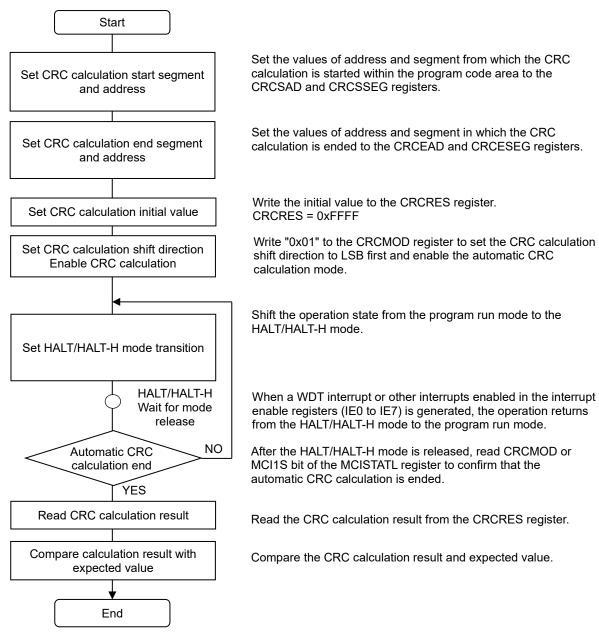

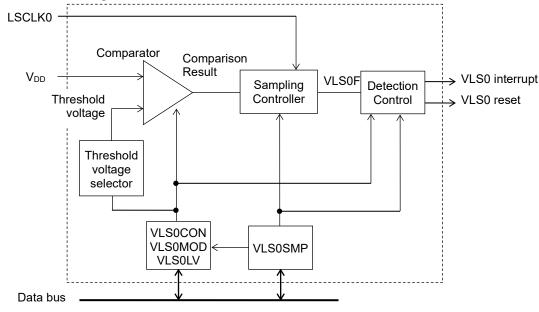

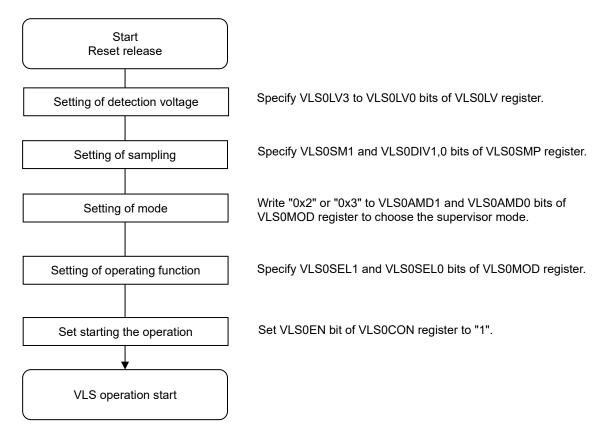

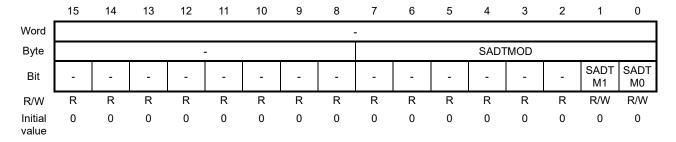

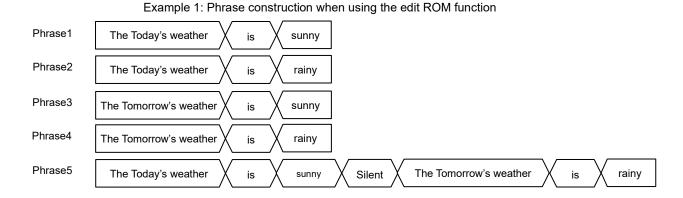

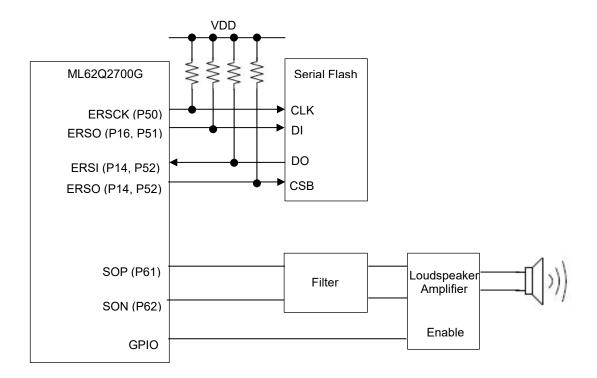

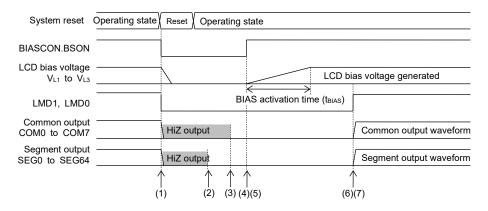

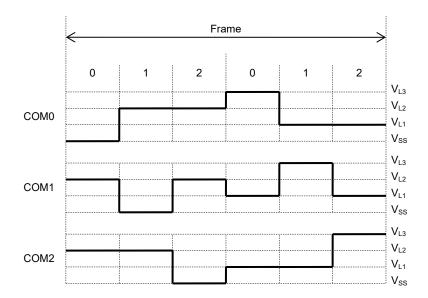

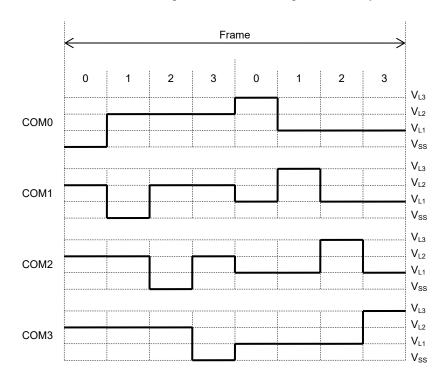

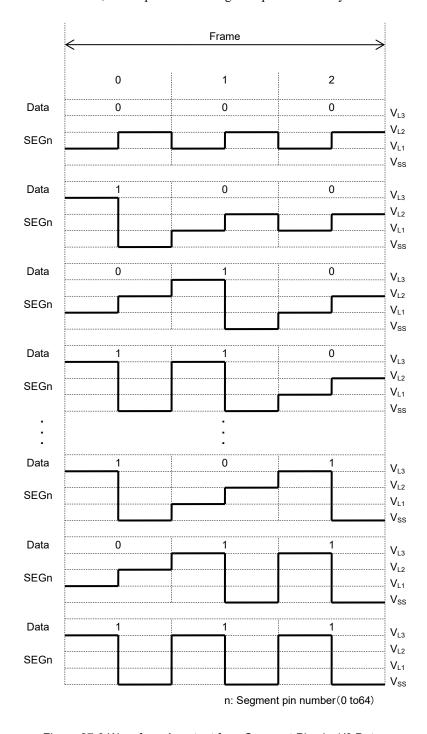

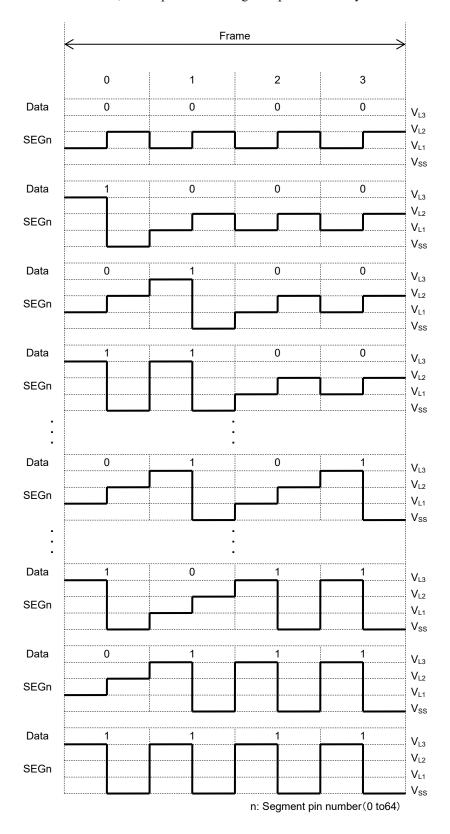

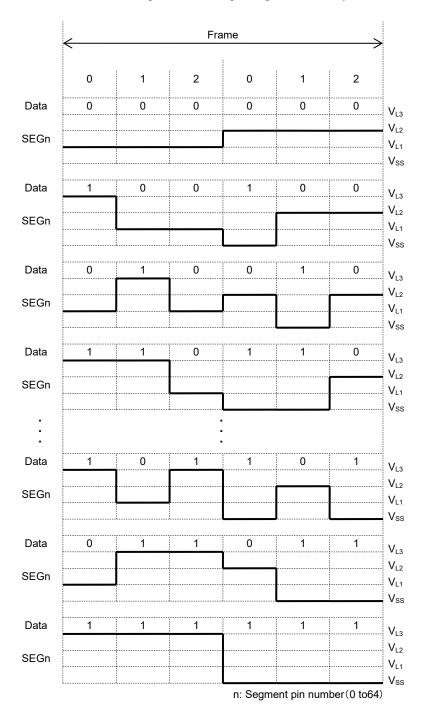

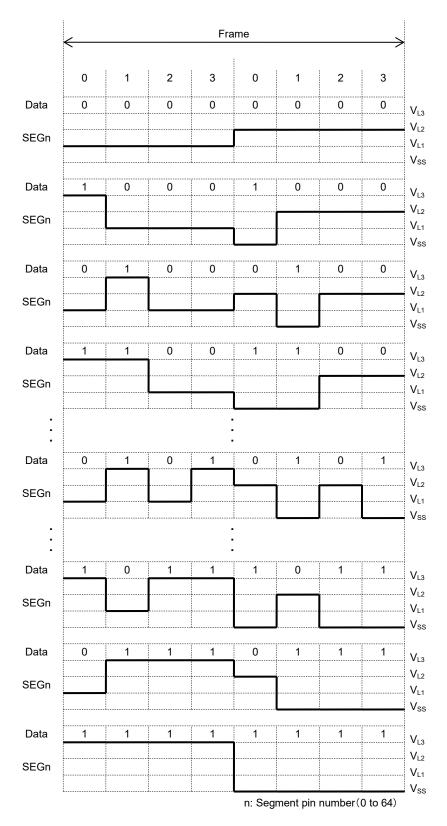

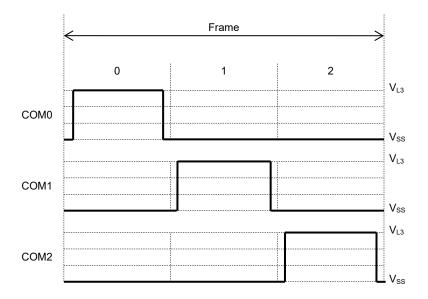

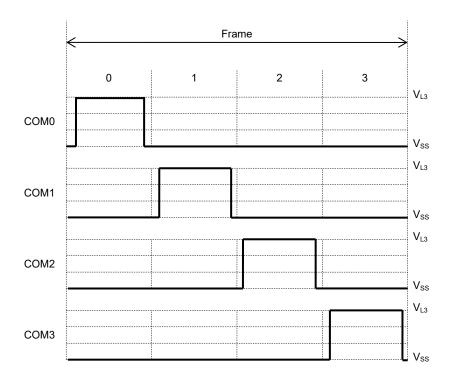

| -     | -       | -     | 64    | 81      | 83     | PB5                   | -                                   | SEG46                   | -                     | ERXD2*3               | -                     | -                     | -     | -               |