Dear customer

ROHM Co., Ltd. ("ROHM"), on the 1st day of April, 2024, has absorbed into merger with 100%-owned subsidiary of LAPIS Technology Co., Ltd.

Therefore, all references to "LAPIS Technology Co., Ltd.", "LAPIS Technology" and/or "LAPIS" in this document shall be replaced with "ROHM Co., Ltd." Furthermore, there are no changes to the documents relating to our products other than the company name, the company trademark, logo, etc.

Thank you for your understanding.

ROHM Co., Ltd. April 1, 2024

FEUL630Q464-03

# ML630Q464/Q466 User's Manual

Issue Date: Dec.15, 2023

#### Notes

- 1) When using LAPIS Technology Products, refer to the latest product information and ensure that usage conditions (absolute maximum ratings<sup>\*1</sup>, recommended operating conditions, etc.) are within the ranges specified. LAPIS Technology disclaims any and all liability for any malfunctions, failure or accident arising out of or in connection with the use of LAPIS Technology Products outside of such usage conditions specified ranges, or without observing precautions. Even if it is used within such usage conditions specified ranges, semiconductors can break down and malfunction due to various factors. Therefore, in order to prevent personal injury, fire or the other damage from break down or malfunction of LAPIS Technology Products, please take safety at your own risk measures such as complying with the derating characteristics, implementing redundant and fire prevention designs, and utilizing backups and fail-safe procedures.

- \*1: Absolute maximum ratings: a limit value that must not be exceeded even momentarily.

- 2) The Products specified in this document are not designed to be radiation tolerant.

- 3) Descriptions of circuits, software and other related information in this document are provided only to illustrate the standard operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. And the peripheral conditions must be taken into account when designing circuits for mass production. LAPIS Technology disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, and other related information.

- 4) No license, expressly or implied, is granted hereby under any intellectual property rights or other rights of LAPIS Technology or any third party with respect to LAPIS Technology Products or the information contained in this document (including but not limited to, the Product data, drawings, charts, programs, algorithms, and application examples, etc.). Therefore, LAPIS Technology shall have no responsibility whatsoever for any dispute, concerning such rights owned by third parties, arising out of the use of such technical information.

- 5) LAPIS Technology intends our Products to be used in a way indicated in this document. Please be sure to contact a ROHM sales office if you consider the use of our Products in different way from original use indicated in this document. For use of our Products in medical systems, please be sure to contact a LAPIS Technology representative and must obtain written agreement. Do not use our Products in applications which may directly cause injuries to human life, and which require extremely high reliability, such as aerospace equipment, nuclear power control systems, and submarine repeaters, etc. LAPIS Technology disclaims any and all liability for any losses and damages incurred by you or third parties arising by using the Product for purposes not intended by us without our prior written consent.

- 6) All information contained in this document is subject to change for the purpose of improvement, etc. without any prior notice. Before purchasing or using LAPIS Technology Products, please confirm the latest information with a ROHM sales office. LAPIS Technology has used reasonable care to ensure the accuracy of the information contained in this document, however, LAPIS Technology shall have no responsibility for any damages, expenses or losses arising from inaccuracy or errors of such information.

- Please use the Products in accordance with any applicable environmental laws and regulations, such as the RoHS Directive. LAPIS Technology shall have no responsibility for any damages or losses resulting non-compliance with any applicable laws or regulations.

- 8) When providing our Products and technologies contained in this document to other countries, you must abide by the procedures and provisions stipulated in all applicable export laws and regulations, including without limitation the US Export Administration Regulations and the Foreign Exchange and Foreign Trade Act.

- 9) Please contact a ROHM sales office if you have any questions regarding the information contained in this document or LAPIS Technology's Products.

- 10) This document, in part or in whole, may not be reprinted or reproduced without prior consent of LAPIS Technology.

(Note) "LAPIS Technology" as used in this document means LAPIS Technology Co., Ltd.

Copyright 2020 - 2023 LAPIS Technology Co., Ltd.

### LAPIS Technology Co., Ltd.

2-4-8 Shinyokohama, Kouhoku-ku, Yokohama 222-8575, Japan https://www.lapis-tech.com/en/

LTSZ08023 • 01 • 002

### Notes for product usage

Notes on this page are applicable to the all LAPIS Technology microcontroller products. For individual notes on each LAPIS Technology microcontroller product, refer to [Note] in the chapters of each user's manual.

The individual notes of each user's manual take priority over those contents in this page if they are different.

#### 1. HANDLING OF UNUSED INPUT PINS

Fix the unused input pins to the power pin or GND to prevent to cause the device performing wrong operation or increasing the current consumption due to noise, etc. If the handlings for the unused pins are described in the chapters, follow the instruction.

#### 2. STATE AT POWER ON

At the power on, the data in the internal registers and output of the ports are undefined until the power supply voltage reaches to the recommended operating condition and "L" level is input to the reset pin. On LAPIS Technology microcontroller products that have the power on reset function, the data in the internal registers and output of the ports are undefined until the power on reset is generated. Be careful to design the application system does not work incorrectly due to the undefined data of internal registers and output of the ports.

#### 3. ACCESS TO UNUSED MEMORY

If reading from unused address area or writing to unused address area of the memory, the operations are not guaranteed.

#### 4. CHARACTERISTICS DIFFERENCE BETWEEN THE PRODUCTS

Electrical characteristics, noise tolerance, noise radiation amount, and the other characteristics are different from each microcontroller product.

When replacing from other product to LAPIS Technology microcontroller products, please evaluate enough the apparatus/system which implemented LAPIS Technology microcontroller products.

#### 5. USE ENVIRONMENT

When using LAPIS Technology microcontroller products in a high humidity environment and an environment where dew condensation, take moisture-proof measures.

# Preface

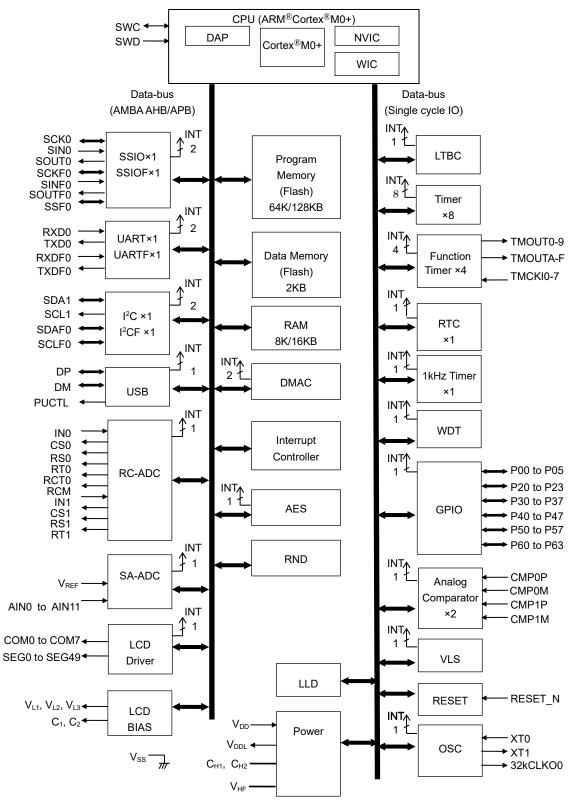

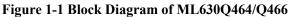

This manual describes the operation of the hardware of the 32-bit microcontroller ML630Q464/Q466.

Please ensure that you refer to the latest versions.

Cortex<sup>TM</sup>-M0+ Technical Reference Manual (DDI0484C)

Cortex<sup>TM</sup>-M0+ Generic User Guide (DUI0662B)

The documents above are published by ARM Limited. Please ensure that you refer to the latest versions.

ARM, Cortex, Thmub are registered trademarks of ARM Limited in the EU and other countries.

| Classification  | Notation                                                                                                                            | Description                                                                                                                                                                                                             |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ♦ Numeric value | xxh, xxH<br>0xnn, 0xnnnn_nnnn<br>xxb<br>0bnn, 0bnnnn_nnnn                                                                           | Indicates a hexadecimal number. x: Any value in the range of 0 to F<br>Indicates a hexadecimal number.<br>Indicates a binary number; "b" may be omitted. x: A value 0 or 1<br>Indicates a binary number.                |

| ◆ Unit          | word, W<br>byte, B<br>nibble, N<br>mega-, M<br>kilo-, K<br>kilo-, k<br>milli-, m<br>micro-, μ<br>nano-, n<br>second, s (lower case) | 1 word = 32 bits<br>1 byte = 8 bits<br>1 nibble = 4 bits<br>$10^{6}$<br>$2^{10} = 1024$<br>$10^{3} = 1000$<br>$10^{-3}$<br>$10^{-6}$<br>$10^{-9}$<br>second                                                             |

| ◆ Terminology   | "H" level, "1" level<br>"L" level, "0" level                                                                                        | Indicates high voltage signal levels $V_{IH}$ and $V_{OH}$ as specified by the electrical characteristics.<br>Indicates low voltage signal levels $V_{IL}$ and $V_{OL}$ as specified by the electrical characteristics. |

# Notation

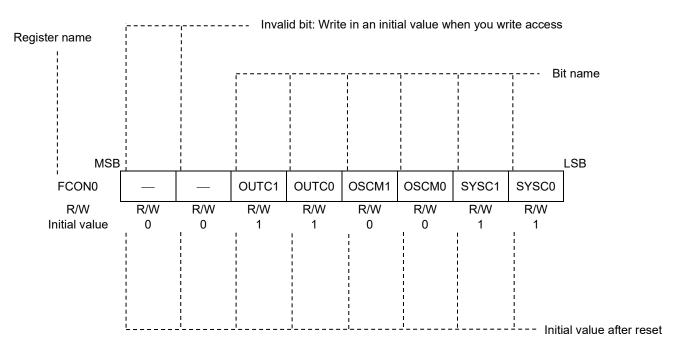

#### ♦ Register description

R/W: Indicates that Read/Write attribute. "R" indicates that data can be read and "W" indicates that data can be written. "R/W" indicates that data can be read or written.

# Contents

# Table of Contents

### Chapter 1

| 1-1          |

|--------------|

| 1-1          |

| 1-5          |

| 1-5          |

| 1 <b>-</b> 6 |

| 1 <b>-</b> 6 |

| 1 <b>-</b> 6 |

| 1-7          |

| 1-7          |

| 1-9          |

| 1-12         |

|              |

# Chapter 2

| 2. CPU                        | 2-1 |

|-------------------------------|-----|

| 2.1. Overview                 | 2-1 |

| 2.1.1. Features               |     |

| 2.2. Description of Registers |     |

| 2.2.1. List of Registers      |     |

# Chapter 3

| 3. Memory Space                                   |     |

|---------------------------------------------------|-----|

| 3.1. General Description                          |     |

| 3.2. Memory Map                                   |     |

| 3.3. Internal Memory                              | 3-6 |

| 3.3.1. Internal Flash ROM                         |     |

| 3.3.2. Work RAM                                   | 3-6 |

| 3.4. Memory Controller Function                   |     |

| 3.4.1 List of Registers                           |     |

| 3.4.2 Remapping Control Register (REMAPCON)       |     |

| 3.4.3 Remapping Base Address Register (REMAPBASE) |     |

| 3.4.4 Boot/Remapping Function                     |     |

| 3.5 Access Response for Memory Space              |     |

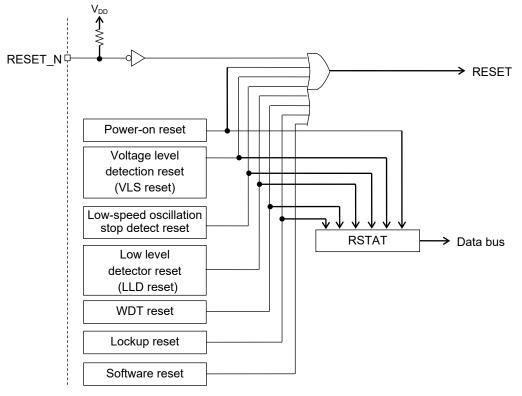

| 4 Reset 1 | Function                                 | 4-1   |

|-----------|------------------------------------------|-------|

|           | erview                                   |       |

|           | Features                                 |       |

| 4.1.2.    | Configuration                            | . 4-1 |

|           | List of Pin                              |       |

| 4.2. De   | scription of Registers                   | . 4-3 |

|           | List of Registers                        |       |

|           | Reset Status Register (RSTAT)            |       |

| 4.2.3.    | LOCKUP reset setting register (LOCKUPEN) | . 4-6 |

|           | scription of Operation                   |       |

| 4.3.1.    | Cause of Reset                           | . 4-7 |

| 4.3.2.    | Operation of System Reset Mode           | . 4-8 |

#### FEUL630Q464

6.3.3.

6.3.4.

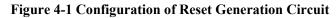

| Chapter        | 5                                                           |               |

|----------------|-------------------------------------------------------------|---------------|

|                | Control Function                                            |               |

| -              | neral Description                                           |               |

| 5.1.1.         | Features                                                    |               |

| 5.1.2.         | Configuration                                               |               |

| 5.2. De        | scription of Registers                                      |               |

| 5.2.1.         | Register Configuration List                                 |               |

| 5.2.2.         | Revision Register (IDR)                                     |               |

| 5.2.3.         | DMA Request Select register (DREQSEL)                       |               |

| 5.2.4.         | BRMP Control Register (BRMPCON)                             |               |

| 5.2.5.         | Standby Control Register (SBYCON)                           |               |

| 5.2.6.         | Power Management Control Register (PMCON)                   |               |

| 5.2.7.         | Clock Control Register (CLKCON)                             |               |

| 5.2.8.         | Reset Control Register (RSTCON)                             |               |

| 5.3. De        | scription of Operation                                      |               |

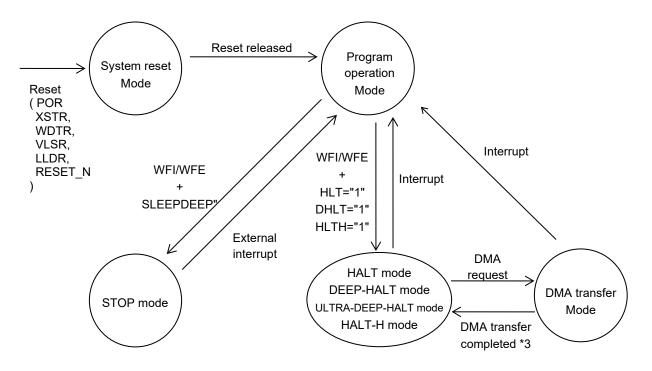

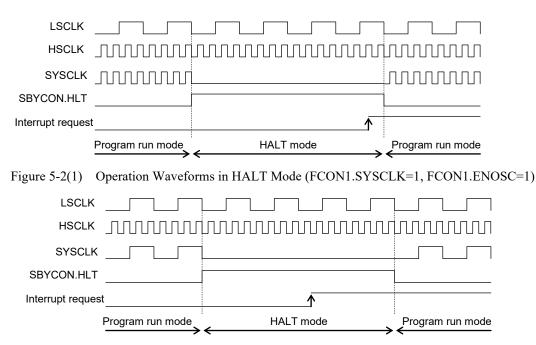

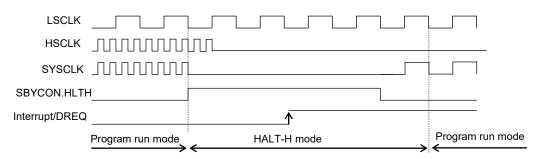

| 5.3.1.         | HALT Mode                                                   |               |

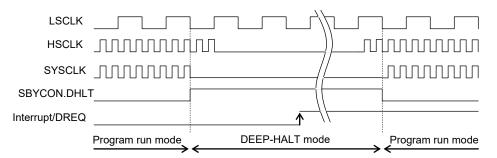

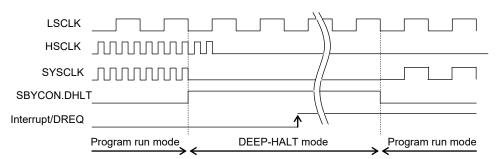

| 5.3.2.         | DEEP-HALT Mode                                              |               |

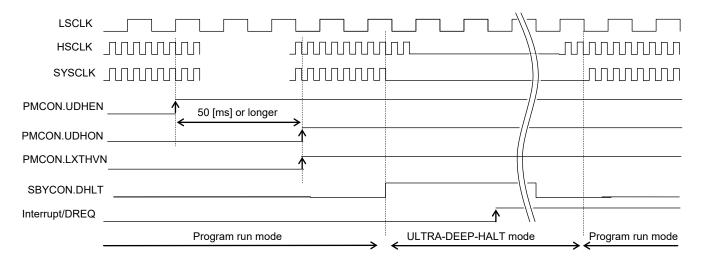

| 5.3.3.         | ULTRA-DEEP-HALT Mode                                        |               |

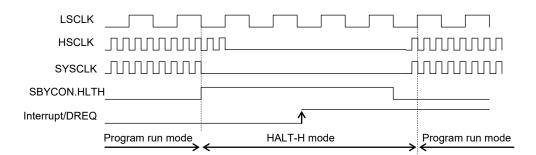

| 5.3.4.         | HALT-H Mode                                                 |               |

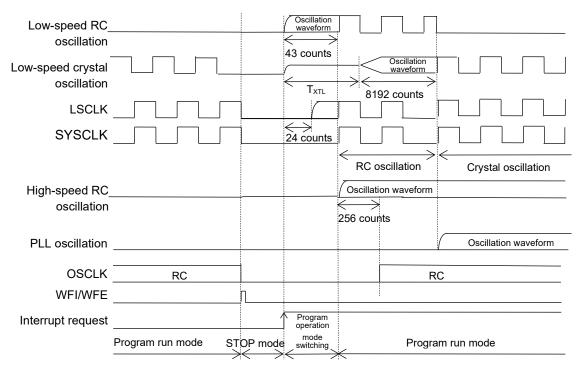

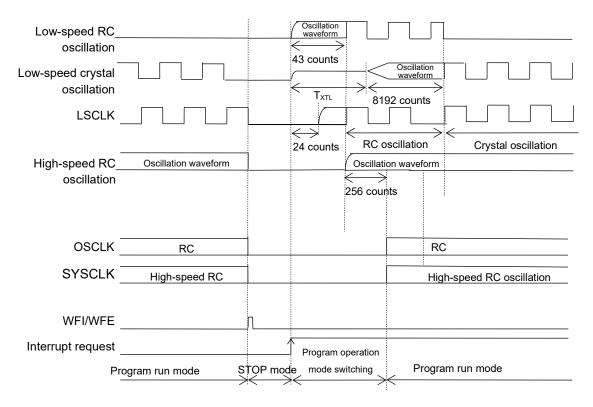

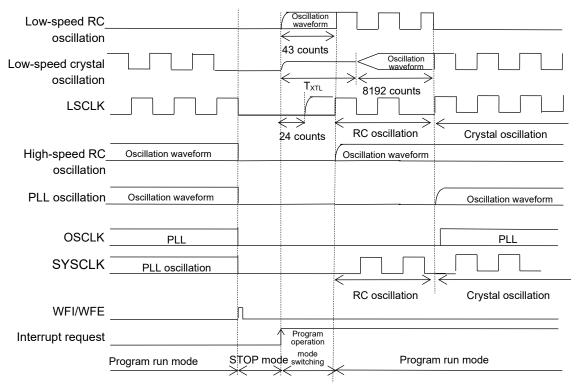

| 5.3.5.         | STOP Mode                                                   |               |

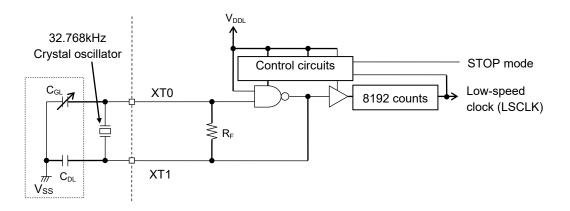

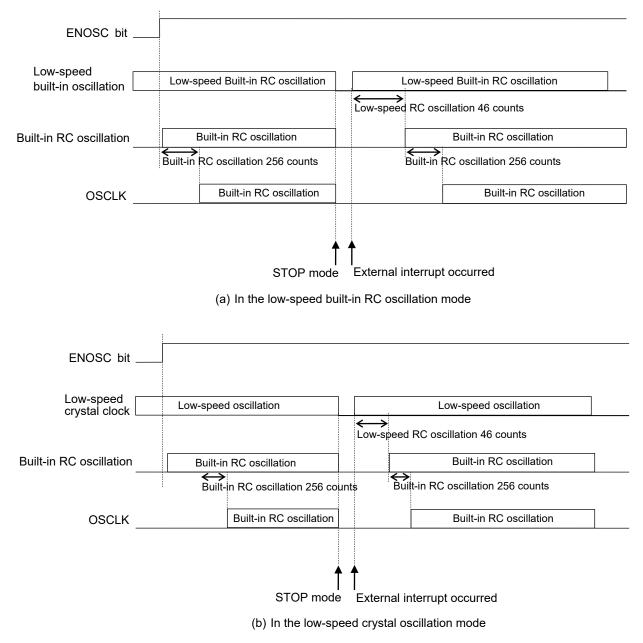

| 5.3.5          | .1. Oscillation Stop and Restart Timing of Low-Speed Clock  |               |

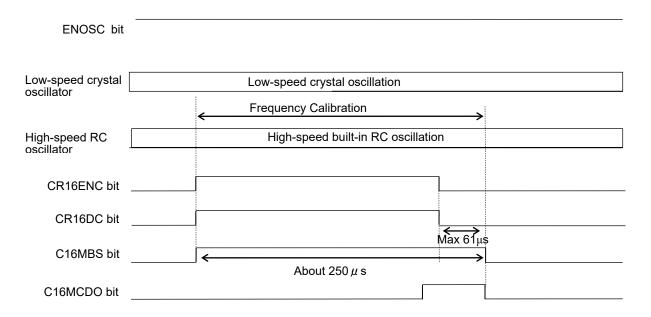

| 5.3.5          | .2. Oscillation Stop and Restart Timing of High-Speed Clock |               |

| 5.3.6.         | Operation of Functions in STOP/HALT/DEEP-HALT/ULTRA-DEE     | P-HALT/HALT-H |

| Mode           | 5-26                                                        |               |

| 5.3.7.         | Block Control Function                                      |               |

| _              |                                                             |               |

| <u>Chapter</u> | <u>6</u>                                                    |               |

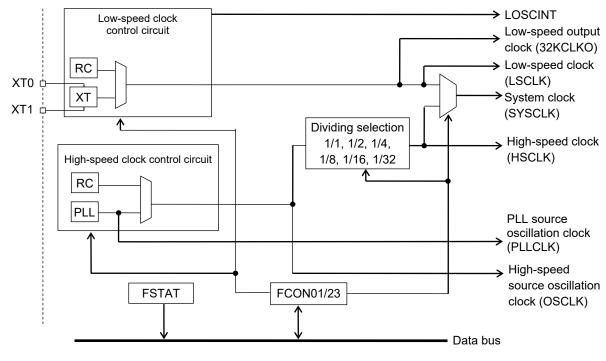

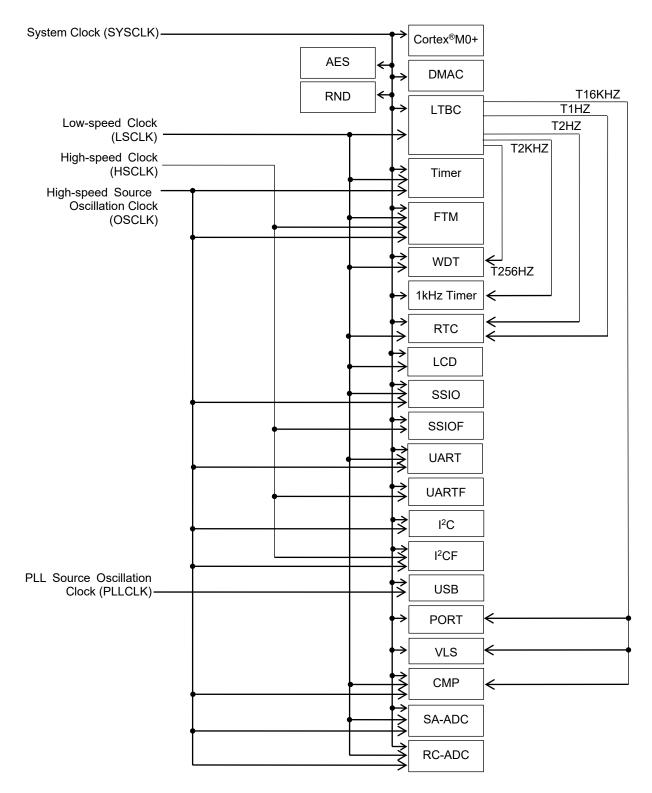

| 6. Clock (     | Generation Circuit                                          |               |

| 6.1. Ge        | neral Description                                           | 6-1           |

| 6.1.1.         | Features                                                    | 6-1           |

| 6.1.2.         | Configuration                                               | 6-1           |

| 6.1.3.         | List of Pins                                                |               |

| 6.1.4.         | Clock Configuration Diagram                                 | 6-3           |

| 6.2. De        | scription of Registers                                      |               |

| 6.2.1.         | List of Registers                                           |               |

| 6.2.2.         | Frequency Control Register 01 (FCON01)                      |               |

| 6.2.3.         | Frequency Control Register 23(FCON23)                       |               |

| 6.2.4.         | Frequency Status Register (FSTAT)                           |               |

| 6.3. De        | scription of Operation                                      | 6-11          |

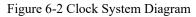

| 6.3.1.         | Low-Speed Clock                                             | 6-11          |

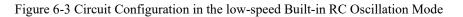

| 6.3.1          | .1. Low-Speed Built-In RC Oscillation Mode                  | 6-11          |

| 6.3.1          | .2. Low-Speed Crystal Oscillation Mode                      | 6-11          |

| 6.3.1          | .3. Low-Speed Built-In RC Oscillation Mode Operation        |               |

| 6.3.1          | .4. Low-Speed Crystal Oscillation Mode Operation            |               |

| 6.3.2.         |                                                             |               |

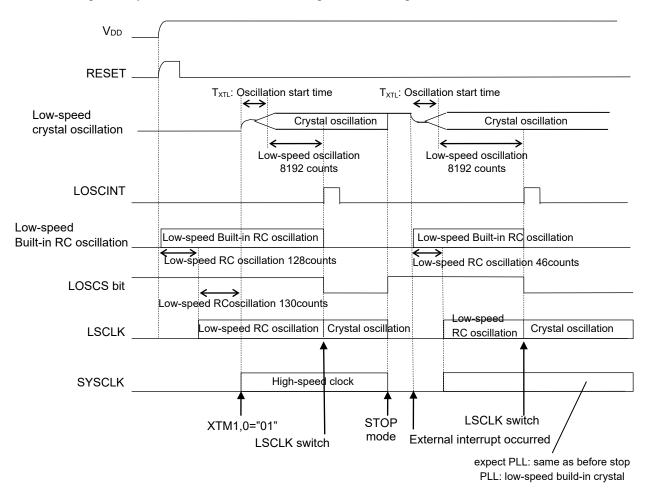

| 6.3.2          | .1. Built-In RC Oscillation Mode                            |               |

| 6.3.2          |                                                             |               |

| 6.3.2          | .3. Built-In RC Oscillation Mode Operation                  |               |

| 6.3.2          |                                                             |               |

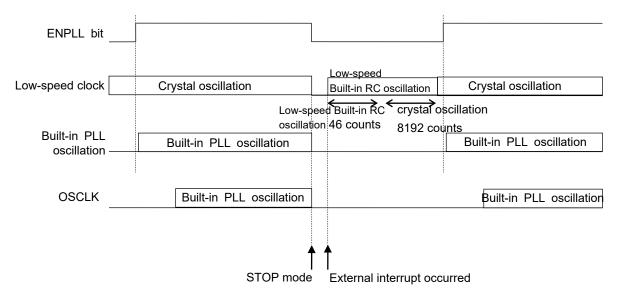

| 6.3.2          | .5. Operation of the Built-In PLL Oscillation mode          |               |

| .pts                                                |                                                                                                                                                                                                                                                            |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| neral Description                                   |                                                                                                                                                                                                                                                            |

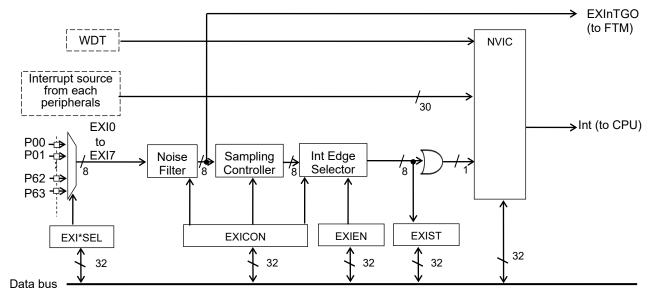

| Features                                            |                                                                                                                                                                                                                                                            |

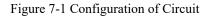

| Configuration                                       |                                                                                                                                                                                                                                                            |

| scription of Registers                              |                                                                                                                                                                                                                                                            |

| List of Registers                                   |                                                                                                                                                                                                                                                            |

| External interrupt enable register (EXIEN)          |                                                                                                                                                                                                                                                            |

| Interrupt Request Register 01 (EXIST)               |                                                                                                                                                                                                                                                            |

| External Interrupt Control Register (EXICON)        |                                                                                                                                                                                                                                                            |

| External Interrupt 03 Selection Register (EXI03SEL) |                                                                                                                                                                                                                                                            |

| External Interrupt 47 Selection Register (EXI47SEL) | <b>7-</b> 11                                                                                                                                                                                                                                               |

| scription of Operation                              |                                                                                                                                                                                                                                                            |

| Interrupt Source                                    |                                                                                                                                                                                                                                                            |

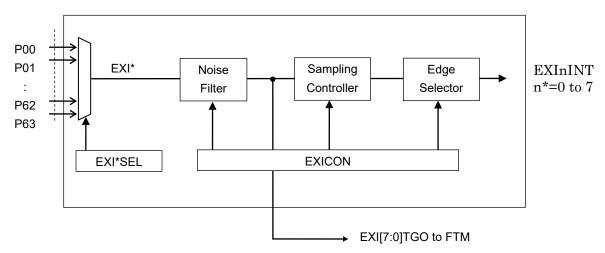

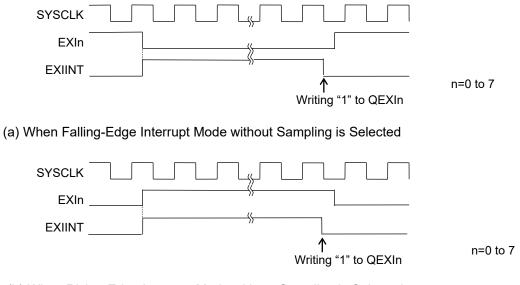

| External Interrupt                                  |                                                                                                                                                                                                                                                            |

|                                                     | Configuration<br>scription of Registers<br>List of Registers<br>External interrupt enable register (EXIEN)<br>Interrupt Request Register 01 (EXIST)<br>External Interrupt Control Register (EXICON)<br>External Interrupt 03 Selection Register (EXI03SEL) |

## Chapter 8

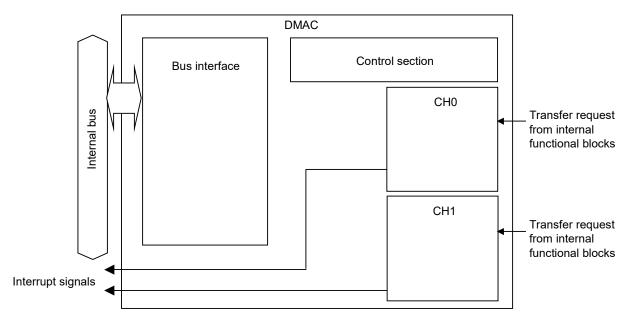

| 8. | DMAC     |                                                         |      |

|----|----------|---------------------------------------------------------|------|

| 8  | 8.1. Gei | neral Description                                       | 8-1  |

|    | 8.1.1.   | Features                                                | 8-1  |

|    | 8.1.2.   | Configuration                                           |      |

| 8  | 8.2. Des | scription of Registers                                  |      |

|    | 8.2.1.   | List of Registers                                       |      |

|    | 8.2.2.   | DMA Mode Register (DMAMOD)                              |      |

|    | 8.2.3.   | DMA Status Register (DMASTA)                            |      |

|    | 8.2.4.   | DMA Completion Status Register (DMAINT)                 |      |

|    | 8.2.5.   | DMA Channel Mask Registers (DMACMSK0-1)                 |      |

|    | 8.2.6.   | DMA Transfer Mode Registers (DMACTMOD0-1)               |      |

|    | 8.2.7.   | DMA Transfer Source Address Registers (DMACSAD0-1)      |      |

|    | 8.2.8.   | DMA Transfer Destination Address Registers (DMACDAD0-1) | 8-12 |

|    | 8.2.9.   | DMA Transfer Count Registers (DMACSIZ0-1)               | 8-13 |

|    | 8.2.10.  | F                                                       | 8-14 |

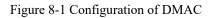

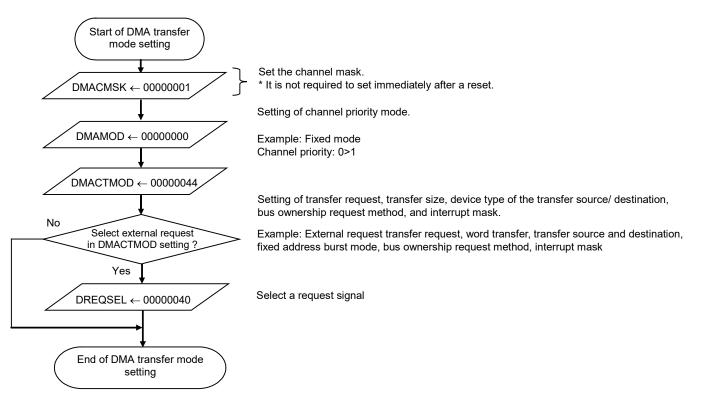

| 8  | 8.3. Des | scription of Operation                                  | 8-15 |

|    | 8.3.1.   | Channel Priority                                        |      |

|    | 8.3.1    |                                                         |      |

|    | 8.3.1    |                                                         |      |

|    | 8.3.2.   | Dual Address Access                                     |      |

|    | 8.3.3.   | Bus Ownership Request Method                            |      |

|    | 8.3.3    | - J                                                     |      |

|    | 8.3.3    |                                                         |      |

|    | 8.3.4.   | Termination of DMA Transfer                             |      |

|    | 8.3.5.   | DMA Transfer Request                                    |      |

|    | 8.3.5    |                                                         |      |

|    | 8.3.5    | · · · · · · · · · · · · · · · · · · ·                   |      |

|    | 8.3.6.   | Procedure for setting DMA transfer mode                 |      |

| 8  | 3.4. Not | tes                                                     |      |

|    | 8.4.1.   | Notes at Transfer Size Setting                          |      |

|    | 8.4.2.   | Notes at Accessing                                      | 8-21 |

|    |          |                                                         |      |

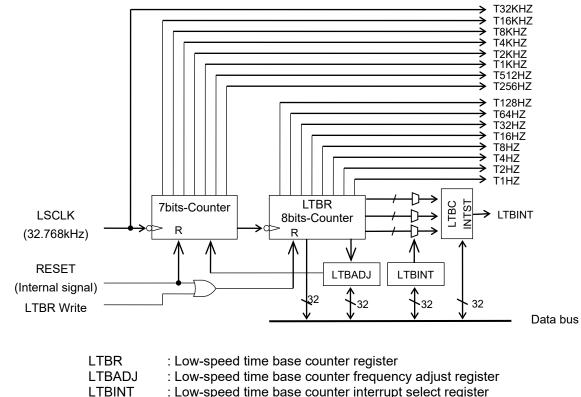

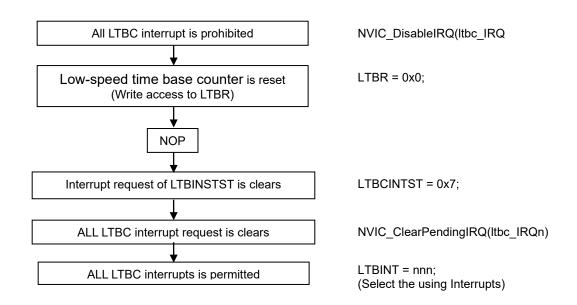

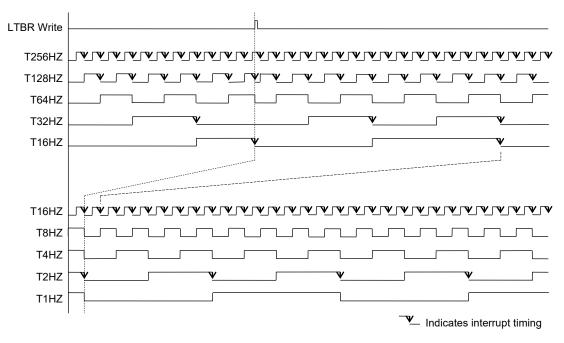

| 9. | Time | e Base Counter | 9-1 |

|----|------|----------------|-----|

| 9  | .1.  | Overview       | 9-1 |

| 9.1.1.  | Features                                                           | 9-1 |

|---------|--------------------------------------------------------------------|-----|

| 9.1.2.  | Configuration                                                      | 9-1 |

| 9.2. De | scription of Registers                                             | 9-2 |

| 9.2.1.  | List of Registers                                                  | 9-2 |

| 9.2.2.  | Low-Speed Time Base Counter Register (LTBR)                        | 9-3 |

| 9.2.3.  | Low-Speed Time Base Counter Frequency Adjustment Register (LTBADJ) | 9-4 |

| 9.2.4.  | Low-Speed Time Base Counter Interrupt Select Register (LTBINT)     | 9-6 |

| 9.2.5.  | Low-speed Time Base Counter Interrupt Status Register (LTBCINTST)  | 9-7 |

| 9.3. De | scription of Operation                                             | 9-8 |

| 9.3.1.  | Low-Speed Time Base Counter                                        | 9-8 |

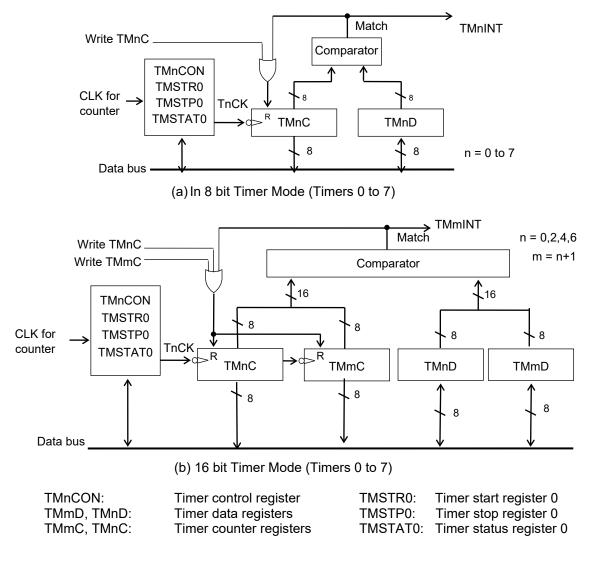

| 10. Timers |                                                   | 10-1  |

|------------|---------------------------------------------------|-------|

| 10.1. Ov   | erview                                            |       |

| 10.1.1.    | Features                                          |       |

| 10.1.2.    | Configuration                                     |       |

| 10.2. De   | scription of Registers                            |       |

| 10.2.1.    | List of Registers                                 |       |

| 10.2.2.    | Timer n Data Register (TMnD : n=0, 2, 4, 6)       |       |

| 10.2.3.    | Timer m Data Register (TMmD : m=1, 3, 5, 7)       |       |

| 10.2.4.    | Timer n Counter Register (TMnC : n=0, 2, 4, 6)    |       |

| 10.2.5.    | Timer m Counter Register (TMmC : n=1, 3, 5, 7)    |       |

| 10.2.6.    | Timer n Control Register (TMnCON : n= 0, 2, 4, 6) |       |

| 10.2.7.    | Timer m Control Register (TMmCON : m= 1, 3, 5, 7) | 10-10 |

| 10.2.8.    | Timer Start Register (TMSTR)                      | 10-12 |

| 10.2.9.    | Timer Stop Register (TMSTP)                       |       |

| 10.2.10.   | Timer Status Register (TMSTAT)                    | 10-14 |

| 10.3. De   | scription of operation                            | 10-15 |

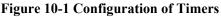

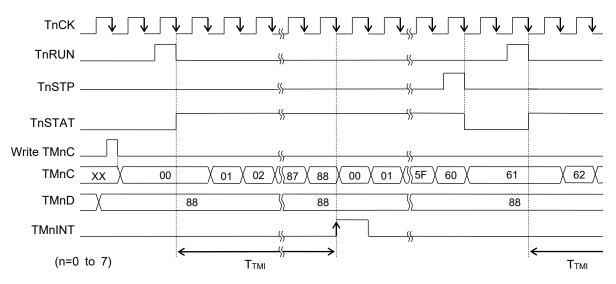

| 10.3.1.    | Normal timer mode operation                       | 10-15 |

| 10.3.2.    | One shot timer mode operation                     | 10-16 |

| 10.3.3.    | 16bit timer mode                                  | 10-16 |

|            |                                                   |       |

| 11.  | Function | n Timer (FTM)                                         | 11-1    |

|------|----------|-------------------------------------------------------|---------|

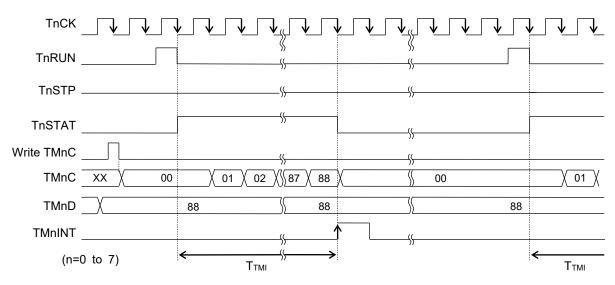

| 11.1 | l. Ger   | neral Description                                     | 11-1    |

| 1    | 1.1.1.   | Features                                              |         |

| 1    | 1.1.2.   | Configuration                                         | 11-2    |

| 1    | 1.1.3.   | List of Pins                                          |         |

| 11.2 | 2. Des   | scription of Registers                                | 11-4    |

| 1    | 1.2.1.   | List of Registers                                     |         |

| 1    | 1.2.2.   | FTMn Period Register (FTnP: n=0,1,2,3)                | 11-6    |

| 1    | 1.2.3.   | FTMn Event Register A (FTnEA : n=0,1,2,3)             |         |

| 1    | 1.2.4.   | FTMn Event Register B (FTnEB : n=0,1,2,3)             | 11-8    |

| 1    | 1.2.5.   | FTMn Dead Time Register (FTnDT : n=0,1,2,3)           | 11-9    |

| 1    | 1.2.6.   | FTMn Counter Register (FTnC : n=0,1,2,3)              |         |

| 1    | 1.2.7.   | FTMn Control Register 0 (FTnCON0 : n=0,1,2,3)         | . 11-11 |

| 1    | 1.2.8.   | FTMn Control Register 1 (FTnCON1 : n=0,1,2,3)         | .11-13  |

| 1    | 1.2.9.   | FTMn Mode Register (FTnMOD : n=0,1,2,3)               | .11-15  |

| 1    | 1.2.10.  | FTMn Clock Register (FTnCLK : n=0,1,2,3)              | .11-17  |

| 1    | 1.2.11.  | FTMn Trigger Register (FTnTRG : n=0,1,2,3)            | .11-19  |

| 1    | 1.2.12.  | FTMn Interrupt Enable Register (FTnINTE: n = 0,1,2,3) | 11-22   |

| 1    | 1.2.13.  | FTMn Interrupt Status Register (FTnINTS : n=0,1,2,3)  |         |

| 1    | 1.2.14.  | FTMn Interrupt Clear Register (FTnINTC : n=0,1,2,3)   |         |

|      |          |                                                       |         |

#### ML630Q464/Q466 User's Manual Contents

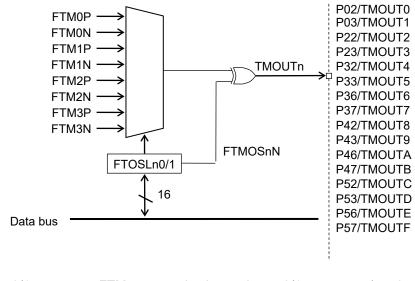

| 11.2.15.  | FTM Output nm Select Register n (FTOSLn : n = 0, 4, 8, C)  | 11-27 |

|-----------|------------------------------------------------------------|-------|

| 11.3. Des | scription of Operation                                     | 11-29 |

| 11.3.1.   | Common Sequence                                            |       |

| 11.3.2.   | Counter Operation                                          | 11-31 |

| 11.3.2.1  | . Starting/Stopping Counting by Software                   | 11-31 |

| 11.3.2.2  | 2. Starting/Stopping Counting by Trigger Event             | 11-31 |

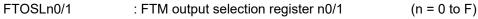

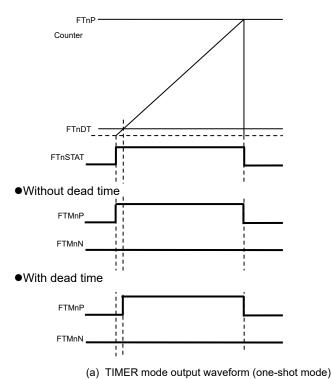

| 11.3.3.   | TIMER Mode Operation                                       | 11-32 |

| 11.3.3.1  |                                                            |       |

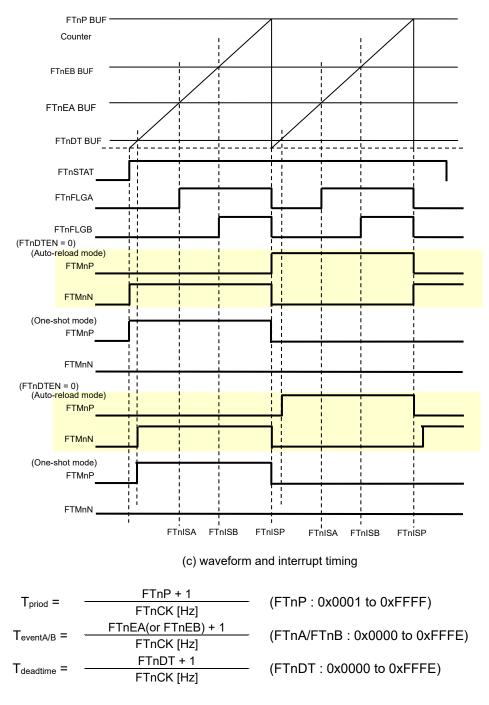

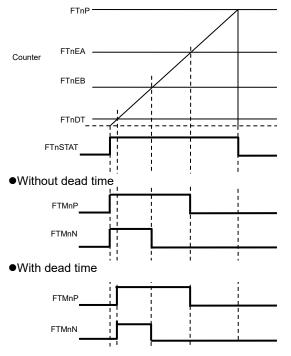

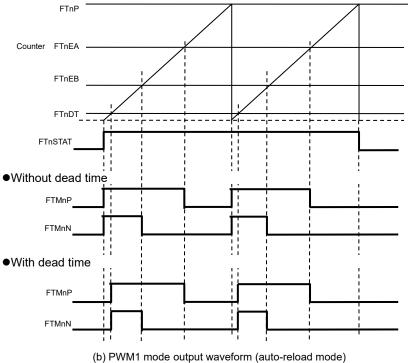

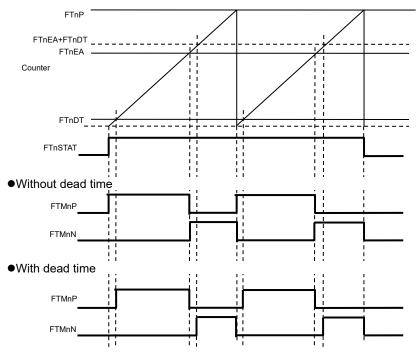

| 11.3.4.   | PWM1 Mode Operation                                        | 11-35 |

| 11.3.4.1  | . Output Waveform in PWM1 Mode                             | 11-35 |

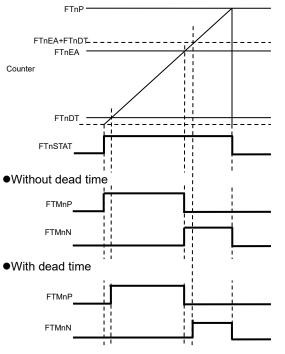

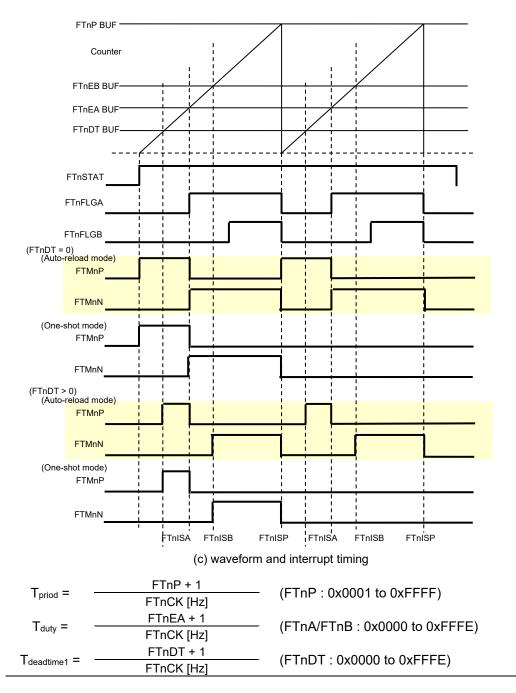

| 11.3.5.   | PWM2 Mode Operation                                        | 11-37 |

| 11.3.5.1  |                                                            |       |

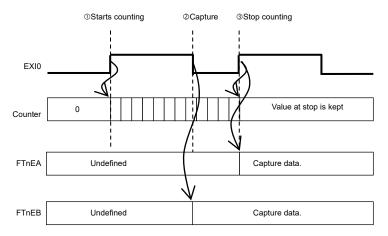

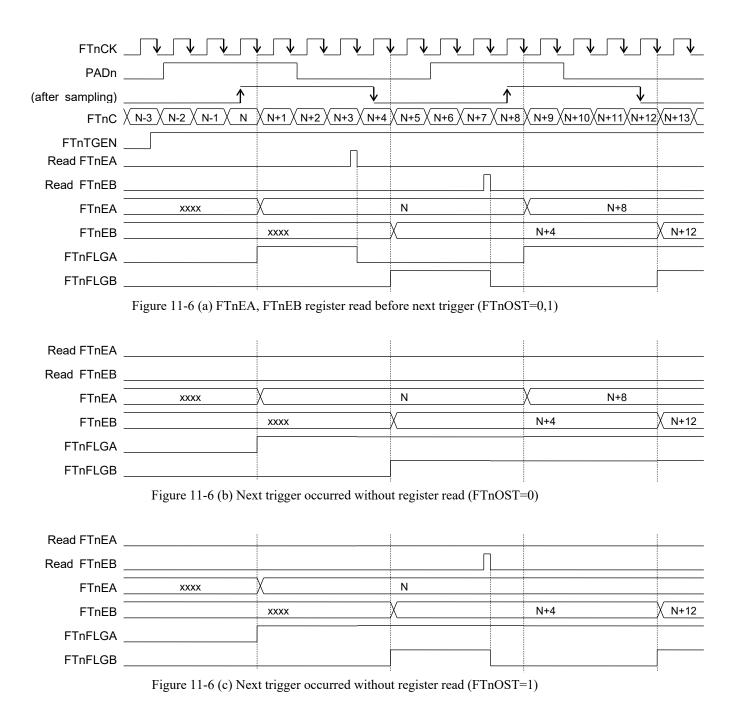

| 11.3.6.   | CAPTURE Mode Operation                                     | 11-40 |

| 11.3.6.1  | . Measurement Example in the CAPTURE Mode                  | 11-40 |

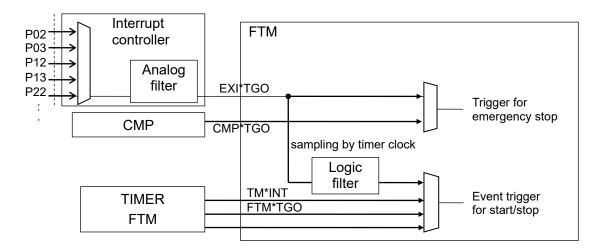

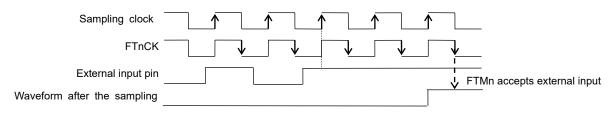

| 11.3.7.   | Event/Emergency Stop Trigger Control                       | 11-42 |

| 11.3.7.1  | . Trigger Signal                                           | 11-42 |

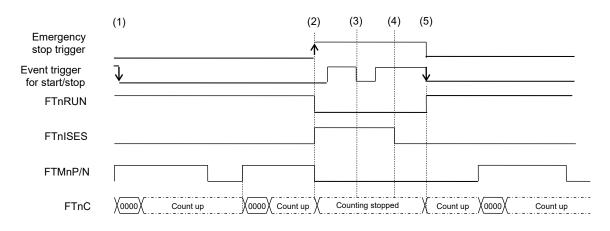

| 11.3.7.2  | 8. Start/Stop Operationg by Event Trigger                  | 11-43 |

| 11.3.7.3  | Emergency Stop Operation                                   | 11-44 |

| 11.3.8.   | Output at Counter Stop                                     | 11-44 |

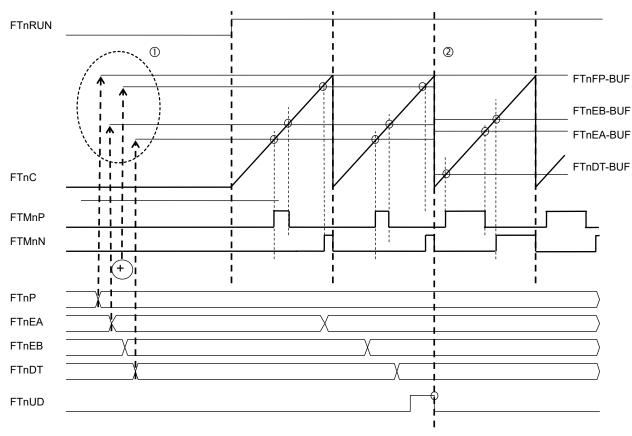

| 11.3.9.   | Changing Period, Event A/B, and Dead Time during Operation |       |

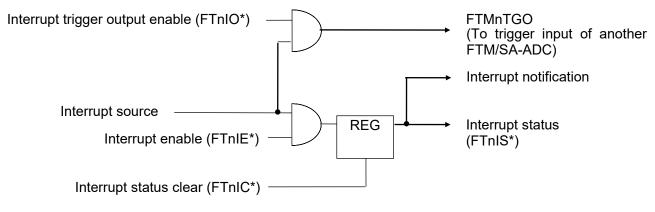

| 11.3.10.  | Interrupt Source                                           | 11-46 |

|           |                                                            |       |

# Chapter 12

| 12. Real Tin | ne Clock                                               | 12-1  |

|--------------|--------------------------------------------------------|-------|

| 12.1. Ove    | erview                                                 | 12-1  |

| 12.1.1.      | Features                                               | 12-1  |

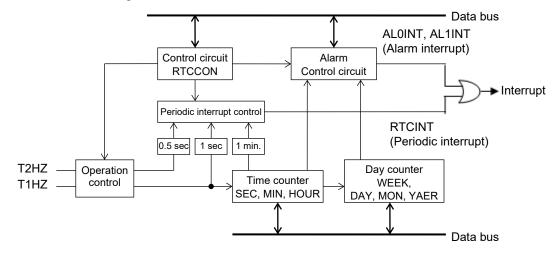

| 12.1.2.      | Configuration                                          | 12-1  |

| 12.2. Des    | scription of Registers                                 | 12-2  |

| 12.2.1.      | List of Registers                                      |       |

| 12.2.2.      | Real Time Clock Second Register (RTCSEC)               |       |

| 12.2.3.      | Real Time Clock Minute Register (RTCMIN)               |       |

| 12.2.4.      | Real Time Clock Hour Register (RTCHOUR)                | 12-5  |

| 12.2.5.      | Real Time Clock Week Register (RTCWEEK)                | 12-6  |

| 12.2.6.      | Real Time Clock Day Register (RTCDAY)                  | 12-7  |

| 12.2.7.      | Real Time Clock Month Register (RTCMON)                | 12-8  |

| 12.2.8.      | Real Time Clock Year Register (RTCYEAR)                | 12-9  |

| 12.2.9.      | Real Time Clock Control Register (RTCCON)              |       |

| 12.2.10.     | Real Time Clock Alarm 0 Minute Register (AL0MIN)       | 12-11 |

| 12.2.11.     | Real Time Clock Alarm 0 Hour Register (AL0HOUR)        | 12-12 |

| 12.2.12.     | Real Time Clock Alarm 0 Week Register (AL0WEEK)        | 12-13 |

| 12.2.13.     | Real Time Clock Alarm 1 Minute Register (AL1MIN)       | 12-14 |

| 12.2.14.     | Real Time Clock Alarm 1 Hour Register (AL1HOUR)        | 12-15 |

| 12.2.15.     | Real Time Clock Alarm 1 Day Register (AL1DAY)          | 12-16 |

| 12.2.16.     | Real Time Clock Alarm 1 Month Register (AL1MON)        | 12-17 |

| 12.2.17.     | Real Time Clock Hour/Minute/Second Register (RTCHMS)   | 12-18 |

| 12.2.18.     | Real Time Clock Year/Month/Day/Week Register (RTCYMDW) | 12-19 |

| 12.2.19.     | Real Time Clock Interrupt Status Register (RTCINTST)   |       |

| 12.3. Des    | scription of Operation                                 | 12-21 |

|              |                                                        |       |

| 13. 1 | kHz Timer (1kHzTM) 1 | 3-1  |

|-------|----------------------|------|

| 13.1. | Overview1            | 3-1  |

| 13.1  | 1.1. Features 1      | .3-1 |

#### ML630Q464/Q466 User's Manual Contents

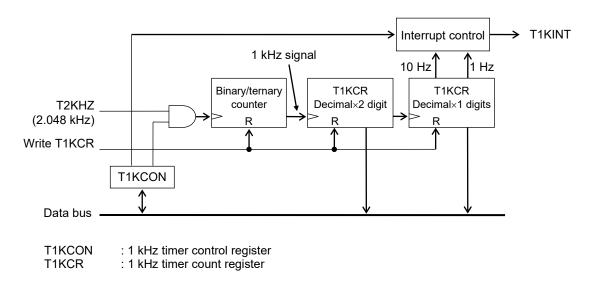

| 13.1.2. Configuration                         | 13-1 |

|-----------------------------------------------|------|

| 13.2. Description of Registers                |      |

| 13.2.1. List of Registers                     |      |

| 13.2.2. 1 kHz Timer Count Register (T1KCR)    |      |

| 13.2.3. 1 kHz Timer Control Register (T1KCON) |      |

| 13.3. Description of Operation                | 13-5 |

# Chapter 14

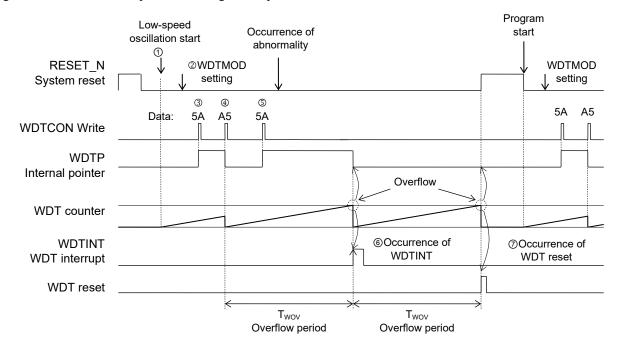

| 14. Wate | hdog Timer                                        |      |

|----------|---------------------------------------------------|------|

| 14.1. (  | Dverview                                          |      |

| 14.1.1.  | Features                                          |      |

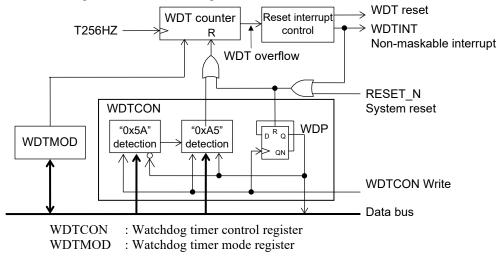

| 14.1.2.  | Configuration                                     |      |

| 14.2. I  | Description of Registers                          |      |

| 14.2.1.  | List of Registers                                 |      |

| 14.2.2.  | Watchdog Timer Control Register (WDTCON)          | 14-3 |

| 14.2.3.  | Watchdog Timer Mode Register (WDTMOD)             |      |

| 14.3. I  | Description of Operation                          |      |

| 14.3.1.  | The process example when not using Watchdog Timer |      |

# Chapter 15

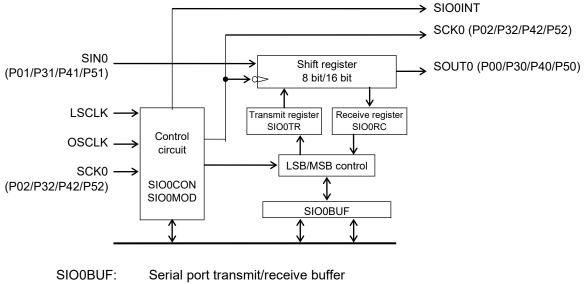

|          | ronous Serial Port                              |  |

|----------|-------------------------------------------------|--|

| 15.1. Ov | verview                                         |  |

| 15.1.1.  | Features                                        |  |

| 15.1.2.  | Configuration                                   |  |

| 15.1.3.  | List of Pins                                    |  |

| 15.2. De | escription of Registers                         |  |

| 15.2.1.  | List of Registers                               |  |

| 15.2.2.  | Serial Port 0 Transmit/Receive Buffer (SIO0BUF) |  |

| 15.2.3.  | Serial Port 0 Control Register (SIO0CON)        |  |

| 15.2.4.  | Serial Port 0 Mode Register (SIO0MOD)           |  |

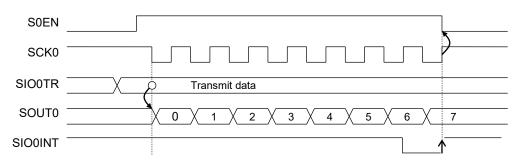

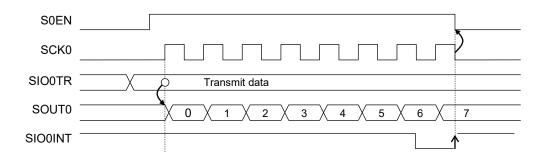

| 15.3. De | escription of Operation                         |  |

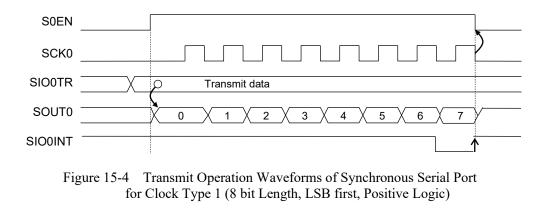

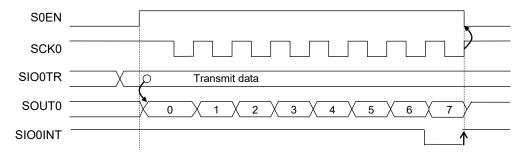

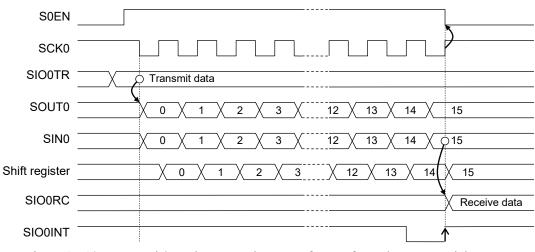

| 15.3.1.  | Transmit Operation                              |  |

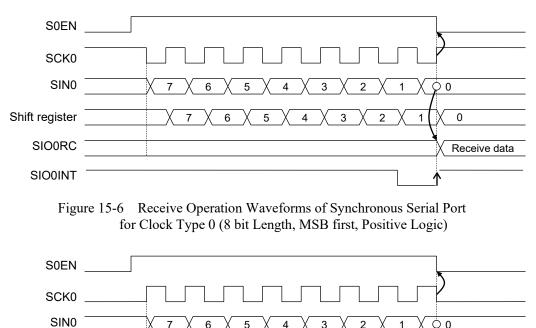

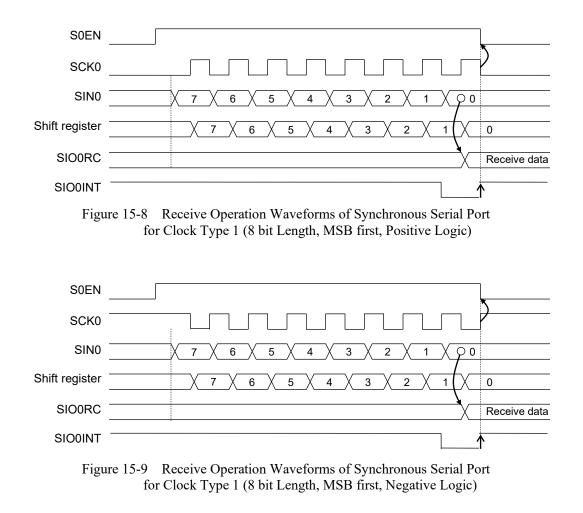

| 15.3.2.  | Receive Operation                               |  |

| 15.3.3.  | Transmit/Receive Operation                      |  |

| 15.3.4.  | Pin Settings                                    |  |

| 16. Synchro | nous Serial Port with FIFO (SSIOF)                 |  |

|-------------|----------------------------------------------------|--|

| 16.1. Ger   | neral Description                                  |  |

| 16.1.1.     | Features                                           |  |

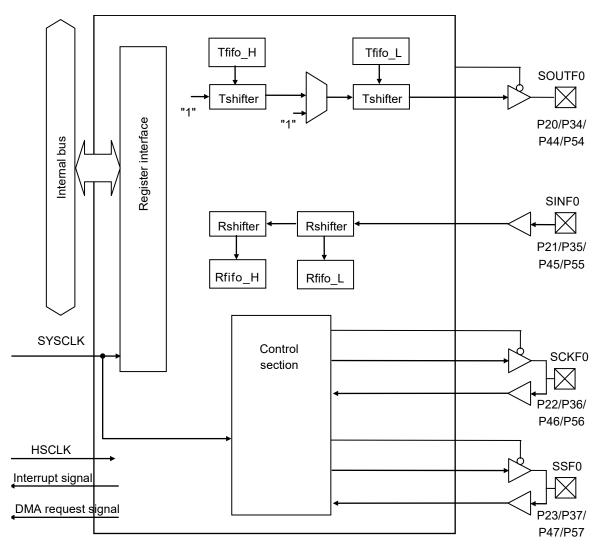

| 16.1.2.     | Configuration                                      |  |

| 16.1.3.     | List of Pins                                       |  |

| 16.2. Des   | cription of Registers                              |  |

| 16.2.1.     | List of Registers                                  |  |

| 16.2.2.     | SIOF0 Control Register (SF0CTRL)                   |  |

| 16.2.3.     | SIOF0 Interrupt Control Register (SF0INTC)         |  |

| 16.2.4.     | SIOF0 Transfer Interval Control Register (SF0TRAC) |  |

| 16.2.5.     | SIOF0 Baud Rate Register (SF0BRR)                  |  |

| 16.2.6.     | SIOF0 Status Register (SF0SRR)                     |  |

| 16.2.7.     | SIOF0 Status Clear Register (SF0SRC)               |  |

| 16.2.8.     | SIOF0 FIFO Status Register (SF0FSR)                |  |

| 16.2.9.     | SIOF0 Write Data Register (SF0DWR)                 |  |

|             |                                                    |  |

| 16.2.10.  | SIOF0 Read Data Register (SF0DRR)                                    | 16-20   |

|-----------|----------------------------------------------------------------------|---------|

| 16.3. Des | cription of Operation                                                | 16-21   |

| 16.3.1.   | Master Mode and Slave Mode                                           | 16-21   |

| 16.3.2.   | Control of Polarity and Phase of Serial Clock                        | 16-21   |

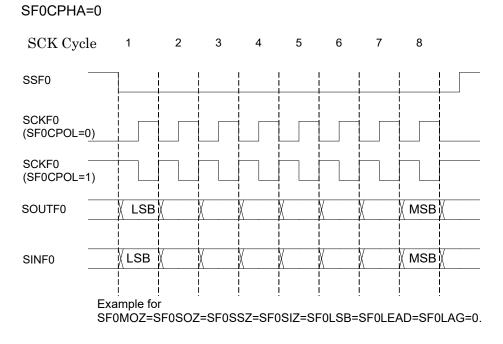

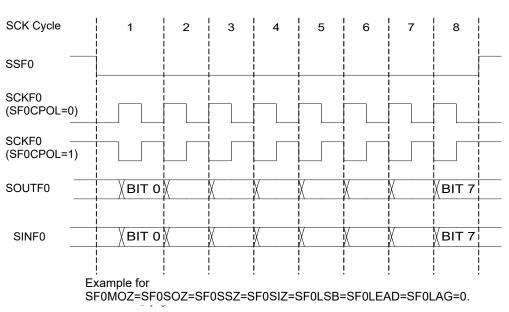

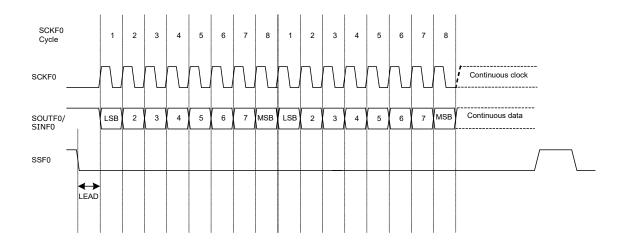

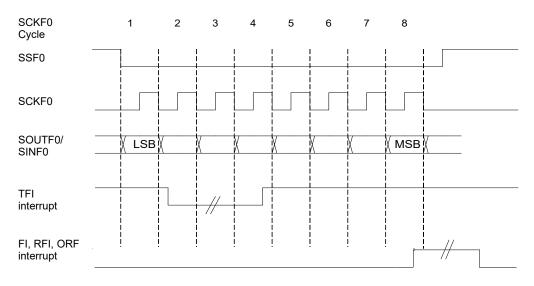

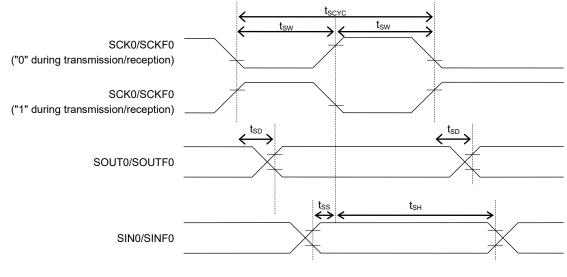

| 16.3.3.   | Data Transfer Timing When SF0CPHA Is "0"                             | 16-21   |

| 16.3.4.   | Data Transfer Timing When SF0CPHA Is "1"                             | 16-22   |

| 16.3.5.   | Serial Clock Baud Rate                                               | 16-22   |

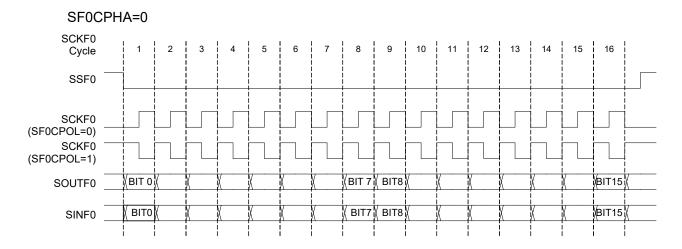

| 16.3.6.   | Transfer Size                                                        | 16-23   |

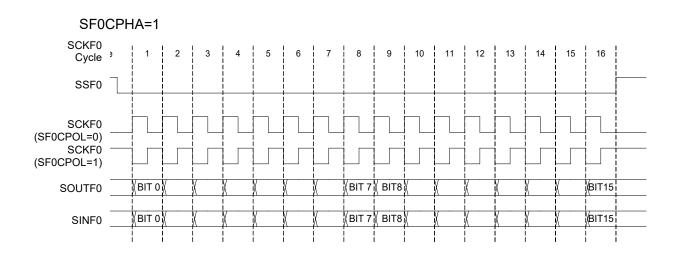

| 16.3.7.   | Transfer Interval Setting                                            | 16-24   |

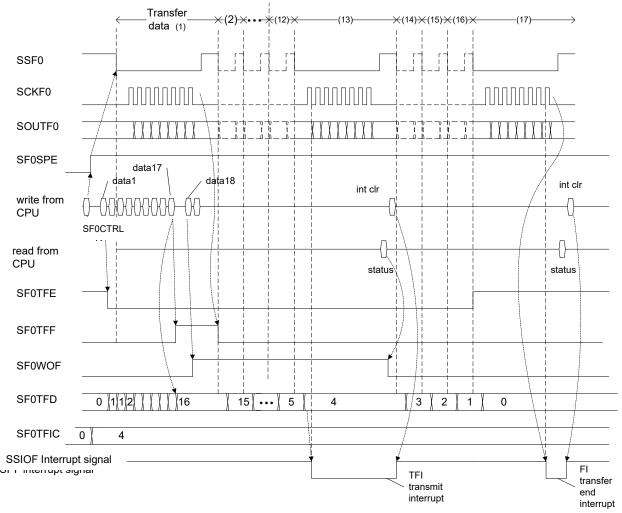

| 16.3.8.   | Transmit Operation (Master Mode)                                     | 16-26   |

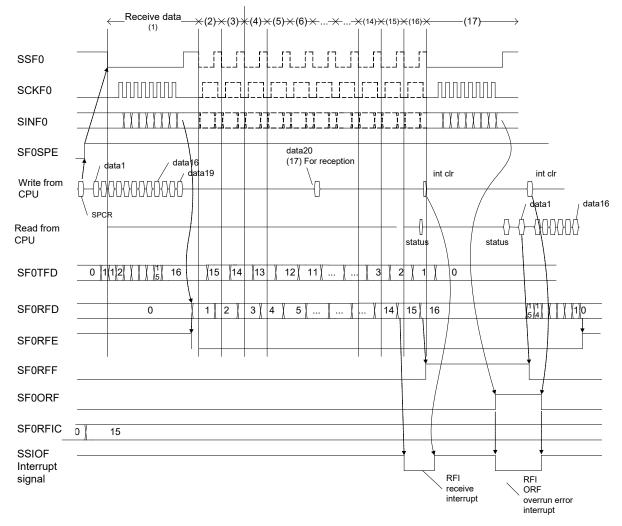

| 16.3.9.   | Receive Operation (Master Mode)                                      | 16-27   |

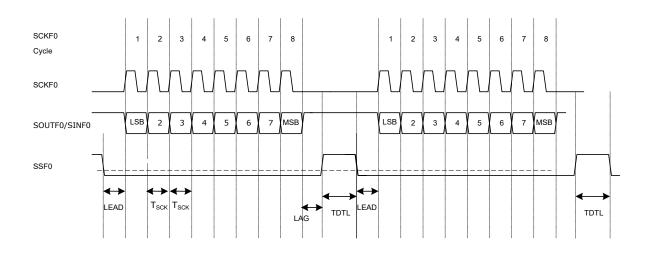

| 16.3.10.  | FIFO Operation                                                       | 16-28   |

| 16.3.11.  | Write Overflow                                                       | 16-28   |

| 16.3.12.  | Overrun Error                                                        | 16-28   |

| 16.3.13.  | FIFO Clear                                                           | 16-28   |

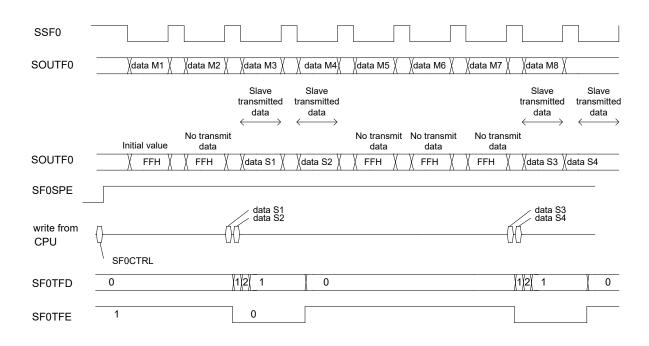

| 16.3.14.  | Transfer When Slave Has Different Number of FIFO Transfer Bytes/Half | Words   |

|           | 16-29                                                                |         |

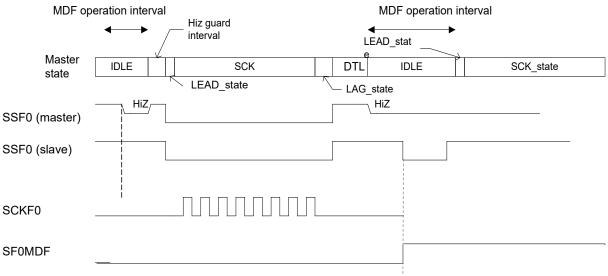

| 16.3.15.  | Mode Fault (MDF)                                                     | 16 - 30 |

| 16.3.16.  | Interrupt Source                                                     | 16-31   |

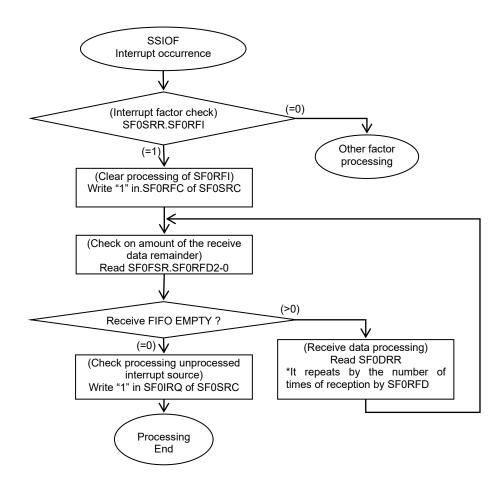

| 16.3.16.  | 1. SSIOF Interrupt Source                                            | 16-31   |

| 16.3.16.  | 2. Clear SSIOF Interrupt                                             | 16-31   |

| 16.3.16.  | 3. SSIOF Interrupt Timing                                            | 16-31   |

| 16.3.16.  | 4. Interrupt processing flow                                         | 16-32   |

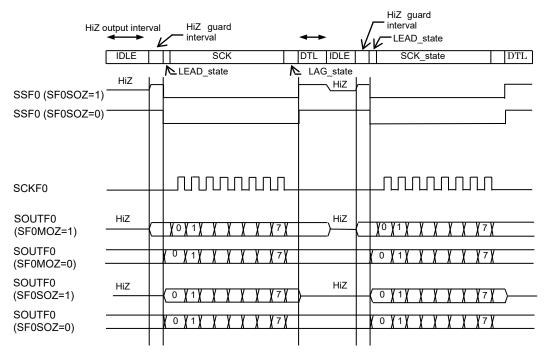

| 16.3.17.  | Hi-Z Operation                                                       | 16 - 33 |

| 16.3.18.  | Interval from SF0MST Setting to Transfer Start                       | 16-33   |

| 16.3.19.  | Pin Settings                                                         | 16-33   |

|           |                                                                      |         |

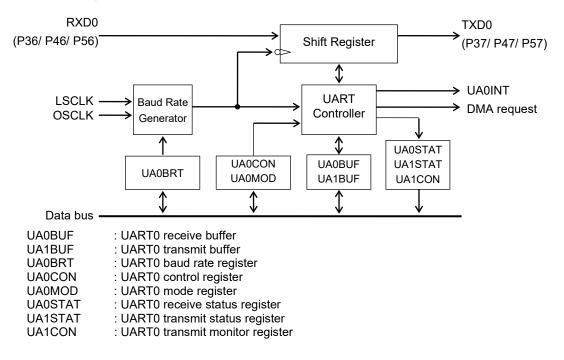

| 17. UART  | -                                          |       |

|-----------|--------------------------------------------|-------|

| 17.1. Ger | neral Description                          |       |

| 17.1.1.   | Features                                   |       |

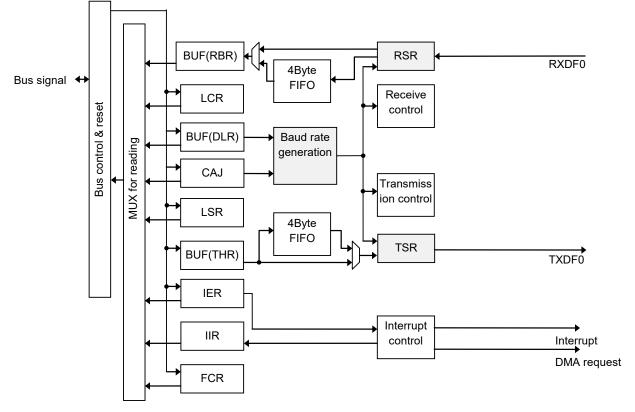

| 17.1.2.   | Configuration                              | 17-1  |

| 17.1.3.   | List of Pins                               | 17-2  |

| 17.2. Des | cription of Registers                      |       |

| 17.2.1.   | List of Registers                          |       |

| 17.2.2.   | UARTO Receive Buffer (UA0BUF)              |       |

| 17.2.3.   | UARTO Transmit Buffer (UA1BUF)             |       |

| 17.2.4.   | UARTO Control Register (UA0CON)            |       |

| 17.2.5.   | UARTO Transmit Monitor Register (UA1CON)   |       |

| 17.2.6.   | UARTO Mode Register (UA0MOD)               |       |

| 17.2.7.   | UARTO Baud Rate Register (UA0BRT)          |       |

| 17.2.8.   | UARTO Receive Status Register (UA0STAT)    |       |

| 17.2.9.   | UARTO Transmit Status Register (UA1STAT)   |       |

| 17.2.10.  | UARTO Interrupt Status Register (UA0INTST) | 17-13 |

| 17.3. Des | cription of Operation                      | 17-14 |

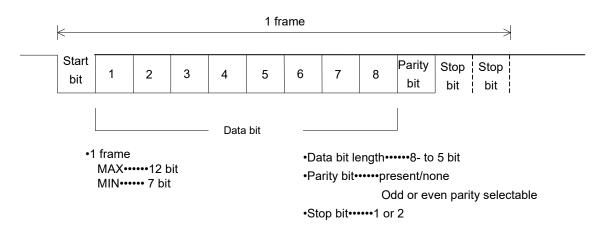

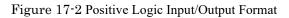

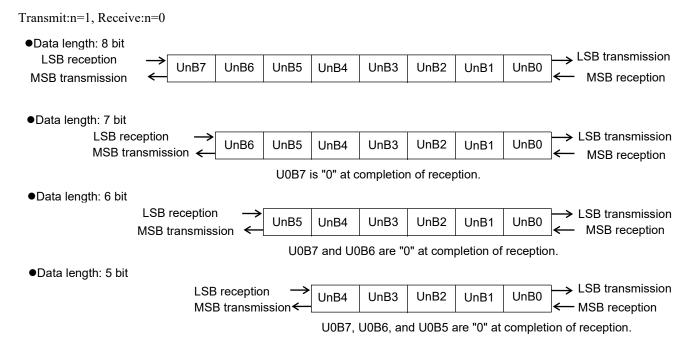

| 17.3.1.   | Transfer Data Format                       |       |

| 17.3.2.   | Baud Rate                                  |       |

| 17.3.3.   | Transmitted Data Direction                 |       |

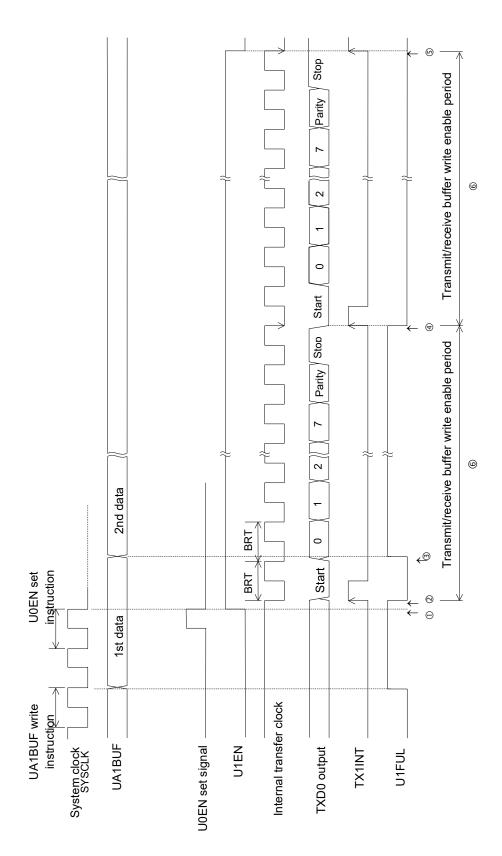

| 17.3.4.   | Transmit Operation                         | 17-16 |

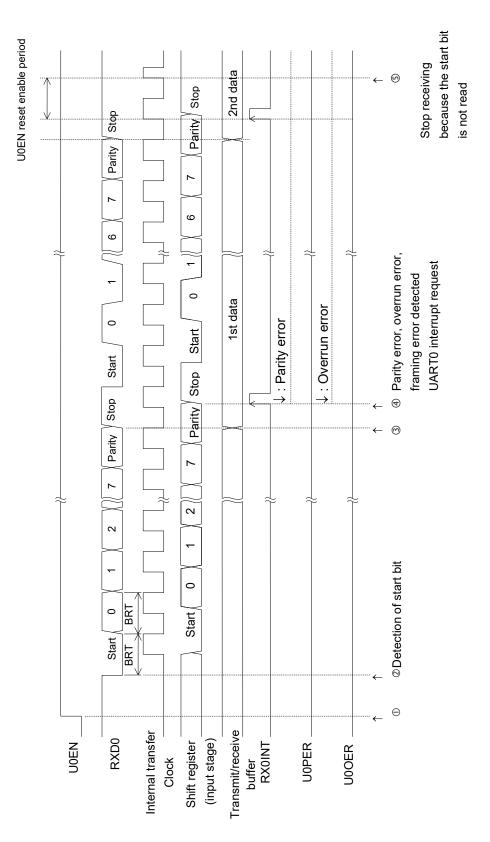

| 17.3.5.   | Receive Operation                          |       |

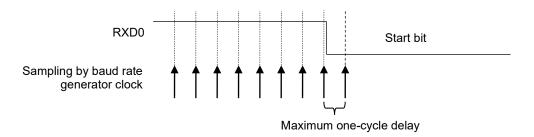

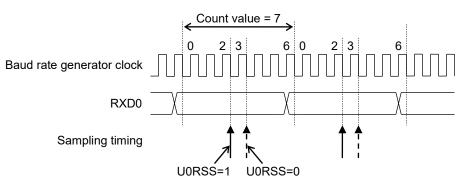

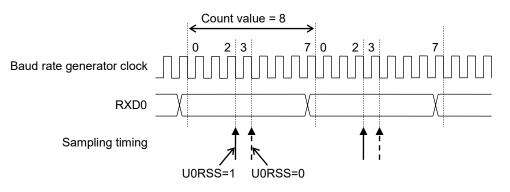

| 17.3.5.1  | . Detection of Start Bit                   | 17-20 |

| 17.3.5.2  |                                            |       |

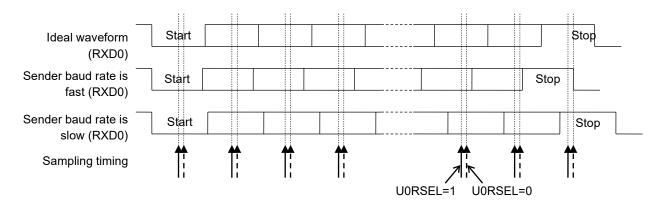

| 17.3.5.3  | B. Receive Margin                          | 17-21 |

#### ML630Q464/Q466 User's Manual Contents

### Chapter 18

| 18. UART w | rith FIFO (UARTF)                          |       |

|------------|--------------------------------------------|-------|

| 18.1. Ger  | neral Description                          |       |

| 18.1.1.    | Features                                   |       |

| 18.1.2.    | Configuration                              |       |

| 18.1.3.    | List of Pins                               |       |

| 18.2. Des  | cription of Registers                      |       |

| 18.2.1.    | List of Registers                          |       |

| 18.2.2.    | UARTF0 Transmit/Receive Buffer (UAF0BUF)   |       |

| 18.2.3.    | UARTF0 Interrupt Enable Register (UAF0IER) |       |

| 18.2.4.    | UARTF0 Interrupt Status Register (UAF0IIR) |       |

| 18.2.5.    | UARTF0 Mode Register (UAF0MOD)             |       |

| 18.2.6.    | UARTF0 Line Status Register (UAF0LSR)      |       |

| 18.2.7.    | UARTF0 Clock Adjustment Register (UAF0CAJ) | 18-15 |

| 18.3. Des  | cription of Operation                      |       |

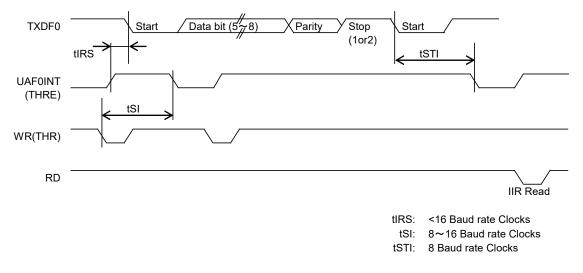

| 18.3.1.    | Data Transmission                          | 18-16 |

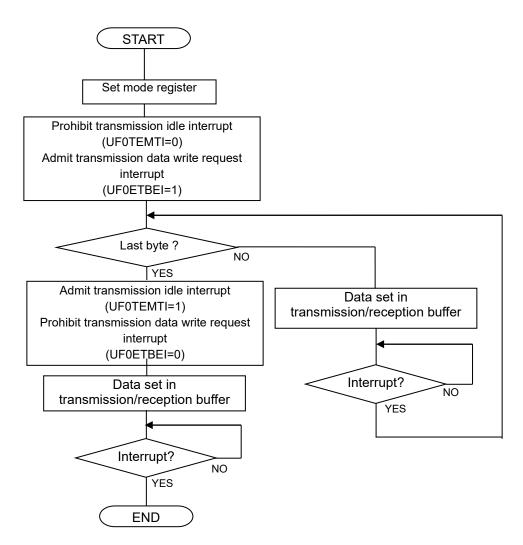

| 18.3.2.    | Transmission Flow                          |       |

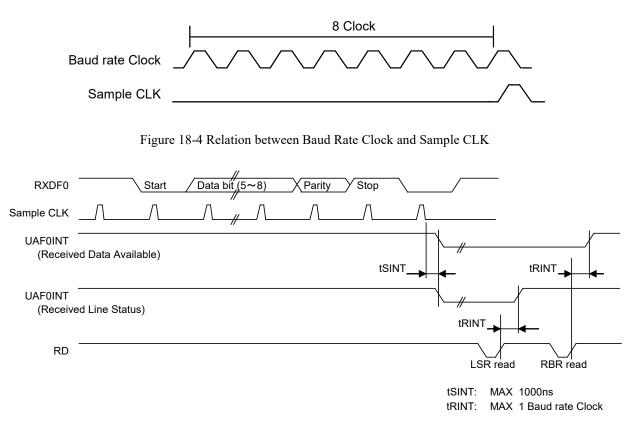

| 18.3.3.    | Data Reception                             |       |

| 18.3.4.    | Baud Rate Clock Generation                 |       |

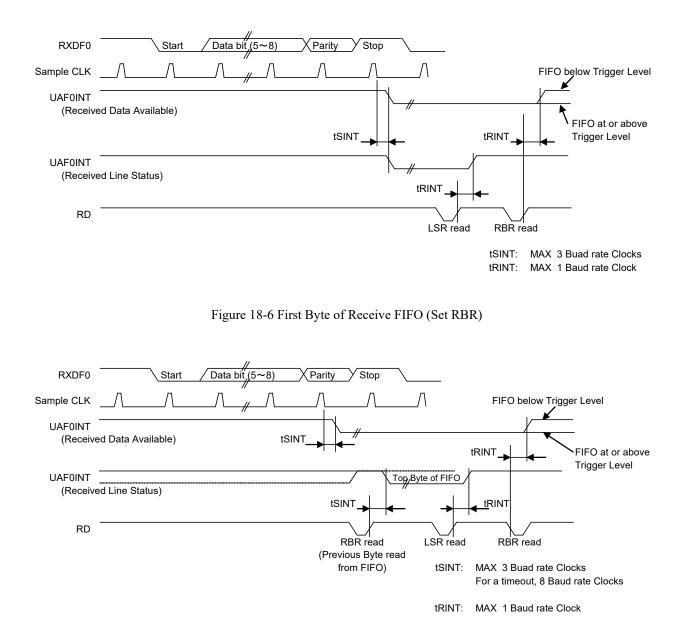

| 18.3.5.    | FIFO Mode                                  |       |

| 18.3.6.    | FIFO Polled Mode                           |       |

| 18.3.7.    | Error Status                               |       |

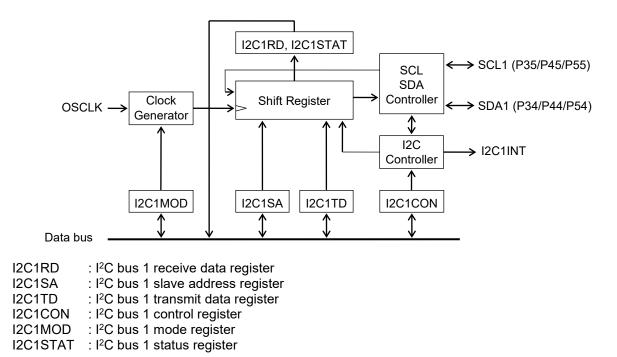

| 19. I <sup>2</sup> C Bus | Interface                                              | 19-1  |

|--------------------------|--------------------------------------------------------|-------|

| 19.1. Gen                | eral Description                                       | 19-1  |

| 19.1.1.                  | Features                                               | 19-1  |

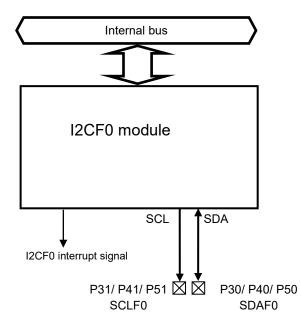

| 19.1.2.                  | Configuration                                          | 19-1  |

| 19.1.3.                  | List of Pins                                           | 19-1  |

| 19.2. Des                | cription of Registers                                  | 19-2  |

| 19.2.1.                  | List of Registers                                      |       |

| 19.2.2.                  | I <sup>2</sup> C Bus 1 Receive Data Register (I2C1RD)  | 19-3  |

| 19.2.3.                  | I <sup>2</sup> C Bus 1 Slave Address Register (I2C1SA) |       |

| 19.2.4.                  | I <sup>2</sup> C Bus 1 Transmit Data Register (I2C1TD) |       |

| 19.2.5.                  | I <sup>2</sup> C Bus 1 Control Register (I2C1CON)      |       |

| 19.2.6.                  | I <sup>2</sup> C Bus 1 Mode Register (I2C1MOD)         | 19-8  |

| 19.2.7.                  | I <sup>2</sup> C Bus 1 Status Register (I2C1STAT)      | 19-10 |

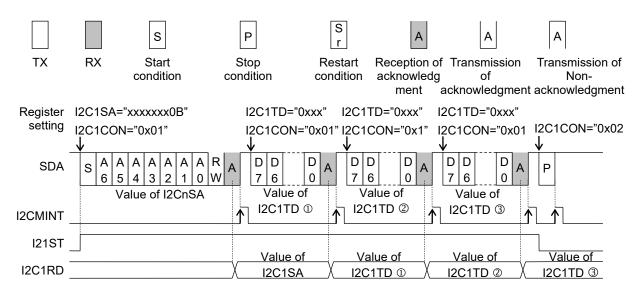

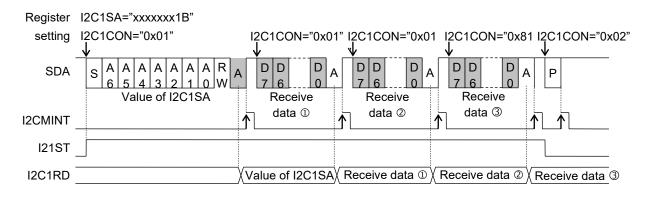

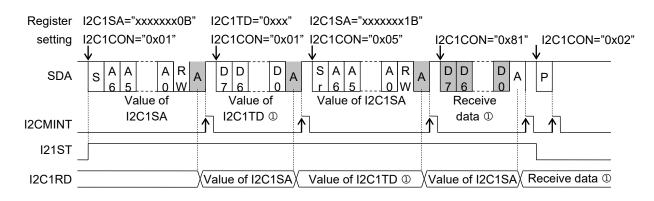

| 19.3. Des                | cription of Operation                                  | 19-11 |

| 19.3.1.                  | Communication Operation Mode                           | 19-11 |

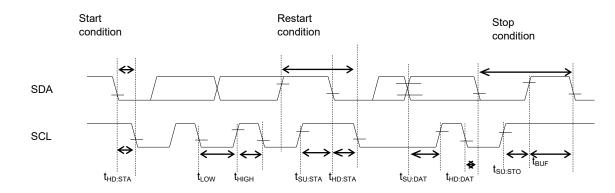

| 19.3.1.1                 | Start Condition                                        | 19-11 |

| 19.3.1.2                 | Restart Condition                                      | 19-11 |

| 19.3.1.3                 | Slave Address Transmit Mode                            | 19-11 |

| 19.3.1.4                 | Data Transmit Mode                                     | 19-11 |

| 19.3.1.5                 | Data receive Mode                                      | 19-11 |

| 19.3.1.6                 | Control Register Setting Wait State                    | 19-12 |

| 19.3.1.7                 | Stop Condition                                         | 19-12 |

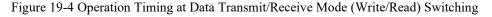

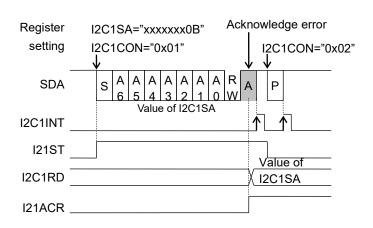

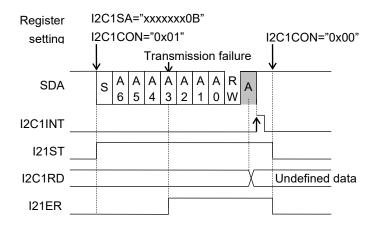

| 19.3.2.                  | Communication Operation Timing                         | 19-13 |

| 19.3.3.                  | Operation Waveforms                                    | 19-15 |

| 19.3.4.                  | Pin Settings                                           | 19-16 |

| 20. I <sup>2</sup> C Bus |                                                                       | 20-1    |

|--------------------------|-----------------------------------------------------------------------|---------|

| 20.1. Ove                | erview                                                                | 20-1    |

| 20.1.1.                  | Features                                                              | 20-1    |

| 20.1.2.                  | Configuration                                                         | 20-1    |

| 20.1.3.                  | List of Pins                                                          |         |

|                          | scription of Registers                                                |         |

| 20.2.1.                  | List of Registers                                                     |         |

| 20.2.2.                  | I <sup>2</sup> C Slave Address Register (I2F0SAD)                     |         |

| 20.2.3.                  | I <sup>2</sup> C Control Register (I2F0CTL)                           |         |

| 20.2.4.                  | I <sup>2</sup> C Status Register (I2F0SR)                             |         |

| 20.2.5.                  | I <sup>2</sup> C Data Register (I2F0DR)                               |         |

| 20.2.6.                  | I <sup>2</sup> C Bus Monitor Register (I2F0MON)                       |         |

| 20.2.7.                  | I <sup>2</sup> C Bus Transfer Rate Setup Counter (I2F0BC)             |         |

| 20.2.8.                  | I <sup>2</sup> C Mode Register (I2F0MOD)                              |         |

| 20.2.9.                  | I <sup>2</sup> C Buffer Mode Slave Address Register (I2F0BSV)         |         |

| 20.2.10.                 | I <sup>2</sup> C Buffer Mode Sub Address Register (I2F0BSB)           |         |

| 20.2.11.                 | I <sup>2</sup> C Buffer Mode Format Register (I2F0BFR)                |         |

| 20.2.12.                 | I <sup>2</sup> C Buffer Mode Control Register (I2F0BCT)               |         |

| 20.2.13.                 | I <sup>2</sup> C Buffer Mode Interrupt Mask Register (I2F0BMK) *n=0,1 |         |

| 20.2.14.                 | I <sup>2</sup> C Buffer Mode Status Register (I2F0BSR)                |         |

| 20.2.15.                 | I <sup>2</sup> C Buffer Mode Level Register (I2F0BLV)                 |         |

| 20.2.16.                 | I <sup>2</sup> C Timer Register (I2F0TMR)                             |         |

| 20.2.17.                 | I <sup>2</sup> C Input Noise Filter Setting Register (I2F0NF)         |         |

|                          | scription of Operation                                                |         |

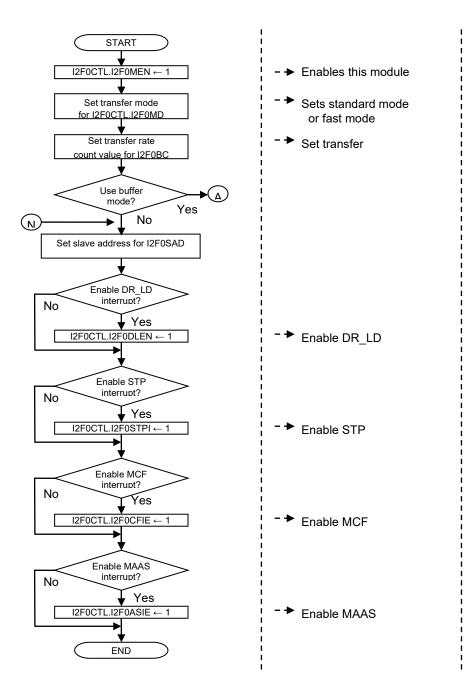

| 20.3.1.                  | Flow of Initial Setting                                               |         |

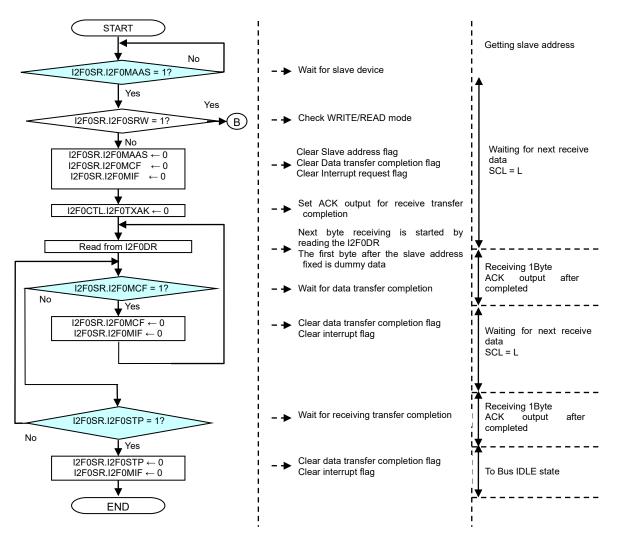

| 20.3.2.                  | Flow of Slave Reception                                               |         |

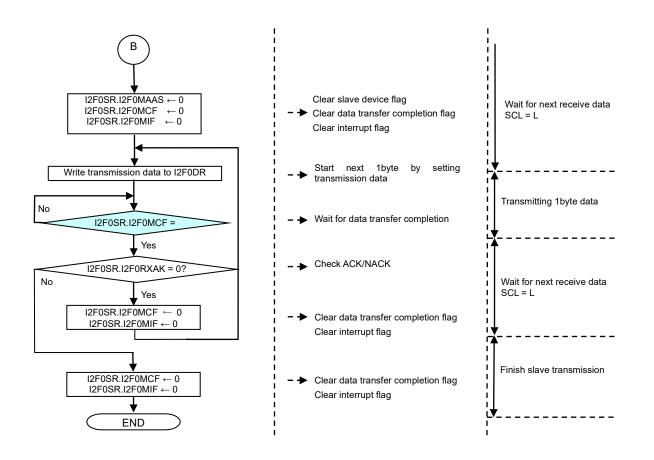

| 20.3.3.                  | Flow of Slave Transmission                                            |         |

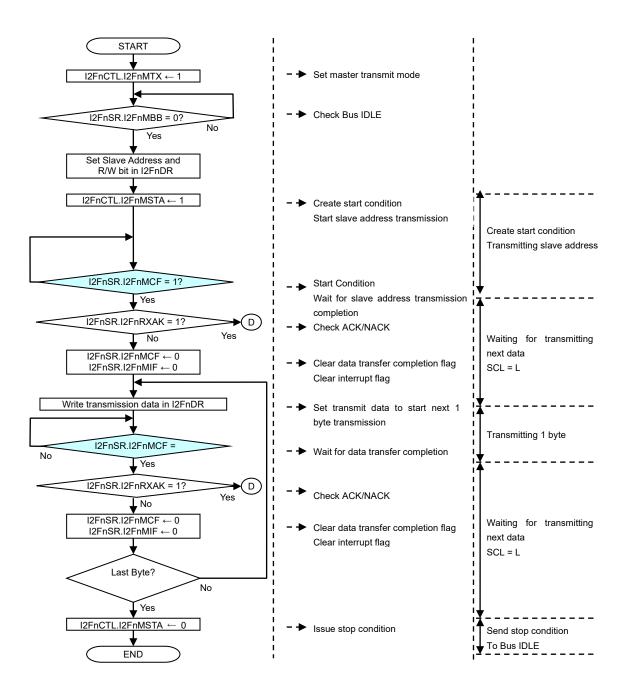

| 20.3.4.                  | Flow of Master Transmission                                           |         |

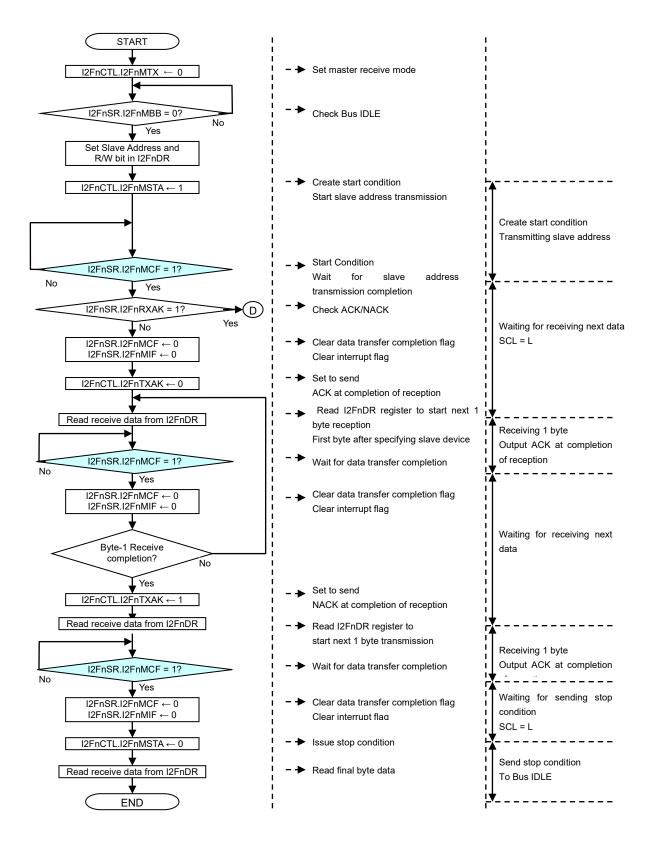

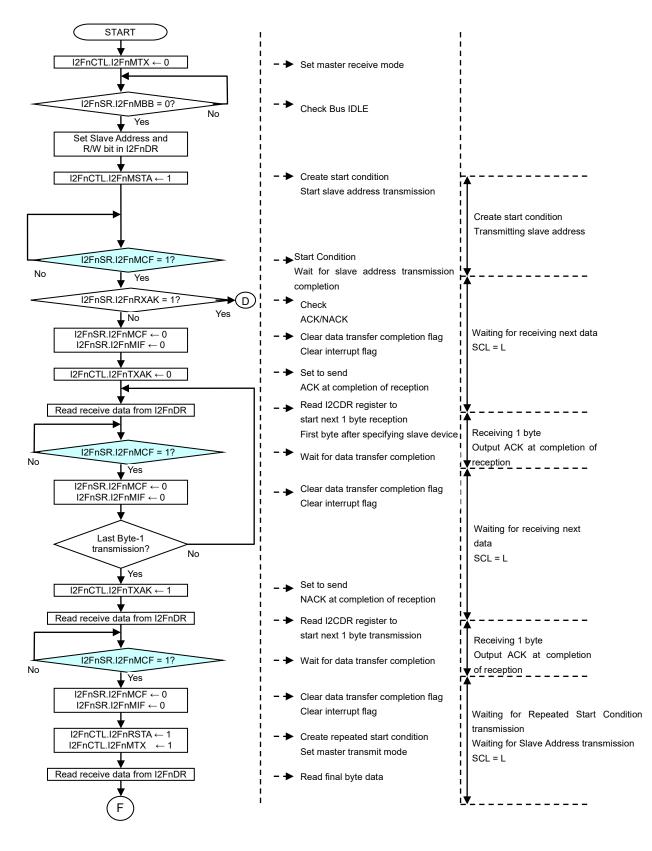

| 20.3.5.                  | Flow of Master Reception                                              |         |

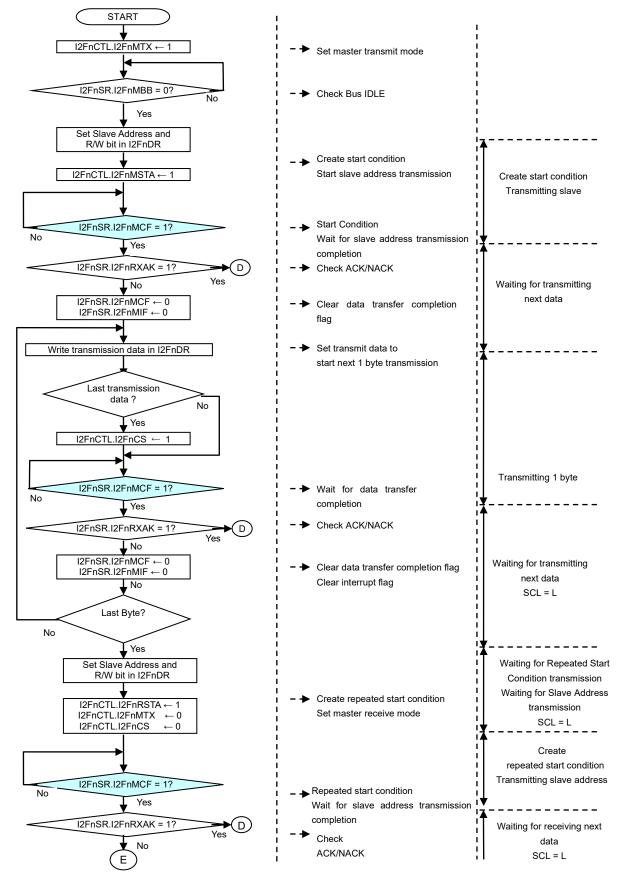

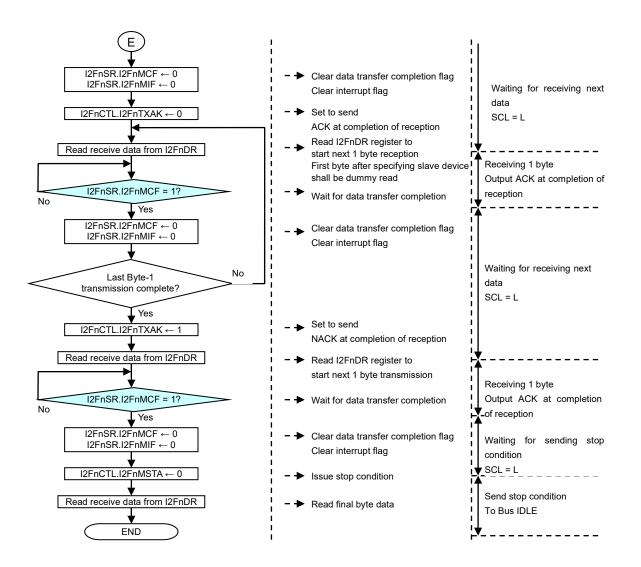

| 20.3.6.                  | Flow of Compound Mode (Receiving by Master after Transmitting from    |         |

|                          | 20-32                                                                 |         |

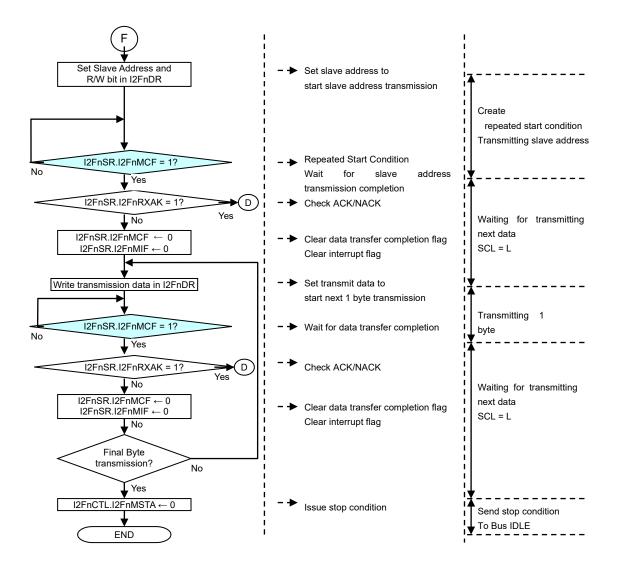

| 20.3.7.                  | Flow of Compound Mode (Transmitting from Master after Receiving by    | Master) |

|                          | 20-34                                                                 |         |

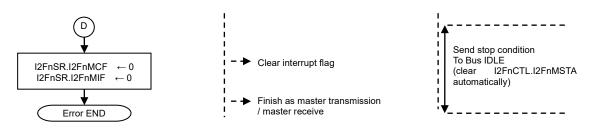

| 20.3.8.                  | Flow of NACK Recieving                                                | 20-35   |

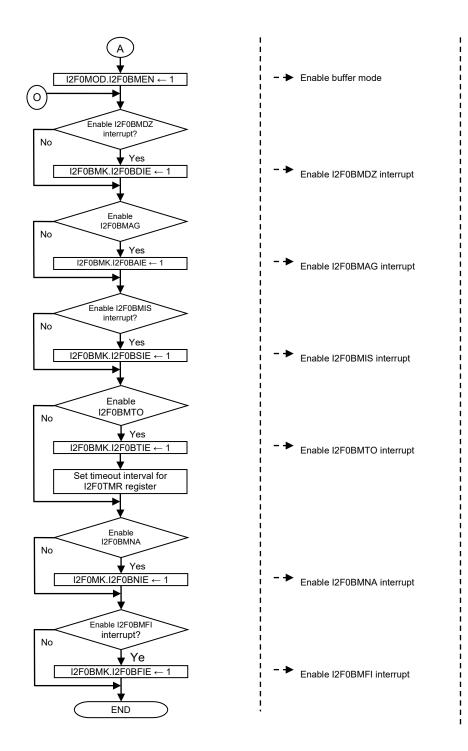

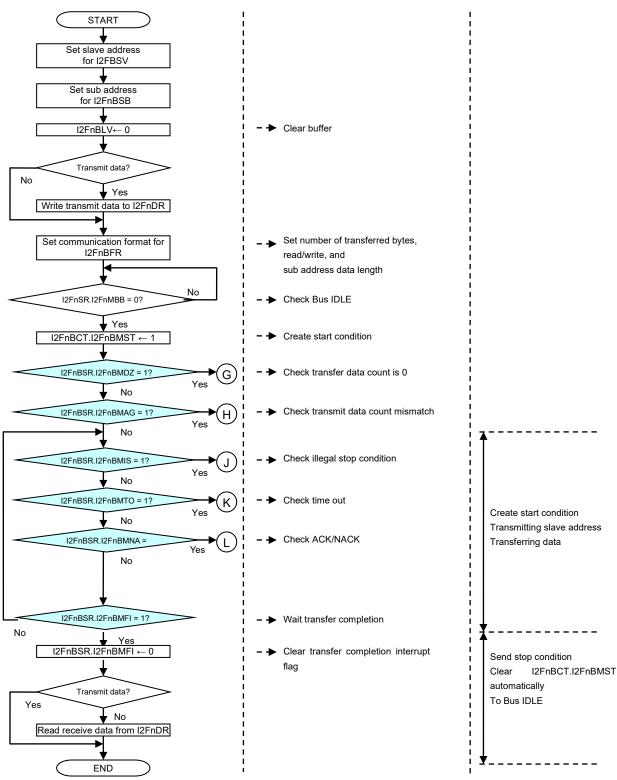

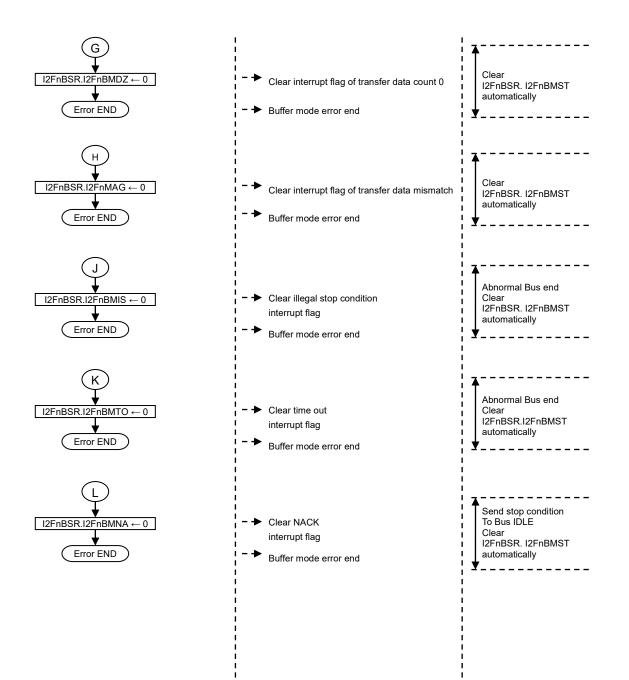

| 20.3.9.                  | Flow When Using Buffer Mode                                           | 20-36   |

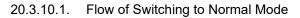

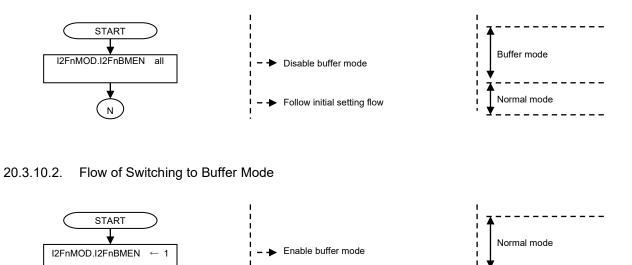

| 20.3.10.                 | Flow of Mode Switching                                                | 20-38   |

|                          | 0.1. Flow of Switching to Normal Mode                                 |         |

| 20.3.10                  | 0.2. Flow of Switching to Buffer Mode                                 | 20-38   |

| 20.4. Wa                 | veform in Each Mode                                                   | 20-39   |

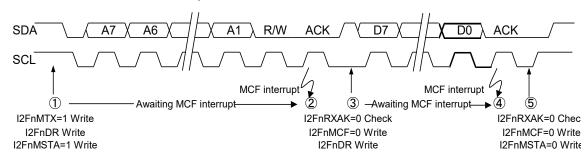

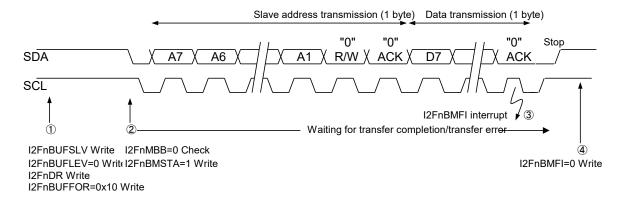

| 20.4.1.                  | Waveform Transmitted by Master                                        | 20-39   |

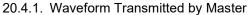

| 20.4.2.                  | Waveform Received by Master                                           | 20-39   |

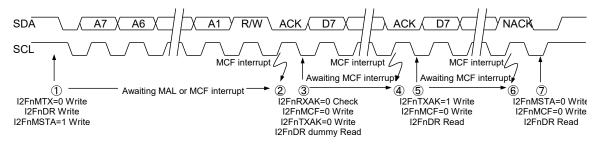

| 20.4.3.                  | Waveform Transmitted by Slave                                         | 20-39   |

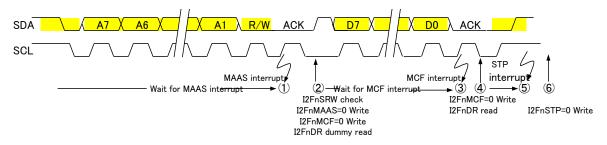

| 20.4.4.                  | Waveform Received by Slave                                            | 20-39   |

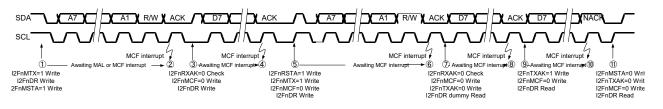

| 20.4.5.                  | Waveform of Compound Format (Master Transmission + Master Reception). | 20-40   |

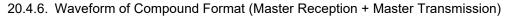

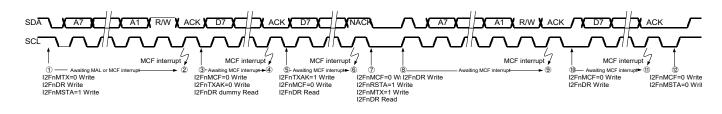

| 20.4.6.                  | Waveform of Compound Format (Master Reception + Master Transmission). | 20-40   |

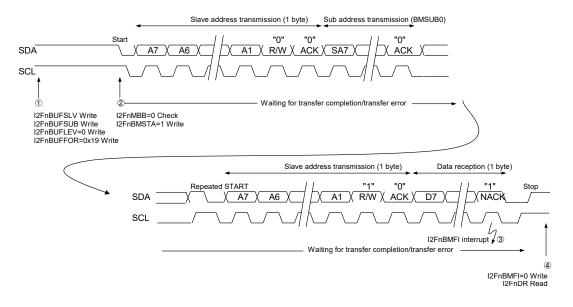

| 20.4.7.                  | Waveform 1 When Using Buffer Mode                                     |         |

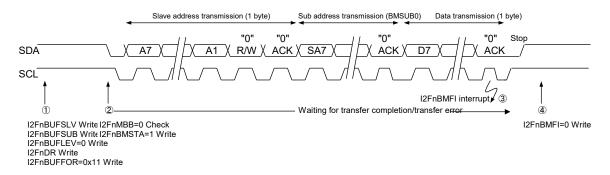

| 20.4.8.                  | Waveform 2 When Using Buffer Mode                                     | 20-41   |

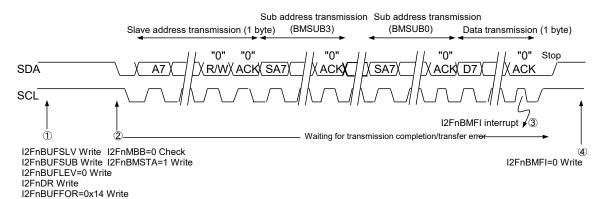

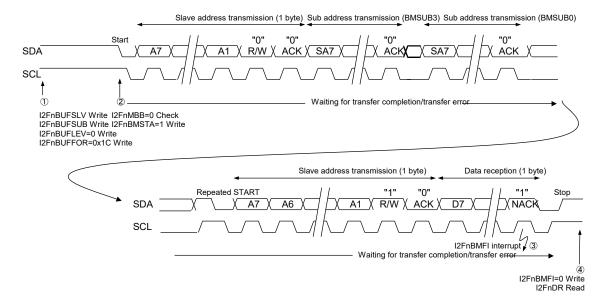

| 20.4.9.                  | Waveform 3 When Using Buffer Mode                                     | 20-41   |

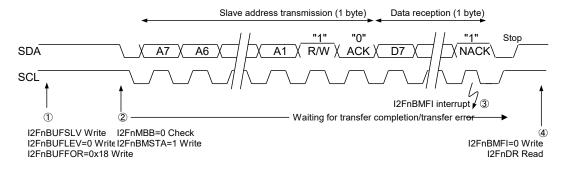

| 20.4.10.                 | Waveform 4 When Using Buffer Mode                                     | 20-42   |

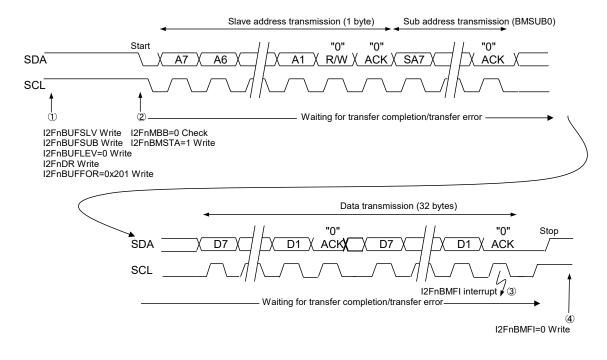

| 20.4.11.                 | Waveform 5 When Using Buffer Mode                                     | 20-42   |

| 20.4.12.                 | Waveform 6 When Using Buffer Mode                                     | 20-43   |

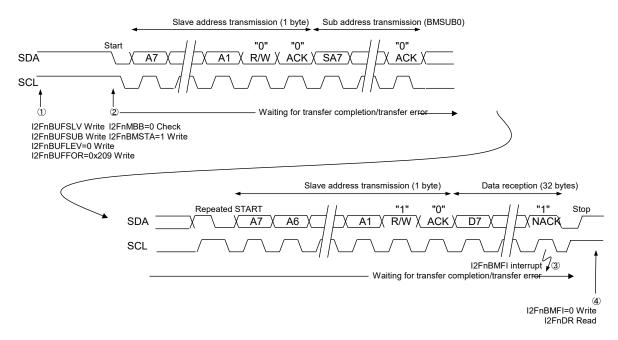

| 20.4.13.                 | Waveform 7 When Using Buffer Mode                                     | 20-43   |

#### ML630Q464/Q466 User's Manual Contents

| 20.4.1 | 14. Waveform 8 When Using Buffer Mode | 20-44 |

|--------|---------------------------------------|-------|

|        | Restrictions                          |       |

| 21. USB DE | VICE                                                   | 21-1   |

|------------|--------------------------------------------------------|--------|

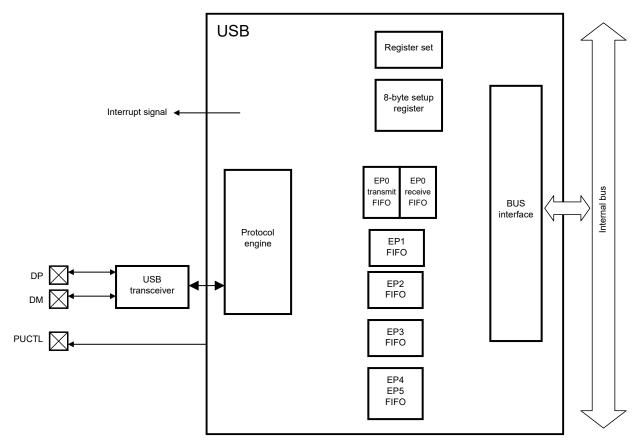

| 21.1. Gen  | eral Description                                       | 21-2   |

| 21.1.1.    | Features                                               | 21-2   |

| 21.1.2.    | Configuration                                          | 21-3   |

| 21.1.3.    | List of Pins                                           | 21-4   |

| 21.2. Des  | cription of Registers                                  | 21-5   |

|            | List of Registers                                      |        |

|            | bmRequestType Set-up Register (BMREQUESTTYPE)          |        |

|            | bRequest Set-up register (BREQUEST)                    |        |

| 21.2.4.    | wValueLSB Set-up register (WVALUELSB)                  | 21-10  |

| 21.2.5.    | wValueMSB Set-up register (WVALUEMSB)                  | 21-10  |

| 21.2.6.    | wIndexLSB Set-up register (WINDEXLSB)                  | .21-11 |

| 21.2.7.    | wIndexMSB Set-up register (WINDEXMSB)                  |        |

| 21.2.8.    | wLengthLSB Set-up register (WLENGTHLSB)                | 21-12  |

| 21.2.9.    | wLengthMSB Set-up register (WLENGTHMSB)                |        |

|            | Device address register (DVCADR)                       |        |

|            | Interrupt Status Register 1 (INTSTAT1)                 |        |

|            | Interrupt Status Register 2 (INTSTAT2).                |        |

|            | Interrupt Enable Register 1 (INTENBL1)                 |        |

|            | Interrupt Enable Register 2 (INTENBL2)                 |        |

| 21.2.15.   | Isochronous (ISO) Mode Selection Register (ISOMODESEL) | 21-22  |

| 21.2.16.   | Frame Number Register LSB (FRAMELSB)                   | 21-23  |

| 21.2.17.   | Frame Number Register MSB (FRAMEMSB)                   | 21-23  |

| 21.2.18.   | System Control Register (SYSCON)                       |        |

|            | Polarity Select Register (POLSEL)                      |        |

| 21.2.20.   | Oscillation Test Register (OSCTEST)                    |        |

| 21.2.21.   | Transmit Clock Control Register (TXCLKCONT)            |        |

| 21.2.22.   | EP0 Configuration Register (EP0CONF)                   |        |

| 21.2.23.   | EPn Configuration Register (EPnCONF: $n = 1$ to 5)     |        |

| 21.2.24.   | EP0 Control Register (EP0CONT)                         |        |

| 21.2.25.   | EPn Control Register (EPnCONT: $n = 1$ to 5)           |        |

| 21.2.26.   | EPO Payload Register (EPOPLD)                          |        |

|            | EPn Payload Register (EPnPLD: $n = 1, 2$ )             |        |

|            | EP3 Payload Register (EP3PLD)                          |        |

| 21.2.29.   | EPm Payload Register (EPmPLD: $m = 4, 5$ )             |        |

| 21.2.30.   | EP0 Receive Byte Counter (EP0RXCNT)                    |        |

| 21.2.31.   | EPn Receive Byte Counter (EPnRXCNT: $n = 1, 2$ )       |        |

| 21.2.32.   | EP3 Receive Byte Counter (EP3RXCNT)                    |        |

| 21.2.33.   | EPm Receive Byte Counter (EPmRXCNT: m = 4, 5)          | 21-41  |

| 21.2.34.   | EPO Status Register (EPOSTAT)                          |        |

| 21.2.35.   | EPn Status Register (EPnSTAT: $n = 1, 2, 4, 5$ )       |        |

| 21.2.36.   | EP3 Status Register (EP3STAT)                          |        |

| 21.2.37.   | EP0 transmit FIFO (EP0TXFIFO)                          |        |

| 21.2.38.   | EP0 Receive FIFO (EP0RXFIFO)                           |        |

| 21.2.39.   | EP1 Transmit/Receive FIFO (EP1FIFO)                    |        |

| 21.2.40.   | EP2 Transmit/Receive FIFO (EP2FIFO)                    |        |

| 21.2.41.   | EP3 Transmit/Receive FIFO (EP3FIFO)                    |        |

| 21.2.42.   | EP4 Transmit/Receive FIFO (EP4FIFO)                    |        |

| 21.2.43.   | EP5 Transmit/Receive FIFO (EP5FIFO)                    |        |

| 21.3. Des | scription of Operation                                                    | 21-55  |

|-----------|---------------------------------------------------------------------------|--------|

| 21.3.1.   | USB Interface                                                             | 21-55  |

| 21.3.2.   | USB Transfer Mode                                                         | 21-55  |

| 21.3.3.   | Endpoint and FIFO                                                         | 21-56  |

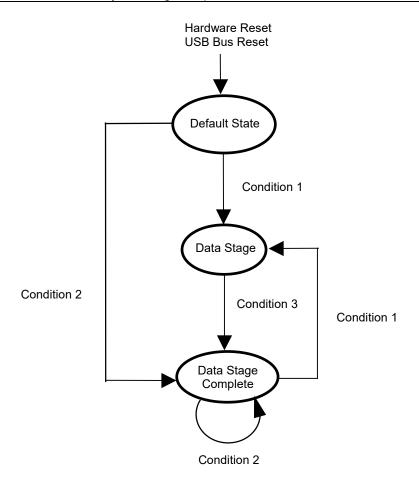

| 21.3.4.   | Operation of Control Transfer                                             | 21-57  |

| 21.3.5.   | Data Packet Transmit/Receive Procedures of Bulk Transfer and Interrupt Tr | ansfer |

|           | 21-58                                                                     |        |

| 21.3.6.   | Data Packet Transmit/Receive Procedures of Isochronous Transfer           | 21-59  |

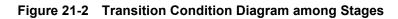

| 21.3.7.   | Packets and Packet Size                                                   | 21-60  |

| 21.3.8.   | Interrupt                                                                 | 21-61  |

| 21.3.8.1  | . Set-up Ready Interrupt                                                  | 21-62  |

| 21.3.8.2  | EP0 Receive Packet Ready Interrupt                                        | 21-62  |

| 21.3.8.3  | EP0 Transmit Packet Ready Interrupt                                       | 21-63  |

| 21.3.8.4  | . Receive Packet Ready Interrupt (EP1, EP2, EP3, EP4 Bulk, EP5 Bulk)      | 21-63  |

| 21.3.8.5  | . Transmit Packet Ready Interrupt (EP1, EP2, EP3, EP4 Bulk, EP5 Bulk)     | 21-64  |

| 21.3.8.6  | SOF Interrupt                                                             | 21-64  |

| 21.3.8.7  | USB Bus Reset Assert Interrupt                                            | 21-65  |

| 21.3.8.8  | USB Bus Reset De-assert Interrupt                                         | 21-65  |

| 21.3.8.9  | . Suspended State Interrupt                                               | 21-65  |

| 21.3.8.1  | 0. Awake Interrupt                                                        | 21-65  |

| 21.3.9.   | Power Down                                                                | 21-66  |

| 21.3.9.1  | . Power Down Modes and Settings                                           | 21-66  |

| 21.3.9.2  | . USB Suspend ⇔ Awake Operation                                           | 21-67  |

| 21.3.10.  | Operation of Dual-Side FIFO Configuration in Bulk Transfer                | 21-68  |

| 21.3.11.  | Error Processing and Retry Operation                                      | 21-70  |

|           |                                                                           |        |

| 22. Port     |                                                 | 22-1    |

|--------------|-------------------------------------------------|---------|

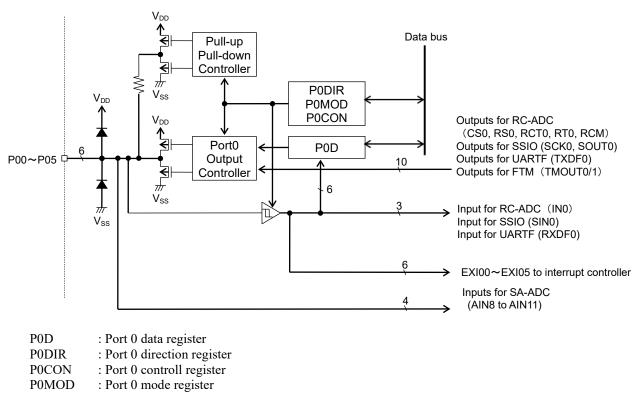

| 22.1. PORT0  |                                                 | 22-1    |

| 22.1.1. Ove  | erview                                          | 22-1    |

| 22.1.1.1. F  | 'eatures                                        | 22-1    |

| 22.1.1.2. C  | Configuration                                   | 22-2    |

| 22.1.1.3. L  | ist of Pins                                     | 22-3    |

| 22.1.2. Des  | scription of Registers                          | 22-4    |

|              | ist of Registers                                |         |

|              | Port 0 Data Register (P0D)                      |         |

|              | Port 0 Direction Register (P0DIR)               |         |

|              | Port 0 Control Register (P0CON)                 |         |

| 22.1.2.5. P  | Port 0 Mode Register (P0MOD)                    | 22-8    |

| 22.1.3. Des  | scription of Operation                          | . 22-10 |

| 22.1.3.1. In | nput / Output Port Function                     | . 22-10 |

| 22.1.3.2. P  | Primary Function Except for Input / Output Port | . 22-10 |

| 22.1.3.3. S  | econdary, Tertiary and Quaternary Functions     | . 22-10 |

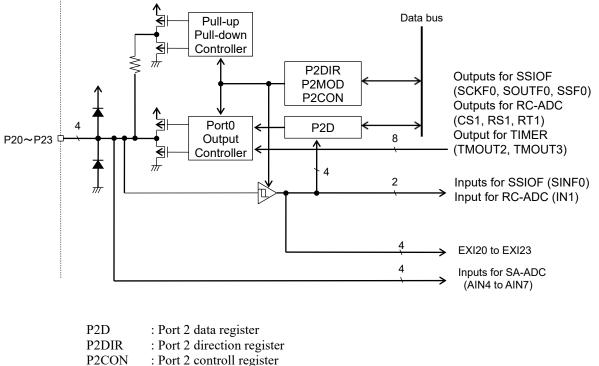

| 22.2. PORT2  |                                                 | 22-11   |

| 22.2.1. Ove  | erview                                          | 22-11   |

| 22.2.1.1. F  | 'eatures                                        | 22-11   |

| 22.2.1.2. C  | Configuration                                   | . 22-12 |

| 22.2.1.3. L  | ist of Pins                                     | . 22-13 |

| 22.2.2. Des  | scription of Registers                          | . 22-14 |

|              | ist of Registers                                |         |

| 22.2.2.2. P  | Port 2 Data Register (P2D)                      | 22-15   |

| 22.2.2.3. P  | Port 2 Direction Register (P2DIR)               | 22-16   |

| 22.2.2.4. P  | Port 2 Control Register (P2CON)                 | . 22-17 |

|            |                                                       | 22.10   |

|------------|-------------------------------------------------------|---------|

|            | Port 2 Mode Register (P2MOD)                          |         |

|            | Description of Operation                              |         |

|            | Input/Output Port Functions                           |         |

|            | Primary Function Except for Input/Output Port         |         |

|            | Secondary, Tertiary and Quaternary Functions          |         |

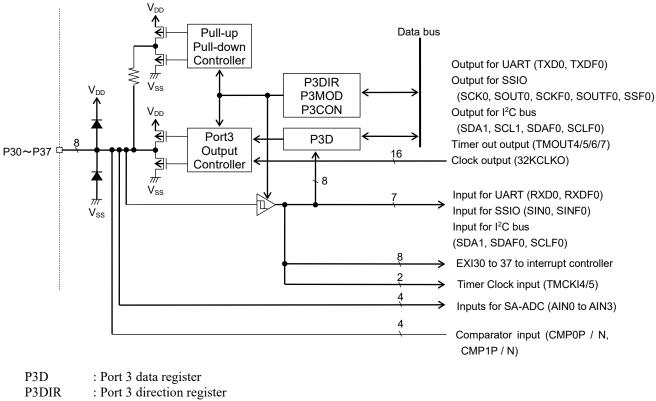

|            | ГЗ                                                    |         |

|            | Overview                                              |         |

|            | Features                                              |         |

|            | Configuration                                         |         |

| 22.3.1.3.  | List of Pins                                          | 22 - 23 |

| 22.3.2. I  | Description of Registers                              | 22 - 24 |

|            | List of Registers                                     |         |

| 22.3.2.2.  | Port 3 Data Register (P3D)                            | 22 - 25 |

| 22.3.2.3.  | Port 3 Direction Register (P3DIR)                     | 22-26   |

| 22.3.2.4.  | Port 3 Control Register (P3CON)                       | 22-27   |

|            | Port 3 Mode Register (P3MOD)                          |         |

|            | Description of Operation                              |         |

|            | Input/Output Port Functions                           |         |

|            | Primary Function Except for Input/Output Port         |         |

|            | Secondary, Tertiary, Quaternary and Quinary Functions |         |

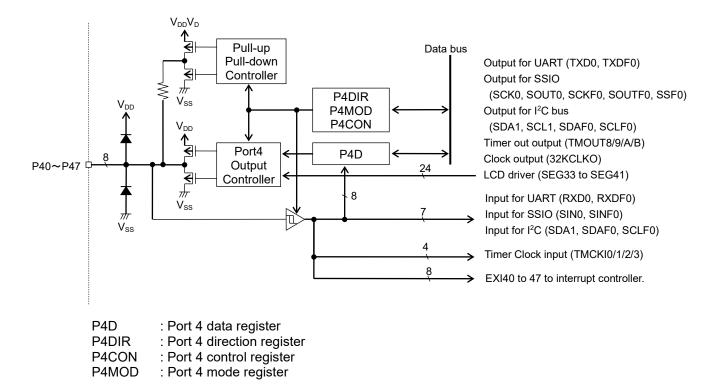

|            | $\Gamma 4$                                            |         |

|            | erview                                                |         |

|            | Features                                              |         |

|            |                                                       |         |

|            | Configuration                                         |         |

|            | List of Pins                                          |         |

|            | Description of Registers                              |         |

|            | List of Registers                                     |         |

|            | Port 4 Data Register (P4D)                            |         |

|            | Port 4 Direction Register (P4DIR)                     |         |

|            | Port 4 Control Register (P4CON)                       |         |

|            | Port 4 Mode Register (P4MOD)                          |         |

|            | Description of Operation                              |         |

|            | Input/Output Port Functions                           |         |

| 22.4.3.2.  | Primary Function Except for Input/Output Port         | 22-42   |

| 22.4.3.3.  | Secondary, Tertiary and Quaternary Functions          | 22-42   |

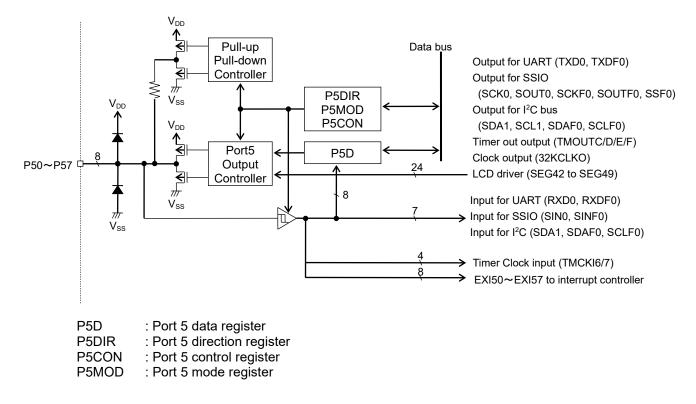

| 22.5. POR' | Г5                                                    | 22 - 43 |

| 22.5.1. C  | Overview                                              | 22-43   |

| 22.5.1.1.  | Features                                              | 22-43   |

| 22.5.1.2.  | Configuration                                         | 22-44   |

| 22.5.1.3.  | List of Pins                                          | 22-45   |

|            | Description of Registers                              |         |

|            | List of Registers                                     |         |

|            | Port 5 Data Register (P5D)                            |         |

|            | Port 5 Direction Register (P5DIR)                     |         |

|            | Port 5 Control Register (P5CON)                       |         |

|            | Port 5 Mode Register (P5MOD)                          |         |

|            | Description of Operation                              |         |

|            | Input/Output Port Functions                           |         |

|            |                                                       |         |

|            | Primary Function Except for Input/Output Port         |         |

|            | Secondary, Tertiary, Quaternary and Quinary Functions |         |

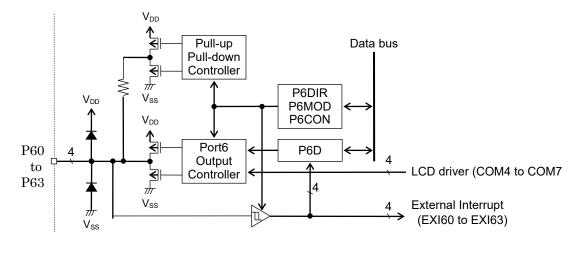

|            | Γ6                                                    |         |

|            | )verview                                              |         |

| 22.6.1.1.  | Features                                              | 22-54   |

#### ML630Q464/Q466 User's Manual Contents

| 22.6.1.2. | Configuration                                 | . 22-55 |

|-----------|-----------------------------------------------|---------|

| 22.6.1.3. | List of Pins                                  | . 22-55 |

| 22.6.2. I | Description of Registers                      | . 22-56 |

| 22.6.2.1. | List of Resigers                              | . 22-56 |

| 22.6.2.2. | Port 6 Data Register (P6D)                    | . 22-57 |

| 22.6.2.3. | Port 6 Direction Register (P6DIR)             | . 22-58 |

| 22.6.2.4. | Port 6 Control Register (P6CON)               | . 22-59 |

| 22.6.2.5. | Port 6 Mode Register (P6MOD)                  | . 22-60 |

| 22.6.3. I | Description of Operation                      | . 22-61 |

| 22.6.3.1. | Input/Output Port Functions                   | . 22-61 |

| 22.6.3.2. | Primary Function Except for Input/Output Port | . 22-61 |

| 22.6.3.3. | Secondary Function                            | . 22-61 |

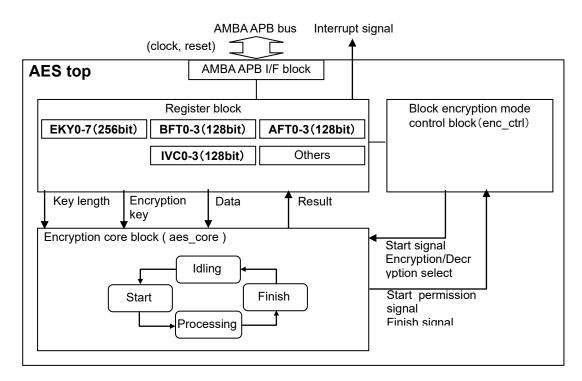

### Chapter 23

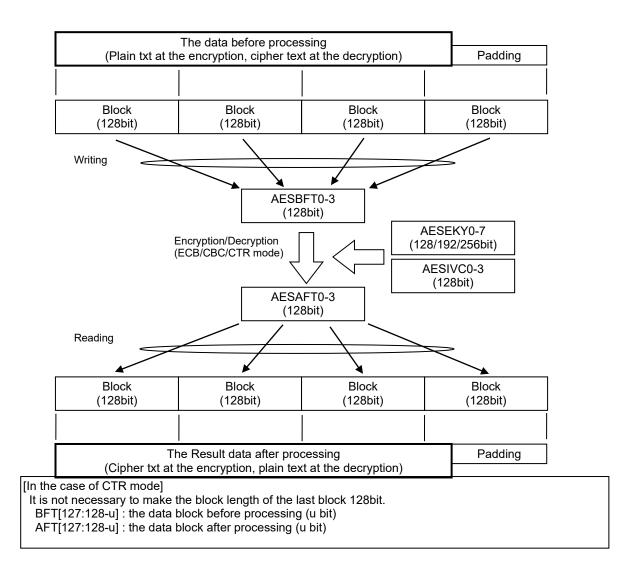

| 23. AES  |                                                                 |       |

|----------|-----------------------------------------------------------------|-------|

|          | eneral Description                                              |       |

| 23.1.1.  | Features                                                        |       |

| 23.1.2.  | Configuration                                                   |       |

| 23.2. De | escription of Registers                                         |       |

| 23.2.1.  | List of Registers                                               |       |

| 23.2.2.  | Interrupt Request Register (AESIREQ)                            |       |

| 23.2.3.  | Interrupt Mask Register (AESIMSK)                               |       |

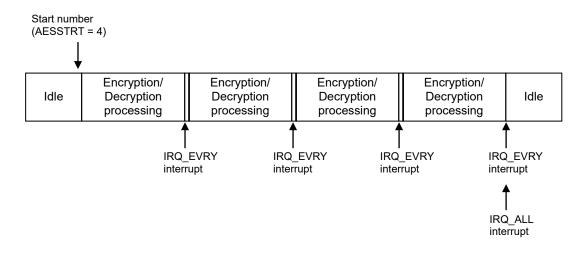

| 23.2.4.  | Starting Number Register (AESSTRT)                              |       |

| 23.2.5.  | Status Register (AESSTAT)                                       |       |

| 23.2.6.  | Control Register (AESCTRL)                                      |       |

| 23.2.7.  | Initialization Vector & Counter Register n (AESIVCn (n=0 to 3)) | 23-11 |

| 23.2.8.  | Before Processing Data Register n (AESBFTn (n=0 to 3))          |       |

| 23.2.9.  | After Processing Data Register n (AESAFTn (n=0 to 3))           |       |

| 23.2.10. | Encryption Key Register n (AESEKYn (n=0 to 7))                  |       |

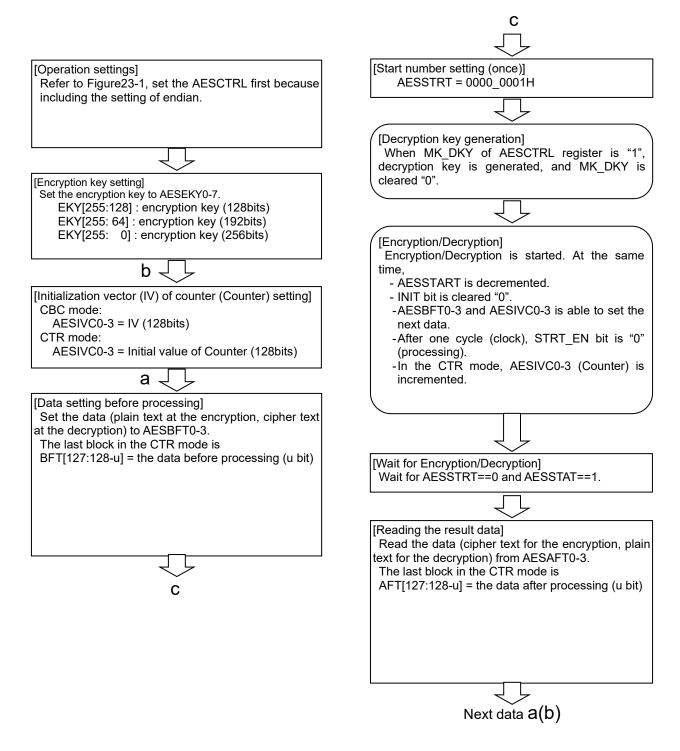

| 23.3. De | escription of Operation                                         |       |

| 23.3.1.  | AES basic control flow                                          |       |

| 23.3.2.  | AES encryption                                                  |       |

| 23.3.3.  | Interrupt                                                       |       |

# Chapter 24

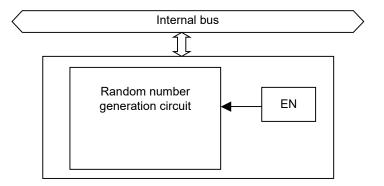

| 24. Random Number Generator                              |  |

|----------------------------------------------------------|--|

| 24.1. Overview                                           |  |

| 24.1.1. Features                                         |  |

| 24.1.2. Configuration                                    |  |

| 24.2. Description of Registers                           |  |

| 24.2.1. List of Registers                                |  |

| 24.2.2. Random Number Generating Register (RNDDT)        |  |

| 24.2.3. Random Number Generating Enable Register (RNDEN) |  |

| 5 6 7 7                                                  |  |

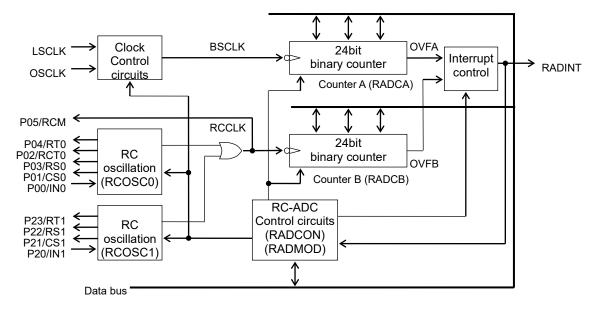

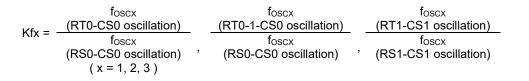

| 25. RC Oscillation Type A/D Converter (RC-ADC) | 25-1 |

|------------------------------------------------|------|

| 25.1. General Description                      | 25-1 |

| 25.1.1. Features                               | 25-1 |

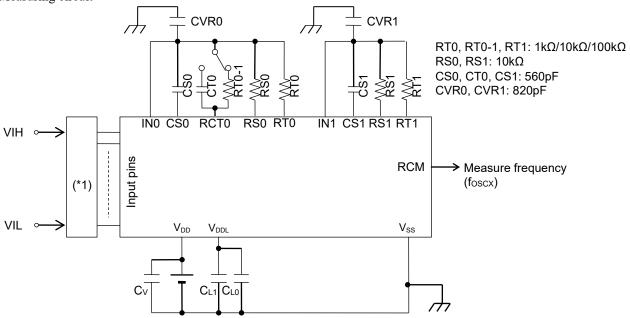

| 25.1.2. Configuration                          | 25-1 |

| 25.1.3. List of Pins                           | 25-2 |

| 25.2. Description of Registers                 | 25-3 |

| 25.2.1. List of Registers                      |      |

| 25.2.2. | RC-ADC Counter A Register (RADCA)                           |  |

|---------|-------------------------------------------------------------|--|

| 25.2.3. | RC-ADC Counter B Register (RADCB)                           |  |

| 25.2.4. | RC-ADC Mode Register (RADMOD)                               |  |

| 25.2.5. | RC-ADC Control Register (RADCON)                            |  |

| 25.2.6. | RC-ADC Trigger Register (RADTRG)                            |  |

| 25.2.7. | RC-ADC Continuous Measurement Register n (RADCMn) n=0 to 4. |  |

| 25.2.8. | RC-ADC Result Counter Register (RADRC)                      |  |

|         | Description of Operation                                    |  |

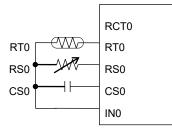

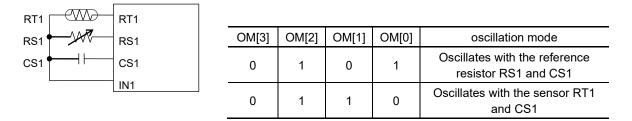

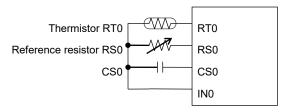

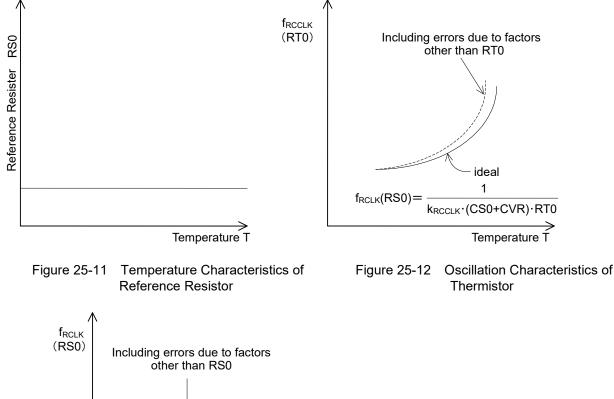

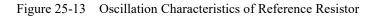

| 25.3.1. | RC Oscillator Circuits                                      |  |

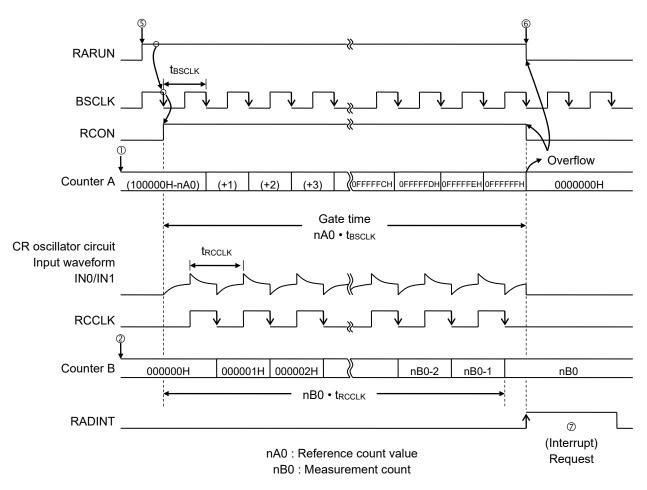

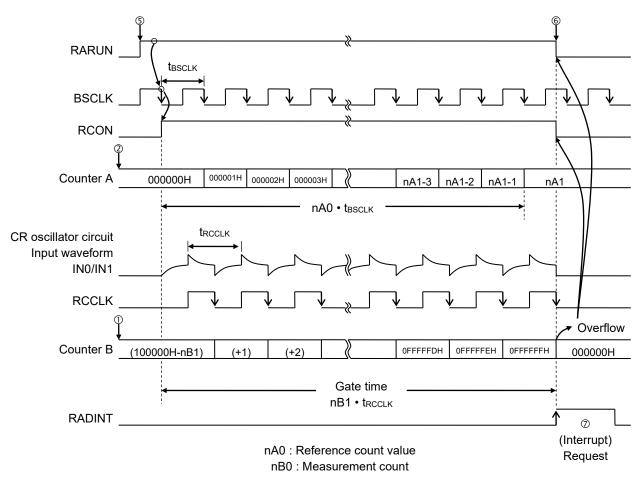

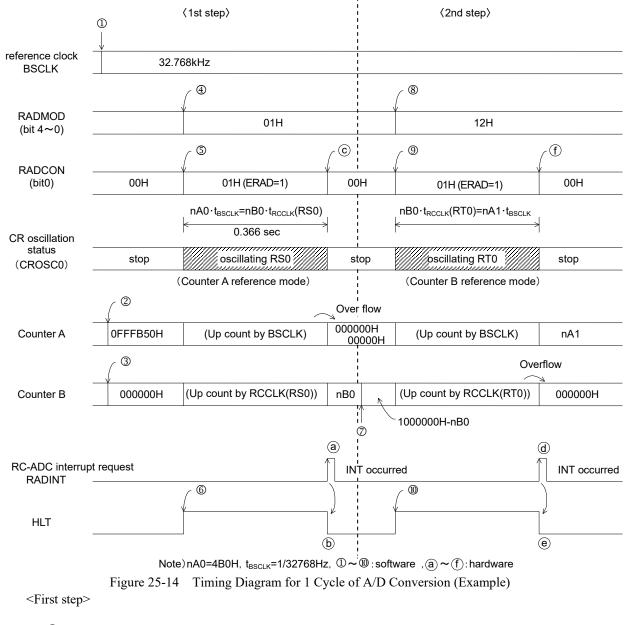

| 25.3.2. | Counter A/B Reference Modes                                 |  |

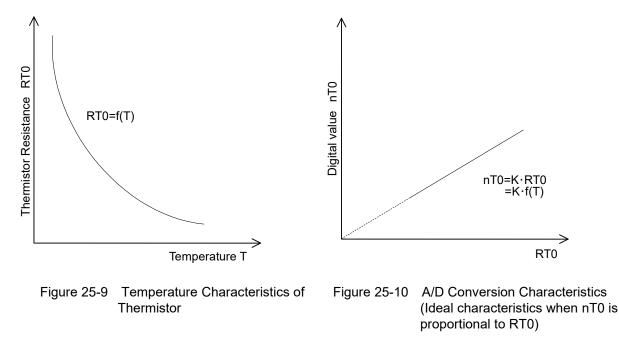

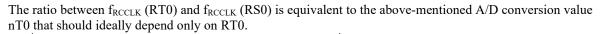

| 25.3.3. | Example of Use of RC Oscillation Type A/D Converter         |  |

|         | Monitoring RC Oscillation                                   |  |

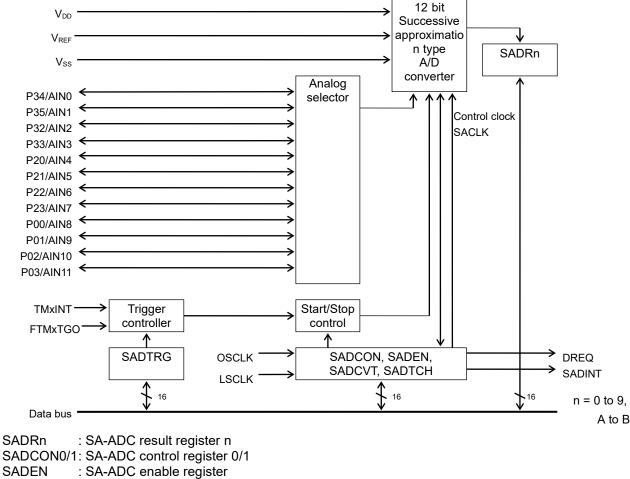

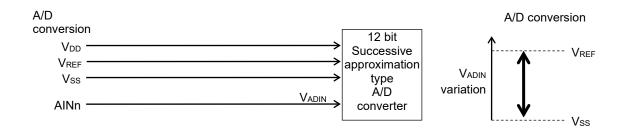

| 26. Su | accessive Approximation Type A/D Converter (SA-ADC)             |  |

|--------|-----------------------------------------------------------------|--|

| 26.1.  | General Description                                             |  |

| 26.1   | .1. Features                                                    |  |

| 26.1   | .2. Configuration                                               |  |

| 26.1   | .3. List of Pins                                                |  |

| 26.2.  | Description of Registers                                        |  |

| 26.2   | .1. List of Registers                                           |  |

| 26.2   | .2. SA-ADC Result Register n (SADRn) n=0 to 9, A, B             |  |

| 26.2   |                                                                 |  |

| 26.2   | .4. SA-ADC Control Register1 (SADCON1)                          |  |

| 26.2   | 5. SA-ADC Enable Register (SADEN)                               |  |

| 26.2   | .6. SA-ADC Touch Sensor Register (SADTCH)                       |  |

| 26.2   | .7. SA-ADC Trigger Register (SADTRG)                            |  |

| 26.2   |                                                                 |  |

| 26.2   |                                                                 |  |

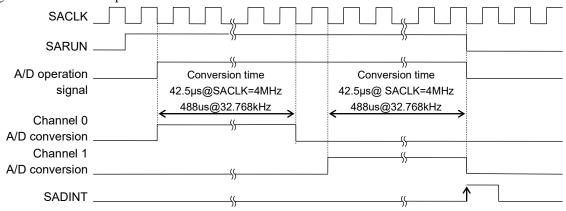

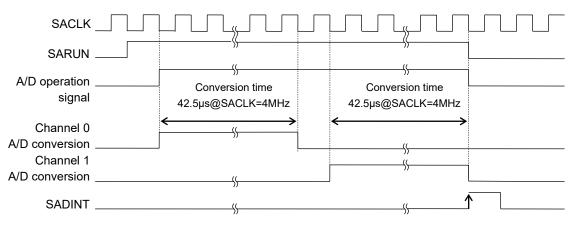

| 26.3.  | Description of Operation                                        |  |

| 26.3   | 1. Setting of A/D Conversion Channels                           |  |

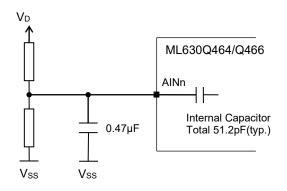

| 26.3   | 2. Operation of the Successive Approximation Type A/D Converter |  |

| 26.3   | .3. Capacitive Touch sensor mode operation                      |  |

| 26.3   | .4. Notes on Use of SA-ADC                                      |  |

| 27. LCD 1 | Driver                                                                 | 27-1                       |

|-----------|------------------------------------------------------------------------|----------------------------|

| 27.1. C   | )verview                                                               | 27-1                       |

| 27.1.1.   | Features                                                               | 27-3                       |

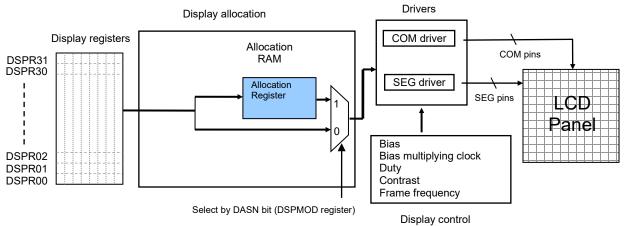

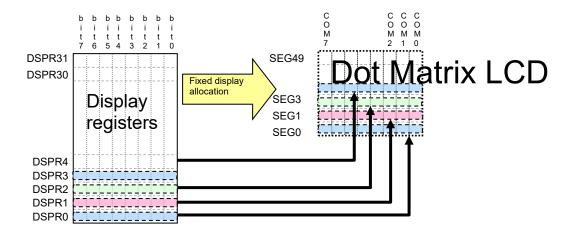

| 27.1.2.   | Configuration of the LCD Drivers                                       | 27-4                       |

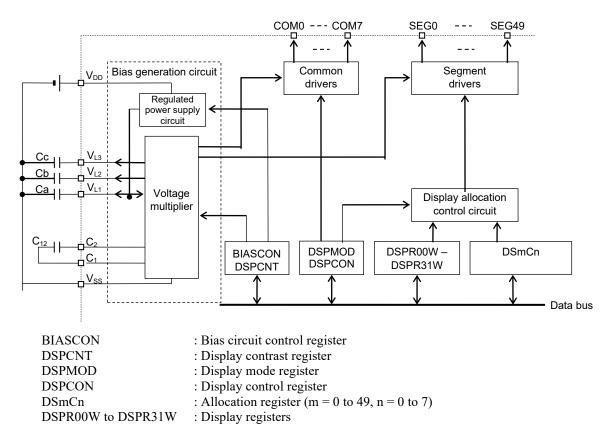

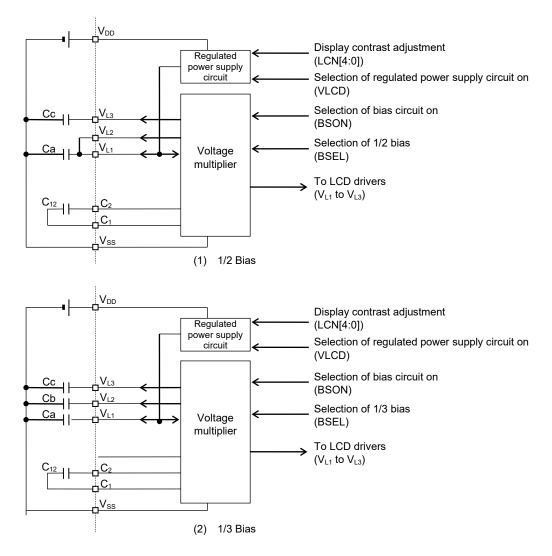

| 27.1.3.   | Configuration of the Bias Generation Circuit                           | 27-5                       |

| 27.1.4.   | List of Pins                                                           | 27-6                       |

| 27.2. L   | Description of Registers                                               | 27-7                       |

| 27.2.1.   | List of Registers                                                      | 27-7                       |

| 27.2.2.   | Bias Circuit Control Register (BIASCON)                                | 27-8                       |

| 27.2.3.   | Display Contrast Register (DSPCNT)                                     | 27-10                      |

| 27.2.4.   | Display Mode Register 0 (DSPMOD)                                       | 27-12                      |

| 27.2.5.   |                                                                        |                            |

| 27.2.6.   | Display Registers 00 to 31 (DSPR00W to DSPR31W)                        | 27-15                      |

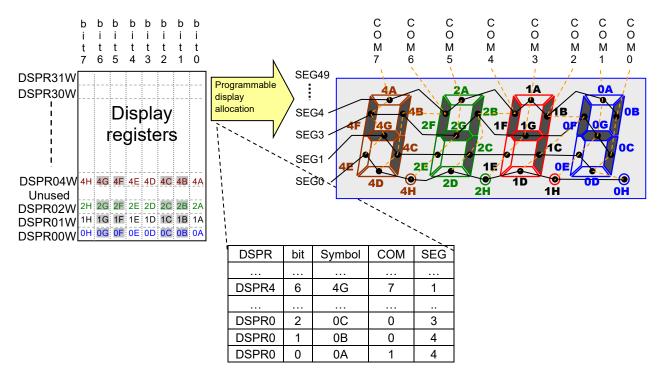

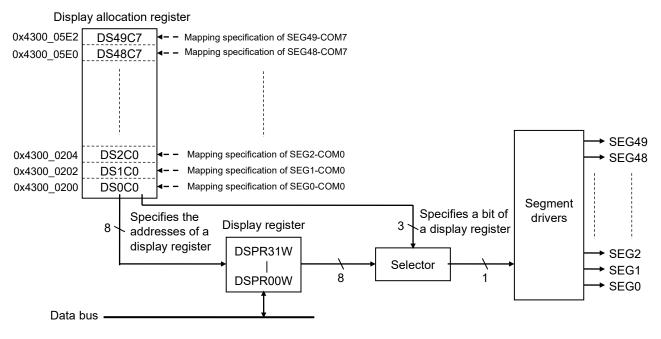

| 27.2.7.   | Display Allocation Register (DS0C0 to DS49C7)                          | 27-17                      |

| 27.3. L   | Description of Operation                                               |                            |

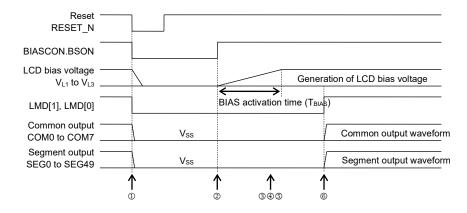

| 27.3.1.   | Operation of LCD Drivers and Bias Generation Circuit                   | 27-19                      |

| 27.3.2.   | Segment Mapping When the Programmable Display Allocation Function is U | $\operatorname{sed} 27-20$ |

#### ML630Q464/Q466 User's Manual Contents

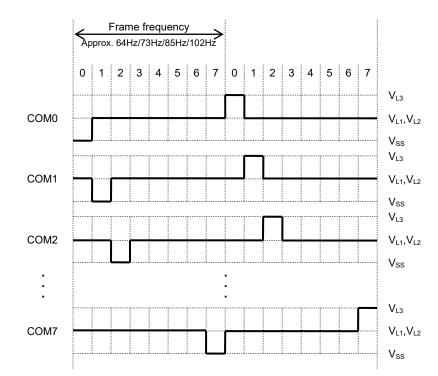

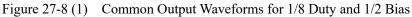

| 27.3.3. | Common Output Waveforms  | 27-22 |

|---------|--------------------------|-------|

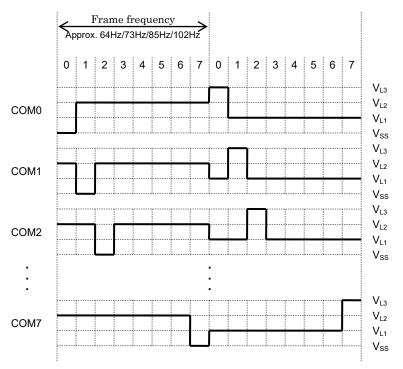

| 27.3.4. | Segment Output Waveforms | 27-23 |

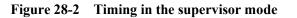

### Chapter 28

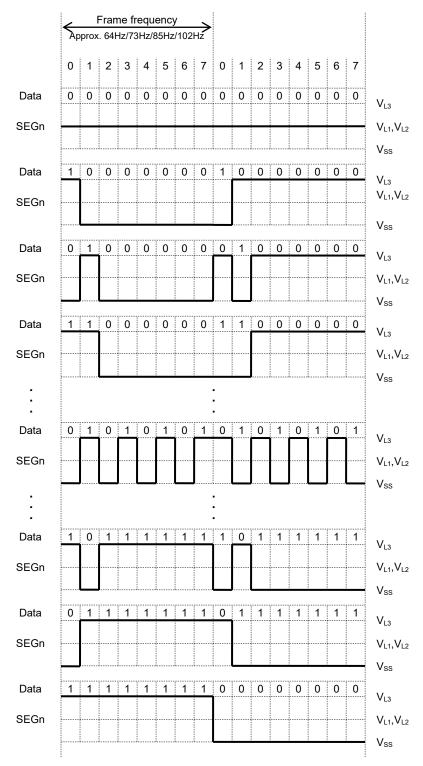

| 28. Analo | g Comparator                                     |  |

|-----------|--------------------------------------------------|--|

| 28.1. C   | Dverview                                         |  |

| 28.1.1.   | Features                                         |  |

| 28.1.2.   | Configuration                                    |  |

| 28.1.3.   | List of Pins                                     |  |

| 28.2. I   | Description of Registers                         |  |

|           | List of Registers                                |  |

| 28.2.2.   | Comparator n Control Register (CMPnCON : n=0,1)  |  |

| 28.2.3.   | Comparator n mode Registers (CMPnMOD : n=0,1)    |  |

| 28.2.4.   | Comparator Interrupt status Registers (CMPINTST) |  |

| 28.3. F   | unction description                              |  |

| 28.3.1.   | Comparator function                              |  |

|           | Supervisor mode                                  |  |

| 28.3.3.   | Single mode                                      |  |

| 28.3.4.   | Single monitor mode                              |  |

### Chapter 29

| 29.  | Flash  | Programming                                            |  |

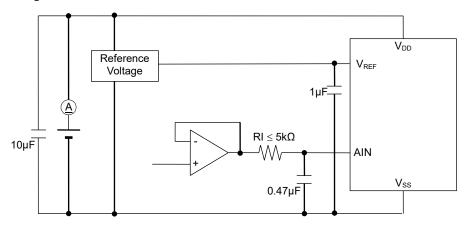

|------|--------|--------------------------------------------------------|--|