FEUL63Q2500-01

# ML63Q2500 Group User's Manual

1<sup>st</sup> Edition Issue Date: Jun. 20, 2025

# Notice

#### Precaution on using ROHM Products

- 1) When using ROHM Products, refer to the latest product information and ensure that usage conditions (absolute maximum ratings<sup>\*1</sup>, recommended operating conditions, etc.) are within the ranges specified. ROHM disclaims any and all liability for any malfunctions, failure or accident arising out of or in connection with the use of ROHM Products outside of such usage conditions specified ranges, or without observing precautions. Even if it is used within such usage conditions specified ranges, semiconductors can break down and malfunction due to various factors. Therefore, in order to prevent personal injury, fire or the other damage from break down or malfunction of ROHM Products, please take safety at your own risk measures such as complying with the derating characteristics, implementing redundant and fire prevention designs, and utilizing backups and fail-safe procedures.

- \*1: Absolute maximum ratings: a limit value that must not be exceeded even momentarily.

- 2) The Products specified in this document are not designed to be radiation tolerant.

- 3) Descriptions of circuits, software and other related information in this document are provided only to illustrate the standard operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. And the peripheral conditions must be taken into account when designing circuits for mass production. ROHM disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, and other related information.

- 4) No license, expressly or implied, is granted hereby under any intellectual property rights or other rights of ROHM or any third party with respect to ROHM Products or the information contained in this document (including but not limited to, the Product data, drawings, charts, programs, algorithms, and application examples, etc.). Therefore, ROHM shall have no responsibility whatsoever for any dispute, concerning such rights owned by third parties, arising out of the use of such technical information.

- 5) ROHM intends our Products to be used in a way indicated in this document. Please be sure to contact a ROHM sales office if you consider the use of our Products in different way from original use indicated in this document. For use of our Products in medical systems, please be sure to contact a ROHM representative and must obtain written agreement. Do not use our Products in applications which may directly cause injuries to human life, and which require extremely high reliability, such as aerospace equipment, nuclear power control systems, and submarine repeaters, etc. ROHM disclaims any and all liability for any losses and damages incurred by you or third parties arising by using the Product for purposes not intended by us without our prior written consent.

- 6) Please use the Products in accordance with any applicable environmental laws and regulations, such as the RoHS Directive. ROHM shall have no responsibility for any damages or losses resulting non-compliance with any applicable laws or regulations.

- 7) When providing our Products and technologies contained in this document to other countries, you must abide by the procedures and provisions stipulated in all applicable export laws and regulations, including without limitation the US Export Administration Regulations and the Foreign Exchange and Foreign Trade Act.

- Please contact a ROHM sales office if you have any questions regarding the information contained in this document or ROHM's Products.

- 9) This document, in part or in whole, may not be reprinted or reproduced without prior consent of ROHM.

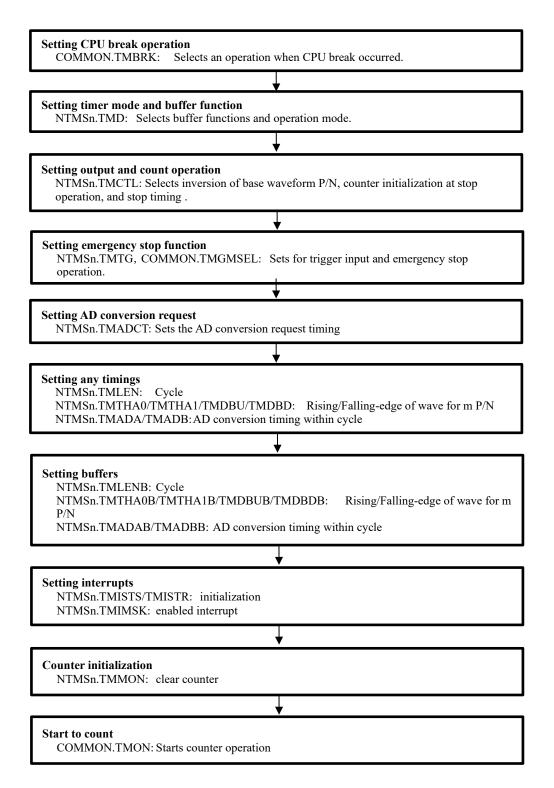

(Note) "ROHM" as used in this document means ROHM Co., Ltd.

#### **Other Precaution**

- 1) All information contained in this document is subject to change for the purpose of improvement, etc. without any prior notice. Before purchasing or using ROHM Products, please confirm the latest information with a ROHM sales office.

- 2) ROHM has used reasonable care to ensure the accuracy of the information contained in this document, however, ROHM shall have no responsibility for any damages, expenses or losses arising from inaccuracy or errors of such information.

TSZ72037.01.001

### Notes for product usage

Notes on this page are applicable to the all LAPIS TECHNOLOGY microcontroller products. For individual notes on each LAPIS TECHNOLOGY microcontroller product, refer to [Note] in the chapters of each user's manual.

The individual notes of each user's manual take priority over those contents in this page if they are different.

1. HANDLING OF UNUSED INPUT PINS Fix the unused input pins to the power pin or GND to prevent to cause the device performing wrong operation or increasing the current consumption due to noise, etc. If the handlings for the unused pins are described in the chapters, follow the instruction. STATE AT POWER ON 2.

At the power on, the data in the internal registers and output of the ports are undefined until the power supply voltage reaches to the recommended operating condition and "L" level is input to the reset pin. On LAPIS TECHNOLOGY microcontroller products that have the power on reset function, the data in the internal registers and output of the ports are undefined until the power on reset is generated. Be careful to design the application system does not work incorrectly due to the undefined data of internal registers and output of the ports.

- ACCESS TO UNUSED MEMORY 3. If reading from unused address area or writing to unused address area of the memory, the operations are not guaranteed.

- CHARACTERISTICS DIFFERENCE BETWEEN THE PRODUCT 4. Electrical characteristics, noise tolerance, noise radiation amount, and the other characteristics are different from each microcontroller product. When replacing from other product to LAPIS TECHNOLOGY microcontroller products, please evaluate enough the apparatus/system which implemented LAPIS TECHNOLOGY microcontroller products.

- 5. USE ENVIRONMENT

When using LAPIS TECHNOLOGY microcontroller products in a high humidity environment and an environment where dew condensation, take moisture-proof measures.

# Preface

This manual describes the operation of the hardware of the 32-bit microcontroller.

Please ensure that you refer to the latest versions.

- Cortex<sup>®</sup>-M0+ Technical Reference Manual (DDI0484C)

- Cortex<sup>®</sup>-M0+ Generic User Guide (DUI0662B)

The documents above are published by Arm Limited. Please ensure that you refer to the latest versions.

<sup>\*</sup> This product uses Super Flash® technology licensed from Silicon Storage Technology, Inc. Super Flash® is a registered trademark of Silicon Storage Technology, Inc.

<sup>\*</sup> Arm<sup>®</sup>, Cortex<sup>®</sup>, Thumb<sup>®</sup> are registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere. \* LAPIS TECHNOLOGY<sup>TM</sup>, Solist-AI<sup>TM</sup> are trademark or registered trademark of ROHM Co., Ltd.

# Notation

| Classification | Notation                                                                                                                               | Description                                                                                                                               |  |  |  |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Numeric value  | nnh, nnH, 0xnn                                                                                                                         | Indicates a hexadecimal number. n: Any value in the range of 0 to F                                                                       |  |  |  |  |

| • Unit         | word, W<br>half word, HW<br>byte, B<br>nibble, N<br>mega-, M<br>kilo-, K<br>kilo-, k<br>milli-, m<br>micro-, μ<br>nano, n<br>second, s | 32 bits<br>16 bits<br>8 bits<br>4 bits<br>$10^{6}$<br>$2^{10} = 1024$<br>$10^{3} = 1000$<br>$10^{-3}$<br>$10^{-6}$<br>$10^{-9}$<br>second |  |  |  |  |

• Terminology

"H", "1": Indicates high voltage signal levels VIH and VOH as specified by the electrical characteristics. "L", "0": Indicates low voltage signal levels VIL and VOL as specified by the electrical characteristics. SFR: Indicates special function register.

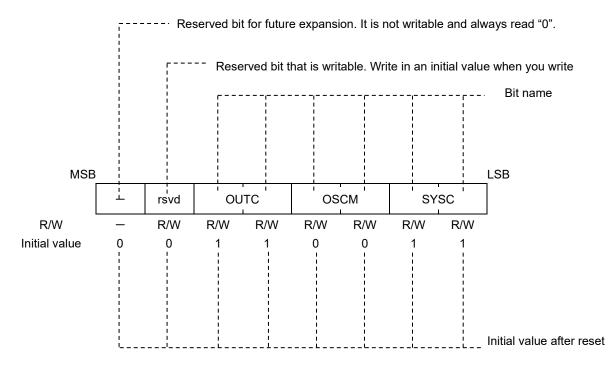

• Register description

R/W: Indicates that Read/Write attribute. "R" indicates that data can be read and "W" indicates that data can be written. "R/W" indicates that data can be read or written.

Chapter 1

# **Overview**

#### • Please see "Notes for product usage" and "Notice" in this document on use with this product.

#### 1. Overview

This LSI is a high-performance low power 32-bit microcontroller. Equipped with a 32-bit CPU core Arm<sup>®</sup>Cortex<sup>®</sup>-M0+, it implements peripheral circuits, such as the Solist-AI<sup>TM</sup> accelerator and CAN controller.

#### • Applications

Consumer and Industrial equipment (e.g., Household appliances, Housing equipment, Office equipment, Measurement instrumentation, etc)

#### [Note]

This product cannot be applicable for automotive use, automatic train control systems, and railway safety systems.

Please contact ROHM sales office in advance if contemplating the integration of this product into applications that requires high reliability, such as transportation equipment for ships and railways, communication equipment for trunk lines, traffic signal equipment, power transmission systems, core systems for financial terminals and various safety control devices.

#### • Product list

The ML63Q2500 group has products as show in the Table1-1 with multiple package and memory size combinations.

| Table1-1 Product List |         |        |           |           |  |  |  |  |

|-----------------------|---------|--------|-----------|-----------|--|--|--|--|

| Drogram               | Data    | Data   | 48pin     | 64pin     |  |  |  |  |

| Program               | memory  | Flash  | TQFP48    | TQFP64    |  |  |  |  |

| memory                | (RAM)   | FIASI  | WQFN48*   | WQFN64*   |  |  |  |  |

| 256KByte              | 16KByte | 8KByte | ML63Q2537 | ML63Q2557 |  |  |  |  |

| 128KByte              | TONDYLE | ondyle | ML63Q2534 | ML63Q2554 |  |  |  |  |

| * 14/0 51/40          |         |        |           |           |  |  |  |  |

\* WQFN48 and WQFN64 package product is under development.

#### 1.1 Features

- CPU

- 32-bit RISC CPU (CPU name: Arm<sup>®</sup>Cortex<sup>®</sup>-M0+)

- Arm®Thumb®/Thumb®-2 instruction supported

- Serial Wire Debug Port

- Minimum instruction execution time

- 30.5 μs (@32.768 kHz system clock)

- 20.83ns (@48 MHz system clock)

- System timer (SysTick)

24 bits × 1 channel, counting by System clock (SYSCLK) (Initial clock: LSCLK) External reference clock is not required

- Internal memory

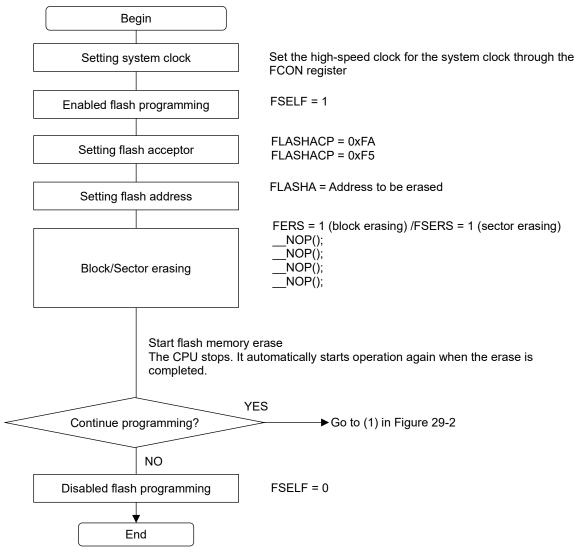

- Re-writing the program memory area by software

- Background Operation (CPU can work while erasing and rewriting to the Data Flash memory area.)

- Flash ROM

- Program area: 128/256KB

- Data area: 8KB

- Data RAM

- Work memory 16KB

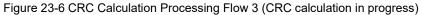

- Solist-AI<sup>TM</sup> Acceralator (AxlCORE-ODL)

- Not only prediction but also learning can be performed on the device. (No need for server/cloud/network connection)

- Detect anomaly conditions by learning normal conditions for each individual.

- Capable of high-speed execution of calculations used in AI processing.

- Addition, subtraction and multiplication of scalars, vectors, and (non-square) matrices are possible.

- Enables FFT calculation processing useful for vibration sensor data processing.

- Calculations can be executed without CPU load.

- Data format: bFloat16 (Built-in integer to bFloat16 conversion function.)

- Low power consumption/low cost. (Compared to FPGA/GPU etc.), High-speed processing. (Compared to software processing.)

- One-stop utility using model-based technology.

- Provides software library.

- Built-in bFloat16-format uniform distribution pseudo-random number generator that can be used as a fixed table.

- Application example.

- Motor + acceleration sensor + AI: Early detection of bearing damage.

- Motor + current sensor + AI: Detection of poor lubrication/contamination of foreign objects.

- Thermography camera + AI: Accurate detection of abnormal heat generation.

- FA sensor + AI: Early detection of random failures and abnormal conditions.

- CAN controller

- 1 channel

- Equipped with one channel of CAN\_FD and 2.0B protocol compliant controller

- Ability of real time communication control with up to 5Mbps (TBD)

- ISO 11898-1:2015 compliant

- SAE J1939 is supported

- CAN FD up to 64 data bytes is supported

- Up to 64 proprietaries receive buffers

- Up to 32 proprietaries transmit buffers

- Equipped with CAN error log function

- Equipped with reception filter

- Individual signals are transmitted when a high-priority message is received

- Interrupt controller (NVIC)

- 1 non-maskable interrupt source and 31 maskable interrupt sources

- Priority level (4-level) can be set for each interrupt

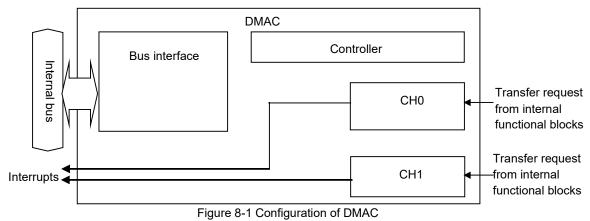

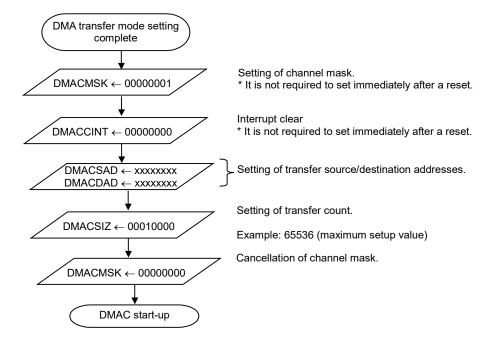

- DMA controller (DMAC)

- 2 channels

- Enable to allocate multiple DMA transfer request sources for each channel.

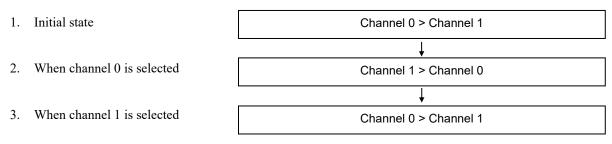

- Channel priority: fixed mode/round robin mode

- DMA transfer mode: cycle steal mode/burst mode

- DMA request type: software requests/hardware requests

- Maximum transfer count: 65,536

- Data transfer size: 8 bits/16 bits/32 bits

- Transfer request source: SSIOF, UARTF, I<sup>2</sup>CF, SA-ADC

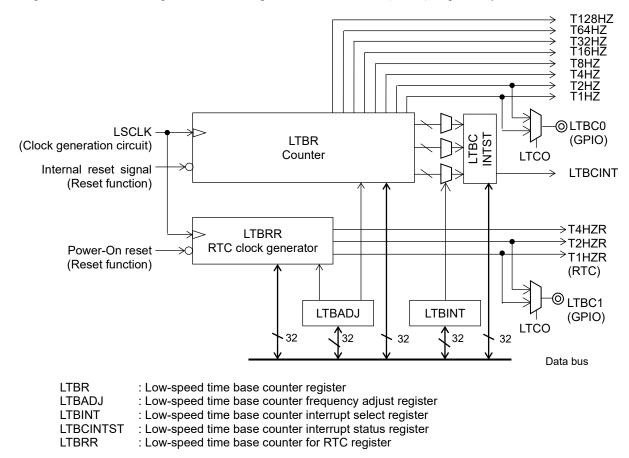

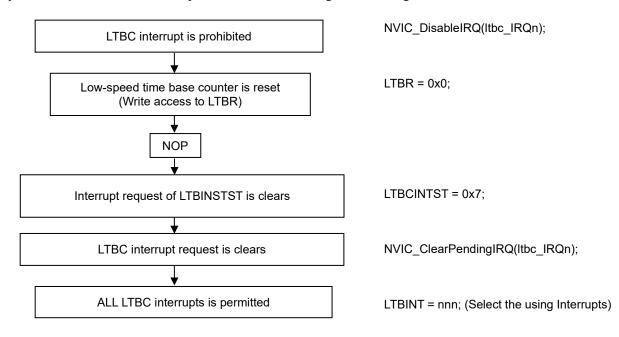

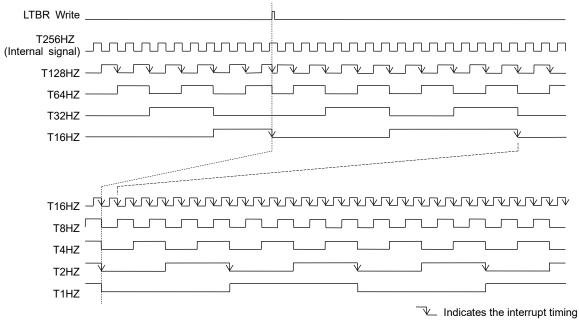

- Time base counter (TBC)

- Low-speed time base counter  $\times$  1 channel with interrupt,  $\times$  1 channel for RTC.

- The clock frequency adjustment in a range approx. -488ppm to +488ppm with 0.119ppm step.

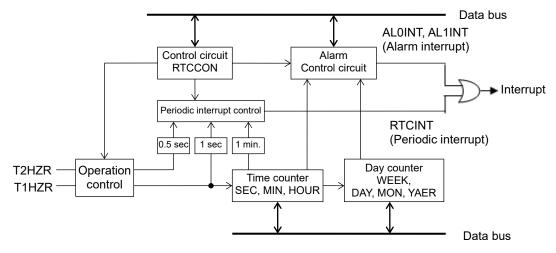

- Real Time Clock (RTC)

- 99 years calendar, alarm, adjustment of the clock

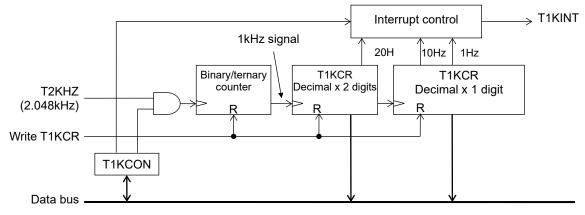

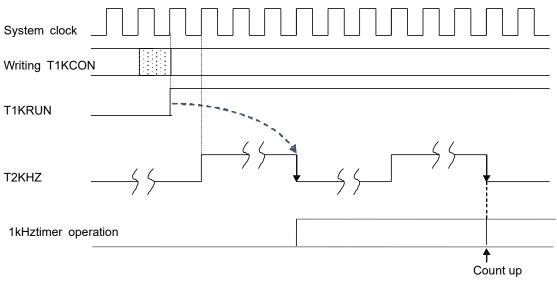

- 1 kHz Timer (TM1K)

80Hz/60Hz/40Hz/20Hz/10Hz/1Hz interrupt function

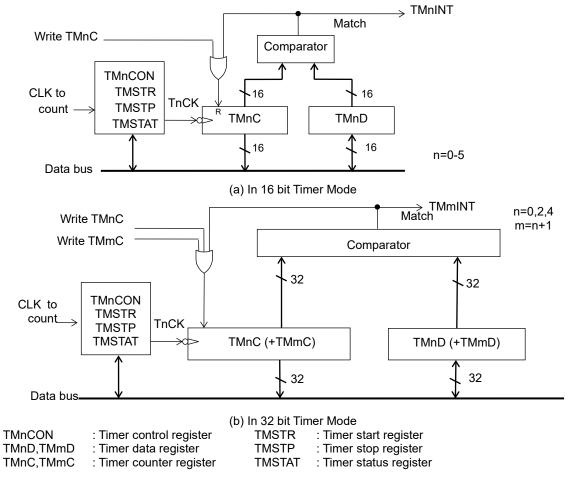

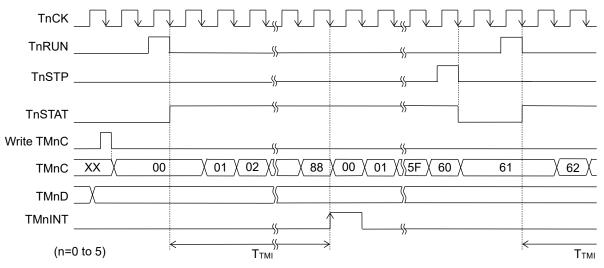

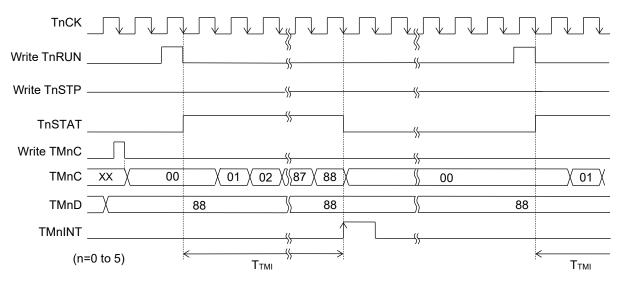

- Timers (TMR)

- 16-bit  $\times$  6 channels

- 32-bit configuration available by using 2 channels

- Selection of one-shot timer mode is possible

- External clock can be selected as timer clock.

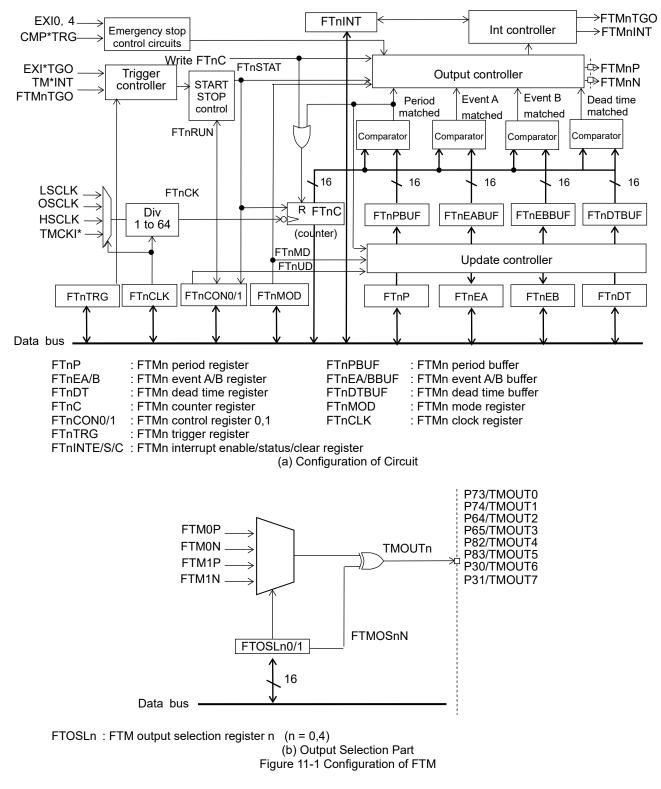

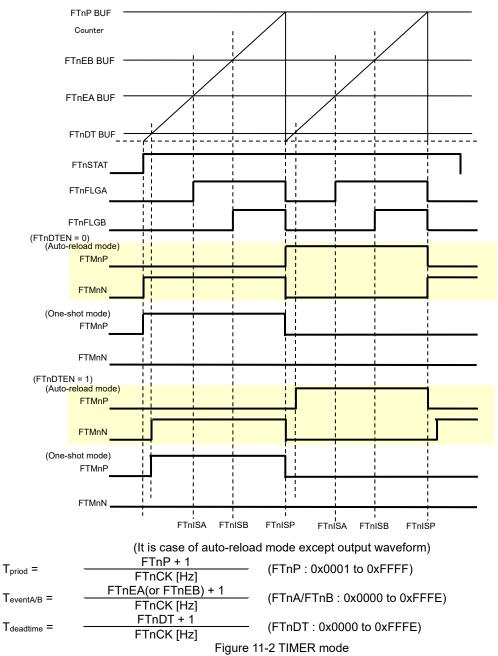

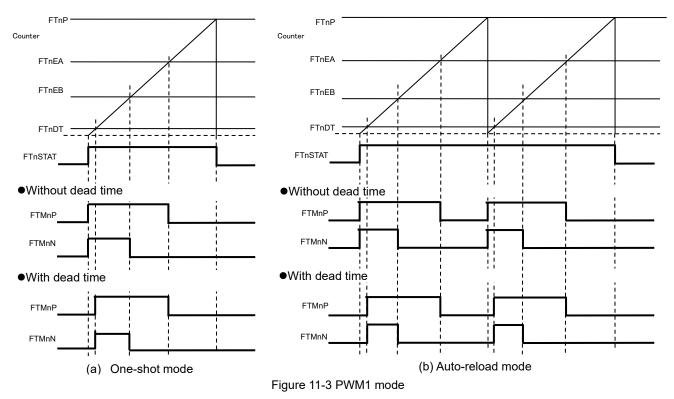

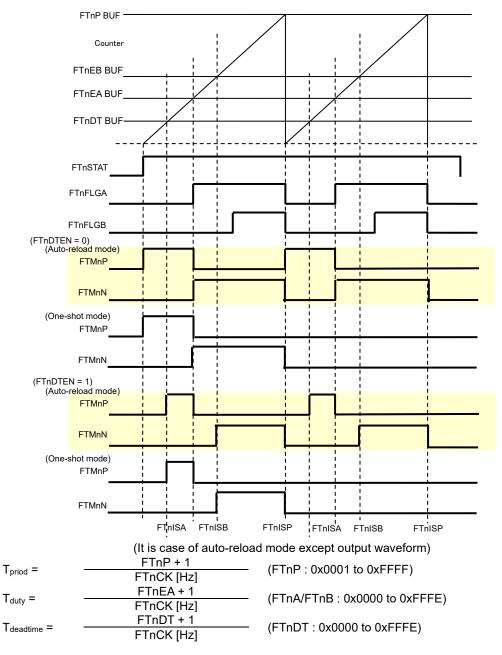

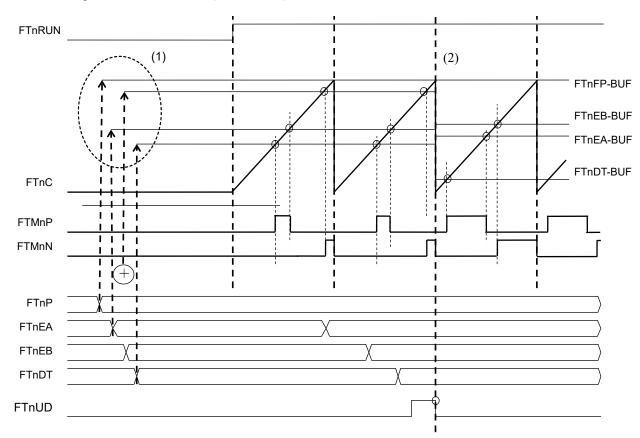

- Function Timers (FTM)

- 16-bit  $\times 2$  channels

- Equipped with the timer/capture/PWM functions using a 16-bit counter

- An event trigger (external pin input interrupt or timer interrupt request) can control start/stop/clear of the timer (however, the minimum pulse width of pin input is timer clock 3φ)

- 1 to 64 dividing of LSCLK/OSCLK/HSCLK/external input selectable as timer clock

- Two types of PWM with the same period and different duties and complementary PWM with the dead time set can be output.

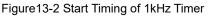

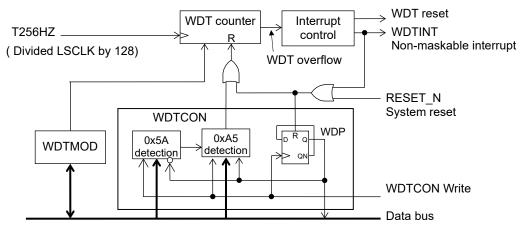

- Watchdog timer (WDT)

- Non-maskable interrupt and reset

- Free running

- Overflow period: 4 types selectable (125ms, 500ms, 2s, and 8s when LSCLK = 32.768 kHz)

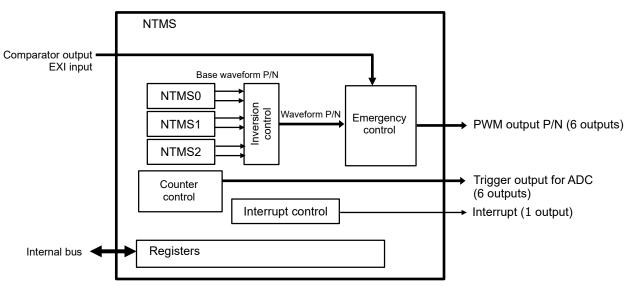

- Three-phase motor control PWM (NTMS)

- 16-bit × 3 channels, 2 outputs each; total 6 outputs

- Center-aligned waveform output with up-down counter

- Generatable a trigger of the SA-ADC conversion starting

- Emergency stop with analog-comparator or pin input

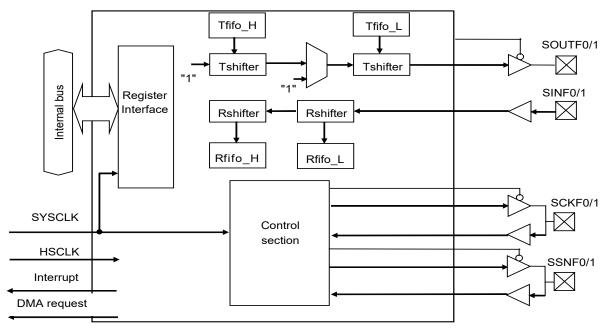

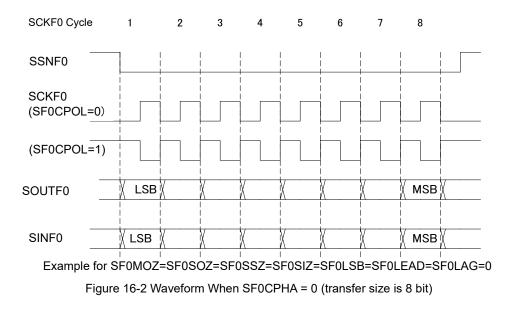

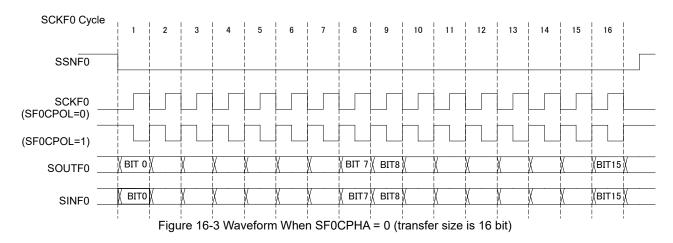

- Synchronous serial port (SSIOF)

- 2 channels

- 4-stage FIFO for each transmission and reception

- Master/slave selectable

- LSB first/MSB first selectable

- Clock polarity and phase selectable

- Supports slave-select signal

#### • UART (UARTF)

- 4 channels

- 4-stage FIFO for each transmission and reception

- Full duplex buffer system

- Communication speed: up to 115200bps.

- Programmable interface (data length, parity, stop bits selectable)

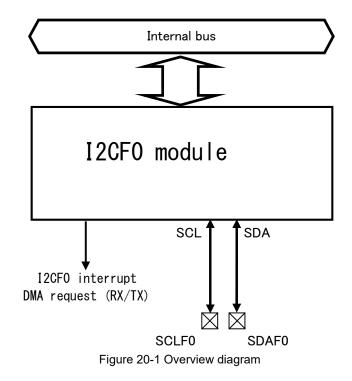

- I<sup>2</sup>C bus interface (I2CF)

- 1 channel

- 4-stage FIFO for each transmission and reception

- Master/slave function

- Fast mode (400 kHz), standard mode (100 kHz)

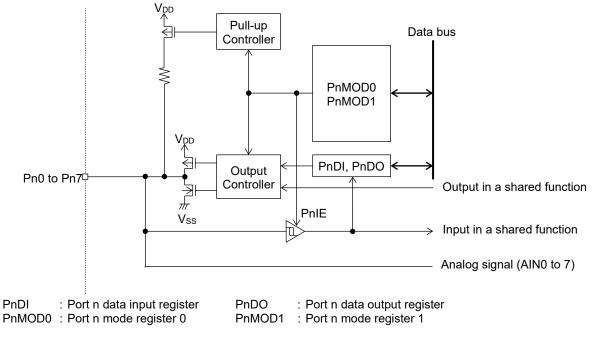

- General-purpose ports (GPIO)

- Input/output port × up to 49 channels (including secondary or tertiary or quaternary).

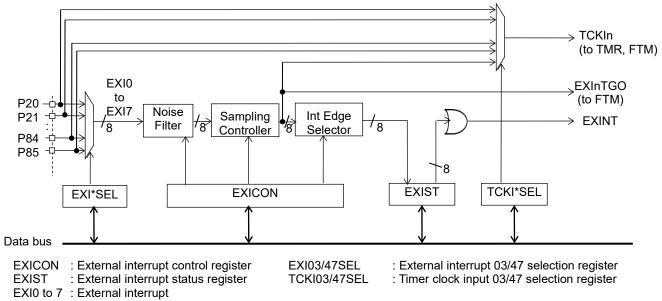

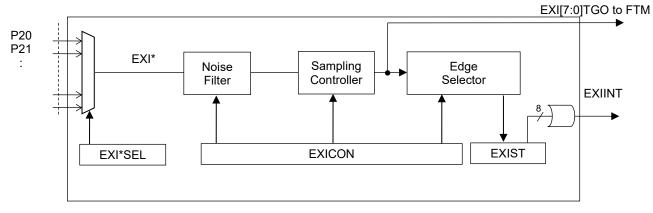

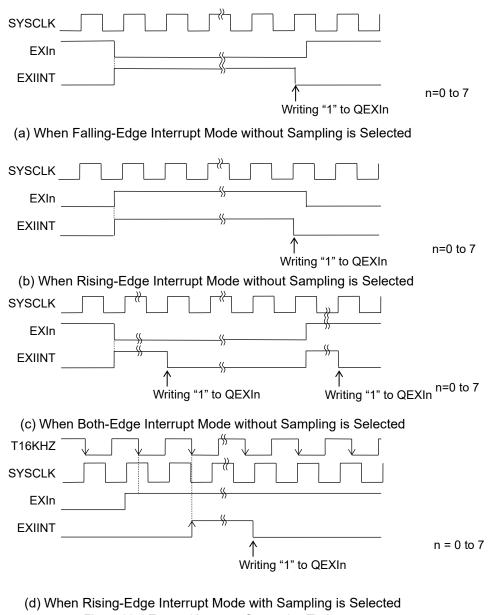

- Port interrupt: 8 sources selectable from all GPIOs

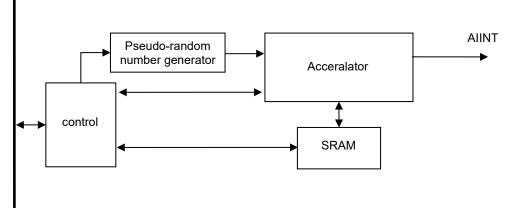

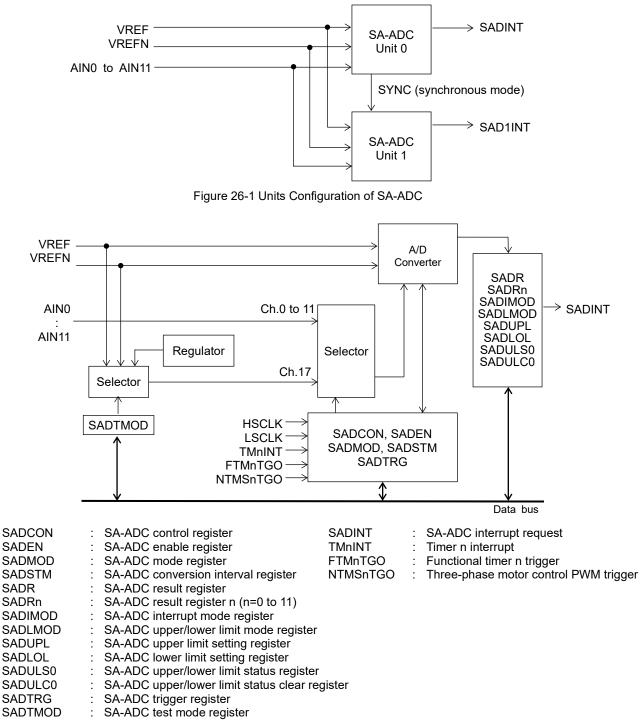

- Successive approximation type A/D converter (SA-ADC)

- 2 units

- Input × 12 channels

- 12-bit resolution

- Conversion time minimum 1µs/ channel @conversion clock is 24MHz

- Simultaneous conversion of 2 inputs with 2 units is possible

- Sampling time can be chosen

- Consecutive scan conversion function for target input channels

- Consecutive scan conversion with a specific interval time

- One conversion result register for each channel

- Upper /Lower limit is configurable for the conversion result, generates an interrupt

- A/D converter self test function (full scale, zero scale, internal reference voltage)

- Following triggers is available to start the A/D conversion

16-bit timer interrupt requests, functional timer trigger and three-phase motor control PWM ADC conversion staring trigger.

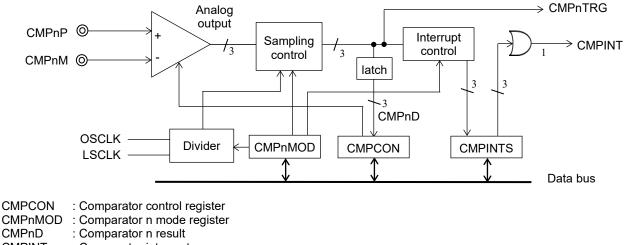

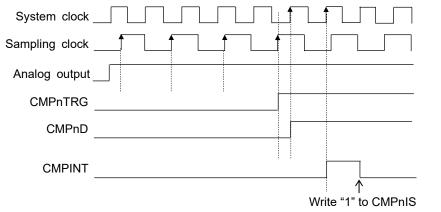

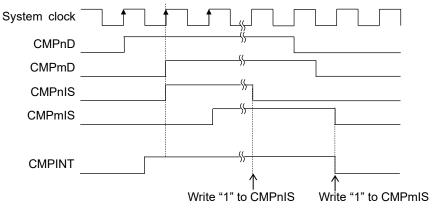

- Analog comparator (CMP)

- 3 units

- Common-mode input voltage range: 0.1 to V<sub>DD</sub>-1.2V

- Propagation delay: Typ. 0.5μs

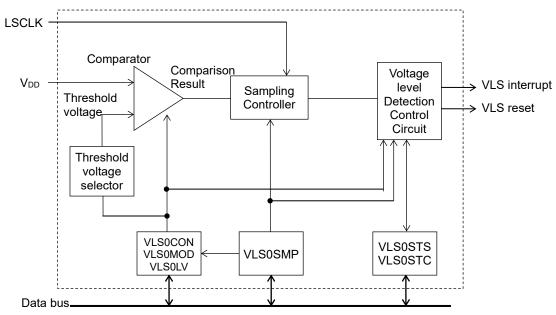

- Voltage Level Supervisor (VLS)

- Monitoring V<sub>DD</sub> level.

- Threshold voltage: selectable from 10 level

- Functional Voltage level detection reset or interrupt is generatable

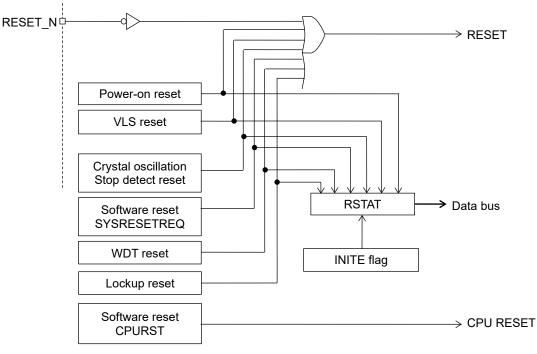

- Reset

- RESET\_N pin reset

- Power-on reset

- Watchdog timer (WDT) overflow reset

- Voltage Level Supervisor (VLS) reset

- Crystal oscillation stop detection reset

- SYSRESETREQ of Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ (software reset)

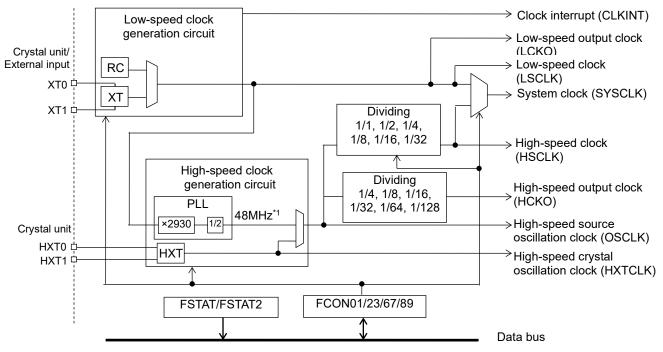

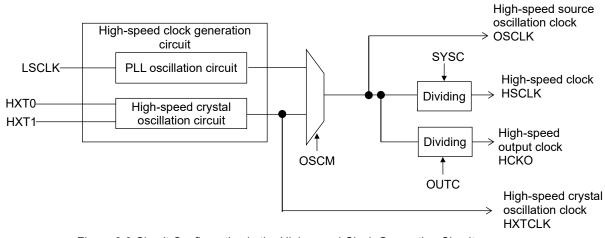

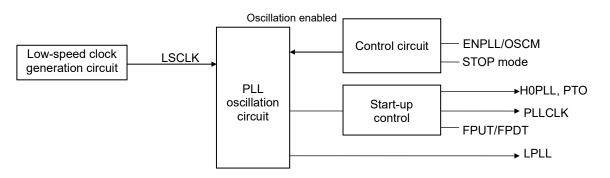

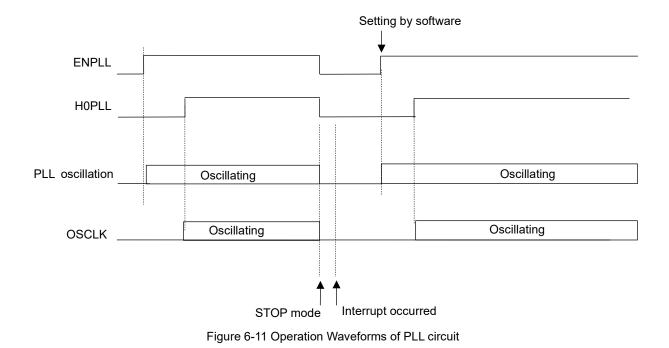

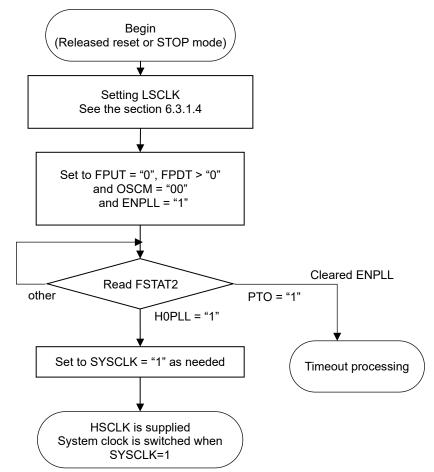

- Clock

- Low-speed clock:

- Crystal oscillation (32.768 kHz)

- Built-in RC oscillation (32.768kHz)

- High-speed clock:

- PLL (48MHz) generated from Low-speed clock

- Crystal oscillation (40/20MHz) for system or CAN

#### • Power management

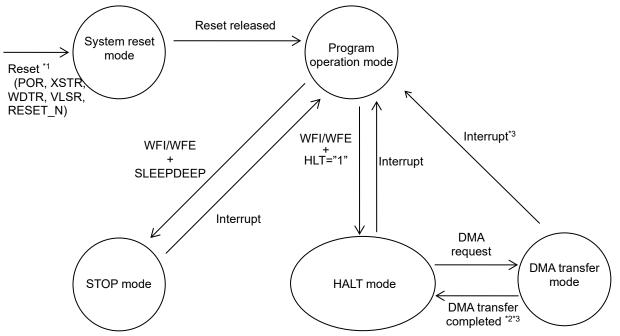

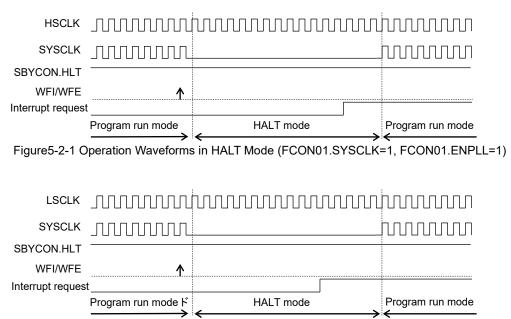

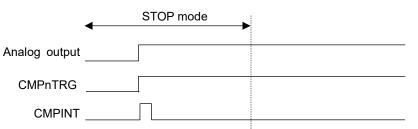

- HALT mode: Instruction execution by CPU is suspended. All peripheral circuits can keep in operating states.

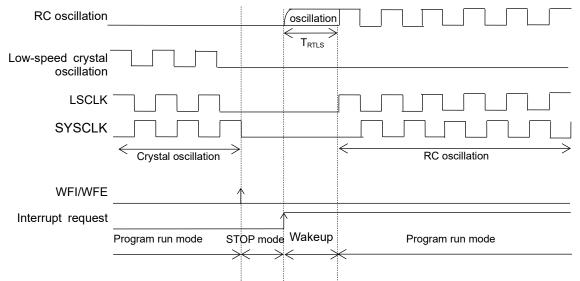

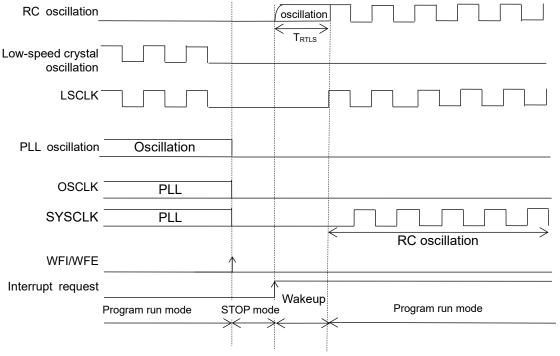

- STOP mode: Stop of low-speed oscillation and high-speed oscillation (Operations of CPU and peripheral circuits are stopped.)

- Clock gear: The frequency of high-speed system clock can be changed by software (1/1, 1/2, 1/4, 1/8, 1/16, 1/32 of the oscillation clock)

- Block Control Function: Power down (reset registers and stop clock supply) the circuits of unused peripherals.

- Guaranteed operating range

- Operating temperature: (ambient) -40°C to +105°C, (junction) -40°C to +115°C

- Operating voltage: V<sub>DD</sub>=2.3 to 5.5V

- Shipping package

| Table1-2 | Product | name | list |

|----------|---------|------|------|

|                     | Body size                     | Pin pitch | Packing form and Product name                |                                              |  |  |

|---------------------|-------------------------------|-----------|----------------------------------------------|----------------------------------------------|--|--|

| Package             | (including lead)<br>[mm × mm] |           | Tray                                         | Tape & Reel                                  |  |  |

| 48 pin plastic WQFN | 7.0 × 7.0<br>(-)              | 0.5       | ML63Q2534-NNNGDZW5AY<br>ML63Q2537-NNNGDZW5AY | ML63Q2534-NNNGDZW5BY<br>ML63Q2537-NNNGDZW5BY |  |  |

| 48 pin plastic TQFP | 7.0 × 7.0<br>(9.0 × 9.0)      | 0.5       | ML63Q2534-NNNTBZWAY<br>ML63Q2537-NNNTBZWAY   | ML63Q2534-NNNTBZWBY<br>ML63Q2537-NNNTBZWBY   |  |  |

| 64 pin plastic WQFN | 9.0 × 9.0<br>(-)              | 0.5       | ML63Q2554-NNNGDZW5AY<br>ML63Q2557-NNNGDZW5AY | ML63Q2554-NNNGDZW5BY<br>ML63Q2557-NNNGDZW5BY |  |  |

| 64 pin plastic TQFP | 10.0 × 10.0<br>(12.0 × 12.0)  | 0.5       | ML63Q2554-NNNTBZWAY<br>ML63Q2557-NNNTBZWAY   | ML63Q2554-NNNTBZWBY<br>ML63Q2557-NNNTBZWBY   |  |  |

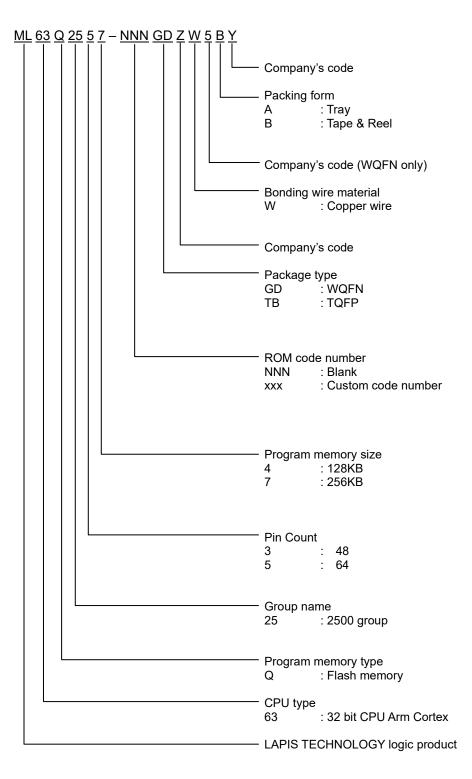

#### 1.1.1 How To Read The Part Number

Figure1-1 Part Number

#### 1.1.2 Function List

|               |                                    | Table1-3 Product S                        | pecification           |                       |                |  |  |  |

|---------------|------------------------------------|-------------------------------------------|------------------------|-----------------------|----------------|--|--|--|

| Category      |                                    | ML63Q2534                                 | ML63Q2537              | ML63Q2554             | ML63Q2557      |  |  |  |

| CPU           |                                    | Arm <sup>®</sup> Cortex <sup>®</sup> -M0+ |                        |                       |                |  |  |  |

| Memory        | Program FLASH                      | 128KB                                     | 256KB                  | 128KB                 | 256KB          |  |  |  |

|               | Data RAM                           |                                           | 16K                    | В                     |                |  |  |  |

|               | Data FLASH                         |                                           | 8KE                    | 3                     |                |  |  |  |

| Pins          | Total                              | 48                                        | 48                     | 64                    | 64             |  |  |  |

|               | Power                              |                                           | 4                      |                       |                |  |  |  |

|               | Reset                              |                                           | 1                      |                       |                |  |  |  |

|               | GPIO                               | 34                                        | ļ                      | 4                     | .9             |  |  |  |

| interrupt     | Non maskable                       |                                           | 1                      |                       |                |  |  |  |

|               | Maskable                           |                                           | 31                     |                       |                |  |  |  |

|               | (External pin input)               |                                           | (8)                    |                       |                |  |  |  |

| Timer         | TMR                                |                                           | 6 cł                   | า                     |                |  |  |  |

|               | FTM                                |                                           | 2 cł                   | า                     |                |  |  |  |

|               | NTMS                               | 1 ch                                      |                        |                       |                |  |  |  |

|               | TBC                                | 2 ch                                      |                        |                       |                |  |  |  |

|               | RTC                                | 1 ch                                      |                        |                       |                |  |  |  |

|               | TM1K                               | 1 ch                                      |                        |                       |                |  |  |  |

|               | WDT                                |                                           | 1 cł                   | า                     |                |  |  |  |

| Communication | SSIOF                              |                                           | 2 cł                   | า                     |                |  |  |  |

|               | UARTF                              |                                           | 4 cł                   | า                     |                |  |  |  |

|               | I2CF                               |                                           | 1 cł                   | า                     |                |  |  |  |

|               | CAN                                | 1 ch                                      |                        |                       |                |  |  |  |

| Analog        | VLS                                |                                           | 1 un                   | iit                   |                |  |  |  |

|               | SA-ADC                             |                                           | 2 un                   | iit                   |                |  |  |  |

|               |                                    |                                           | 12 inp                 | out                   |                |  |  |  |

|               | CMP                                |                                           | 3 un                   | it                    |                |  |  |  |

| Other         | DMAC                               |                                           | 2 cł                   |                       |                |  |  |  |

|               | Solist-AI <sup>™</sup> Accelerator |                                           | 1 cł                   |                       |                |  |  |  |

| Clock         | Low speed                          |                                           | Hz (built-in RC osci   |                       |                |  |  |  |

|               | High speed                         | PLL (Up                                   | to 48MHz), crystal     | oscillation (20 or 4  | OMHz)          |  |  |  |

| Reset         | cause                              | Pin / POR / WD                            | T / VLS / crystal oso  | cillation stop detect | ion / software |  |  |  |

| Operating     | Temperature                        |                                           | Ta: -40°C to +105°     | C (Tj < +115°C)       |                |  |  |  |

| Condition     | Voltage                            |                                           | V <sub>DD</sub> =2.3 t | o 5.5V                |                |  |  |  |

| Package       |                                    | WQFN48,                                   | TQFP48                 | WQFN64                | , TQFP64       |  |  |  |

#### ML63Q2500 Group User's Manual Chapter 1 Overview

### ROHM Co., Ltd.

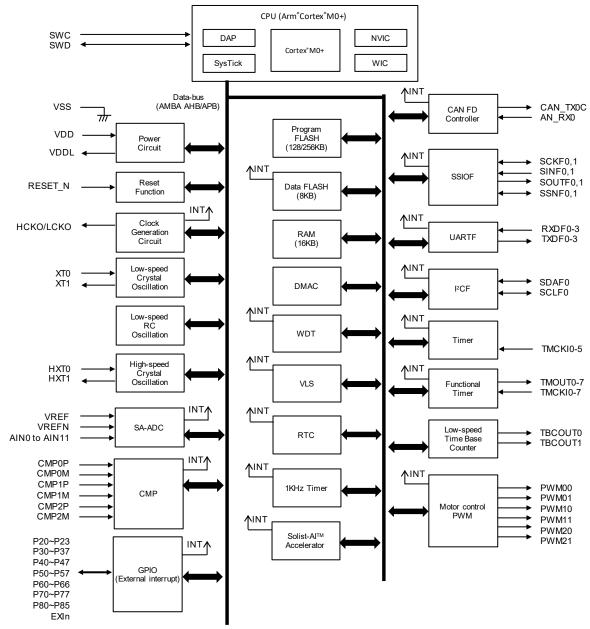

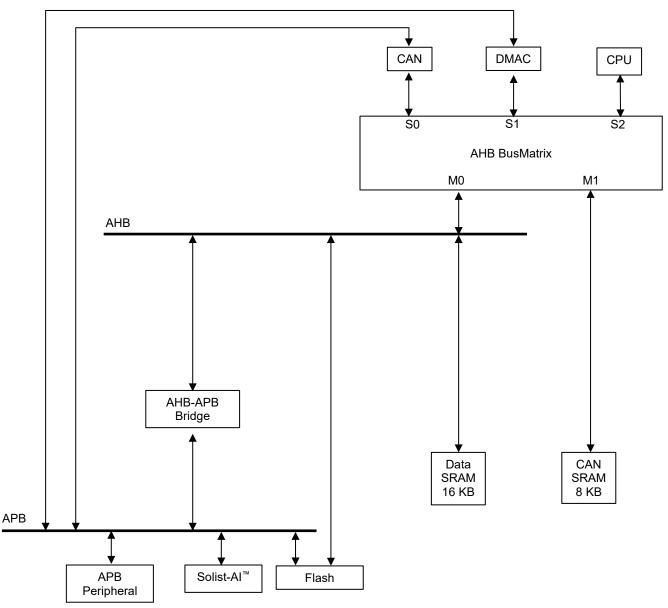

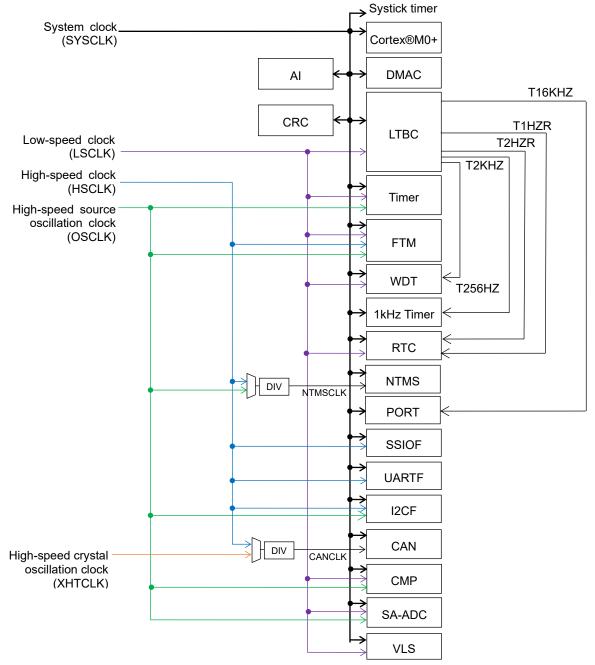

#### 1.2 Block Diagram

Figure1-2 BLOCK DIAGRAM

1.3 Pins

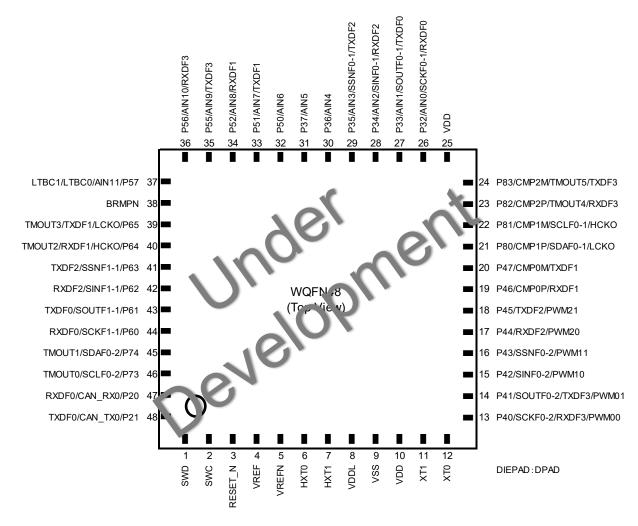

1.3.1 Pin Configuration

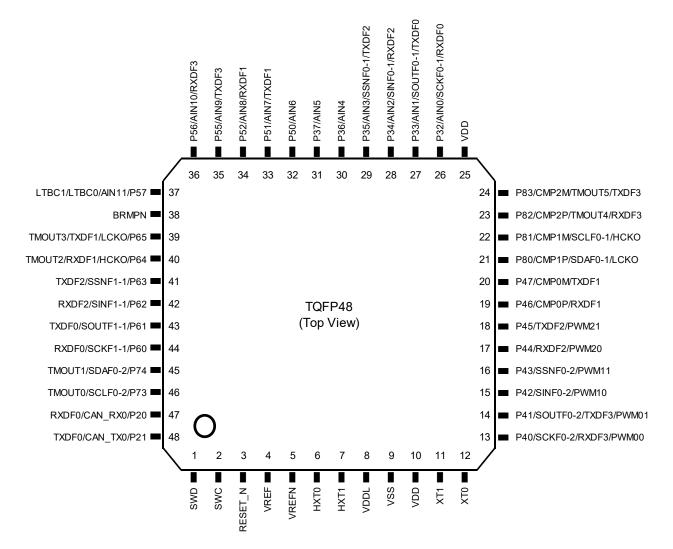

1.3.1.1 ML63Q2537/2534 48pin WQFN Package

Figure1-3-1 48pin WQFN Package

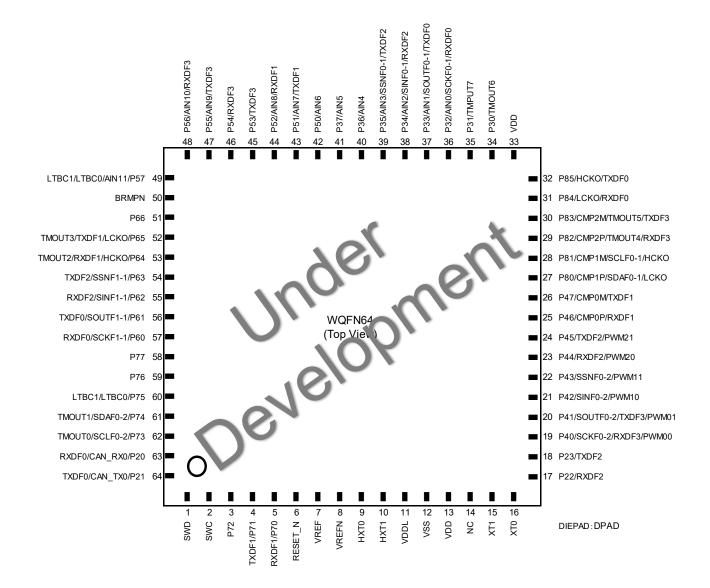

#### 1.3.1.2 ML63Q2537/2534 48pin TQFP Package

Figure1-3-2 48pin TQFP Package

#### 1.3.1.3 ML63Q2557/2554 64pin WQFN Package

Figure1-3-3 64pin WQFN Package

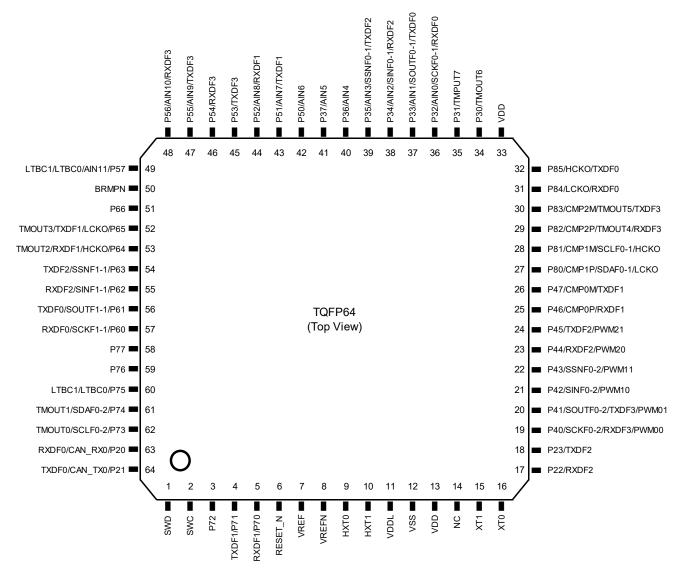

#### 1.3.1.4 ML63Q2557/2554 64pin TQFP Package

Figure1-3-4 64pin TQFP Package

#### 1.3.2 List of Pins

| DIN       | Table1-4 List of Pins           PIN No.         Primary Function         Secondary Function         Tertiary Function         Quaternary Function |                 |               |                        |      |                        |       |                        |     |                        |       |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|------------------------|------|------------------------|-------|------------------------|-----|------------------------|-------|

|           | NO.                                                                                                                                               |                 |               | Primary Fund           | tion | Secondary Fun          | ction | Tertiary Funct         | on  | Quaternary Fun         | ction |

| ML63Q253x | ML63Q255x                                                                                                                                         | LSI<br>Pin name | Reset state   | Functional<br>pin name | I/O  | Functional pin<br>name | I/O   | Functional pin<br>name | I/O | Functional pin<br>name | I/O   |

| 1         | 1                                                                                                                                                 | SWD             | Pull-up input | SWD                    | I/O  | -                      | -     | _                      | -   | —                      | -     |

| 2         | 2                                                                                                                                                 | SWC             | Pull-up input | SWC                    | -    | _                      | -     | —                      | ١   | —                      | —     |

| -         | 3                                                                                                                                                 | P72             | Hi-Z output   | P72                    | I/O  | _                      | -     | _                      | -   | —                      | -     |

| -         | 4                                                                                                                                                 | P71             | Hi-Z output   | P71                    | I/O  | _                      | -     | TXDF1                  | 0   | _                      | -     |

| -         | 5                                                                                                                                                 | P70             | Hi-Z output   | P70                    | I/O  | -                      | -     | RXDF1                  | Ι   | -                      | -     |

| 3         | 6                                                                                                                                                 | RESET_N         | Hi-Z input    | RESET_N                | I    | _                      | -     | _                      | -   | _                      | -     |

| 4         | 7                                                                                                                                                 | VREF            | Hi-Z output   | VREF                   | I/O  | _                      | -     | _                      | _   | _                      | -     |

| 5         | 8                                                                                                                                                 | VREFN           | Hi-Z output   | VREFN                  | I/O  | _                      | -     | _                      | _   | _                      | -     |

| 6         | 9                                                                                                                                                 | HXT0            | Hi-Z output   | HXT0                   | _    | _                      | _     | _                      | _   | _                      | _     |

| 7         | 10                                                                                                                                                | HXT1            | Hi-Z output   | HXT1                   | -    | -                      | _     | _                      | -   | —                      | _     |

| 8         | 11                                                                                                                                                | VDDL            | _             | VDDL                   | 1    | —                      | _     | _                      | Ι   | —                      | -     |

| 9         | 12                                                                                                                                                | VSS             | _             | VSS                    | I    | _                      | -     | _                      | Ι   | —                      | -     |

| 10        | 13                                                                                                                                                | VDD             | -             | VDD                    | _    | _                      | -     | —                      | _   | -                      | -     |

| -         | 14                                                                                                                                                | NC              | -             | NC                     | -    | _                      | -     | _                      | -   | —                      | -     |

| 11        | 15                                                                                                                                                | XT1             | Hi-Z output   | XT1                    | _    | _                      | -     | _                      | _   | _                      | -     |

| 12        | 16                                                                                                                                                | XT0             | Hi-Z output   | XT0                    | _    | —                      | _     | _                      | _   | —                      | -     |

| -         | 17                                                                                                                                                | P22             | Hi-Z output   | P22                    | I/O  | -                      | -     | RXDF2                  | Ι   | —                      | —     |

| -         | 18                                                                                                                                                | P23             | Hi-Z output   | P23                    | I/O  | _                      | -     | TXDF2                  | 0   | _                      | _     |

| 13        | 19                                                                                                                                                | P40             | Hi-Z output   | P40                    | I/O  | SCKF0-2                | I/O   | RXDF3                  | Ι   | PWM00                  | 0     |

| 14        | 20                                                                                                                                                | P41             | Hi-Z output   | P41                    | I/O  | SOUTF0-2               | 0     | TXDF3                  | 0   | PWM01                  | 0     |

| 15        | 21                                                                                                                                                | P42             | Hi-Z output   | P42                    | I/O  | SINF0-2                | Ι     | _                      | _   | PWM10                  | 0     |

| 16        | 22                                                                                                                                                | P43             | Hi-Z output   | P43                    | I/O  | SSNF0-2                | I/O   |                        | _   | PWM11                  | 0     |

| 17        | 23                                                                                                                                                | P44             | Hi-Z output   | P44                    | I/O  | _                      | _     | RXDF2                  | Ι   | PWM20                  | 0     |

| 18        | 24                                                                                                                                                | P45             | Hi-Z output   | P45                    | I/O  | _                      | -     | TXDF2                  | 0   | PWM21                  | 0     |

| 19        | 25                                                                                                                                                | P46             | Hi-Z output   | P46/CMP0P              | I/O  | _                      | _     | RXDF1                  | I   | _                      | -     |

| 20        | 26                                                                                                                                                | P47             | Hi-Z output   | P47/CMP0M              | I/O  | _                      | _     | TXDF1                  | 0   | _                      | _     |

| 21        | 27                                                                                                                                                | P80             | Hi-Z output   | P80/CMP1P              | I/O  | LCKO                   | 0     | SDAF0-1                | I/O | —                      | -     |

| 22        | 28                                                                                                                                                | P81             | Hi-Z output   | P81/CMP1M              | I/O  | HCKO                   | 0     | SCLF0-1                | I/O | —                      | -     |

| 23        | 29                                                                                                                                                | P82             | Hi-Z output   | P82/CMP2P              | I/O  | _                      | -     | RXDF3                  | Ι   | TMOUT4                 | 0     |

| 24        | 30                                                                                                                                                | P83             | Hi-Z output   | P83/CMP2M              | I/O  | _                      | -     | TXDF3                  | 0   | TMOUT5                 | 0     |

| -         | 31                                                                                                                                                | P84             | Hi-Z output   | P84                    | I/O  | LCKO                   | 0     | RXDF0                  | Ι   | _                      | -     |

| -         | 32                                                                                                                                                | P85             | Hi-Z output   | P85                    | I/O  | HCKO                   | 0     | TXDF0                  | 0   | —                      | -     |

| 25        | 33                                                                                                                                                | VDD             | _             | VDD                    | _    | _                      | -     | _                      | _   | _                      | -     |

| -         | 34                                                                                                                                                | P30             | Hi-Z output   | P30                    | I/O  | -                      | _     | -                      | -   | TMOUT6                 | 0     |

| -         | 35                                                                                                                                                | P31             | Hi-Z output   | P31                    | I/O  | _                      | -     | _                      | _   | TMOUT7                 | 0     |

| 26        | 36                                                                                                                                                | P32             | Hi-Z output   | P32/AIN0               | I/O  | SCKF0-1                | I/O   | RXDF0                  | Ι   | _                      | _     |

| 27        | 37                                                                                                                                                | P33             | Hi-Z output   | P33/AIN1               | I/O  | SOUTF0-1               | 0     | TXDF0                  | 0   | _                      | -     |

| 28        | 38                                                                                                                                                | P34             | Hi-Z output   | P34/AIN2               | I/O  | SINF0-1                | Ι     | RXDF2                  | Ι   | _                      | -     |

| 29        | 39                                                                                                                                                | P35             | Hi-Z output   | P35/AIN3               | I/O  | SSNF0-1                | I/O   | TXDF2                  | 0   | -                      | _     |

| 30        | 40                                                                                                                                                | P36             | Hi-Z output   | P36/AIN4               | I/O  | _                      | _     | _                      | I   | _                      | -     |

| 31        | 41                                                                                                                                                | P37             | Hi-Z output   | P37/AIN5               | I/O  | _                      | _     | -                      | _   | -                      | _     |

| 32        | 42                                                                                                                                                | P50             | Hi-Z output   | P50/AIN6               | I/O  | —                      | _     |                        | _   | _                      | -     |

| 33        | 43                                                                                                                                                | P51             | Hi-Z output   | P51/AIN7               | I/O  | _                      | -     | TXDF1                  | 0   | _                      | -     |

| 34        | 44                                                                                                                                                | P52             | Hi-Z output   | P52/AIN8               | I/O  | _                      | -     | RXDF1                  | I   | _                      | -     |

| PIN       | No        |                 |                       | Primary Function Seco |     | Secondary Fun          | Secondary Function Tertiary Func |                        | ion | Quaternary Fun         | ction |

|-----------|-----------|-----------------|-----------------------|-----------------------|-----|------------------------|----------------------------------|------------------------|-----|------------------------|-------|

| ML63Q253x | ML63Q255x | LSI<br>Pin name | Reset state           | Functional pin name   | I/O | Functional pin<br>name | I/O                              | Functional pin<br>name | I/O | Functional pin<br>name | I/O   |

| -         | 45        | P53             | Hi-Z output           | P53                   | I/O | _                      | I                                | TXDF3                  | 0   | _                      | _     |

| -         | 46        | P54             | Hi-Z output           | P54                   | I/O | _                      | _                                | RXDF3                  | I   | _                      | _     |

| 35        | 47        | P55             | Hi-Z output           | P55/AIN9              | I/O | _                      | -                                | TXDF3                  | 0   | _                      | —     |

| 36        | 48        | P56             | Hi-Z output           | P56/AIN10             | I/O | -                      | -                                | RXDF3                  | Ι   | —                      | —     |

| 37        | 49        | P57             | Hi-Z output           | P57/AIN11             | I/O | LTBC0                  | 0                                | LTBC1                  | 0   | —                      | —     |

| 38        | 50        | BRMPN           | Pull-up input         | BRMPN                 | Ι   | -                      | -                                | _                      | I   | -                      | —     |

| -         | 51        | P66             | Hi-Z output           | P66                   | I/O | -                      | -                                | _                      | I   | -                      | —     |

| 39        | 52        | P65             | Hi-Z output           | P65                   | I/O | LCKO                   | 0                                | TXDF1                  | 0   | TMOUT3                 | 0     |

| 40        | 53        | P64             | Hi-Z output           | P64                   | I/O | HCKO                   | 0                                | RXDF1                  | Ι   | TMOUT2                 | 0     |

| 41        | 54        | P63             | Hi-Z output           | P63                   | I/O | SSNF1-1                | I/O                              | TXDF2                  | 0   | -                      | —     |

| 42        | 55        | P62             | Hi-Z output           | P62                   | I/O | SINF1-1                | Ι                                | RXDF2                  | Ι   | -                      | —     |

| 43        | 56        | P61             | Hi-Z output           | P61                   | I/O | SOUTF1-1               | 0                                | TXDF0                  | 0   | -                      | —     |

| 44        | 57        | P60             | Hi-Z output           | P60                   | I/O | SCKF1-1                | I/O                              | RXDF0                  | Ι   | _                      | —     |

| -         | 58        | P77             | Hi-Z output           | P77                   | I/O | _                      | -                                | _                      | _   | _                      | _     |

| -         | 59        | P76             | Hi-Z output           | P76                   | I/O | _                      | -                                | _                      | _   | _                      | _     |

| -         | 60        | P75             | Hi-Z output           | P75                   | I/O | LTBC0                  | 0                                | LTBC1                  | 0   | -                      | —     |

| 45        | 61        | P74             | Hi-Z output           | P74                   | I/O | _                      | -                                | SDAF0-2                | I/O | TMOUT1                 | 0     |

| 46        | 62        | P73             | Hi-Z output           | P73                   | I/O | _                      | -                                | SCLF0-2                | I/O | TMOUT0                 | 0     |

| 47        | 63        | P20             | Hi-Z output           | P20                   | I/O | CAN_RX0                | Ι                                | RXDF0                  | Ι   |                        | _     |

| 48        | 64        | P21             | Hi-Z output           | P21                   | I/O | CAN_TX0                | 0                                | TXDF0                  | 0   | —                      | _     |

| DIEI      |           | DPAD            | –<br>PIO EXI and TMCk | DPAD                  | -   | _                      | -                                | —                      | -   | -                      | -     |

Pxx can be used as GPIO, EXI and TMCKI.

The I<sup>2</sup>C and SSIO interface use pins with a combination of the same suffix number after the hyphen.

#### 1.3.3 Pin Description

The table below shows the pin descriptions for each function.

"I/O" Field in the below table define the pin type ("-" : power supply pin, "I" : Input pin, "O" : Out put pin, "I/O" bi-directional pin) Table1-5 Pin Description

| Table1-5 Pin Description |                        |              |          |                                                                                                                                                                                                                                                              |  |  |  |

|--------------------------|------------------------|--------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Function                 | Functional pin<br>name | LSI pin name | I/O      | Description                                                                                                                                                                                                                                                  |  |  |  |

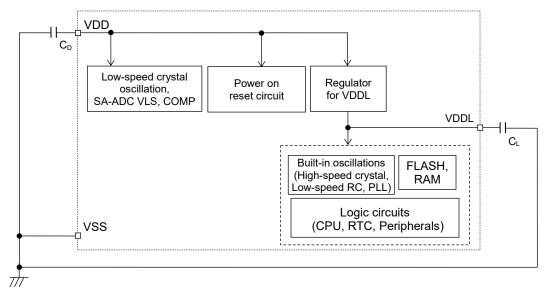

|                          | _                      | VSS          | -        | Negative power supply pin (-) Define this terminal potential as $V_{\rm SS}$                                                                                                                                                                                 |  |  |  |

| Power                    | _                      | VDD          | _        | Positive power supply pin (+).<br>Connect a capacitor $C_V$ (more than 1µF) between this pin and VSS. Define this terminal potential as $V_{DD}$ .                                                                                                           |  |  |  |

|                          | -                      | VDDL         | -        | Power supply for internal logic (internal regulator's output).<br>Connect a capacitor C <sub>L</sub> (1µF) between this pin and VSS.                                                                                                                         |  |  |  |

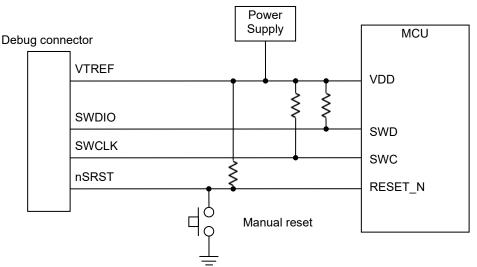

|                          | SWC                    | SWC          |          | Debugger clock input                                                                                                                                                                                                                                         |  |  |  |

|                          | SWD                    | SWD          | I/O      | Debugger data input/output                                                                                                                                                                                                                                   |  |  |  |

| System                   | BRMPN                  | BRMPN        | I        | Remapping control input (for firmware update)<br>Based on the BRMPN pin setting at the time of the<br>reset release, Bank0 is remapped.                                                                                                                      |  |  |  |

| System                   | RESET_N                | RESET_N      | I        | Reset input. When this pin is set to a "L" level, system reset mode is set and the internal section is initialized. When this pin is set to a "H" level subsequently, program execution starts. A pull-up resistor is NOT internally connected.              |  |  |  |

|                          | P20 to P23             | P20 to P23   |          |                                                                                                                                                                                                                                                              |  |  |  |

| _                        | P30 to P37             | P30 to P37   |          | General purpose input/output<br>- High-impedance (initial value)                                                                                                                                                                                             |  |  |  |

| General-purpose          | P40 to P47             | P40 to P47   |          | - Input with Pull-up                                                                                                                                                                                                                                         |  |  |  |

| input/output port        | P50 to P57             | P50 to P57   | I/O      | - Input without Pull-up                                                                                                                                                                                                                                      |  |  |  |

| (GPIO)                   | P60 to P66             | P60 to P66   |          | - CMOS output                                                                                                                                                                                                                                                |  |  |  |

| -                        | P70 to P77             | P70 to P77   |          | - N channel (N-ch) open drain output                                                                                                                                                                                                                         |  |  |  |

|                          | P80 to P85             | P80 to P85   |          |                                                                                                                                                                                                                                                              |  |  |  |

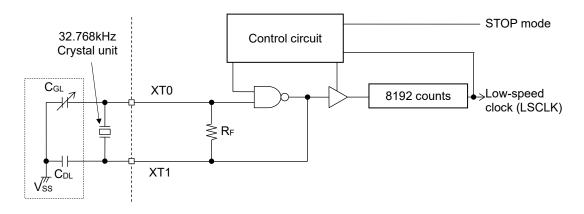

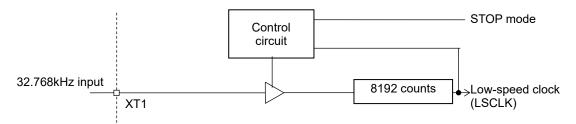

| _                        | XT0<br>XT1             | XT0<br>XT1   | I<br>I/O | 32.768kHz crystal connection pin for low-speed clock.<br>The oscillation unit is connected across XT0 and XT1.<br>Capacitors $C_{DL}$ and $C_{GL}$ are connected across this pin<br>and VSS as required.<br>The XT1 is also used as an external clock input. |  |  |  |

| Clock input              | HXT0                   | HXT0         | I        | 20MHz or 40MHz crystal connection pin to use for CAN interface or high-speed clock.                                                                                                                                                                          |  |  |  |

| -                        | HXT1                   | HXT1         | ο        | The oscillation unit is connected across HXT0 and HXT1. Capacitors C <sub>DL2</sub> and C <sub>GL2</sub> are connected across this pin and VSS as required.<br>An external clock input is not supported.                                                     |  |  |  |

|                          | НСКО                   | P81 P64 P85  | 0        | High-speed clock output                                                                                                                                                                                                                                      |  |  |  |

| Clock output             | LCKO                   | P80 P65 P84  | 0        | Low-speed clock output                                                                                                                                                                                                                                       |  |  |  |

|                          | LTBC0<br>/LTBC1        | P57 P75      | 0        | LTBC 1Hz/2Hz output                                                                                                                                                                                                                                          |  |  |  |

| External<br>interrupt    | EXI0 to EXI7           | P20 to P85   | I        | External maskable interrupt input.<br>Select and assign from all GPIOs.<br>There are also used for trigger of functional timers.                                                                                                                             |  |  |  |

| External timer<br>clock  | TMCKI0<br>toTMCKI7     | P20 to P85   | 1        | External timer clock input<br>Select and assign from all GPIOs.<br>There are used for clock of timers and functional<br>timers.                                                                                                                              |  |  |  |

|                          | TMOUT0                 | P73          | 0        |                                                                                                                                                                                                                                                              |  |  |  |

| ļ Ē                      | TMPUT1                 | P74          | 0        |                                                                                                                                                                                                                                                              |  |  |  |

|                          | TMOUT2                 | P64          | 0        | 1                                                                                                                                                                                                                                                            |  |  |  |

|                          | TMOUT3                 | P65          | 0        | 1                                                                                                                                                                                                                                                            |  |  |  |

| Functional timer         | TMOUT4                 | P82          | 0        | Functional timer output                                                                                                                                                                                                                                      |  |  |  |

|                          | TMOUT5                 | P83          | 0        |                                                                                                                                                                                                                                                              |  |  |  |

|                          | TMOUT6                 | P30          | 0        |                                                                                                                                                                                                                                                              |  |  |  |

|                          | TMOUT7                 | P31          | 0        |                                                                                                                                                                                                                                                              |  |  |  |

|                          |                        | 1 31         | 0        |                                                                                                                                                                                                                                                              |  |  |  |

| Function              | Functional pin<br>name | LSI pin name    | I/O      | Description                                                                                                                                                             |

|-----------------------|------------------------|-----------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | PWM00                  | P40             | 0        |                                                                                                                                                                         |

|                       | PWM01                  | P41             | 0        |                                                                                                                                                                         |

| Three phase           | PWM10                  | P42             | 0        |                                                                                                                                                                         |

| motor control<br>PWM  | PWM11                  | P43             | 0        | PWM output                                                                                                                                                              |

|                       | PWM20                  | P44             | 0        |                                                                                                                                                                         |

|                       | PWM21                  | P45             | 0        |                                                                                                                                                                         |

| I <sup>2</sup> C      | SCLF0                  | P73 P81         | I/O      | I2CF0 clock input/output pin. This pin has an NMOS open drain output. When using this pin as a function of the I <sup>2</sup> C, externally connect a pull-up resistor. |

|                       | SDAF0                  | P74 P80         | I/O      | I2CF0 data input/output pin. This pin has an NMOS open drain output. When using this pin as a functio of the I <sup>2</sup> C, externally connect a pull-up resistor.   |

| CAN                   | CAN_RX0                | P20             | I        | Serial data input of CAN bus 0                                                                                                                                          |

| •                     | CAN_TX0                | P21             | 0        | Serial data output pin of CAN bus 0                                                                                                                                     |

|                       | RXDF0                  | P20 P84 P32 P60 |          | UARTF0 reception data input                                                                                                                                             |

|                       | TXDF0                  | P21 P85 P33 P61 | 0        | UARTF0 transmission data output                                                                                                                                         |

|                       | RXDF1                  | P70 P46 P52 P64 |          | UARTF1 reception data input                                                                                                                                             |

| UART                  | TXDF1                  | P71 P47 P51 P65 | 0        | UARTF1 transmission data output                                                                                                                                         |

| UAN                   | RXDF2                  | P22 P34 P44 P62 | 1        | UARTF2 reception data input                                                                                                                                             |

|                       | TXDF2                  | P23 P35 P45 P63 | 0        | UARTF2 transmission data output                                                                                                                                         |

|                       | RXDF3                  | P40 P54 P56 P82 | Ι        | UARTF3 reception data input                                                                                                                                             |

|                       | TXDF3                  | P41 P53 P55 P83 | 0        | UARTF3 transmission data output                                                                                                                                         |

|                       | SCKF0                  | P32 P40         | I/O      | SIOF0 clock input/output                                                                                                                                                |

|                       | SOUTF0                 | P33 P41         | 0        | SIOF0 data output                                                                                                                                                       |

|                       | SINF0                  | P34 P42         | Ι        | SIOF0 data input                                                                                                                                                        |

| Synchronous           | SSNF0                  | P35 P43         | I/O      | SIOF0 select input/output                                                                                                                                               |

| serial port<br>(SIOF) | SCKF1                  | P60             | I/O      | SIOF1 clock input/output                                                                                                                                                |

|                       | SOUTF1                 | P61             | 0        | SIOF1 data output                                                                                                                                                       |

|                       | SINF1                  | P62             | Ι        | SIOF1 data input                                                                                                                                                        |

|                       | SSNF1                  | P63             | I/O      | SIOF1 select input/output                                                                                                                                               |

|                       | VREF                   | VREF            | 1        | Reference voltage positive input for SA-ADC                                                                                                                             |

|                       | VREFN                  | VREFN           | I        | Reference voltage negative input for SA-ADC                                                                                                                             |

|                       | AIN0                   | P32             | I        | SA-ADC analog input channel 0                                                                                                                                           |

|                       | AIN1                   | P33             | Ι        | SA-ADC analog input channel 1                                                                                                                                           |

|                       | AIN2                   | P34             | I        | SA-ADC analog input channel 2                                                                                                                                           |

| Successive            | AIN3                   | P35             | I        | SA-ADC analog input channel 3                                                                                                                                           |

| approximation         | AIN4                   | P36             | I        | SA-ADC analog input channel 4                                                                                                                                           |

| type A/D<br>converter | AIN5                   | P37             | I        | SA-ADC analog input channel 5                                                                                                                                           |

| (SA-ADC)              | AIN6                   | P50             | I        | SA-ADC analog input channel 6                                                                                                                                           |

| (0/1/12/0)            | AIN7                   | P51             | I        | SA-ADC analog input channel 7                                                                                                                                           |

|                       | AIN8                   | P52             | I        | SA-ADC analog input channel 8                                                                                                                                           |

|                       | AIN9                   | P55             | 1        | SA-ADC analog input channel 9                                                                                                                                           |

|                       | AIN10                  | P56             |          | SA-ADC analog input channel 10                                                                                                                                          |

|                       | AIN11                  | P57             |          | SA-ADC analog input channel 11                                                                                                                                          |

|                       | CMP0P                  | P46             | 1        | Input (+) for analog comparator 0                                                                                                                                       |

|                       | CMP0M                  | P47             | 1        | Input (-) for analog comparator 0                                                                                                                                       |

|                       | CMP1P                  | P80             |          | Input (+) for analog comparator 1                                                                                                                                       |

| CMP                   | CMP1M                  | P81             | 1        | Input (-) for analog comparator 1                                                                                                                                       |

|                       | CMP2P                  | P82             | i        | Input (+) for analog comparator 2                                                                                                                                       |

|                       | CMP2M                  | P83             |          | Input (-) for analog comparator 2                                                                                                                                       |

|                       | _                      | NC              | <u> </u> | Not connected anywhere. Do connect nothing.                                                                                                                             |

| Other                 | _                      | DPAD            | -        | This is pad on the bottom of WQFN package.<br>Do connect nothing.                                                                                                       |

#### 1.3.4 Termination of Unused Pins

| Table1-6 Termination of unused pins                                                            |                             |  |  |  |  |  |

|------------------------------------------------------------------------------------------------|-----------------------------|--|--|--|--|--|

| Pin                                                                                            | Pin termination             |  |  |  |  |  |

| RESET_N                                                                                        | Connect to V <sub>DD</sub>  |  |  |  |  |  |

| BRMPN                                                                                          | Open                        |  |  |  |  |  |

| SWC                                                                                            | Connect a pull-up resistor. |  |  |  |  |  |

| SWD                                                                                            | Connect a pull-up resistor. |  |  |  |  |  |

| VREF                                                                                           | Connect to V <sub>DD</sub>  |  |  |  |  |  |

| VREFN                                                                                          | Connect to Vss              |  |  |  |  |  |

| HXT0, HXT1                                                                                     | Open                        |  |  |  |  |  |

| XT0, XT1                                                                                       | Open                        |  |  |  |  |  |

| P20 to P23<br>P30 to P37<br>P40 to P47<br>P50 to P57<br>P60 to P66<br>P70 to P77<br>P80 to P85 | Open                        |  |  |  |  |  |

| DPAD                                                                                           | Open                        |  |  |  |  |  |

| NC                                                                                             | Open                        |  |  |  |  |  |

[Note]

For unused input ports or unused input/output ports, if the corresponding pins are configured as high-impedance inputs and left open, the supply current may become excessively large. Therefore, terminate unused pins according to Table 1-6.

Chapter 2

# **CPU**

### 2. CPU

#### 2.1 Overview

A RISC processor manufactured by Arm®.

It is a 32-bit processor for small size and low power consumption applications and has a 2-stage pipeline configuration. It implements the Arm<sup>®</sup>v6-M architecture, and operates with 16-bit Arm<sup>®</sup>Thumb<sup>®</sup> instructions and Arm<sup>®</sup>Thumb<sup>®</sup>-2 instructions.

For details, see "Cortex®-M0+ Technical Reference Manual".

#### 2.1.1 Features

- Multiplier can process 32 bit × 32 bit in one cycle (holding the lower 32 bits of the operation result).

- Serial wire debug port

- Little-Endian

- Built-in debug component with four break points and two watch points

- Wakeup from any interrupt is possible.

- WFI (Wait for Interrupts) supported

- WFE (Wait for Events) supported

- SysTick supported

- MTB (Micro Trace Buffer) not supported

#### 2.2 Description of Registers

#### 2.2.1 List of Registers

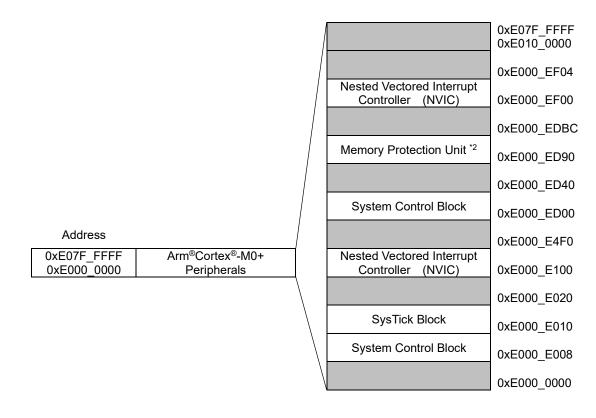

| Address     | Name                                    | Symbol     | R/W | Size | Initial value |

|-------------|-----------------------------------------|------------|-----|------|---------------|

| 0xE000_E010 | SysTick control and status register     | SYST_CSR   | R/W | 32   | 0x0000_00004  |

| 0xE000_E014 | SysTick reload value register           | SYST_RVR   | R/W | 32   | Unknown       |

| 0xE000_E018 | SysTick current value register          | SYST_CVR   | R/W | 32   | Unknown       |

| 0xE000_E01C | SysTick calibration value register      | SYST_CALIB | R   | 32   | 0xC000_0000   |

| 0xE000_ED00 | CPUID register                          | CPUID      | R   | 32   | 0x410C_C601   |

| 0xE000_ED04 | Interrupt control and state register    | ICSR       | R/W | 32   | 0x0000_0000   |

| 0xE000_ED0C | Application interrupt and reset control | AIRCR      | R/W | 32   | 0xFA05_0000   |

|             | register                                |            |     |      |               |

| 0xE000_ED10 | System control register                 | SCR        | R/W | 32   | 0x0000_0000   |

| 0xE000_ED14 | Configuration and control register      | CCR        | R   | 32   | 0x0000_0208   |

| 0xE000_ED1C | System handler priority register 2      | SHPR2      | R/W | 32   | 0x0000_0000   |

| 0xE000_ED20 | System handler priority register 3      | SHPR3      | R/W | 32   | 0x0000_0000   |

For details of the register, see "Cortex<sup>®</sup>-M0+ Technical Reference Manual".

#### 2.3 AHB Bus Configuration

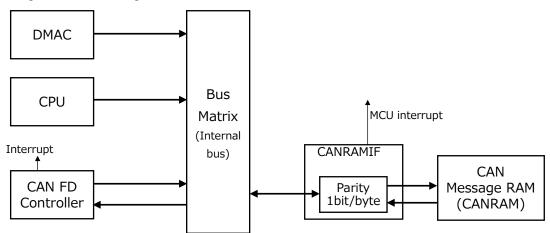

The internal bus is multi-layer bus architecture shown as Figure 2-1. The priority of access is CAN, DMAC, and CPU, in that order.

Figure 2-1 Configuration of internal bus

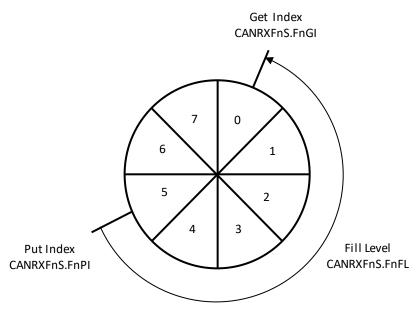

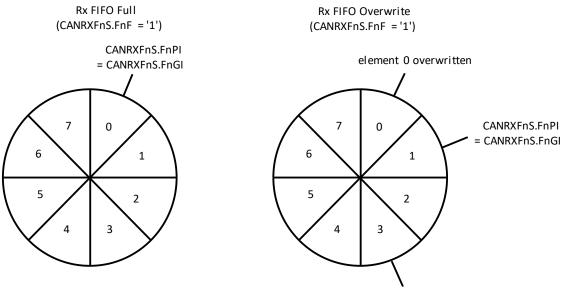

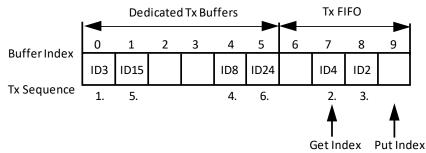

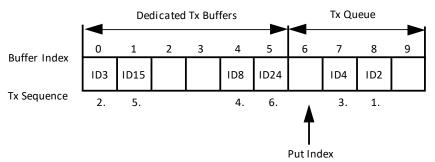

Chapter 3