Dear customer

ROHM Co., Ltd. ("ROHM"), on the 1st day of April, 2024, has absorbed into merger with 100%-owned subsidiary of LAPIS Technology Co., Ltd.

Therefore, all references to "LAPIS Technology Co., Ltd.", "LAPIS Technology" and/or "LAPIS" in this document shall be replaced with "ROHM Co., Ltd." Furthermore, there are no changes to the documents relating to our products other than the company name, the company trademark, logo, etc.

Thank you for your understanding.

ROHM Co., Ltd. April 1, 2024

FEUL610Q306-01

# ML610Q305/306 User's Manual

Issue Date: Jun. 28, 2021

Notes

1) The information contained herein is subject to change without notice.

- 2) When using LAPIS Technology Products, refer to the latest product information (data sheets, user's manuals, application notes, etc.), and ensure that usage conditions (absolute maximum ratings, recommended operating conditions, etc.) are within the ranges specified. LAPIS Technology disclaims any and all liability for any malfunctions, failure or accident arising out of or in connection with the use of LAPIS Technology Products outside of such usage conditions specified ranges, or without observing precautions. Even if it is used within such usage conditions specified ranges, semiconductors can break down and malfunction due to various factors. Therefore, in order to prevent personal injury, fire or the other damage from break down or malfunction of LAPIS Technology Products, please take safety at your own risk measures such as complying with the derating characteristics, implementing redundant and fire prevention designs, and utilizing backups and fail-safe procedures. You are responsible for evaluating the safety of the final products or systems manufactured by you.

- 3) Descriptions of circuits, software and other related information in this document are provided only to illustrate the standard operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. And the peripheral conditions must be taken into account when designing circuits for mass production. LAPIS Technology disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, and other related information.

- 4) No license, expressly or implied, is granted hereby under any intellectual property rights or other rights of LAPIS Technology or any third party with respect to LAPIS Technology Products or the information contained in this document (including but not limited to, the Product data, drawings, charts, programs, algorithms, and application examples, etc.). Therefore, LAPIS Technology shall have no responsibility whatsoever for any dispute, concerning such rights owned by third parties, arising out of the use of such technical information.

- 5) The Products are intended for use in general electronic equipment (AV/OA devices, communication, consumer systems, gaming/entertainment sets, etc.) as well as the applications indicated in this document. For use of our Products in applications requiring a high degree of reliability (as exemplified below), please be sure to contact a LAPIS Technology representative and must obtain written agreement: transportation equipment (cars, ships, trains, etc.), primary communication equipment, traffic lights, fire/crime prevention, safety equipment, medical systems, servers, solar cells, and power transmission systems, etc. LAPIS Technology disclaims any and all liability for any losses and damages incurred by you or third parties arising by using the Product for purposes not intended by us. Do not use our Products in applications requiring extremely high reliability, such as aerospace equipment, nuclear power control systems, and submarine repeaters, etc.

- 6) The Products specified in this document are not designed to be radiation tolerant.

- 7) LAPIS Technology has used reasonable care to ensure the accuracy of the information contained in this document. However, LAPIS Technology does not warrant that such information is error-free and LAPIS Technology shall have no responsibility for any damages arising from any inaccuracy or misprint of such information.

- 8) Please use the Products in accordance with any applicable environmental laws and regulations, such as the RoHS Directive. LAPIS Technology shall have no responsibility for any damages or losses resulting non-compliance with any applicable laws or regulations.

- 9) When providing our Products and technologies contained in this document to other countries, you must abide by the procedures and provisions stipulated in all applicable export laws and regulations, including without limitation the US Export Administration Regulations and the Foreign Exchange and Foreign Trade Act..

- 10) Please contact a ROHM sales office if you have any questions regarding the information contained in this document or LAPIS Technology's Products.

- 11) This document, in part or in whole, may not be reprinted or reproduced without prior consent of LAPIS Technology.

(Note) "LAPIS Technology" as used in this document means LAPIS Technology Co., Ltd.

Copyright 2021 LAPIS Technology Co., Ltd.

#### LAPIS Technology Co., Ltd.

2-4-8 Shinyokohama, Kouhoku-ku, Yokohama 222-8575, Japan http://www.lapis-tech.com/en/

### Preface

This manual describes the operation of the hardware of the 8-bit microcontroller ML610Q305/306.

The following manuals are also available. Read them as necessary.

| nX-U8/100 Core Instruction Manual<br>Description on the basic architecture and the each instruction of the nX-U8/100 Core.                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ■ MACU8 Assembler Package User's Manual Description on the method of operating the relocatable assembler, the linker, the librarian, and the object converter and also on the specifications of the assembler language. |

| CCU8 User's Manual Description on the method of operating the compiler.                                                                                                                                                 |

| CCU8 Programming Guide Description on the method of programming.                                                                                                                                                        |

| CCU8 Language Reference<br>Description on the language specifications of CCU8.                                                                                                                                          |

| DTU8 Debugger User's Manual<br>Description on the method of operating the debugger DTU8.                                                                                                                                |

| ■ LEXIDE-U16 User's Manual Description on the integrated development environment LEXIDE-U16.                                                                                                                            |

| EASE1000 V2 User's Manual Description on the on-chip debug tool EASE1000 V2.                                                                                                                                            |

| MWU16 Flash Writer Host Program User's Manual<br>Description on the Flash Multi Writer host program, MWU16.                                                                                                             |

| Classification  | Notation                                                                                                                          | Description                                                                                                                                                                                                             |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ◆ Numeric value | xxh, xxH<br>xxb                                                                                                                   | Indicates a hexadecimal number.<br>Indicates a binary number.                                                                                                                                                           |

| ◆ Unit          | word, W<br>byte, B<br>nibble, N<br>maga-, M<br>kilo-, K<br>kilo-, k<br>milli-, m<br>micro-, µ<br>nano-, n<br>second, s (lower cas | 1 word = 16 bits<br>1 byte = 8 bits<br>1 nibble = 4 bits<br>$10^{6}$<br>$2^{10} = 1024$<br>$10^{3} = 1000$<br>$10^{-3}$<br>$10^{-6}$<br>$10^{-9}$<br>second                                                             |

| ♦ Terminology   | "L" level                                                                                                                         | Indicates high voltage signal levels $V_{IH}$ and $V_{OH}$ as specified by the electrical characteristics.<br>Indicates low voltage signal levels $V_{IL}$ and $V_{OL}$ as specified by the electrical characteristics. |

### **Notation**

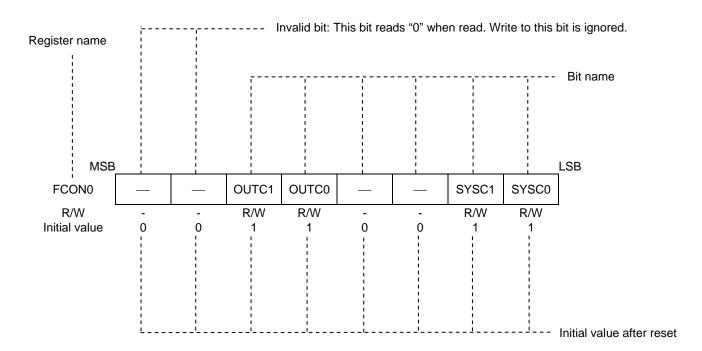

◆ Register description

R/W: Indicates that Read/Write attribute. "R" indicates that data can be read and "W" indicates that data can be written. "R/W" indicates that data can be read or written.

MSB: The highest bit of 8-bit register

LSB: The lowest bit of 8-bit register

### Table of Contents

Chapter 1

| _ |

|---|

| 1 |

| 1 |

| 4 |

| 1 |

| 5 |

| 5 |

| 5 |

| 5 |

| 7 |

| 3 |

| 9 |

| 1 |

|   |

#### Chapter 2

| 2.  | CPU and Memory Space             |  |

|-----|----------------------------------|--|

|     | Overview                         |  |

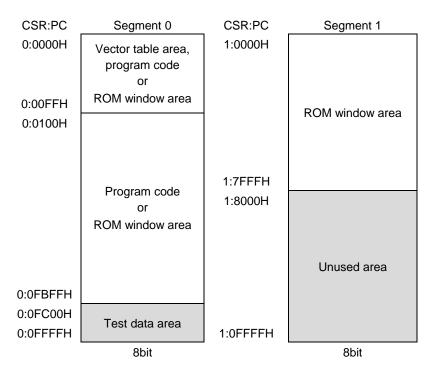

| 2.2 | Program Memory Space             |  |

| 2.3 | Data Memory Space                |  |

|     | Instruction Length               |  |

|     | 5 Data Type                      |  |

|     | Description of Registers         |  |

|     | .6.1 List of Registers           |  |

|     | .6.2 Data Segment Register (DSR) |  |

|     |                                  |  |

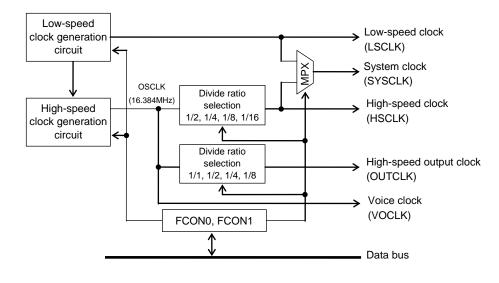

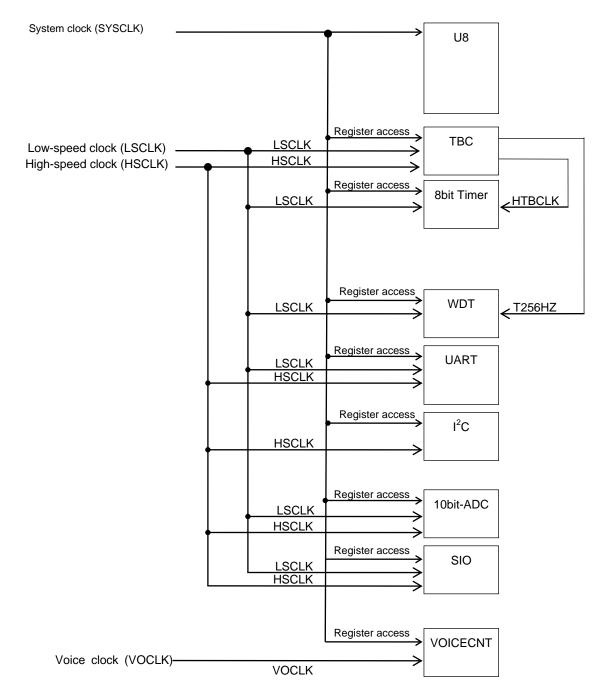

| 3. Clock | Generation Circuit                                    |  |

|----------|-------------------------------------------------------|--|

| 3.1 Ove  | erview                                                |  |

| 3.1.1    | Features                                              |  |

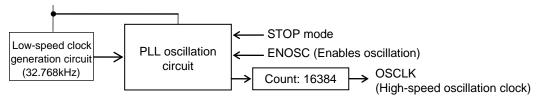

| 3.1.2    | Configuration                                         |  |

| 3.1.3    | Clock Configuration                                   |  |

| 3.2 Des  | cription of Registers                                 |  |

| 3.2.1    | List of Registers                                     |  |

| 3.2.2    | Frequency Control Register 0(FCON0)                   |  |

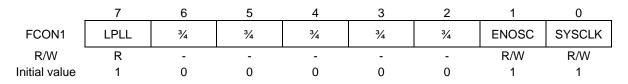

| 3.2.3    | Frequency Control Register 1(FCON1)                   |  |

| 3.3 Des  | cription of Operation                                 |  |

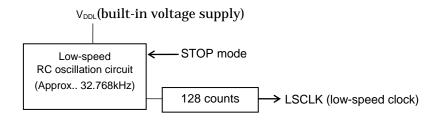

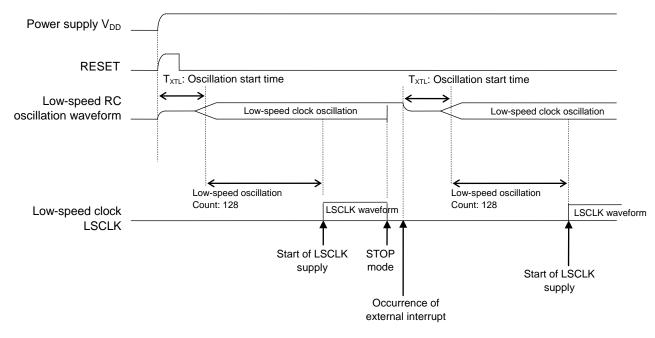

| 3.3.1    | Low-Speed Clock                                       |  |

| 3.3.1.   | Low-Speed Clock Generation Circuit                    |  |

| 3.3.1.   | 2 Operation of the Low-Speed Clock Generation Circuit |  |

| 3.3.2    | High-Speed Clock                                      |  |

| 3.3.2.   | High-Speed Clock Generation Circuit                   |  |

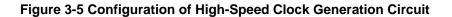

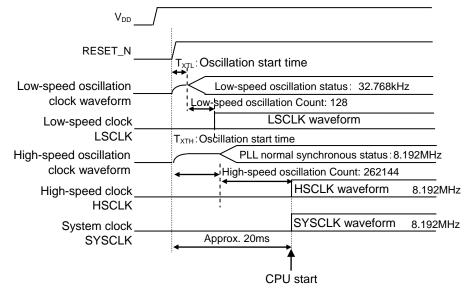

| 3.3.2.2  | 2 Operation of High-Speed Clock Generation Circuit    |  |

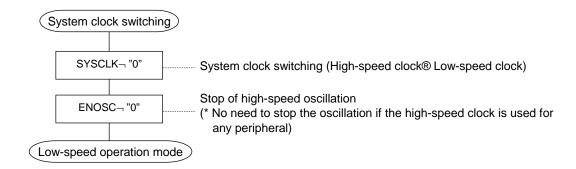

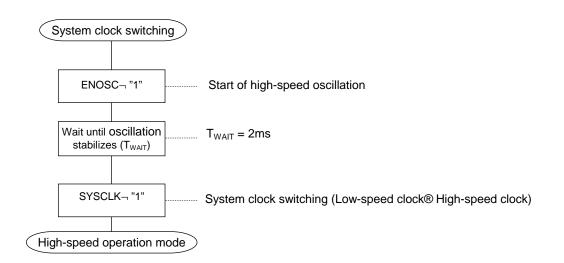

| 3.3.3    | Switching of System Clock                             |  |

|          |                                                       |  |

#### Chapter 4

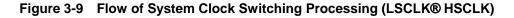

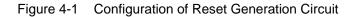

| 4. Reset | Function                       |  |

|----------|--------------------------------|--|

| 4.1 Ov   | erview                         |  |

| 4.1.1    | Features                       |  |

| 4.1.2    | Configuration                  |  |

| 4.1.3    | List of Pin                    |  |

| 4.2 Des  | scription of Registers         |  |

| 4.2.1    | List of Registers              |  |

| 4.2.2    | Reset Status Register (RSTAT)  |  |

| 4.3 Des  | scription of Operation         |  |

|          | Operation of System Reset Mode |  |

|          | · ·                            |  |

### Chapter 5

|         | Control Function                             |      |

|---------|----------------------------------------------|------|

| 5.1 Ove | rview                                        |      |

| 5.1.1   | Features                                     |      |

| 5.1.2   | Configuration                                | 5-1  |

| 5.2 Des | cription of Registers                        |      |

| 5.2.1   | List of Registers                            |      |

| 5.2.2   | Stop Code Acceptor (STPACP)                  | 5-3  |

| 5.2.3   | Standby Control Register (SBYCON)            | 5-4  |

| 5.2.4   | Block Control Register 0 (BLKCON0)           | 5-5  |

| 5.2.5   | Block Control Register 2 (BLKCON2)           | 5-6  |

| 5.2.6   | Block Control Register 3 (BLKCON3)           | 5-8  |

| 5.2.7   | Block Control Register 4 (BLKCON4)           | 5-9  |

| 5.3 Des | cription of Operation                        | 5-10 |

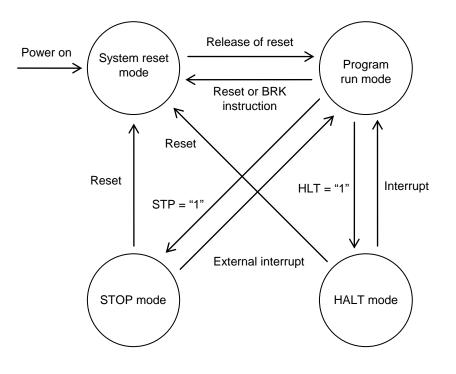

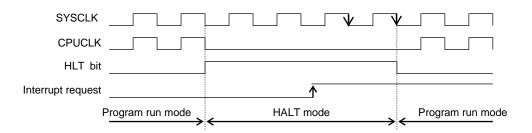

| 5.3.1   | Program Run Mode                             | 5-10 |

| 5.3.2   | HALT Mode                                    | 5-10 |

| 5.3.3   | STOP Mode                                    |      |

| 5.3.3.1 | Note on Return Operation from STOP/HALT Mode | 5-12 |

| 5.3.4   | Block control function                       |      |

|         |                                              |      |

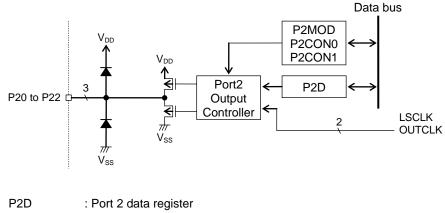

| <ol> <li>6. Port 2</li> <li>6.1 Overview</li> </ol>                        | 6-1        |

|----------------------------------------------------------------------------|------------|

| 6.1 Overview                                                               |            |

|                                                                            | <i>C</i> 1 |

| 6.1.1 Features                                                             | 0-1        |

| 6.1.2 Configuration                                                        | 6-1        |

| 6.1.3 List of Pins                                                         | 6-1        |

| 6.2 Description of Registers                                               | 6-2        |

| 6.2.1 List of Registers                                                    | 6-2        |

| 6.2.2 Port 2 Data Register (P2D)                                           | 6-3        |

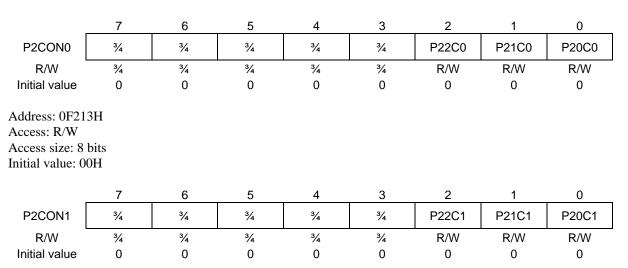

| 6.2.3 Port 2 control registers 0, 1 (P2CON0, P2CON1)                       | 6-4        |

| 6.2.4 Port 2 Mode Register (P2MOD)                                         | 6-5        |

| 6.3 Description of Operation                                               | 6-6        |

| 6.3.1 Output Port Function                                                 | 6-6        |

| 6.3.2 Secondary Function                                                   | 6-6        |

| 6.4 Register setup of the port                                             | 6-7        |

| 6.4.1 When use the High-speed clock (OUTCLK) output function using P21 pin |            |

| 6.4.2 When use the Low-speed clock (LSCLK) output function using P20 pin   | 6-8        |

#### Chapter 7

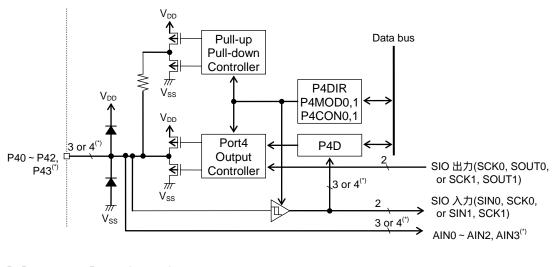

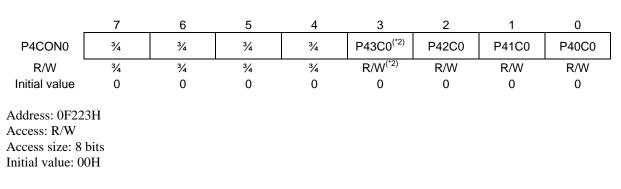

| 7. P | Port 4                               |  |

|------|--------------------------------------|--|

| 7.1  | Overview                             |  |

| 7.1. | .1 Features                          |  |

| 7.1. | .2 Configuration                     |  |

| 7.1. | -                                    |  |

| 7.2  | Description of Registers             |  |

| 7.2. | .1 List of Registers                 |  |

| 7.2. |                                      |  |

| 7.2. | .3 Port 4 Direction Register (P4DIR) |  |

| 7.2. |                                      |  |

| 7.2. |                                      |  |

| 7.3  | Description of Operation             |  |

| 7.3. |                                      |  |

| 7.3. |                                      |  |

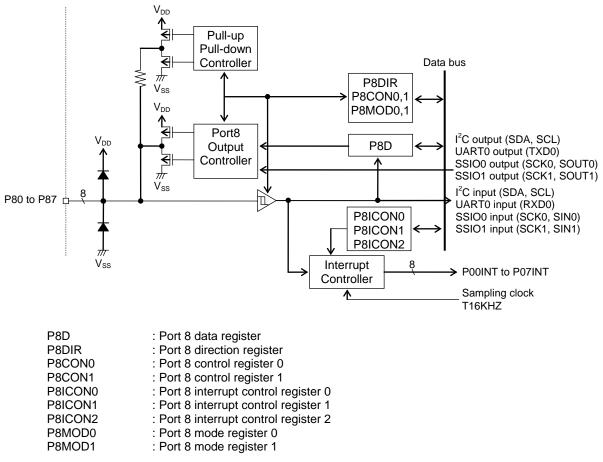

| 8. Port 8. |                                                            |      |

|------------|------------------------------------------------------------|------|

| 8.1 Ove    | rview                                                      |      |

| 8.1.1      | Features                                                   |      |

| 8.1.2      | Configuration                                              | 8-1  |

| 8.1.3      | List of Pins                                               |      |

| 8.2 Des    | cription of Registers                                      |      |

| 8.2.1      | List of Registers                                          |      |

| 8.2.2      | Port 8 Data Register (P8D)                                 |      |

| 8.2.3      | Port 8 Direction Register (P8DIR)                          |      |

| 8.2.4      | Port 8 Control Registers 0, 1 (P8CON0, P8CON1)             |      |

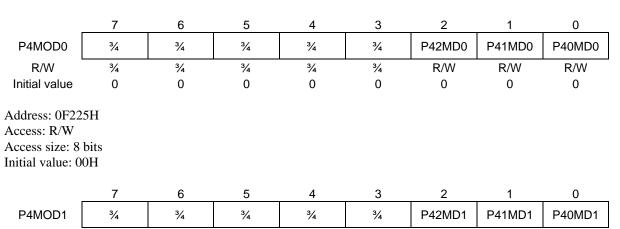

| 8.2.5      | Port 8 Mode Registers 0, 1 (P8MOD0, P8MOD1)                |      |

| 8.2.6      | Port 8 Interrupt Control Registers 0, 1 (P8ICON0, P8ICON1) |      |

| 8.2.7      | Port 8 Interrupt Control Register 2 (P8ICON2)              |      |

| 8.3 Des    | cription of Operation                                      |      |

| 8.3.1      | Input/Output Port Functions                                |      |

| 8.3.2      | Secondary and Tertiary Functions                           |      |

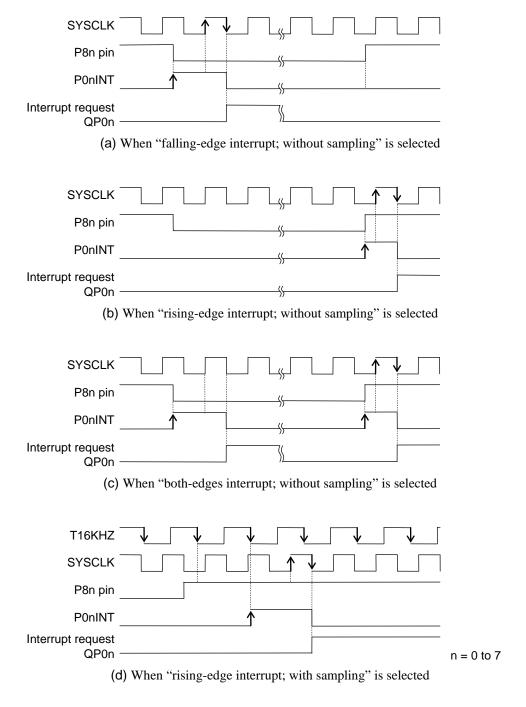

| 8.3.3      | External Interrupt                                         | 8-13 |

| 8.3.4      | Interrupt Request                                          |      |

|            |                                                            |      |

#### Chapter 9

| 9.  | Interru | ipts (INTs)                         |  |

|-----|---------|-------------------------------------|--|

| 9.1 | Ove     | rview                               |  |

| 9   | .1.1    | Features                            |  |

| 9.2 | 2 Des   | cription of Registers               |  |

| 9   | .2.1    | List of Registers                   |  |

| 9   | .2.2    | Interrupt Enable Register 1 (IE1)   |  |

| 9   | .2.3    | Interrupt Enable Register 2 (IE2)   |  |

| 9   | .2.4    | Interrupt Enable Register 3 (IE3)   |  |

| 9   | .2.5    | Interrupt Enable Register 4 (IE4)   |  |

| 9   | 0.2.6   | Interrupt Enable Register 5 (IE5)   |  |

| 9   | 0.2.7   | Interrupt Enable Register 6 (IE6)   |  |

| 9   | .2.8    | Interrupt Enable Register 7 (IE7)   |  |

| 9   | 0.2.9   | Interrupt Request Register 0 (IRQ0) |  |

| 9   | .2.10   | Interrupt Request Register 1 (IRQ1) |  |

| 9   | .2.11   | Interrupt Request Register 2 (IRQ2) |  |

| 9   | .2.12   | Interrupt Request Register 3 (IRQ3) |  |

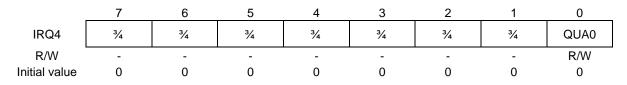

| 9   | .2.13   | Interrupt Request Register 4 (IRQ4) |  |

| 9   | .2.14   | Interrupt Request Register 5 (IRQ5) |  |

| 9   | .2.15   | Interrupt Request Register 6 (IRQ6) |  |

| 9   | .2.16   | Interrupt Request Register 7 (IRQ7) |  |

| 9.3 | B Des   | cription of Operation               |  |

| 9   | .3.1    | Maskable Interrupt Processing       |  |

| 9   | .3.2    | Non-Maskable Interrupt Processing   |  |

| 9   | .3.3    | Software Interrupt Processing       |  |

| 9   | 0.3.4   | Notes on Interrupt Routine          |  |

| 9   | .3.5    | Interrupt Disable State             |  |

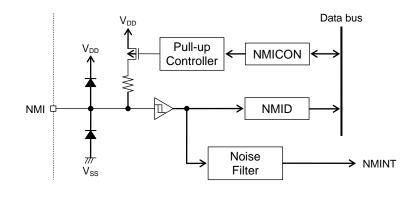

| 10. NMI Pin   |                               |  |

|---------------|-------------------------------|--|

| 10.1 Overview |                               |  |

| 10.1.1        | Features                      |  |

| 10.1.2        | Configuration                 |  |

| 10.1.3        | List of Pins                  |  |

|               | cription of Registers         |  |

| 10.2.1        | List of Registers             |  |

| 10.2.2        | NMI Data Register (NMID)      |  |

| 10.2.3        | NMI Control Register (NMICON) |  |

| 10.3 Des      | cription of Operation         |  |

| 10.3.1        | Interrupt Request             |  |

|               |                               |  |

#### Chapter 11

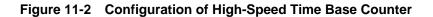

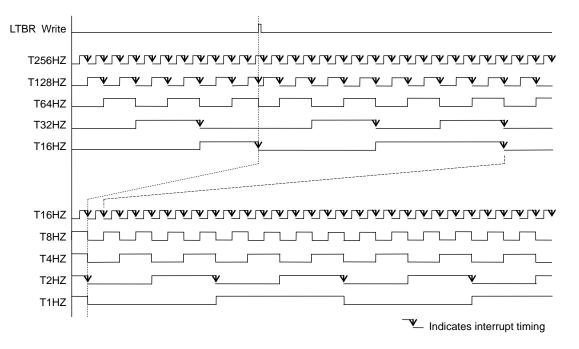

| 11. Time | Base Counter                                         |  |

|----------|------------------------------------------------------|--|

| 11.1 Ov  | erview                                               |  |

| 11.1.1   | Features                                             |  |

| 11.1.2   | Configuration                                        |  |

| 11.2 Des | scription of Registers                               |  |

| 11.2.1   | List of Registers                                    |  |

| 11.2.2   | Low-Speed Time Base Counter (LTBR)                   |  |

| 11.2.3   | High-Speed Time Base Counter Divide Register (HTBDR) |  |

| 11.3 Des | scription of Operation                               |  |

|          | Low-Speed Time Base Counter                          |  |

| 11.3.2   | High-Speed Time Base Counter                         |  |

|          |                                                      |  |

#### Chapter 12

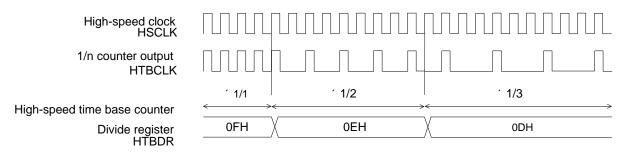

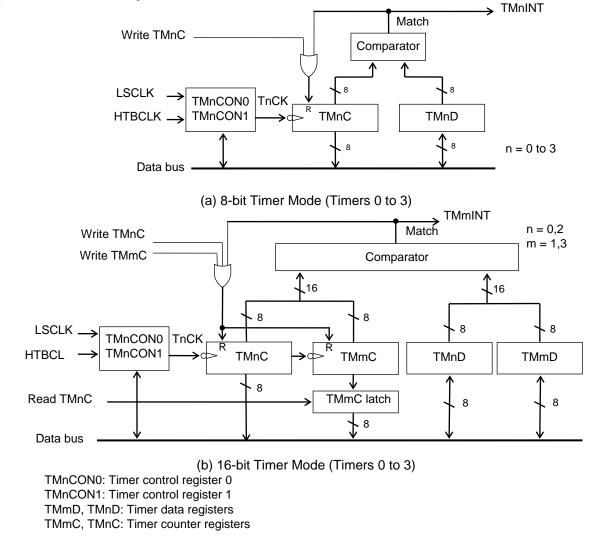

| 12. Timera                    | S                                    |      |

|-------------------------------|--------------------------------------|------|

| 12.1 Ove                      | erview                               | 12-1 |

| 12.1.1                        | Features                             |      |

| 12.1.2                        | Configuration                        |      |

| 12.2 Des                      | cription of Registers                |      |

| 12.2.1                        | List of Registers                    |      |

| 12.2.2                        | Timer 0 Data Register (TM0D)         |      |

| 12.2.3                        | Timer 1 Data Register (TM1D)         |      |

| 12.2.4                        | Timer 2 Data Register (TM2D)         |      |

| 12.2.5                        | Timer 3 Data Register (TM3D)         |      |

| 12.2.6                        | Timer 0 Counter Register (TM0C)      |      |

| 12.2.7                        | Timer 1 Counter Register (TM1C)      |      |

| 12.2.8                        | Timer 2 Counter Register (TM2C)      |      |

| 12.2.9                        | Timer 3 Counter Register (TM3C)      |      |

| 12.2.10                       | Timer 0 Control Register 0 (TM0CON0) |      |

| 12.2.11                       | Timer 1 Control Register 0 (TM1CON0) |      |

| 12.2.12                       | Timer 2 Control Register 0 (TM2CON0) |      |

| 12.2.13                       | Timer 3 Control Register 0 (TM3CON0) |      |

| 12.2.14                       | Timer 0 Control Register 1 (TM0CON1) |      |

| 12.2.15                       | Timer 1 Control Register 1 (TM1CON1) |      |

| 12.2.16                       | Timer 2 Control Register 1 (TM2CON1) |      |

| 12.2.17                       |                                      |      |

| 12.3 Description of Operation |                                      |      |

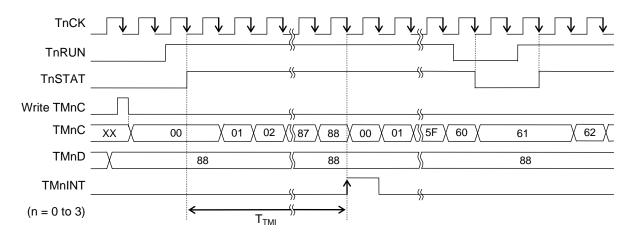

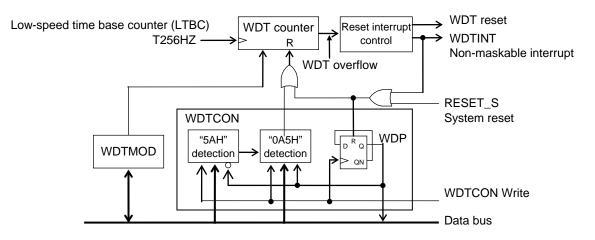

| 13. Watch                     | ıdog Timer                                         |  |

|-------------------------------|----------------------------------------------------|--|

|                               | erview                                             |  |

| 13.1.1                        | Features                                           |  |

| 13.1.2                        | Configuration                                      |  |

| 13.2 Description of Registers |                                                    |  |

| 13.2.1                        | List of Registers                                  |  |

| 13.2.2                        | Watchdog Timer Control Register (WDTCON)           |  |

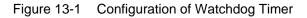

| 13.2.3                        | Watchdog Timer Mode Register (WDTMOD)              |  |

| 13.3 Description of Operation |                                                    |  |

| 13.3.1                        | Handling example when not using the watchdog timer |  |

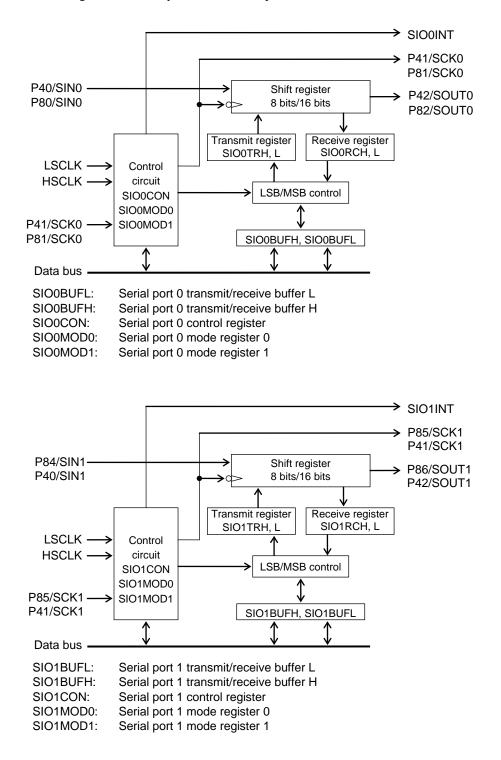

| 14. Synch | ronous Serial Port                                                                     | 14-1  |

|-----------|----------------------------------------------------------------------------------------|-------|

| 14.1 Ove  | erview                                                                                 | 14-1  |

| 14.1.1    | Features                                                                               |       |

| 14.1.2    | Configuration                                                                          |       |

| 14.1.3    | List of Pins                                                                           |       |

| 14.2 Des  | cription of Registers                                                                  |       |

| 14.2.1    | List of Registers                                                                      |       |

| 14.2.2    | Serial Porto Transmit/Receive Buffers (SIO0BUFL, SIO0BUFH)                             |       |

| 14.2.3    | Serial Port1 Transmit/Receive Buffers (SIO1BUFL, SIO1BUFH)                             |       |

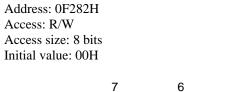

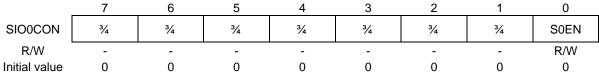

| 14.2.4    | Serial Port0 Control Register (SIO0CON)                                                |       |

| 14.2.5    | Serial Port1 Control Register (SIO1CON)                                                |       |

| 14.2.6    | Serial Port0 Mode Register 0 (SIO0MOD0)                                                |       |

| 14.2.7    | Serial Port1 Mode Register 0 (SIO1MOD0)                                                |       |

| 14.2.8    | Serial Port0 Mode Register 1 (SIO0MOD1)                                                |       |

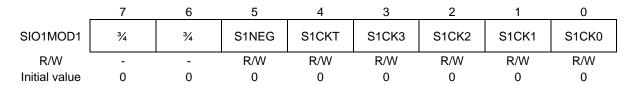

| 14.2.9    | Serial Port1 Mode Register 1 (SIO1MOD1)                                                | 14-11 |

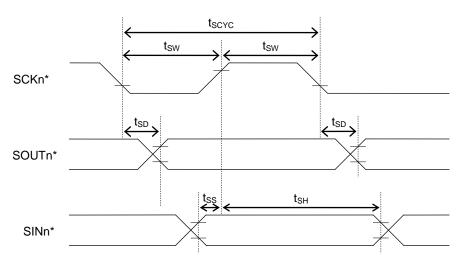

| 14.3 Des  | cription of Operation                                                                  | 14-12 |

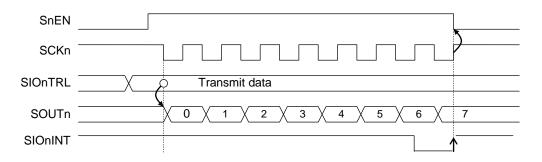

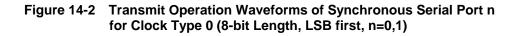

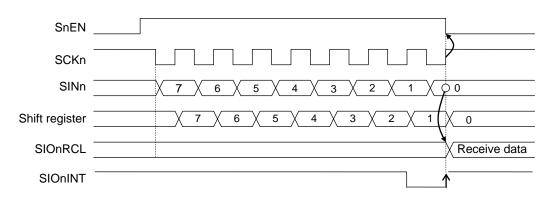

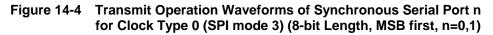

| 14.3.1    | Transmit Operation                                                                     | 14-12 |

| 14.3.2    | Receive Operation                                                                      | 14-13 |

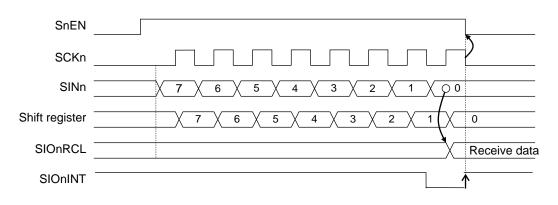

| 14.3.3    | Transmit/Receive Operation                                                             | 14-14 |

| 14.4 Reg  | ister setup of the port                                                                | 14-15 |

| 14.4.1    | When operating the SSIO0 function in master mode using P42 pin (SOUT0:output), P41 pin |       |

|           | (SCK0:input/output), and P40 pin (SIN0:input)                                          | 14-15 |

| 14.4.2    | When operating the SSIO0 function in slave mode using P42 pin (SOUT0:output), P41 pin  |       |

|           | (SCK0:input/output), and P40 pin (SIN0:input)                                          | 14-16 |

| 14.4.3    | When operating the SSIO0 function in master mode using P82 pin (SOUT0:output), P81 pin |       |

|           | (SCK0:input/output), and P80 pin (SIN0:input)                                          | 14-17 |

| 14.4.4    | When operating the SSIO0 function in slave mode using P82 pin (SOUT1:output), P81 pin  |       |

|           | (SCK1:input/output), and P80 pin (SIN1:input)                                          | 14-18 |

| 14.4.5    | When operating the SSIO1 function in master mode using P86 pin (SOUT1:output), P85 pin |       |

|           | (SCK1:input/output), and P84 pin (SIN1:input)                                          | 14-19 |

| 14.4.6    | When operating the SSIO1 function in slave mode using P86 pin (SOUT1:output), P85 pin  |       |

|           | (SCK1:input/output), and P84 pin (SIN1:input)                                          | 14-20 |

| 14.4.7    | When operating the SSIO1 function in master mode using P42 pin (SOUT1:output), P41 pin |       |

|           | (SCK1:input/output), and P40 pin (SIN1:input)                                          | 14-21 |

| 14.4.8    | When operating the SSIO1 function in slave mode using P42 pin (SOUT1:output), P41 pin  |       |

|           | (SCK1:input/output), and P40 pin (SIN1:input)                                          | 14-22 |

|           |                                                                                        |       |

| 15. UAR7 | Γ                                                                                      | 15-1  |

|----------|----------------------------------------------------------------------------------------|-------|

| 15.1 Ove | erview                                                                                 | 15-1  |

| 15.1.1   | Features                                                                               | 15-1  |

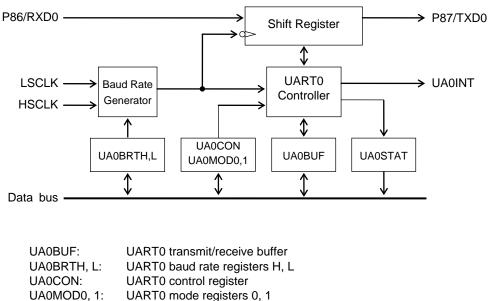

| 15.1.2   | Configuration                                                                          | 15-1  |

| 15.1.3   | List of Pins                                                                           | 15-2  |

| 15.2 Des | cription of Registers                                                                  | 15-2  |

| 15.2.1   | List of Registers                                                                      | 15-2  |

| 15.2.2   | UART0 Transmit/Receive Buffer (UA0BUF)                                                 |       |

| 12.2.3   | UART0 Control Register (UA0CON)                                                        |       |

| 12.2.4   | UART0 Mode Register 0 (UA0MOD0)                                                        |       |

| 12.2.5   | UART0 Mode Register 1 (UA0MOD1)                                                        |       |

| 12.2.6   | UARTO Baud Rate Registers L, H (UA0BRTL, UA0BRTH)                                      |       |

| 12.2.7   | UARTO Status Register (UA0STAT)                                                        |       |

| 15.3 Des | cription of Operation                                                                  |       |

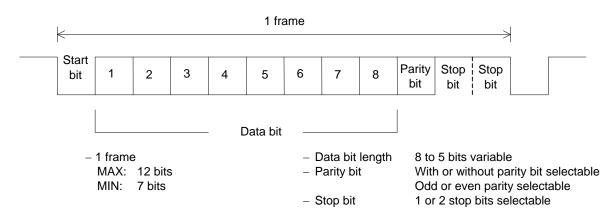

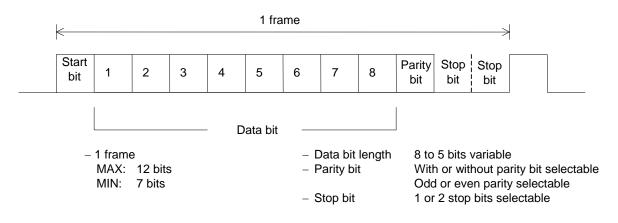

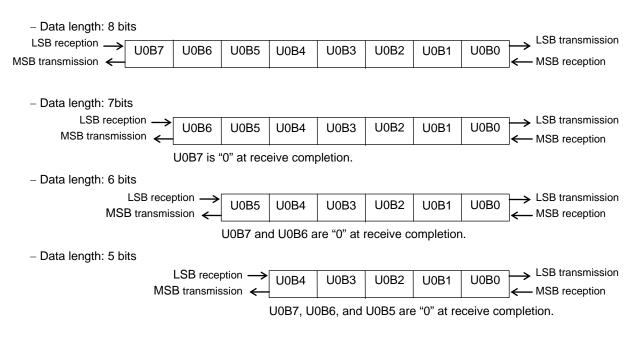

| 15.3.1   | Transfer Data Format                                                                   |       |

| 15.3.2   | Baud Rate                                                                              |       |

| 15.3.3   | Transmit Data Direction                                                                |       |

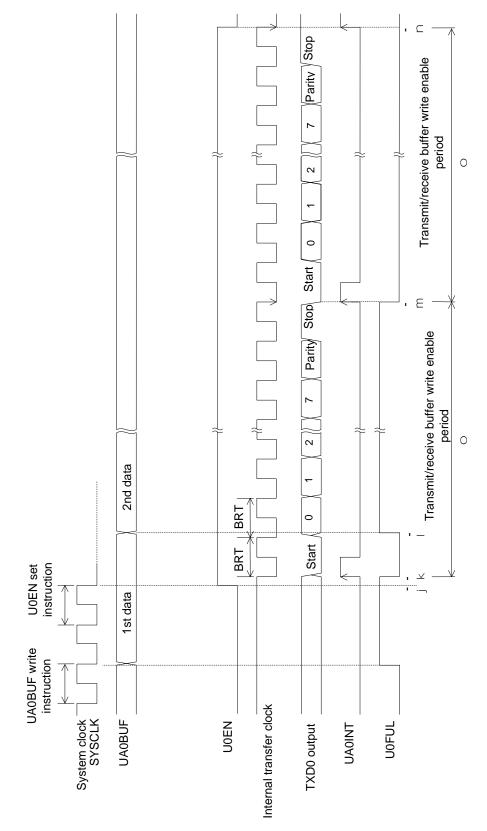

| 15.3.4   | Transmit Operation                                                                     |       |

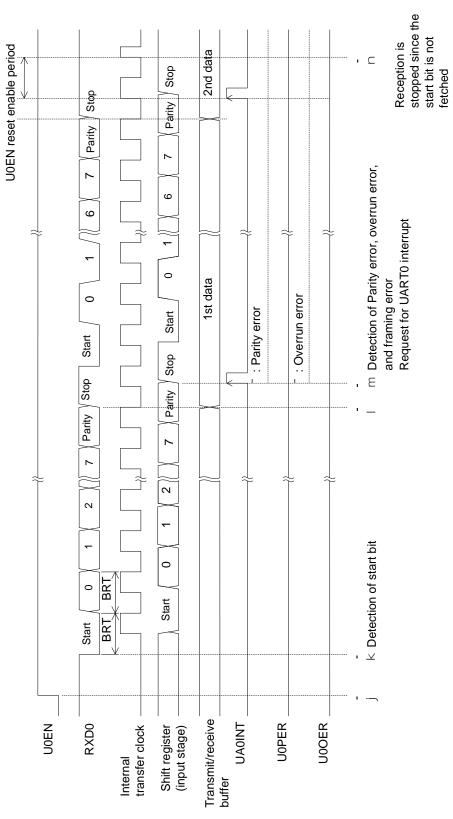

| 15.3.5   | Receive Operation                                                                      |       |

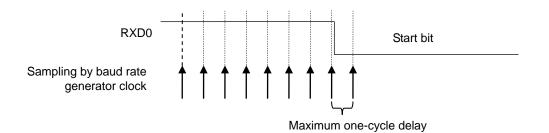

|          | .1 Detection of Start bit                                                              |       |

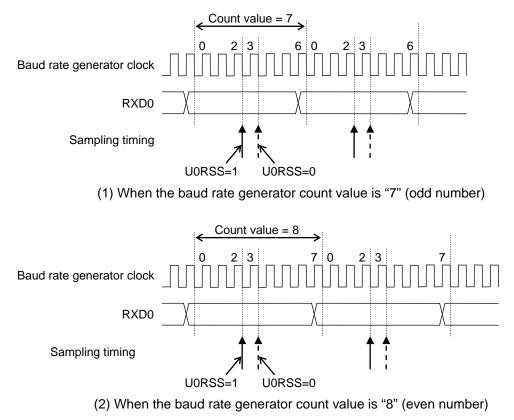

|          | .2 Sampling Timing                                                                     |       |

|          | .3 Reception Margin                                                                    |       |

|          | gister setup of the port                                                               |       |

| 15.4.1 V | When operating the UARTO function using P87 pin (TXD0:output) and P86 pin (RDX0:input) | 15-20 |

|          |                                                                                        |       |

|          | Is Interface (Master)                                     |  |

|----------|-----------------------------------------------------------|--|

| 16.1 Ove | rview                                                     |  |

| 16.1.1   | Features                                                  |  |

| 16.1.2   | Configuration                                             |  |

| 16.1.3   | List of Pins                                              |  |

| 16.2 Des | cription of Registers                                     |  |

| 16.2.1   | List of Registers                                         |  |

| 16.2.2   | I <sup>2</sup> C Bus 0 Receive Register (I2C0RD)          |  |

| 16.2.3   | I <sup>2</sup> C Bus 0 Slave Address Register (I2C0SA)    |  |

| 16.2.4   | I <sup>2</sup> C Bus 0 Transmit Data Register (I2C0TD)    |  |

| 16.2.5   | I <sup>2</sup> C Bus 0 Control Register (I2C0CON)         |  |

| 16.2.6   | I <sup>2</sup> C Bus 0 Mode Register (I2C0MOD)            |  |

| 16.2.7   | I <sup>2</sup> C Bus 0 Status Register (I2C0STAT)         |  |

| 16.3 Des | cription of Operation                                     |  |

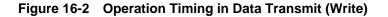

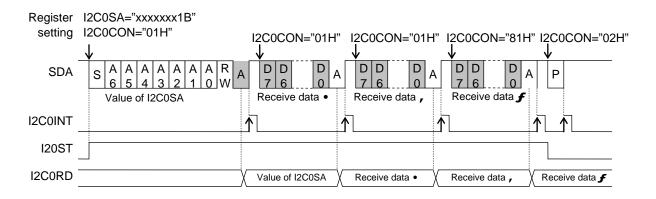

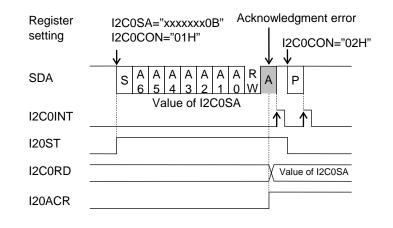

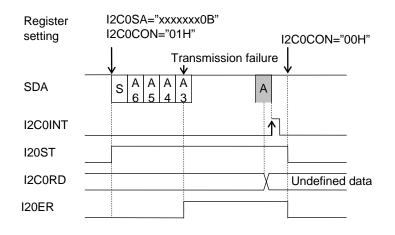

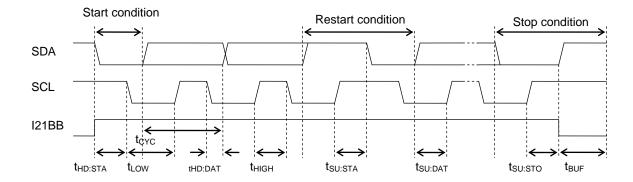

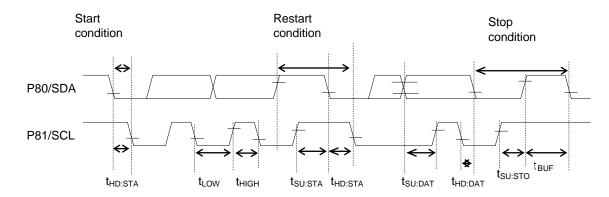

| 16.3.1   | Communication Operating Mode                              |  |

|          | .1 Start Condition                                        |  |

|          | 2 Restart Condition                                       |  |

|          | .3 Slave Address Transmit Mode                            |  |

|          | .4 Data Transmit Mode                                     |  |

|          | .5 Data Receive Mode                                      |  |

| 16.3.1   | .6 Control Register Setting Wait State                    |  |

| 16.3.1   | .7 Stop Condition                                         |  |

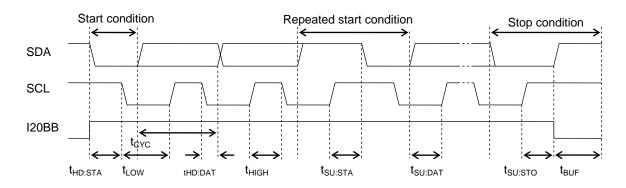

| 16.3.2   | Communication Operation Timing                            |  |

| 16.3.3   | Operation Waveforms                                       |  |

|          | cifying Port Registers                                    |  |

| 16.4.1   | Functioning P81(SCL) and P80(SDA) as the I <sup>2</sup> C |  |

|          |                                                           |  |

| $17 I^2 C P m$ | Interface (slave)                                         | 17 1 |

|----------------|-----------------------------------------------------------|------|

|                |                                                           |      |

|                | rview                                                     |      |

| 17.1.1         | Features                                                  |      |

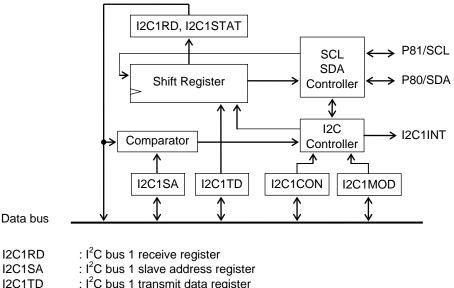

| 17.1.2         | Configuration                                             |      |

| 17.1.3         | List of Pins                                              |      |

| 17.2 Des       | cription of Registers                                     |      |

| 17.2.1         | List of Registers                                         |      |

| 17.2.2         | I <sup>2</sup> C Bus 1 Receive Register (I2C1RD)          |      |

| 17.2.3         | I <sup>2</sup> C Bus 1 Slave Address Register (I2C1SA)    |      |

| 17.2.4         | I <sup>2</sup> C Bus 1 Transmit Data Register (I2C1TD)    |      |

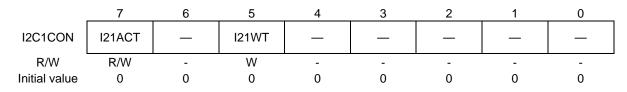

| 17.2.5         | I <sup>2</sup> C Bus 1 Control Register (I2C1CON)         |      |

| 17.2.6         | I <sup>2</sup> C Bus 1 Mode Register (I2C1MOD)            |      |

| 17.2.7         | I <sup>2</sup> C Bus 1 Status Register (I2C1STAT)         |      |

| 17.3 Des       | cription of Operation                                     |      |

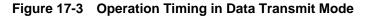

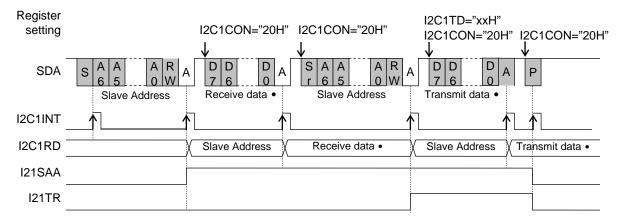

| 17.3.1         | Communication Operating Mode                              |      |

| 17.3.1         | 1 Start Condition                                         |      |

| 17.3.1         | 2 Slave Address Receive Mode                              |      |

|                | 3 Communication waiting state                             |      |

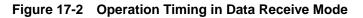

| 17.3.1         | 4 Data Transmit Mode                                      |      |

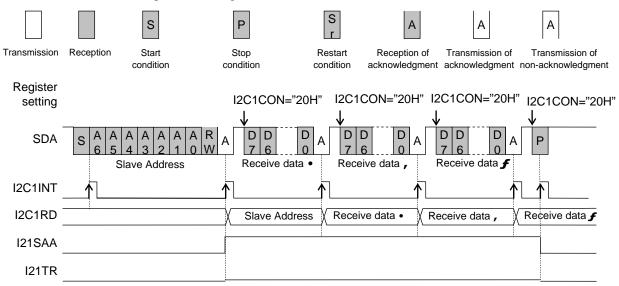

| 17.3.1         | 5 Data Receive Mode                                       |      |

| 17.3.1         | .6 Stop Condition                                         |      |

| 17.3.2         | Communication Operation Timing                            |      |

| 17.3.3         | Operation Waveforms                                       |      |

| 17.4 Spe       | cifying Port Registers                                    |      |

| 17.4.1         | Functioning P81(SCL) and P80(SDA) as the I <sup>2</sup> C |      |

|                |                                                           |      |

#### Chapter 18

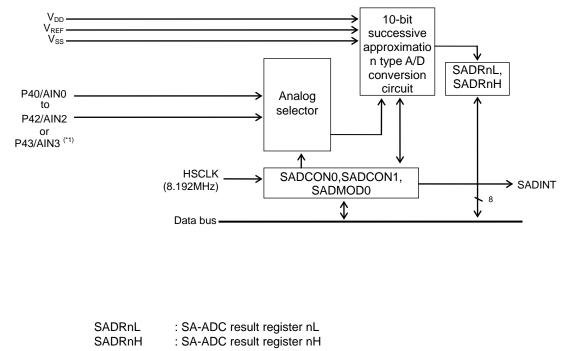

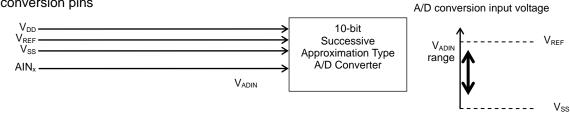

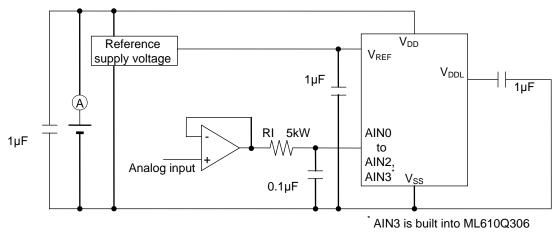

| 18. Succes | ssive Approximation Type A/D Converter (SA-ADC)          |  |

|------------|----------------------------------------------------------|--|

| 18.1 Ove   | erview                                                   |  |

| 18.1.1     | Features                                                 |  |

| 18.1.2     | Configuration                                            |  |

| 18.1.3     | List of Pins                                             |  |

| 18.2 Des   | cription of Registers                                    |  |

| 18.2.1     | List of Registers                                        |  |

| 18.2.2     | SA-ADC Result Register 0L (SADR0L)                       |  |

| 18.2.3     | SA-ADC Result Register 0H (SADR0H)                       |  |

| 18.2.4     | SA-ADC Result Register 1L (SADR1L)                       |  |

| 18.2.5     | SA-ADC Result Register 1H (SADR1H)                       |  |

| 18.2.6     | SA-ADC Result Register 2L (SADR2L)                       |  |

| 18.2.7     | SA-ADC Result Register 2H (SADR2H)                       |  |

| 18.2.8     | SA-ADC Control Register 0 (SADCON0)                      |  |

| 18.2.9     | SA-ADC Control Register 1 (SADCON1)                      |  |

| 18.2.10    | SA-ADC Mode Register 0 (SADMOD0)                         |  |

| 18.2.11    | SA-ADC Result Register 3L (SADR3L)                       |  |

| 18.2.12    | SA-ADC Result Register 3H (SADR3H)                       |  |

| 18.3 Des   | cription of Operation                                    |  |

| 18.3.1     | Setup of the A/D conversion channel                      |  |

| 18.3.2     | Operation of Successive Approximation Type A/D Converter |  |

|            |                                                          |  |

| 19. Audio | Playback Function                                             |  |

|-----------|---------------------------------------------------------------|--|

| 19.1 Ove  | rview                                                         |  |

| 19.1.1    | Features                                                      |  |

| 19.1.2    | Configuration                                                 |  |

| 19.1.2    | .1 Block Configuration                                        |  |

| 19.1.2    | .2 Placement of audio data                                    |  |

| 19.2 Des  | cription of Registers                                         |  |

| 19.2.1    | List of Registers                                             |  |

| 19.2.2    | Audio FIFO Data Register (VFDAT)                              |  |

| 19.2.3    | Audio FIFO Phrase End Data Register (VFEDAT)                  |  |

| 19.2.4    | Audio Status Register (VSTAT)                                 |  |

| 19.2.5    | Audio Mode Register (VMOD)                                    |  |

| 19.2.6    | Audio Data Type Register (VTYPE)                              |  |

| 19.2.7    | Volume Setting Register (VVOL)                                |  |

| 19.2.8    | Audio Playback Control Register (VCON)                        |  |

| 19.2.9    | HQ Phrase Stop-Bit Length Register (VHQSBL)                   |  |

| 19.2.10   | Volume Status Register (VVOLS)                                |  |

| 19.3 Des  | cription of Operation                                         |  |

| 19.3.1    | Audio Playback Operation                                      |  |

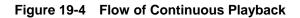

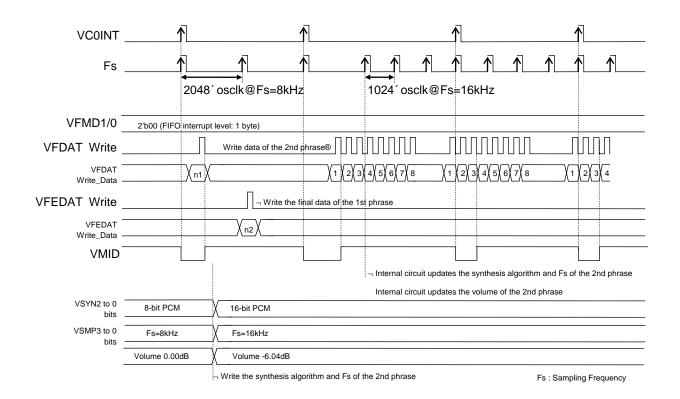

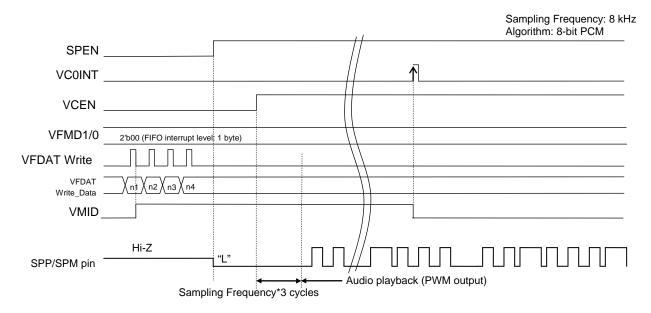

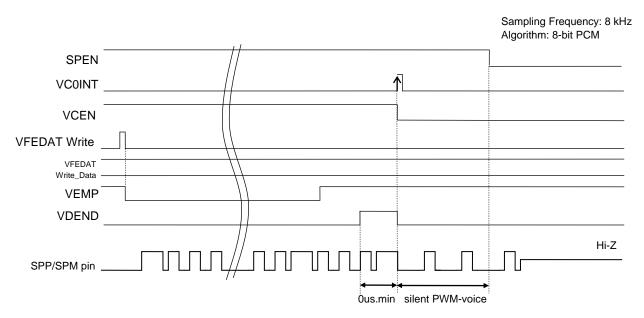

| 19.3.2    | Timing of Audio Playback Operation                            |  |

| 19.3.3    | Audio Code Data Configuration and Audio Data Creation Methods |  |

| 19.3.4    | Playback time and memory capacity                             |  |

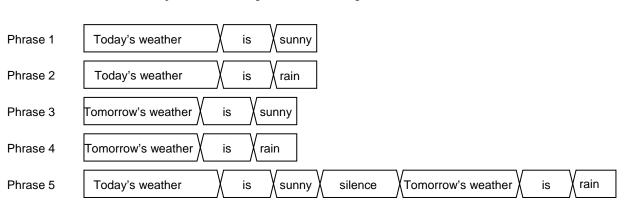

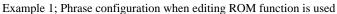

| 19.3.5    | Editing ROM function                                          |  |

#### Chapter 20

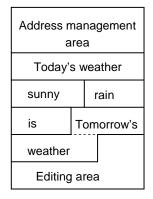

| 20. Spea                      | ker Amplifier                                                                  |  |

|-------------------------------|--------------------------------------------------------------------------------|--|

| 20.1 Ov                       | verview                                                                        |  |

| 20.1.1                        | Features                                                                       |  |

| 20.1.2                        | Configuration                                                                  |  |

| 20.2 De                       | escription of Registers                                                        |  |

| 20.2.1                        | List of Registers                                                              |  |

| 20.2.2                        | Speaker Amplifier Control Register (SPCON)                                     |  |

| 20.2.3                        | Disconnection Detection Control Register (DCDCON)                              |  |

| 20.2.4                        | Speaker Pin Short Detection Control Register (SDCON)                           |  |

| 20.3 Description of Operation |                                                                                |  |

| 20.3.1                        | Speaker Amplifier                                                              |  |

| 20.3.2                        | Disconnection Detection Circuit                                                |  |

| 20.3.3                        | Speaker Pin Short Detection Circuit                                            |  |

| 20.3.                         | 3.1 PWM "H" level fixation detection circuit operation                         |  |

| 20.3.                         | 20.3.3.2 SPP and SPM terminal of speaker Pin Short Detection Circuit operation |  |

|                               |                                                                                |  |

#### Chapter 21

| 21. Flash | memory self rewriting function         |  |

|-----------|----------------------------------------|--|

| 21.1 Ov   | erview                                 |  |

| 21.1.1    | Features                               |  |

| 21.2 Des  | cription of Registers                  |  |

| 21.2.1    | List of Registers                      |  |

| 21.2.2    | Flash address register L,H (FLASHAL,H) |  |

| 21.2.3    | Flash Data Register L,H (FLASHDL,H)    |  |

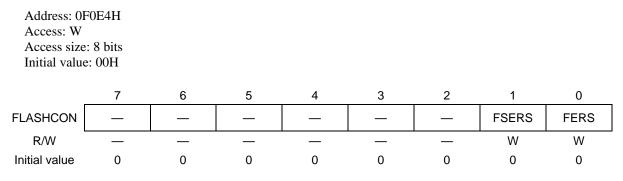

| 21.2.4    | Flash Control Register (FLASHCON)      |  |

| 21.2.5    | Flash Acceptor (FLASHACP)              |  |

| 21.2.6    | Flash Segment Register (FLASHSEG)      |  |

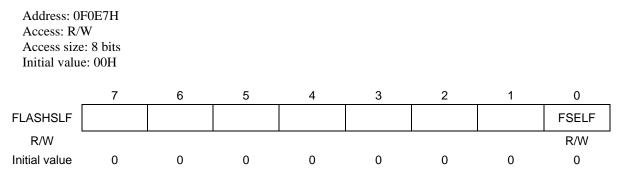

| 21.2.7    | Flash Self Register (FLASHSLF)         |  |

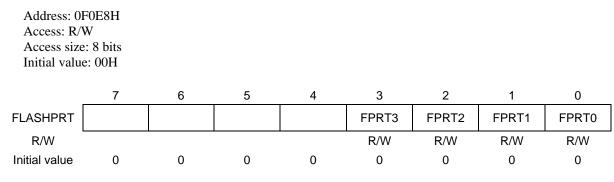

| 21.2.8    | Flash Protection Register (FLASHPRT)   |  |

| 21.3 Des  | scription of Operation                 |  |

| 21.3.1    | Sector Erase Function                  |  |

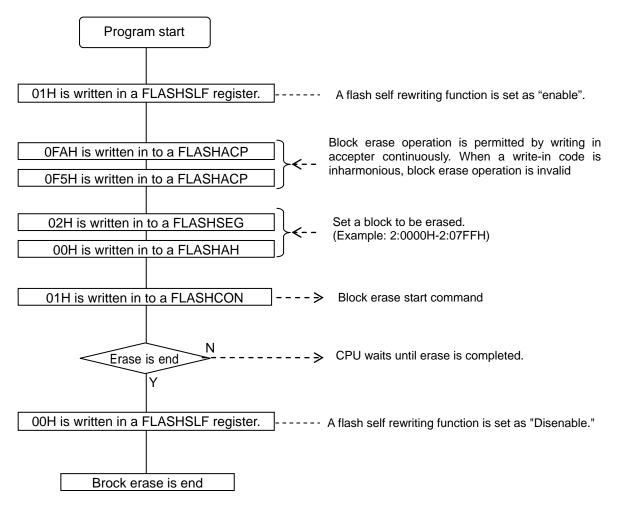

| 21.3.2    | Block Erase Function                   |  |

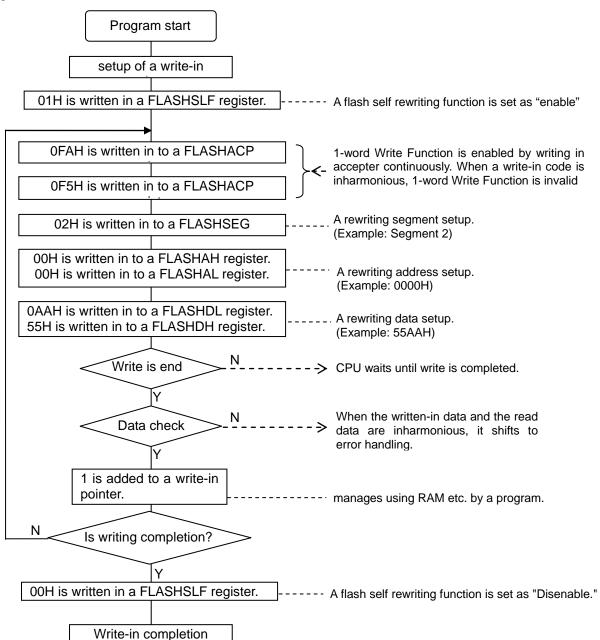

| 21.3.3    | 1-word Write Function                  |  |

| 21.3.4    | Notes in Use                           |  |

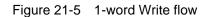

| 22. Power | r Supply Circuit       |  |

|-----------|------------------------|--|

|           | erview                 |  |

| 22.1.1    | Features               |  |

| 22.1.2    | Configuration          |  |

| 22.1.3    | List of Pins           |  |

| 22.2 Des  | scription of Operation |  |

|           | 1 1                    |  |

#### Chapter 23

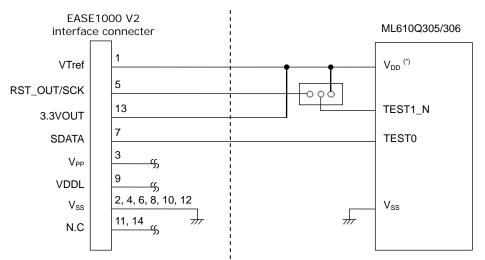

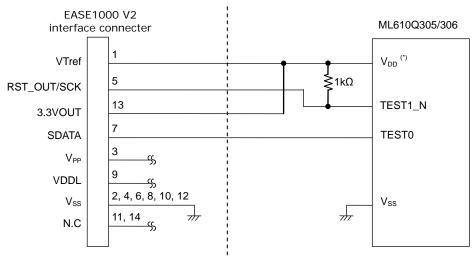

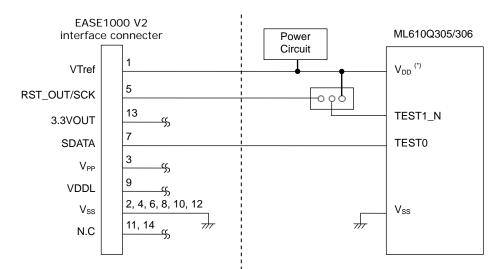

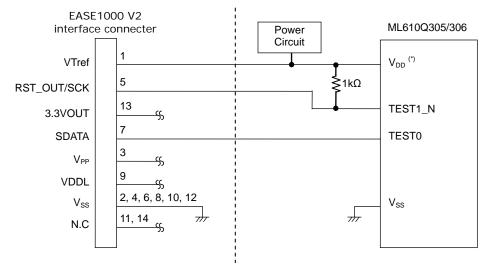

| 23. | On-Chip Debug Function                      | 23-1 |

|-----|---------------------------------------------|------|

|     | 1 Overview                                  |      |

| 23. | 2 How to Connect the On-Chip Debug Emulator | 23-1 |

#### Chapter 24

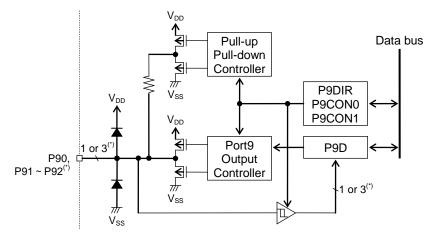

| 24. Port 9                                            |  |

|-------------------------------------------------------|--|

| 24.1 Overview                                         |  |

| 24.1.1 Features                                       |  |

| 24.1.2 Configuration                                  |  |

| 24.1.3 List of Pins                                   |  |

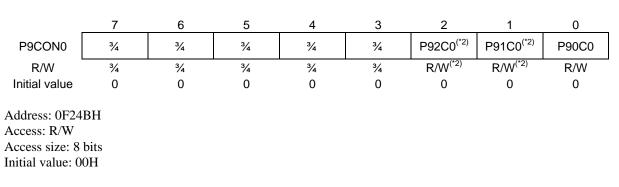

| 24.2 Description of Registers                         |  |

| 24.2.1 List of Registers                              |  |

| 24.2.2 Port 9 Data Register (P9D)                     |  |

| 24.2.3 Port 9 Direction Register (P9DIR)              |  |

| 24.2.4 Port 9 Control Registers 0, 1 (P9CON0, P9CON1) |  |

| 24.3 Description of Operation                         |  |

| 24.3.1 Input/Output Port Functions                    |  |

#### Chapter 25

| 25. Code option                                 |  |

|-------------------------------------------------|--|

| 25.1 Overview                                   |  |

| 25.1.1 Features                                 |  |

| 25.2 The Setting Method of the Code-Option Data |  |

| 25.2.1 Code-Option Data Format                  |  |

| 25.2.2 Code-Option Programming Method           |  |

| 25.3 The Method to refer the Code-Option Data   |  |

#### Appendixes

| Appendix A | Registers                             | A-1 |

|------------|---------------------------------------|-----|

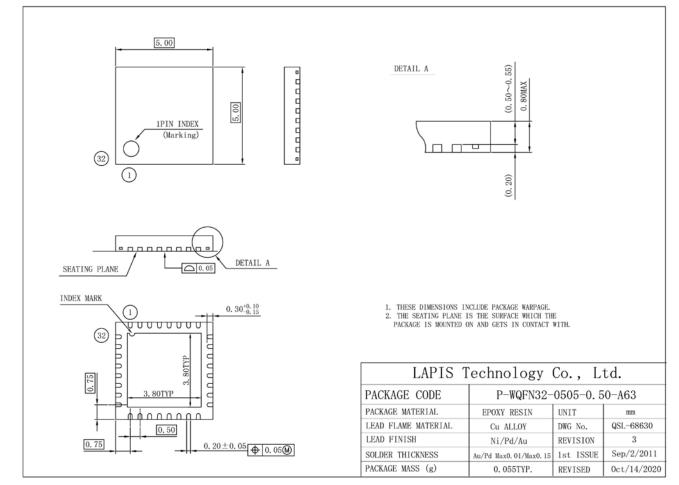

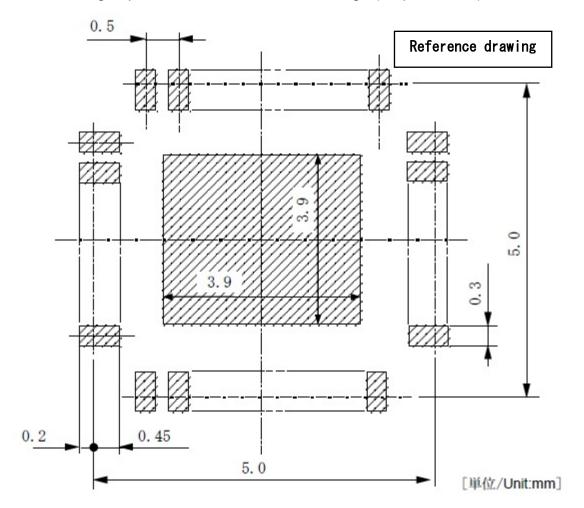

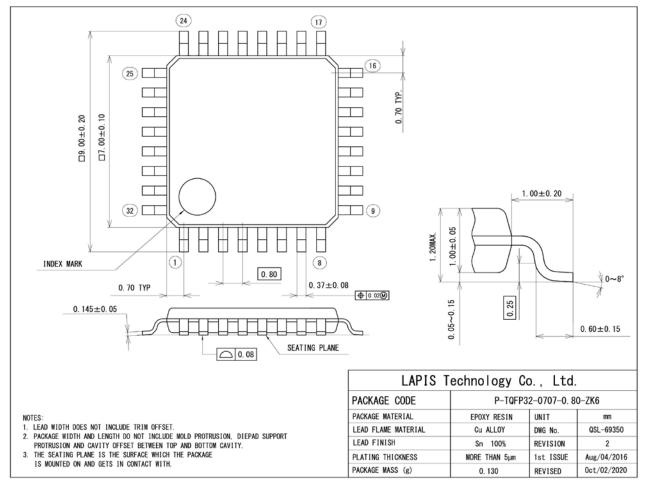

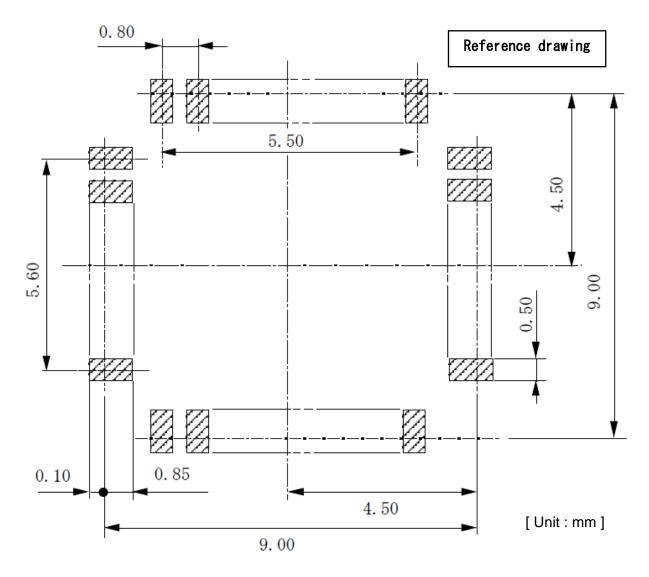

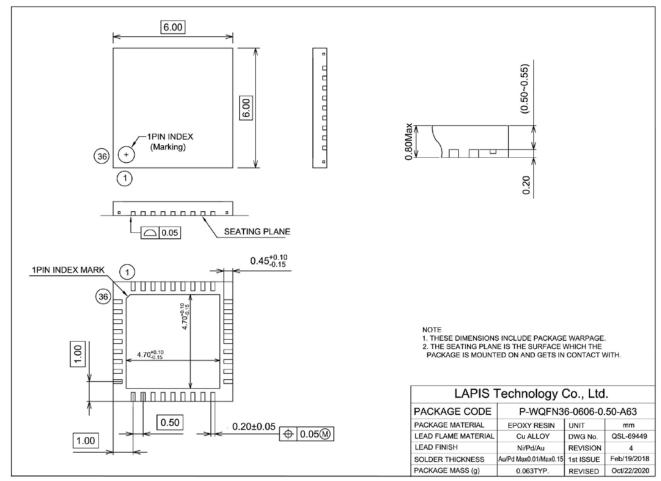

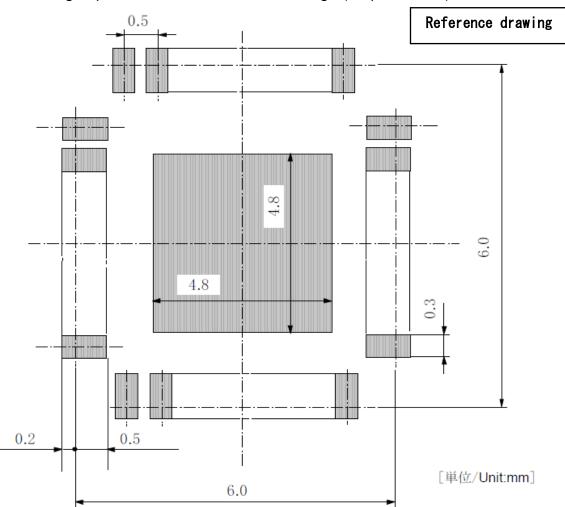

|            | Package Dimensions                    |     |

|            | Electrical Characteristics            |     |

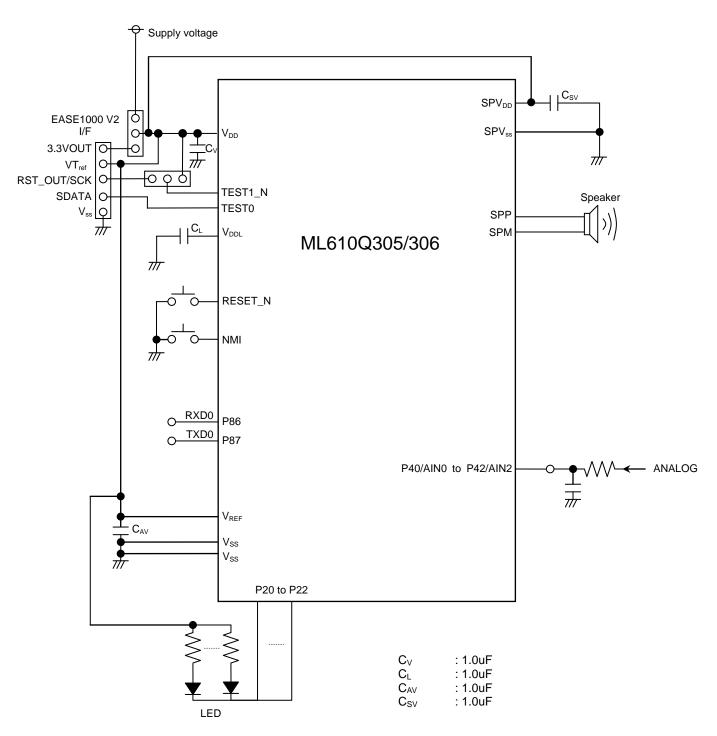

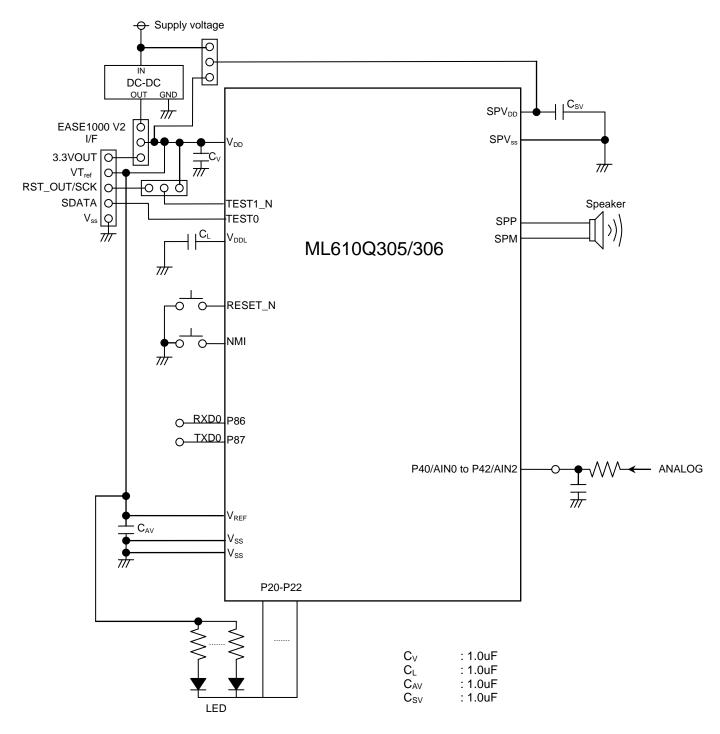

| Appendix D | The example of an application circuit | D-1 |

| Appendix E | Check List.                           | E-1 |

#### **Revision History**

| Revision HistoryR-1 |

|---------------------|

|---------------------|

Chapter 1

## Overview

#### 1. Overview

#### 1.1 Features

Equipped with a 8-bit CPU nX-U8/100, the ML610Q305/306 is a high-performance 8-bit CMOS microcontroller that integrates a wide variety of peripherals such as timer, synchronous serial port, and voice output function. The nX-U8/100 CPU is capable of executing instructions efficiently on a one-instruction-per-clock-pulse basis through parallel processing by the 3-stage pipelined architecture. The ML610Q305/306 is also equipped with a flash memory that has achieved low voltage and low power consumption (at read) equivalent to mask ROMs, so it is best suited to battery-driven applications such as alarm and portable devices. In addition, it has an on-chip debugging function, which allows software debugging/rewriting with the LSI mounted on the board.

- · CPU

- 8-bit RISC CPU (CPU name: nX-U8/100)

- Instruction system: 16-bit instructions

- Instruction set: Transfer, arithmetic operations, comparison, logic operations, multiplication/division, bit manipulations, bit logic operations, jump, conditional jump, call return stack manipulations, arithmetic shift, and so on

- On-Chip debug function

- Minimum instruction execution time Approx 30.5 ms (@32.768kHz system clock) Approx 0.244 ms (@4.096 MHz system clock)@V<sub>DD</sub>=2.0 to 5.5V Approx 0.122 ms (@8.192 MHz system clock)@V<sub>DD</sub>=2.2 to 5.5V

- Internal memory

- Has 96-Kbyte flash ROM(48K ' 16-bits) built in. (1 K byte of test domain that it cannot be used is included)

- Has 2-Kbyte flash ROM built in. (area in which self rewriting is possible (512byte ' 4))

- Internal 1Kbyte RAM (1K ' 8 bits)

- Interrupt controller

- 2 non-maskable interrupt sources Internal source: 1(Watchdog timer) External source: 1(NMI)

- 24 maskable interrupt sources

Internal source: 16(SSIO0, SSIO1, UART, I<sup>2</sup>C bus master/slave interface, Timer 0, Timer 1, Timer 2, Timer 3, A/D converter, Voice sound reproduction, Speaker pin short detection, TBC128Hz, TBC32Hz, TBC16Hz, TBC2Hz)

External source: 8(P80, P81, P82, P83, P84, P85, P86, P87)

- Time base counter

- Low-speed time base counter ' 1 channel

- High-speed time base counter ' 1 channel

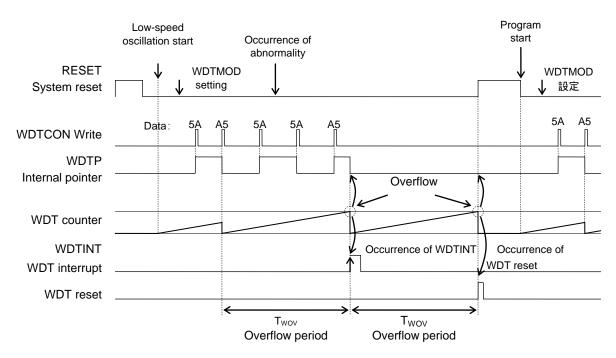

- Watchdog timer

- Generates a non-maskable interrupt upon the first overflow and a system reset occurs upon the second

- Free running

- Overflow period: 4 types selectable (125ms, 500ms, 2s, and 8s@32.768kHz)

- Timers

- 8 bits ' 4ch (16-bit configuration available)

- Voice output function

- Voice synthesis method: 4-bit ADPCM2 / non-linear PCM / straight 8-bit PCM / straight 16-bit PCM / HQ-ADPCM

- Sampling frequency: 8/16/32 kHz; 10.7/21.3 kHz; 6.4/12.8/25.6 kHz

- Successive approximation type A/D converter

- 10-bit A/D converter

- Input: 3ch (ch0-2:External input) (for ML610Q305) /

- 4ch (ch0-3:External input) (for ML610Q306)

- Conversion time: 24.4  $\mu s$  per channel at 4.096MHz  $V_{DD}\!\!\geq\!\!2.2V$

- Conversion time: 12.2  $\mu s$  per channel at 8.192MHz  $V_{DD}\!\!\geq\!\!2.5V$

- Continuous conversion / Single conversion selectable

- Synchronous serial port

- 2ch

- Master/slave selectable

- LSB first/MSB first selectable

- 8-bit length/16-bit length selectable

- UART

- Half-duplex  $\times$  1ch

- TXD/RXD

- Bit length, parity/no parity, odd parity/even parity, 1 stop bit/2 stop bits

- Positive logic/negative logic selectable

- Built-in baud rate generator

- I<sup>2</sup>C bus interface

- Master function: standard mode (100 kbps) and Fast mode (400 kbps)

- Slave function: standard mode (100 kbps) and Fast mode (400 kbps)

- General-purpose ports

- Input-only port 1ch

- Output-only port ' 3ch (including secondary functions)

- Input/output ' 12ch (including secondary functions)

- (P40 to P42 uses also as an A/D converter input port.)(for ML610Q305) /

- 15ch (including secondary functions)

- (P40 to P43 uses also as an A/D converter input port.) (for ML610Q306)

- Speaker amplifier(D-class) output power

- 1.0W(at 5.0V)/0.45W(at 3.0V)

- Disconnection detection circuit

- Speaker pin short detection circuit

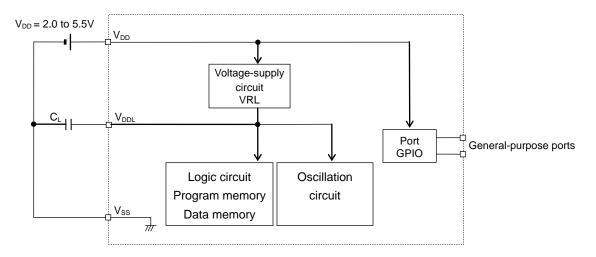

- Reset

- Reset through the RESET\_N pin

- Power-on reset generation when powered on

- Reset by the watchdog timer (WDT) overflow

- PLL oscillation stop detection reset

- Low level detection (LLD) reset

- Clock

- Low-speed clock

- Built-in RC oscillation (32.768 kHz)

- High-speed clock

- Built-in PLL oscillation (Approx. 1.024MHz / 2.048MHz / 4.096MHz / 8.192MHz)

- Power management

- STOP mode: Stop of oscillation (Operations of CPU and peripheral circuits are stopped.)

- HALT mode: Instruction execution by CPU is suspended (peripheral circuits are in operating states).

- Clock gear: The frequency of high-speed system clock can be changed by software (1/2, 1/4, 1/8, or 1/16 of the oscillation clock)

- Block control function: Operation of an intact functional block circuit is powerd down. (register reset and clock stop)

- Shipment

- 32-pin WQFN

- ML610Q305-xxxGD (blank product: ML610Q305-NNNGD) - 32-pin TOFP

- ML610Q305-xxxTB (blank product: ML610Q305-NNNTB) - 36-pin WQFN

- ML610Q306-xxxGD (blank product: ML610Q306-NNNGD) xxx: ROM code number

- Guaranteed operating range

- Operating temperature: 40°C to 85°C

- Operating voltage:  $V_{DD} = 2.0V$  to 5.5V,  $SPV_{DD} = 2.0V$  to 5.5V

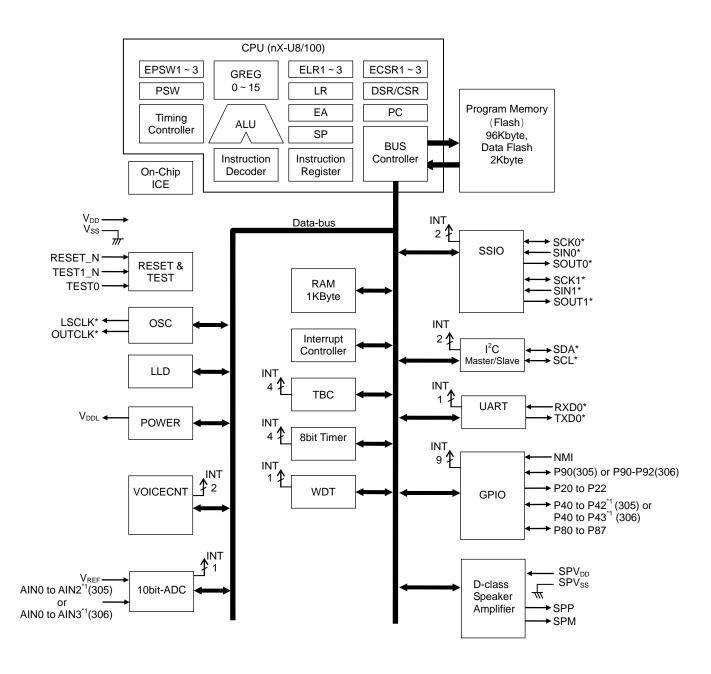

#### 1.2 Configuration of Functional Blocks

1.2.1 Block Diagram of ML610Q305/306

\*: Secondary or tertiary function

\*1: I/O port or A/D converter input terminal

Figure 1-1 Block Diagram of ML610Q305/306

- 1.3 Pins

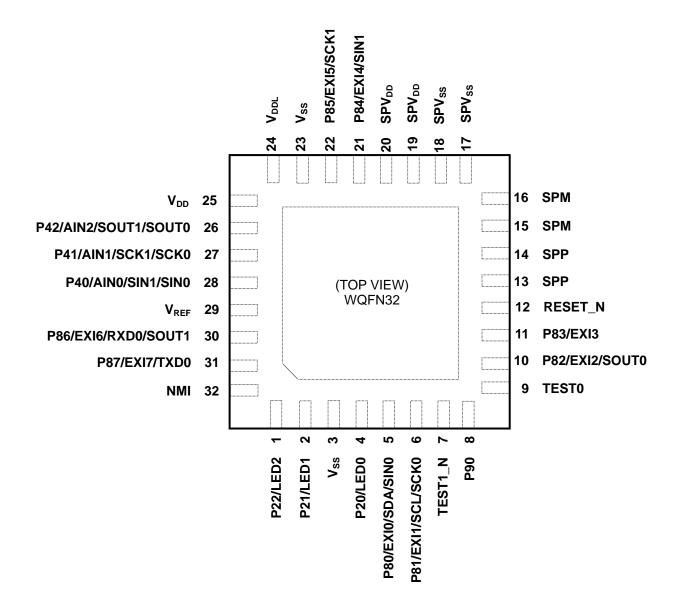

- 1.3.1 Pin Layout

1.3.1.1 Pin Layout of ML610Q305 32-pin WQFN Package (TOP View)

Figure 1-2 Pin Layout of 32-pin WQFN Package

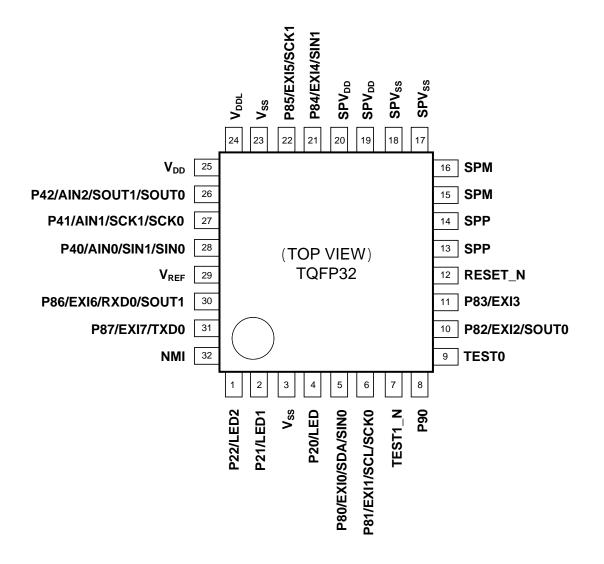

#### 1.3.1.2 Pin Layout of ML610Q305 32-pin TQFP Package (TOP View)

Figure 1-3 Pin Layout of 32-pin TQFP Package

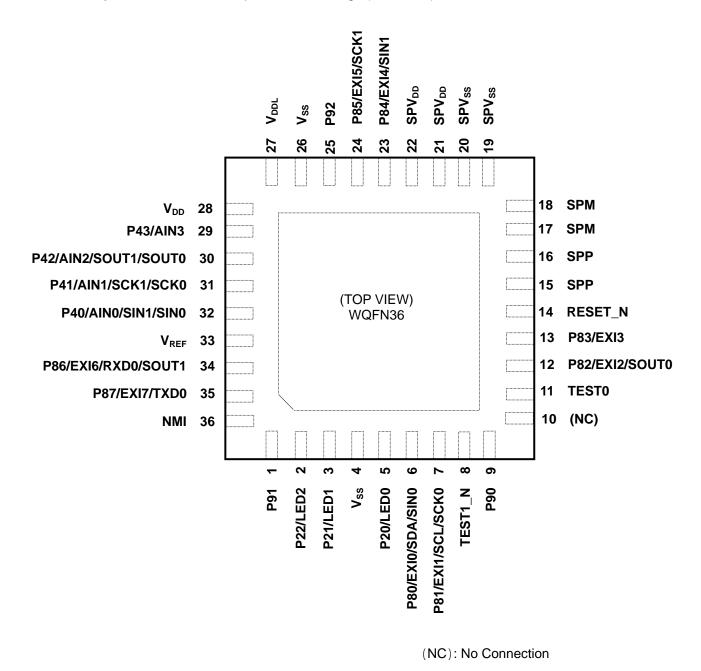

#### 1.3.1.3 Pin Layout of ML610Q306 36-pin WQFN Package (TOP View)

Figure 1-4 Pin Layout of 36-pin WQFN Package

#### 1.3.2 List of Pins

Table 1-1 lists the pins of the ML610Q305/306. In the I/O column, "—" denotes an input pin (for primary functions only), "I" an input pin, "O" an output pin, and "I/O" an input/output pin.

| 36pin  | 32pin         |                  | F   | Primary function                                                        | Secondary/Tertiary function             |              |                             |                                                 |  |  |

|--------|---------------|------------------|-----|-------------------------------------------------------------------------|-----------------------------------------|--------------|-----------------------------|-------------------------------------------------|--|--|

| WQFN   | WQFN<br>/TQFP | Pin name         | I/O | Description                                                             | Secondary/<br>Tertiary                  | Pin<br>name  | I/O                         | Description                                     |  |  |

| 15, 16 | 13, 14        | SPP              | 0   | Positive output pin of the<br>built-in speaker amplifier                | 3⁄4                                     | 3⁄4          | 3⁄4                         | 3⁄4                                             |  |  |

| 17, 18 | 15, 16        | SPM              | 0   | Negative output pin of the<br>built-in speaker                          | 3⁄4                                     | 3⁄4          | 3⁄4                         | 3⁄4                                             |  |  |

| 19, 20 | 17, 18        | SPVss            | 3⁄4 | Negative power supply pin for<br>built-in speaker amplifier             | 3⁄4                                     | 3⁄4          | 3⁄4                         | 3⁄4                                             |  |  |

| 21, 22 | 19, 20        | $SPV_{DD}$       | 3⁄4 | Positive power supply pin for<br>built-in speaker amplifier             | 3⁄4                                     | 3⁄4          | 3⁄4                         | 3⁄4                                             |  |  |

| 4, 26  | 3, 23         | V <sub>SS</sub>  | 3⁄4 | Negative power supply pin                                               | 3⁄4                                     | 3/4          | 3⁄4                         | 3⁄4                                             |  |  |

| 27     | 24            | V <sub>DDL</sub> | 3⁄4 | Power supply for internal logic<br>(internally generated)               | 3⁄4                                     | 3⁄4          | 3⁄4                         | 3⁄4                                             |  |  |

| 28     | 25            | V <sub>DD</sub>  | 3/4 | Positive power supply pin                                               | 3⁄4                                     | 3/4          | 3⁄4                         | 3/4                                             |  |  |

| 33     | 29            | $V_{REF}$        | 3⁄4 | Reference power supply pin for<br>successive- approximation<br>type ADC | 3/4                                     | 3⁄4          | 3⁄4                         | 3⁄4                                             |  |  |

| 14     | 12            | RESET_N          | Ι   | Reset input pin                                                         | 3⁄4                                     | 3⁄4          | 3⁄4                         | 3⁄4                                             |  |  |

| 11     | 9             | TEST0            | I/O | Input/output pin for testing                                            | 3⁄4                                     | 3⁄4          | 3⁄4                         | 3/4                                             |  |  |

| 8      | 7             | TEST1_N          |     | Input pin for testing                                                   | 3/4                                     | 3/4          | 3⁄4                         | 3/4                                             |  |  |

| 36     | 32            | NMI              | I   | Input port,<br>non-maskable interrupt                                   | 3⁄4                                     | 3⁄4          | 3⁄4                         | 3/4                                             |  |  |

| 5      | 4             | P20/LED0         | 0   | Output port / LED port                                                  | Secondary                               | LSCLK        | 0                           | Low-speed clock output                          |  |  |

| 3      | 2             | P21/LED1         | 0   | Output port / LED port                                                  | Secondary                               | OUTCLK       | 0                           | high-speed clock output                         |  |  |

| 2      | 1             | P22/LED2         | 0   | Output port / LED port                                                  | 3/4                                     | 3/4          | 3⁄4                         | 3/4                                             |  |  |

| 9      | 8             | P90              | 1/O | Input port/Output port                                                  | 3/4                                     | 3/4          | 3/4                         | 3/4                                             |  |  |

| 1      | 3/4           | P91              | I/O | Input port/Output port                                                  | 3/4                                     | 3/4          | 3/4                         | 3/4                                             |  |  |

| 25     | 3/4           | P92              | I/O | Input port/Output port                                                  | 3/4                                     | 3/4          | 3/4                         | 3/4                                             |  |  |

| 20     | /4            | 1 52             | 1/0 | Input port/Output port                                                  | Secondary                               | SIN1         | /4<br>                      | SSIO1 data input                                |  |  |

| 32     | 28            | P40/AIN0         | I/O | /Successive-approximation<br>type ADC input0                            | Tertiary                                | SIN0         | I                           | SSIO0 data input                                |  |  |

|        |               |                  |     | Input port/Output port                                                  | Secondary                               | SCK1         | I/O                         | SSIO1 synchronous clock input/output            |  |  |

| 31     | 27            | P41/AIN1         | I/O | /Successive-approximation type ADC input1                               | Tertiary                                | SCK0         | I/O                         | SSIO0 synchronous clock input/output            |  |  |

|        |               |                  |     | Input port/Output port                                                  | Secondary                               | SOUT1        | 0                           | SSIO1 data output                               |  |  |

| 30     | 26            | P42/AIN2         | I/O | /Successive-approximation<br>type ADC input2                            | Tertiary                                | SOUT0        | 0                           | SSIO0 data output                               |  |  |

| 29     | 3⁄4           | P43/AIN3         | I/O | Input port/Output port<br>/Successive-approximation<br>type ADC input3  | 3⁄4                                     | 3⁄4          | 3⁄4                         | 3⁄4                                             |  |  |

| 6      | 5             | P80/EX10         | I/O | Input port/Output port /                                                | Secondary                               | SDA          | I/O                         | I <sup>2</sup> C synchronous data input/ output |  |  |

| 0      | 5             | 100/2/10         | "0  | External interrupt                                                      | Tertiary                                | SIN0         |                             | SSIO0 data input                                |  |  |

| 7      | 6             | P81/EXI1         | I/O | Input port/Output port /                                                | Secondary                               | SCL          | I/O                         | I <sup>2</sup> C synchronous clock input/output |  |  |

| '      | 5             | 101/2/11         |     | External interrupt                                                      | Tertiary                                | SCK0         | I/O                         |                                                 |  |  |

| 12     | 10            | P82/EXI2         | I/O | Input port/Output port /<br>External interrupt                          | <sup>3</sup> ⁄ <sub>4</sub><br>Tertiary | 3⁄4<br>SOUT0 | <sup>3</sup> ⁄ <sub>4</sub> | 3/4<br>SSIO0 data output                        |  |  |

| 13     | 11            | P83/EXI3         | I/O | Input port/Output port /<br>External interrupt                          | 3/4                                     | 3⁄4          | 3⁄4                         | 3/4                                             |  |  |

| 23     | 21            | P84/EXI4         | I/O | Input port/Output port /<br>External interrupt                          | Tertiary                                | SIN1         | I                           | SSIO1 data input                                |  |  |

| 24     | 22            | P85/EXI5         | I/O | Input port/Output port /<br>External interrupt                          | Tertiary                                | SCK1         | I/O                         | SSIO1 synchronous clock input/output            |  |  |

| 34     | 30            | P86/EXI6         | I/O | Input port/Output port /<br>External interrupt                          | Secondary                               | RXD0         |                             | UART0 data                                      |  |  |

|        |               |                  |     |                                                                         | Tertiary                                | SOUT1        | 0                           | SSIO1 data                                      |  |  |

| 35     | 31            | P87/EXI7         | I/O | Input port/Output port /<br>External interrupt                          | Secondary                               | TXD0         | 0                           | UART0 data output                               |  |  |

Table 1-1 List of Pins

Note:

The function which is not chosen is lost when either a secondary function or a tertiary function is chosen. However, when using it as an input, read-out of an input data is possible at a PnD.

#### 1.3.3 Pin Description

Table 1-2 shows the pin description. In the I/O column, "—" denotes an input pin, "I" an input pin, "O" an output pin, and "I/O" an input/output pin.

| Pin name          | I/O                           | Primary/<br>Secondary/<br>Tertiary                                                                                                                                                                                                                         | Logic     |          |

|-------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|

| Power supply      |                               |                                                                                                                                                                                                                                                            |           |          |

| V <sub>SS</sub>   |                               | Negative power supply pin                                                                                                                                                                                                                                  | _         | _        |

| V <sub>DD</sub>   | _                             | Positive power supply pin                                                                                                                                                                                                                                  | _         | —        |

| V <sub>DDL</sub>  | —                             | Positive power supply pin for internal logic (internally generated)<br>Connect a capacitor (CL:1uF) between VDDL and Vss.                                                                                                                                  | _         | —        |

| SPV <sub>SS</sub> | _                             | Negative power supply pin for built-in speaker amplifier                                                                                                                                                                                                   | _         | —        |

| SPVDD             |                               | Positive power supply pin for built-in speaker amplifier                                                                                                                                                                                                   |           | _        |

| V <sub>REF</sub>  | _                             | Reference power supply pin for successive-approximation type ADC                                                                                                                                                                                           |           | _        |

| Test              |                               |                                                                                                                                                                                                                                                            |           |          |

| TEST0             | I/O                           | Input/output pin for testing. Has a pull-down resistor built in.                                                                                                                                                                                           |           | Positive |

| TEST1_N           | I                             | Input pin for testing. Has a pull-up resistor built in.                                                                                                                                                                                                    | _         | Negative |

| System            |                               |                                                                                                                                                                                                                                                            |           |          |

| RESET_N           | I                             | Reset input pin. When this pin is set to a "L" level, the device is placed in system reset mode and the internal circuit is initialized. If after that this pin is set to a "H" level, program execution starts. This pin has a pull-up resistor built in. | _         | Negative |

| LSCLK             | 0                             | Low-speed clock output. This function is allocated to the secondary function of the P20 pin.                                                                                                                                                               | Secondary | —        |

| OUTCLK            | 0                             | High-speed clock output. This function is allocated to the secondary function of the P21 pin.                                                                                                                                                              | Secondary | _        |

| General-purpos    | e Outp                        | ut port                                                                                                                                                                                                                                                    |           |          |

| P20 to P22        | General-purpose output ports. |                                                                                                                                                                                                                                                            | Primary   | Positive |

| General-purpos    | e Input                       |                                                                                                                                                                                                                                                            |           |          |

| P40 to P42        | I/O                           | General-purpose input/output ports.<br>Provided with a tertiary function. Cannot be used as ports if their tertiary function is used.                                                                                                                      | Primary   | Positive |

| P43               | I/O                           | General-purpose input/output port. (built into ML610Q306)                                                                                                                                                                                                  | Primary   | Positive |

| P80 to P87        | I/O                           | General-purpose input/output ports.<br>Provided with a secondary function or a tertiary function. Cannot<br>be used as ports if their secondary function or tertiary function is<br>used.                                                                  | Primary   | Positive |

| P90               | I/O                           | General-purpose input/output ports.                                                                                                                                                                                                                        | Primary   | Positive |

| P91 to P92        | I/O                           | General-purpose input/output port. (built into ML610Q306)                                                                                                                                                                                                  | Primary   | Positive |

#### Table 1-2 Pin Description

| Pin name                       | I/O     | Description                                                                                                                                                                                                                                | Primary/<br>Secondary/<br>Tertiary | Logic                 |

|--------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------|

| I <sup>2</sup> C bus interface | 9       |                                                                                                                                                                                                                                            |                                    |                       |

| SDA                            | I/O     | I <sup>2</sup> C data input/output pin. This pin is used as the secondary function of the P80 pin. This pin has a Nch open drain output. When using this pin as a function of the I <sup>2</sup> C, externally connect a pull-up resistor. | Secondary                          | Positive              |

| SCL                            | I/O     | I <sup>2</sup> C clock output pin. This pin is used as the secondary function of the P81 pin. This pin has a Nch open drain output. When using this pin as a function of the I <sup>2</sup> C, externally connect a pull-up resistor.      | Secondary                          | Positive              |

| Synchronous se                 | rial (S | SIO)                                                                                                                                                                                                                                       |                                    |                       |

| SINO                           | I       | Synchronous serial data input pin. Allocated to the tertiary function of the P40 pin and P80 pin.                                                                                                                                          | Tertiary                           | Positive              |

| SCK0                           | I/O     | Synchronous serial clock input/output pin. Allocated to the tertiary function of the P41 pin and P81 pin.                                                                                                                                  | Tertiary                           | _                     |

| SOUT0                          | 0       | Synchronous serial data output pin. Allocated to the tertiary function of the P42 pin and P82 pin.                                                                                                                                         | Tertiary                           | Positive              |

| SIN1                           | I       | Synchronous serial data input pin. Allocated to the tertiary function of the P84 pin and the secondary function of the P40 pin.                                                                                                            | Secondary/<br>Tertiary             | Positive              |

| SCK1                           | I/O     | Synchronous serial clock input/output pin. Allocated to the tertiary function of the P85 pin and the secondary function of the P41 pin.                                                                                                    | Secondary/<br>Tertiary             | _                     |

| SOUT1                          | 0       | Synchronous serial data output pin. Allocated to the tertiary function of the P86 pin and the secondary function of the P42 pin.                                                                                                           | Secondary/<br>Tertiary             | Positive              |

| UART                           |         |                                                                                                                                                                                                                                            |                                    |                       |

| TXD0                           | 0       | UART0 data output pin. Allocated to the secondary function of the P87 pin.                                                                                                                                                                 | Secondary                          | Positive              |

| RXD0                           | I       | UART0 data input pin. Allocated to the secondary function of the P86 pin.                                                                                                                                                                  | Secondary                          | Positive              |

| External interrup              | ot      |                                                                                                                                                                                                                                            |                                    |                       |

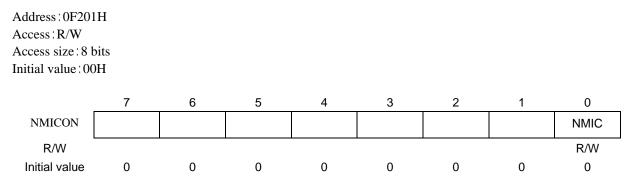

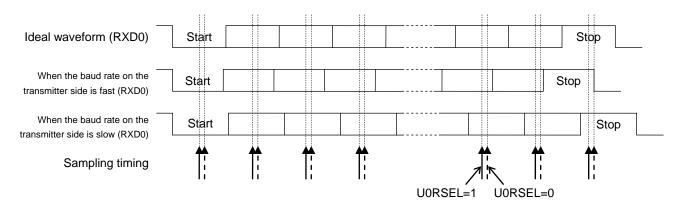

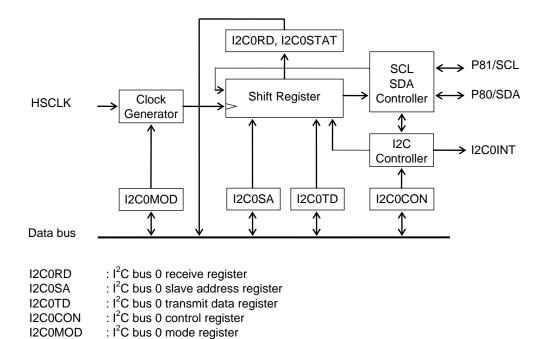

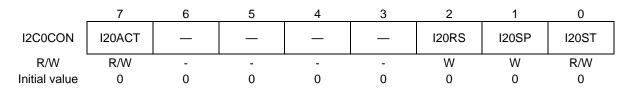

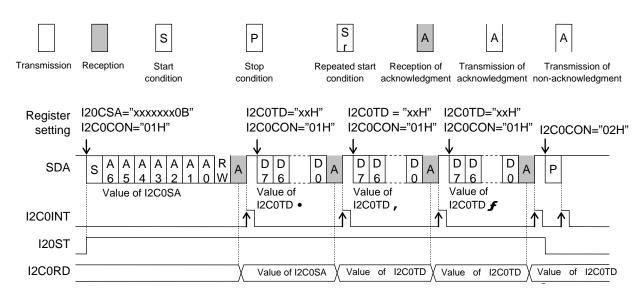

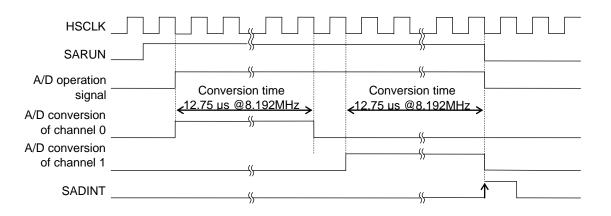

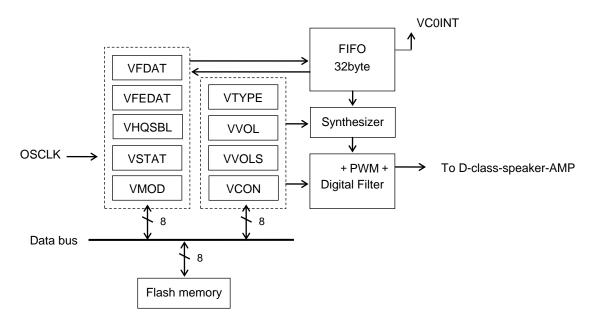

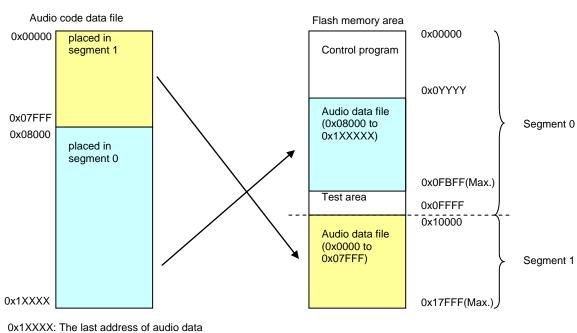

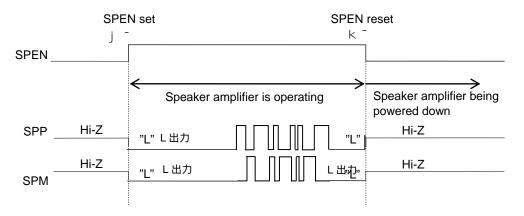

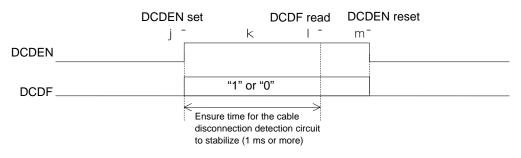

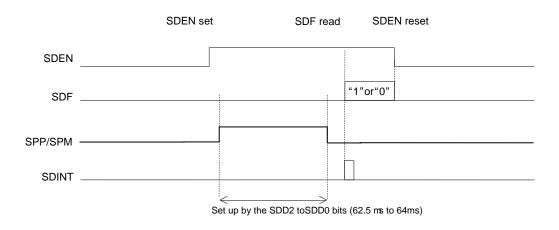

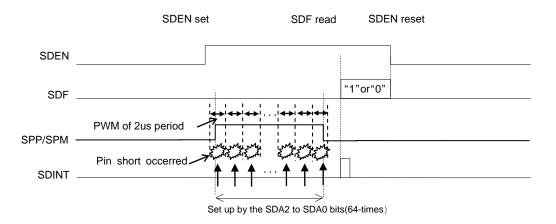

| NMI                            | Ι       | External non-maskable interrupt input pin. The interrupt occurs on both the rising and falling edges.                                                                                                                                      | Primary                            | Positive/<br>Negative |