Dear customer

ROHM Co., Ltd. ("ROHM"), on the 1st day of April, 2024, has absorbed into merger with 100%-owned subsidiary of LAPIS Technology Co., Ltd.

Therefore, all references to "LAPIS Technology Co., Ltd.", "LAPIS Technology" and/or "LAPIS" in this document shall be replaced with "ROHM Co., Ltd." Furthermore, there are no changes to the documents relating to our products other than the company name, the company trademark, logo, etc.

Thank you for your understanding.

ROHM Co., Ltd. April 1, 2024 ROHM GROUP LAPIS TECHNOLOGY ML5239

#### FEDL5239-07

January 9, 2024

Analog Front-End IC for 16-Serial-Cell Lithium-Ion Secondary Battery Protection

# General Description

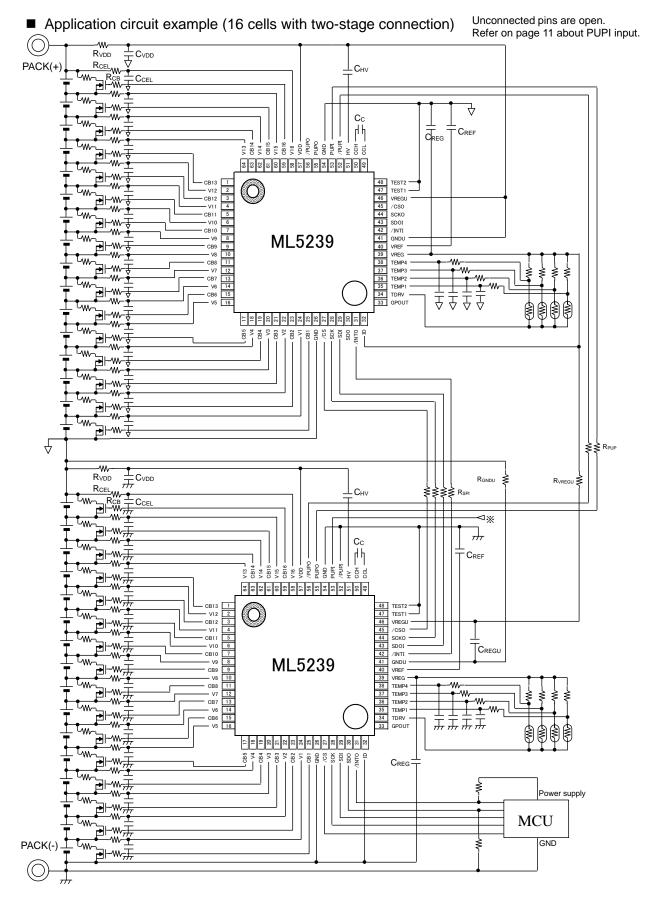

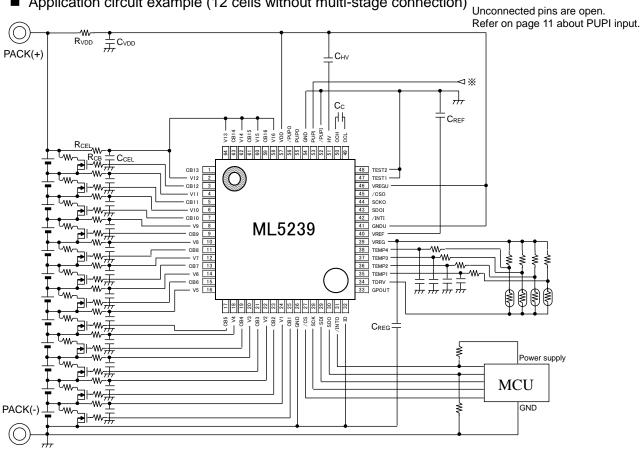

ML5239 is a power voltage monitoring IC for 5 to 16-cell lithium-ion secondary battery pack. It can be connected in multi-stage series to monitor the voltage of more than 17-cell lithium-ion battery. It also has a pin for driving an external cell balance FET, enabling to control the balance for each battery cell.

# Features

- 5 to 16 cell voltage measurement function Built-in 12-bit successive approximation type ADC Cell voltage measurement precision: ±10mV at 25°C, cell voltage 3.6V

- Cell voltage measurement time:1ms (typ)/cell

- Open/short detection function of cell voltage measurement pin

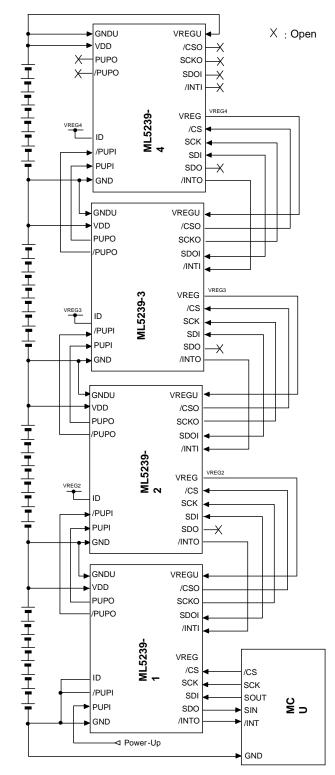

- Multi-stage series IC-IC communication function MCU interface: SPI serial interface CRC communication error detection

- SPI communication speed = 500kHz (max) at four-stage configuration Multi-stage connection ICs: 16 (max)

- Cell balance FET driving pin

- Temperature sensor input: 4 channels

- Current consumption

Cell voltage measurement state: 1.2mA (typ), 2.4mA (max)

Power-down state: 0.1µA (typ), 1µA (max)

- Power supply voltages: 10 to 72V

- Operational temperature: -40 to 85°C

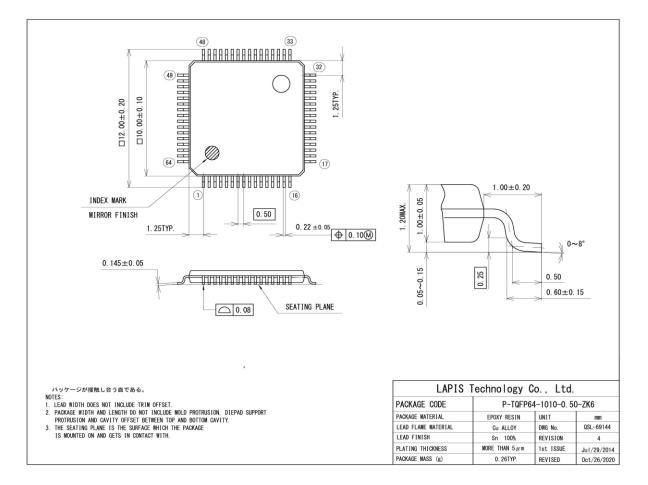

- Package: 64-pin plastic TQFP

- Application

- •Power tools and Garden tools

- •E-Bike and Electric assisted bicycle

- •Uninterruptible Power Supplies (UPS)

- •Energy Storage Systems (ESS)

```

Part number

```

ML5239TB

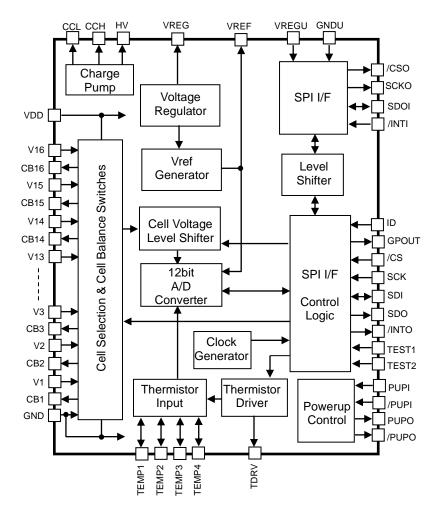

# Block Diagram

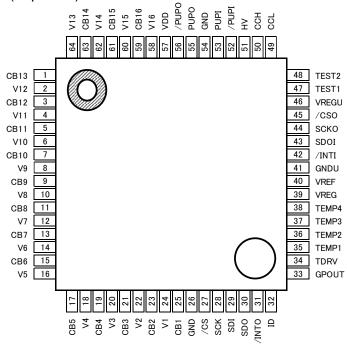

Pin Configuration (Top View)

|         | сприон   |     |                                                                                                                                                                |

|---------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No. | Pin name | I/O | Description                                                                                                                                                    |

| 1       | CB13     | 0   | Battery cell 13 cell balance control output pin.                                                                                                               |

|         |          |     | Battery cell 13 low voltage input and Battery cell 12 high voltage input pins.                                                                                 |

| 2       | V12      | 1   | If the number of connected battery cells is in the range of 5 to 11, input the                                                                                 |

| 2       | VIZ      | 1   | same potential as the highest V pin (V5 to V11) of the battery connected to                                                                                    |

|         |          |     | the IC.                                                                                                                                                        |

| 3       | CB12     | 0   | Battery cell 12 cell balance control output pin.                                                                                                               |

|         |          |     | Battery cell 12 low voltage input and Battery cell 11 high voltage input pins.                                                                                 |

| 4       | V11      | 1   | If the number of connected battery cells is in the range of 5 to 10, input the                                                                                 |

|         |          |     | same potential as the highest V pin (V5 to V10) of the battery connected to                                                                                    |

|         |          |     | the IC.                                                                                                                                                        |

| 5       | CB11     | 0   | Battery cell 11 cell balance control output pin.                                                                                                               |

|         |          |     | Battery cell 11 low voltage input and Battery cell 10 high voltage input pins.                                                                                 |

| 6       | V10      | I   | If the number of connected battery cells is in the range of 5 to 9, input the                                                                                  |

|         |          |     | same potential as the highest V pin (V5 to V9) of the battery connected to the                                                                                 |

| 7       | 0010     |     | IC.                                                                                                                                                            |

| 7       | CB10     | 0   | Battery cell 10 cell balance control output pin.                                                                                                               |

|         |          |     | Battery cell 10 low voltage input and Battery cell 9 high voltage input pins.<br>If the number of connected battery cells is in the range of 5 to 8, input the |

| 8       | V9       | I   | same potential as the highest V pin (V5 to V8) of the battery connected to the                                                                                 |

|         |          |     | IC.                                                                                                                                                            |

| 9       | CB9      | 0   | Battery cell 9 cell balance control output pin.                                                                                                                |

|         | 020      |     | Battery cell 9 low voltage input and Battery cell 8 high voltage input pins.                                                                                   |

|         |          |     | If the number of connected battery cells is in the range of 5 to 7, input the                                                                                  |

| 10      | V8       | I   | same potential as the highest V pin (V5 to V7) of the battery connected to the                                                                                 |

|         |          |     | IC.                                                                                                                                                            |

| 11      | CB8      | 0   | Battery cell 8 cell balance control output pin.                                                                                                                |

|         |          |     | Battery cell 8 low voltage input and Battery cell 7 high voltage input pins.                                                                                   |

| 40      | )/7      |     | If the number of connected battery cells is in the range of 5 to 6, input the                                                                                  |

| 12      | V7       | I   | same potential as the highest V pin (V5 to V6) of the battery connected to the                                                                                 |

|         |          |     | IC.                                                                                                                                                            |

| 13      | CB7      | 0   | Battery cell 7 cell balance control output pin.                                                                                                                |

|         |          |     | Battery cell 7 low voltage input and Battery cell 6 high voltage input pin.                                                                                    |

| 14      | V6       | I   | If the number of connected battery cells is in the range of 5, input the same                                                                                  |

|         |          |     | potential as the highest V pin (V5) of the battery connected to the IC.                                                                                        |

| 15      | CB6      | 0   | Battery cell 6 cell balance control output pin.                                                                                                                |

| 16      | V5       | I   | Battery cell 6 low voltage input and Battery cell 5 high voltage input pins.                                                                                   |

| 17      | CB5      | 0   | Battery cell 5 cell balance control output pin.                                                                                                                |

| 18      | V4       | I   | Battery cell 5 low voltage input and Battery cell 4 high voltage input pins.                                                                                   |

| 19      | CB4      | 0   | Battery cell 4 cell balance control output pin.                                                                                                                |

| 20      | V3       |     | Battery cell 4 low voltage input and Battery cell 3 high voltage input pins.                                                                                   |

| 21      | CB3      | 0   | Battery cell 3 cell balance control output pin.                                                                                                                |

| 22      | V2       |     | Battery cell 3 low voltage input and Battery cell 2 high voltage input pins.                                                                                   |

| 23      | CB2      | 0   | Battery cell 2 cell balance control output pin.                                                                                                                |

| 24      | V1       |     | Battery cell 2 low voltage input and Battery cell 1 high voltage input pins.                                                                                   |

| 25      | CB1      | 0   | Battery cell 1 cell balance control output pin.                                                                                                                |

| 26      | GND      | I — | These are ground pins.                                                                                                                                         |

| Pin No. | Pin name | I/O | Description                                                                                                                                                                                                                                                          |

|---------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27      | /CS      | I   | SPI interface chip select pin. The SPI interface is active if the input is "L" level. Be sure to input "H" level when completing one data write/read operation.                                                                                                      |

| 28      | SCK      | I   | SPI interface clock input pin. Capture the SDI input into the LSI at the rising edge of the SCK clock. Output the data from the SDO pin or SDI pin at the falling edge of the SCK.                                                                                   |

| 29      | SDI      | 10  | SPI interface data input pin.<br>It is data I/O pin for upper IC in multi-stage connection.                                                                                                                                                                          |

| 30      | SDO      | 0   | SPI interface data output pin. If /CS input is in "H" level, output of this pin is Hi-Z state.                                                                                                                                                                       |

| 31      | /INTO    | 0   | Interrupt signal output to an external MCU. This pin is an NMOS open drain output pin and outputs "L" level if interrupted.                                                                                                                                          |

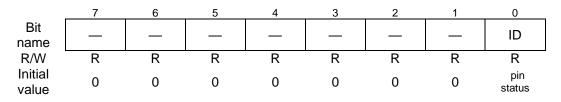

| 32      | ID       | I   | ID identification pin at multi-stage connection. Set it to the GND level without multi-stage connection or for the lowest IC connected with the external MCU. Set it to the VREG level of the IC at multi-stage connection for ICs other than the lowest one.        |

| 33      | GPOUT    | 0   | General output pin. This pin has an NMOS open drain output.                                                                                                                                                                                                          |

| 34      | TDRV     | 0   | Ground pin for thermistor. Set this to 0V output during temperature measurement or to be the Hi-Z state otherwise. This pin has an NMOS open drain output.                                                                                                           |

| 35      | TEMP1    | IO  | Temperature measurement thermistor connection pin. Connect an NTC                                                                                                                                                                                                    |

| 36      | TEMP2    | 10  | thermistor between this pin and the TDRV pin and a resistor between this pin                                                                                                                                                                                         |

| 37      | TEMP3    | IO  | and the VREG pin.                                                                                                                                                                                                                                                    |

| 38      | TEMP4    | IO  | This can be switched to general output by the register setting.                                                                                                                                                                                                      |

| 39      | VREG     | ο   | Built-in 5.3V regulator output pin. Connect a $1\mu$ F capacitor between this pin and GND. Power supply for IC internal circuit.                                                                                                                                     |

| 40      | VREF     | 0   | Reference voltage output pin for the built-in ADC. Connect a $1\mu$ F capacitor between this pin and GND.                                                                                                                                                            |

| 41      | GNDU     | _   | GND pin for the communication circuit with a higher IC at multi-stage connection. Connect to the GND pin of the higher IC via a resistor. Connect to the VDD pin without a higher IC.                                                                                |

| 42      | /INTI    | I   | Interrupt signal input pin from a higher IC at multi-stage connection. Connect to the /INTO pin of the higher IC via a resistor. It has a built-in $100k\Omega$ pull-up resistor between this pin and the VREGU pin. Set this to the open state without a higher IC. |

| 43      | SDOI     | ю   | Data I/O pin of the SPI interface with a higher IC at multi-stage connection.<br>Connect to the SDI pin of the higher IC via a resistor. Set this to the open<br>state without a higher IC.                                                                          |

| 44      | SCKO     | 0   | Serial clock output pin of the SPI interface with a higher IC at multi-stage connection. Connect to the SCK pin of the higher IC via a resistor. Set this to the open state without a higher IC.                                                                     |

| 45      | /CSO     | 0   | Chip select output pin of the SPI interface with a higher IC at multi-stage connection. Connect to the /CS pin of the higher IC via a resistor. Set this to the open state without a higher IC.                                                                      |

| 46      | VREGU    | _   | Power supply pin for the communication circuit with a higher IC at multi-stage connection. Connect to the VREG pin of the higher IC via a resistor. Connect to the VDD pin without a higher IC.                                                                      |

| 47      | TEST1    | I   | LSI test input pin. Fix to GND level.                                                                                                                                                                                                                                |

| Pin No. | Pin name | I/O | Description                                                                       |

|---------|----------|-----|-----------------------------------------------------------------------------------|

| 48      | TEST2    | I   | It has a built-in 1M $\Omega$ (typ) pull-down resistor in the LSI.                |

| 49      | CCL      | 0   | Connection pin of capacitor for the internal voltage multiplier circuit. Connect  |

| 49      | UCL      | 0   | a capacitor of $0.22\mu$ F between this pin and the CCH pin of this IC.           |

| 50      | ССН      | 0   | Connection pin of capacitor for the internal voltage multiplier circuit. Connect  |

| 50      | ССП      | 0   | a capacitor of $0.22\mu F$ between this pin and the CCL pin of this IC.           |

| 51      | HV       | 0   | Pin for smoothing multiplied voltage. Connect a capacitor of $0.22 \mu F$ between |

| 51      |          | 0   | this pin and the VDD pin of this IC.                                              |

|         |          |     | Power-up trigger signal input pin (reverse phase). The "L" pulse input moves      |

| 52      | /PUPI    | I   | the state from power-down to power-up. Set it to the GND level without            |

|         |          |     | multi-stage connection or for the lowest IC connected with the external MCU.      |

| 53      | DUDI     |     | Power-up trigger signal input pin (normal phase). The "H" pulse input moves       |

| 55      | PUPI     | I   | the state from power-down to power-up.                                            |

| 54      | GND      | _   | These are ground pins.                                                            |

|         |          |     | Power-up trigger signal output pin (normal phase). Connect to the PUPI pin        |

| 55      | PUPO     | 0   | of a higher IC via a resistor at multi-phase connection. Set this to the open     |

|         |          |     | state without a higher IC.                                                        |

|         |          |     | Power-up trigger signal output pin (reverse phase). Connect to the /PUPI pin      |

| 56      | /PUPO    | 0   | of a higher IC via a resistor at multi-phase connection. Set this to the open     |

|         |          |     | state without a higher IC.                                                        |

|         |          |     | Power supply input pin.                                                           |

| 57      | VDD      |     | Connect an external CR filter for noise rejection.                                |

|         |          |     | Battery cell 16 high voltage input pin.                                           |

| 50      | VAC      |     | If the number of connected battery cells is in the range of 5 to 15, input the    |

| 58      | V16      | I   | same potential as the highest V pin (V5 to V15) of the battery connected to       |

|         |          |     | the IC.                                                                           |

| 59      | CB16     | 0   | Battery cell 16 cell balance control output pin.                                  |

|         |          |     | Battery cell 16 low voltage input and Battery cell 15 high voltage input pins.    |

|         |          |     | If the number of connected battery cells is in the range of 5 to 14, input the    |

| 60      | V15      | I   | same potential as the highest V pin (V5 to V14) of the battery connected to       |

|         |          |     | the IC.                                                                           |

| 61      | CB15     | 0   | Battery cell 15 cell balance control output pin.                                  |

|         |          |     | Battery cell 15 low voltage input and Battery cell 14 high voltage input pins.    |

|         |          |     | If the number of connected battery cells is in the range of 5 to 13, input the    |

| 62      | V14      | I   | same potential as the highest V pin (V5 to V13) of the battery connected to       |

|         |          |     | the IC.                                                                           |

| 63      | CB14     | 0   | Battery cell 14 cell balance control output pin.                                  |

|         |          |     | Battery cell 14 low voltage input and Battery cell 13 high voltage input pins.    |

|         |          |     | If the number of connected battery cells is in the range of 5 to 12, input the    |

| 64      | V13      | I   | same potential as the highest V pin (V5 to V12) of the battery connected to       |

|         |          |     | the IC.                                                                           |

|                                 |                  |                                                                                                                                     |                                | )V, Ta = 25 |

|---------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------|

| Item                            | Symbol           | Condition                                                                                                                           | Rating                         | Unit        |

| Supply voltage                  | $V_{DD}$         | Potential difference between VDD, VREGU, GNDU, and HV                                                                               | -0.3 to +86.5                  | V           |

| Supply voltage                  | Vreg             | Potential difference between                                                                                                        | -0.3 to +6.5                   | V           |

| upply voltage                   | Vregu            | Potential difference between                                                                                                        | -0.3 to +6.5                   | V           |

|                                 | V <sub>IN1</sub> | Applied to V1 to V16, TEST1,<br>and TEST2 pins                                                                                      | -0.3 to V <sub>DD</sub> +0.3   | V           |

|                                 | V <sub>IN2</sub> | Applied to /CS, SCK, SDI,<br>TEMP1 to TEMP4, and ID pins                                                                            | -0.3 to V <sub>REG</sub> +0.3  | V           |

| Input voltage                   | Vin3             | Potential difference between<br>SDOI and /INTI pins and GNDU<br>pin                                                                 | -0.3 to V <sub>REGU</sub> +0.3 | V           |

|                                 | V <sub>IN4</sub> | Applied to PUPI and /PUPI pins                                                                                                      | -0.5 to V <sub>DD</sub> +0.3   | V           |

| Short-circuit<br>output current | los              | VDD=50V,<br>Applied to VREG, VREF, SDI,<br>SDO, /INTO, GPOUT, PUPO,<br>/PUPO, SDOI, /CSO, SCKO,<br>TDRV, and TEMP1 to TEMP4<br>pins | 20                             | mA          |

| Power dissipation               | PD               | Ta=25°C                                                                                                                             | 3.6                            | W           |

| Storage                         | Tstg             |                                                                                                                                     | -50 to +150                    | °C          |

# Absolute Maximum Ratings

# Recommended Operating Conditions

|                         | a oporating       | Contaitione                                                                   |            | (GND= 0V) |

|-------------------------|-------------------|-------------------------------------------------------------------------------|------------|-----------|

| Item                    | Symbol            | Condition                                                                     | Range      | Unit      |

|                         | VDD               | Applied to VDD pin                                                            | 10 to 72   | V         |

| Supply voltage          | V <sub>REGU</sub> | Potential difference between VREGU<br>and GNDU pins<br>(if there is upper IC) | 5.1 to 5.5 | V         |

| Operational temperature | Та                | No VREG output load                                                           | -40 to +85 | °C        |

# Electrical Characteristics

# • DC Characteristics

| $\nabla$ DC Characteristics<br>V <sub>DD</sub> = 10 to 72V. VREC | SU-GNDU           | = 5.1 to 5.5V, GND = 0V, T                                                   | a = -40 to +85         | °C. no ' | VREG output I         | oad  |

|------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------|------------------------|----------|-----------------------|------|

| Item                                                             | Symbol            | Condition                                                                    | Min.                   | Тур.     | Max.                  | Unit |

| Digital "H" input voltage (Note 1)                               | ViH               | _                                                                            | 0.8×V <sub>REG</sub>   |          | VREG                  | V    |

| Digital "L" input voltage (Note 1)                               | VIL               | _                                                                            | 0                      |          | 0.2×V <sub>REG</sub>  | V    |

| Digital "H" input voltage (Note 2)                               | VIHU              | GNDU pin reference                                                           | 0.8×V <sub>REGU</sub>  | _        | VREGU                 | V    |

| Digital "L" input voltage (Note 2)                               | VILU              | GNDU pin reference                                                           | 0                      | _        | 0.2×V <sub>REGU</sub> | V    |

| PUPI and /PUPI pins "H" input<br>voltage                         | VIHP              | —                                                                            | 3.6                    | _        | VDD                   | V    |

| PUPI and /PUPI pins "L" input<br>voltage                         | VILP              | _                                                                            | 0                      | _        | 0.7                   | V    |

| Digital "H" input current (Note 1)                               | Iн                | $V_{IH} = V_{REG}$                                                           | _                      |          | 2                     | μA   |

| Digital "L" input current (Note 1)                               | lı∟               | VIL = GND                                                                    | -2                     | _        |                       | μA   |

| Digital "H" input current (Note 2)                               | Ііни              | Vih = Vregu                                                                  | _                      |          | 2                     | μA   |

| SDOI pin "L" input current                                       | lilu              | VIL = GNDU                                                                   | -2                     | _        |                       | μA   |

| /INTI pin "L" input current                                      | lilu              | V <sub>REGU</sub> =5.3V, V <sub>IL</sub> =<br>GNDU                           | -106                   | -53      | -26                   | μA   |

| PUPI and /PUPI pins "H" input<br>current                         | IIHP              | V <sub>IH</sub> = 5V                                                         | _                      | _        | 2                     | μA   |

| PUPI and /PUPI pins "L" input<br>current                         | I <sub>ILP</sub>  | $V_{IL} = GND$                                                               | -2                     | _        |                       | μA   |

| Digital "H" output voltage (Note 3)                              | Vон               | Іон=-100μА                                                                   | V <sub>REG</sub> -0.2  | _        | Vreg                  | V    |

| Digital "L" output voltage (Note 4)                              | Vol               | lo∟=1mA                                                                      | 0                      | —        | 0.2                   | V    |

| Digital "H" output voltage (Note 5)                              | V <sub>они</sub>  | I <sub>OH</sub> =-100µA<br>GNDU pin reference                                | V <sub>REGU</sub> -0.2 | _        | V <sub>REGU</sub>     | V    |

| Digital "L" output voltage (Note 5)                              | Volu              | l <sub>o∟</sub> =1mA<br>GNDU pin reference                                   | 0                      | _        | 0.4                   | V    |

| PUPO and /PUPO pins "H" output voltage                           | V <sub>OHP</sub>  | I <sub>OH</sub> =-50μA<br>VDD pin reference                                  | V <sub>HV</sub> -0.2   | _        | $V_{HV}$              | V    |

| PUPO and /PUPO pins "L" output<br>voltage                        | Volp              | l <sub>oL</sub> =50μA<br>VDD pin reference                                   | 0                      | _        | 0.4                   | V    |

| Digital output leakage current<br>(*6)                           | Iolk              | V <sub>OH</sub> =V <sub>reg</sub> ,<br>V <sub>OL</sub> =0V                   | -2                     | _        | 2                     | μA   |

| VREG output voltage                                              | Vreg              | 10V < V <sub>DD</sub> pin voltage <<br>72V<br>Output load current <<br>1.5mA | 5.1                    | 5.3      | 5.5                   | v    |

| VREF output voltage                                              | V <sub>REF1</sub> | Output load current < 0.1µA                                                  | 4.68                   | 4.7      | 4.72                  | V    |

| HV pin output voltage range                                      | V <sub>HV</sub>   | VDD pin reference                                                            | 3.3                    | _        | 5.5                   | V    |

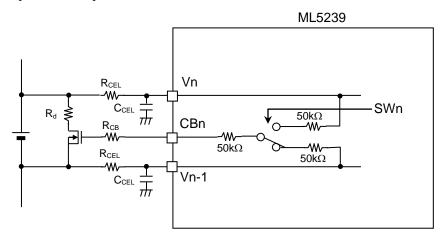

| CB pin output resistor                                           | Rсв               | _                                                                            | 50                     | 100      | 220                   | kΩ   |

| CB pin output voltage                                            | Vсв               | Applied to CBn pin<br>n=1 to 16                                              | Vn-1                   | _        | Vn                    | V    |

| VREG dropping detection voltage                                  | V <sub>RGD</sub>  | _                                                                            | 4.0                    | 4.3      | 4.6                   | V    |

| VREG return detection voltage                                    | Vrgr              | _                                                                            | 4.3                    | 4.7      | 5.1                   | V    |

Note 1: Applied to /CS, SCK, SDI, and ID pins.

Note 2: Applied to SDOI and /INTI pins.

Note 3: Applied to SDO, SDI, and TEMP1 to TEMP4 pins.

Note 4: Applied to SDO, /INTO, GPOUT, SDI, and TEMP1 to TEMP4 pins.

Note 5: Applied to /CSO, SCKO, and SDOI pins.

Note 6: Applied to SDO, /INTO, and GPOUT pins.

| $V_{DD}$ = 10 to 72V, GND = 0V, Ta = -40 to +85°C, no VREG and VREF output load. |                   |                                              |      |      |      |      |  |

|----------------------------------------------------------------------------------|-------------------|----------------------------------------------|------|------|------|------|--|

| Item                                                                             | Symbol            | Condition                                    | Min. | Тур. | Max. | Unit |  |

| Cell voltage measuring<br>state<br>supply current (Note 1)                       | I <sub>DD1</sub>  | Scan measurement<br>VREGU=GNDU=VDD           |      | 1.2  | 2.4  | mA   |  |

| Power-down<br>supply current (Note 1)                                            | IDDS              | VREGU=GNDU=VDD                               |      | 0.1  | 1.0  | μΑ   |  |

| VREGU power supply<br>current                                                    | I <sub>REGU</sub> | At multi-stage connection<br>VREGU-GNDU=5.3V |      | 250  | 500  | μA   |  |

# • Supply Current Characteristics

(Note 1) This is defined by total current flowing into the VDD and VREGU pins without multi-stage connection.

# • Cell Voltage Measurement Characteristics

|                                              | $V_{DD} = 10$ to 72V, GND = 0V, Ta = -40 to +85°C, no VREG output load |                                                    |      |           |      |      |  |

|----------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------|------|-----------|------|------|--|

| Item                                         | Symbol                                                                 | Condition                                          | Min. | Тур.      | Max. | Unit |  |

| Cell monitoring pin<br>input current         | I <sub>INVC</sub>                                                      | Cell voltage being<br>measured                     | -1   | —         | 1    | μΑ   |  |

| Cell monitoring pin<br>input leakage current | lilvc                                                                  | Cell voltage not<br>being measured                 | -1   | _         | 1    | μΑ   |  |

| Cell voltage                                 | Vcert                                                                  | Each cell voltage =<br>3.6V<br>Ta= 25°C            | -10  |           | 10   | mV   |  |

| measurement error                            | Vcer                                                                   | Each cell voltage = 1<br>to 4.3V<br>Ta=-10 to 60°C | -25  |           | 25   | mV   |  |

| Measurement resolution                       | VLSB                                                                   | —                                                  |      | 5000/4095 |      | mV   |  |

| Cell voltage                                 | <b>t</b> SCAN                                                          | 16-cell scan<br>measurement                        | 7.0  | 8.3       | 10.0 | ms   |  |

| measurement time                             | t <sub>SEL</sub>                                                       | Select measurement                                 | 0.8  | 1         | 1.2  | ms   |  |

| $V_{DD}$ = 10 to 72V, GND = 0V, Ta = -40 to +85°C, no VREG output load |                   |                                               |      |           |      |      |

|------------------------------------------------------------------------|-------------------|-----------------------------------------------|------|-----------|------|------|

| Item                                                                   | Symbol            | Condition                                     | Min. | Тур.      | Max. | Unit |

| TEMP1 - TEMP4 pins<br>input current                                    | I <sub>TEMP</sub> | TEMP input = 0.4 to<br>4.5V                   | -2   | —         | 2    | μΑ   |

| TDRV pin<br>"L" output voltage                                         | Volt              | TDRV bit = "0"<br>I <sub>OL</sub> =1mA        | 0    | _         | 0.1  | V    |

| TDRV pin<br>output leakage current                                     | Itdrv             | TDRV bit = "1"<br>TDRV pin voltage=0<br>to 3V | -2   | _         | 2    | μA   |

| TEMP pin<br>input voltage<br>measurement error                         | V <sub>TER</sub>  | TEMP input = 0.4 to<br>4.5V<br>Ta=-10 to 60°C | -20  | _         | 20   | mV   |

| Measurement resolution                                                 | VLSB              | _                                             | _    | 4700/4095 | —    | mV   |

| Temperature                                                            | <b>t</b> SCAN     | 4 temperature scan<br>measurement             | 1.9  | 2.3       | 2.7  | ms   |

| measurement time                                                       | t <sub>SEL</sub>  | Select measurement                            | 0.8  | 1         | 1.2  | ms   |

# • Temperature Sensor Input Measurement Characteristics

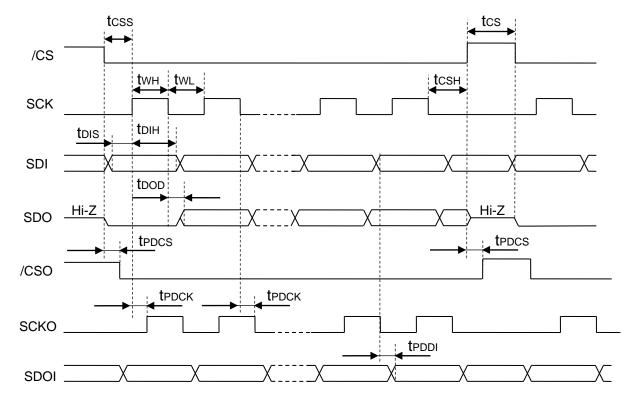

## • AC Characteristics

| V <sub>DD</sub> = 10 to 72V, VREGU-GNDU = 5.1 to 5.5V, GND = 0V, Ta = -40 to +85°C, no VREG output load |                   |                                                         |      |      |      |      |

|---------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------|------|------|------|------|

| Item                                                                                                    | Symbol            | Condition                                               | Min. | Тур. | Max. | Unit |

| SPI communication speed                                                                                 | fck               | operating at 4 or<br>less-stage<br>configuration(Note1) | 100  | _    | 500  | kHz  |

| SPI communication speed<br>(ID Automatic Setting)                                                       | fckid             | operating at 2 to 16<br>stage<br>configuration(Note1)   | 500  | _    | 650  | kHz  |

| /CS-SCK setup time                                                                                      | tcss              |                                                         | 1000 | _    | —    | ns   |

| SCK-/CS hold time                                                                                       | tсsн              |                                                         | 1000 | _    | —    | ns   |

| SCK "H" pulse width                                                                                     | t <sub>WH</sub>   |                                                         | 950  | _    | —    | ns   |

| SCK "L" pulse width                                                                                     | tw∟               |                                                         | 950  |      | _    | ns   |

| SCK-SDI setup time                                                                                      | t <sub>DIS</sub>  |                                                         | 200  | _    | —    | ns   |

| SCK-SDI hold time                                                                                       | tын               |                                                         | 200  |      | —    | ns   |

| SCK-SDO output delay<br>time                                                                            | tdod              |                                                         | —    | —    | 700  | ns   |

| /CS "H" pulse width                                                                                     | t <sub>CS</sub>   |                                                         | 2    | _    | —    | μs   |

| /CS-/CSO output delay time                                                                              | <b>t</b> PDCS     | operating at 4 or<br>less-stage                         |      |      | 100  | ns   |

| SCK-SCKO output delay<br>time                                                                           | tроск             | configuration(Note1)                                    | _    | —    | 100  | ns   |

| SDI-SDOI output delay<br>time                                                                           | tpddi             |                                                         | —    | —    | 115  | ns   |

| /CSO and SCKO output<br>delay time difference                                                           | tpdcs-tp<br>dcк   |                                                         | 0    | _    | 15   | ns   |

| SCKO and SDOI output delay time difference                                                              | tpddi-tp<br>dcк   |                                                         | 10   | _    | 35   | ns   |

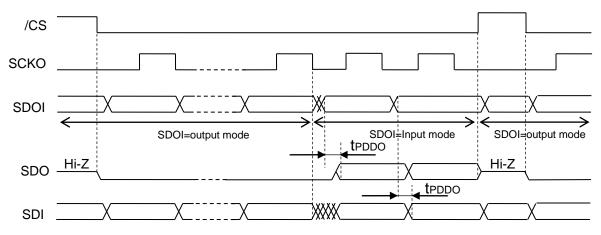

| SDOI-SDO output delay<br>time                                                                           | t <sub>PDDO</sub> |                                                         | _    | _    | 115  | ns   |

Note1: This product is recommended to communicate on the same board for multi-stage series connection. IC-IC transmission delay time is assumed to be less than 10ns.

RSPI=100 $\Omega$  to 330 $\Omega$ , RVREGU=100 $\Omega$  to 330 $\Omega$ , RGNDU=100 $\Omega$  to 330 $\Omega$ , CREGU=10nF to 1.0uF

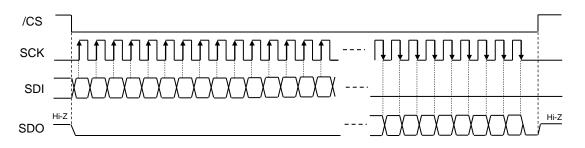

Timing diagram at data write

Timing diagram at multi-stage connection

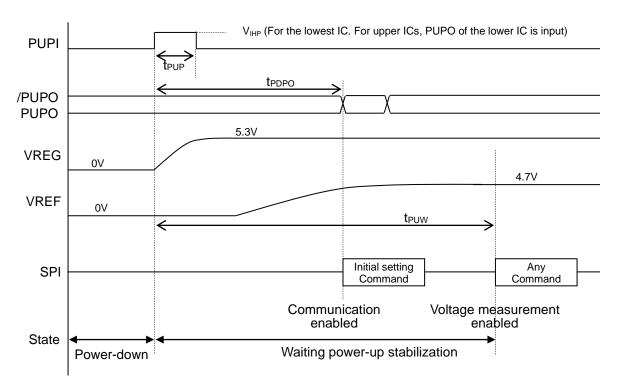

| Item                  | Symbol            | Condition | Min. | Тур. | Max. | Unit       |

|-----------------------|-------------------|-----------|------|------|------|------------|

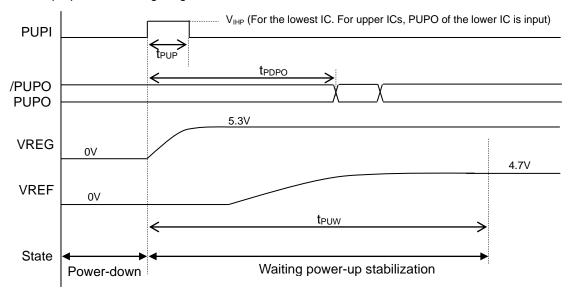

| PUPI "H" pulse width  | <b>t</b> PUP      | —         | 6.0  | —    | —    | μS         |

| PUPI-PUPO             | <b>+</b>          |           |      | F    | 10   | <b>m</b> 0 |

| output delay time     | t <sub>PDPO</sub> | —         | —    | 5    | 10   | ms         |

| Power-up waiting time | <b>t</b> PUW      | —         | 20   | —    | _    | ms         |

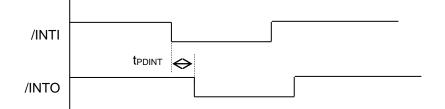

| /INTI- /INTO          | t                 |           |      |      | 1    |            |

| output delay time     | <b>t</b> PDINT    | _         | _    |      | 1    | μS         |

| \/ 40 to 70\        | /. VREGU-GNDU = 5.1 to 5.5V |                  | 40 to 1000 m    |  |

|---------------------|-----------------------------|------------------|-----------------|--|

| $V_{0} = 1010 / 21$ | / VREGU-GNDU = 5 1 10 5 5V  | (abl) = 0V  (a = | -40 10 +85 0 00 |  |

|                     |                             |                  |                 |  |

Power-up operation timing diagram

Interrupt output timing diagram

### Functional Description

#### MCU Interface

The ML5239 is equipped with the SPI interface.

The SPI interface is enabled by setting the /CS pin to the "L" level. It imports the SDI pin data into the LSI in synchronization with the SCK pin clock rise. It outputs the read data to the SDO pin in synchronization with the SCK pin clock fall. The SPI interface is disabled by setting the /CS pin to the "H" level to return to the initial state. Always set the /CS pin to the "H" level every time one data write/read operation completes.

The communication format consists of the control register address, access mode/ID data, write data/read data, and CRC code, all in 8 bits (1 byte) with MSB first.

Data write operation is performed in one byte.

One data read operation can read data from successive addresses.

#### Communication format at data write

| Register | Access | Write data | CRC code |

|----------|--------|------------|----------|

| address  | mode   | (8 bit)    | (8 bit)  |

#### Communication format at data read

| Register<br>address | Access<br>mode | Number of data bytes | Read data 1<br>(8 bit) | Read data 2<br>(8 bit) |  | CRC code<br>(8 bit) |  |

|---------------------|----------------|----------------------|------------------------|------------------------|--|---------------------|--|

|---------------------|----------------|----------------------|------------------------|------------------------|--|---------------------|--|

#### Access mode/ID data

The following table shows the configuration.

|             | 7     | 6      | 5 | 4 | 3   | 2   | 1   | 0   |

|-------------|-------|--------|---|---|-----|-----|-----|-----|

| Bit<br>name | RD/WR | WR_ALL | _ |   | ID3 | ID2 | ID1 | ID0 |

The ID address of an IC in multi-stage connection is specified by ID0 to ID3 bits. Each ID at 16-stages connection is shown in the following table.

| ÷ . |     |     |     |               | 8                               |

|-----|-----|-----|-----|---------------|---------------------------------|

|     | ID3 | ID2 | ID1 | ID0           | Multi-stage<br>connection order |

|     | 0   | 0   | 0   | 0             | Lowest IC                       |

|     | 0   | 0   | 0   | 1             | 2nd lowest IC                   |

|     | 0   | 0   | 1   | 0             | 3rd lowest IC                   |

|     |     | :   | :   |               | :                               |

|     | 1   | 1   | 0   | 1             | 14th lowest IC                  |

|     | 1   | 1   | 1   | 0             | 15th lowest IC                  |

|     | 1   | 1   | 1   | 1 16th lowest |                                 |

A data write operation can be performed for all the ICs in multi-stage connection using WR\_ALL bit. At read operation, the WR\_ALL bit is ignored, and data is read from the specified IC.

| WR_ALL                                   | Accessed IC                       |  |  |  |  |  |  |

|------------------------------------------|-----------------------------------|--|--|--|--|--|--|

| 0 IC specified using the ID0 to ID3 bits |                                   |  |  |  |  |  |  |

| 1                                        | All ICs in multi-stage connection |  |  |  |  |  |  |

The access mode of read/write is selected using the RD/WR bit.

| RD/WR | Access mode |

|-------|-------------|

| 0     | Write       |

| 1     | Read        |

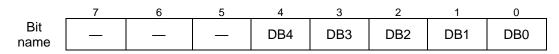

## Number of data bytes

The following table shows the configuration.

The number of bytes of read data is specified using the DB0 to DB4 bits. "Number of read data bytes - 1" should be set. If only one byte is read, "0" should be specified. Up to 32 bytes can be read successively.

### CRC calculation

This IC is equipped with the 8-bit CRC calculation circuit to detect any communication error, and it appends a CRC (Cycle Redundancy Code) generated using a polynomial  $X^{8}+X^{2}+X+1$  to each communication data. It is calculated from all of the address to write/read data, and the result is generated in MSB first. (It includes the empty bits 4 and 5 of the access mode/ID data and 5 to 7 of the number of data bytes.) When the /CS pin is set to "H" level, the CRC calculation is initialized, and the initial value is set to FF [h].

The data write operation is performed on the specified register only when the CRC computation result matches the received CRC code. Otherwise, the data write operation is not performed. When a CRC error is detected, the CRC error flag is set, allowing the interrupt signal to the external MCU to be output to the /INTO pin. For details, refer to the INT\_EN and INT\_REQ registers of the control register.

The CRC computation is also performed for each transmit/receive data during data read operation to output the result at the end of the read data. The external MCU can detect any communication error by comparing the CRC computation result and the received CRC code.

# Control Register

The control register map is shown below. \* Note: The initial value of the INT\_REQ register is value after software reset.

| Address    | Register name | R/W | Initial<br>value | Description                                             |

|------------|---------------|-----|------------------|---------------------------------------------------------|

| 00H        | NOOP          | R/W | 55H              | Register for user                                       |

| 01H        | RSTREQ        | W   | 00H              | Software reset request register                         |

| 02H        | INT EN        | R/W | 80H              | Interrupt enable register                               |

| 03H        | INT_REQ       | R/W | 00H *            | Interrupt request register                              |

| 04H        | PDACP         | W   | 00H              | Power-down code acceptor                                |

| 05H        | POWER         | R/W | 00H              | Power-down control register                             |

|            |               |     |                  | Cell voltage measurement control                        |

| 06H        | MEAS_VCELL    | R/W | 00H              | register                                                |

| 07H        | MEAS_TEMP     | R/W | 00H              | Temperature sensor measurement control register         |

| 08H        | MEAS_VREG     | R/W | 00H              | VREG voltage measurement<br>control register            |

| 09H        | MEAS_VOPSH    | R/W | 00H              | Open/short detection measurement control register       |

| 0AH        | STATUS        | R   | 00H              | Status register                                         |

| 0BH        | STAT_VML      | R   | 00H              | Cell voltage measurement status<br>(lower eight cells)  |

| 0CH        | STAT_VMH      | R   | 00H              | Cell voltage measurement status<br>(higher eight cells) |

| 0DH        | STAT_TM       | R   | 00H              | Temperature sensor measurement<br>status                |

| 0EH        | CBALL         | R/W | 00H              | Cell balancing control register<br>(lower eight cells)  |

| 0FH        | CBALH         | R/W | 00H              | Cell balancing control register<br>(higher eight cells) |

| 10H        | IDSEL         | R   | 00H              | ID storing register                                     |

| 11H        | IDACP         | W   | 00H              | ID automatic setting code acceptor                      |

| 12H        | IDREG         | R/W | 00H              | ID automatic setting register                           |

| 13H        | WDTACP        | W   | 00H              | WDT setting acceptor                                    |

| 14H        | SETWDT        | R/W | 00H              | WDT setting register                                    |

| 15H        | SELOUT        | R/W | 00H              | Pin switch register                                     |

| 16H        | SETOUT        | R/W | 09H              | Pin output setting register                             |

| 17H to 1FH | RSVD          | R   | 00H              | Reserved register                                       |

|            |               |     |                  | Cell 1 measurement result register                      |

| 20H        | VCELL1L       | R   | 00H              | (lower byte)                                            |

| 21H        | VCELL1H       | R   | 00H              | Cell 1 measurement result register<br>(higher byte)     |

| 22H        | VCELL2L       | R   | 00H              | Cell 2 measurement result register<br>(lower byte)      |

| 23H        | VCELL2H       | R   | 00H              | Cell 2 measurement result register<br>(higher byte)     |

| 24H        | VCELL3L       | R   | 00H              | Cell 3 measurement result register<br>(lower byte)      |

| 25H        | VCELL3H       | R   | 00H              | Cell 3 measurement result register<br>(higher byte)     |

| 26H        | VCELL4L       | R   | 00H              | Cell 4 measurement result register<br>(lower byte)      |

| 27H        | VCELL4H       | R   | 00H              | Cell 4 measurement result register<br>(higher byte)     |

| 28H        | VCELL5L       | R   | 00H              | Cell 5 measurement result register<br>(lower byte)      |

| 29H     | VCELL5H       | R   | 00H              | Cell 5 measurement result register<br>(higher byte)  |

|---------|---------------|-----|------------------|------------------------------------------------------|

| Address | Register name | R/W | Initial<br>value | Description                                          |

| 2AH     | VCELL6L       | R   | 00H              | Cell 6 measurement result register<br>(lower byte)   |

| 2BH     | VCELL6H       | R   | 00H              | Cell 6 measurement result register<br>(higher byte)  |

| 2CH     | VCELL7L       | R   | 00H              | Cell 7 measurement result register<br>(lower byte)   |

| 2DH     | VCELL7H       | R   | 00H              | Cell 7 measurement result register<br>(higher byte)  |

| 2EH     | VCELL8L       | R   | 00H              | Cell 8 measurement result register<br>(lower byte)   |

| 2FH     | VCELL8H       | R   | 00H              | Cell 8 measurement result register<br>(higher byte)  |

| 30H     | VCELL9L       | R   | 00H              | Cell 9 measurement result register<br>(lower byte)   |

| 31H     | VCELL9H       | R   | 00H              | Cell 9 measurement result register<br>(higher byte)  |

| 32H     | VCELL10L      | R   | 00H              | Cell 10 measurement result<br>register (lower byte)  |

| 33H     | VCELL10H      | R   | 00H              | Cell 10 measurement result<br>register (higher byte) |

| 34H     | VCELL11L      | R   | 00H              | Cell 11 measurement result<br>register (lower byte)  |

| 35H     | VCELL11H      | R   | 00H              | Cell 11 measurement result<br>register (higher byte) |

| 36H     | VCELL12L      | R   | 00H              | Cell 12 measurement result<br>register (lower byte)  |

| 37H     | VCELL12H      | R   | 00H              | Cell 12 measurement result<br>register (higher byte) |

| 38H     | VCELL13L      | R   | 00H              | Cell 13 measurement result<br>register (lower byte)  |

| 39H     | VCELL13H      | R   | 00H              | Cell 13 measurement result<br>register (higher byte) |

| 3AH     | VCELL14L      | R   | 00H              | Cell 14 measurement result<br>register (lower byte)  |

| 3BH     | VCELL14H      | R   | 00H              | Cell 14 measurement result<br>register (higher byte) |

| 3CH     | VCELL15L      | R   | 00H              | Cell 15 measurement result<br>register (lower byte)  |

| 3DH     | VCELL15H      | R   | 00H              | Cell 15 measurement result<br>register (higher byte) |

| 3EH     | VCELL16L      | R   | 00H              | Cell 16 measurement result<br>register (lower byte)  |

| 3FH     | VCELL16H      | R   | 00H              | Cell 16 measurement result<br>register (higher byte) |

| 40H     | TEMP1L        | R   | 00H              | TEMP1 measurement result<br>register (lower byte)    |

| 41H     | TEMP1H        | R   | 00H              | TEMP1 measurement result<br>register (higher byte)   |

| 42H     | TEMP2L        | R   | 00H              | TEMP2 measurement result<br>register (lower byte)    |

| 43H     | TEMP2H        | R   | 00H              | TEMP2 measurement result<br>register (higher byte)   |

| 44H     | TEMP3L        | R   | 00H              | TEMP3 measurement result<br>register (lower byte)    |

| 45H     | ТЕМРЗН        | R   | 00H              | TEMP3 measurement result<br>register (higher byte)                   |

|---------|---------------|-----|------------------|----------------------------------------------------------------------|

| Address | Register name | R/W | Initial<br>value | Description                                                          |

| 46H     | TEMP4L        | R   | 00H              | TEMP4 measurement result<br>register (lower byte)                    |

| 47H     | TEMP4H        | R   | 00H              | TEMP4 measurement result<br>register (higher byte)                   |

| 48H     | VREGL         | R   | 00H              | VREG voltage measurement result<br>register (lower byte)             |

| 49H     | VREGH         | R   | 00H              | VREG voltage measurement result<br>register (higher byte)            |

| Others  | TEST          | R/W | 00H              | For test (Do not use. Operation is<br>not guaranteed if it is used.) |

# 1. NOOP Register (Adrs = 00H)

|                  | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Bit<br>name      | NO7 | NO6 | NO5 | NO4 | NO3 | NO2 | NO1 | NO0 |

| R/W              | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Initial<br>value | 0   | 1   | 0   | 1   | 0   | 1   | 0   | 1   |

No function is assigned to the NOOP register. Read/write access to this register does not change the LSI state. The written data can be read as it is.

# 2. RSTREQ Register (Adrs = 01H)

|                  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|------------------|---|---|---|---|---|---|---|-----|

| Bit<br>name      | _ |   |   |   |   |   | _ | RST |

| R/W              | R | R | R | R | R | R | R | W   |

| Initial<br>value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

The RSTREQ register requests a software reset.

Setting the RST bit to "1" generates a reset by software request.

All the registers other than IDREG are initialized by the software reset execution.

This is a write-only register. If you read it, 00H is read.

| RST | Software reset                         |

|-----|----------------------------------------|

| 0   | Reset is not performed (initial value) |

| 1   | Reset is performed                     |

3. INT\_EN Register (Adrs = 02H)

|                  | 7     | 6     | 5     | 4    | 3   | 2    | 1   | 0    |

|------------------|-------|-------|-------|------|-----|------|-----|------|

| Bit<br>name      | EWDOV | EVRGR | EVRGD | ECRC | EID | EMVR | EMT | EMVC |

| R/W              | R/W   | R/W   | R/W   | R/W  | R/W | R/W  | R/W | R/W  |

| Initial<br>value | 1     | 0     | 0     | 0    | 0   | 0    | 0   | 0    |

The INT\_EN register sets whether or not to enable the interrupt signal output to the /INTO pin.

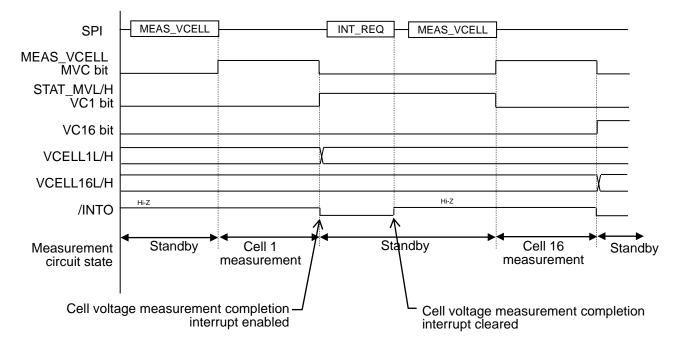

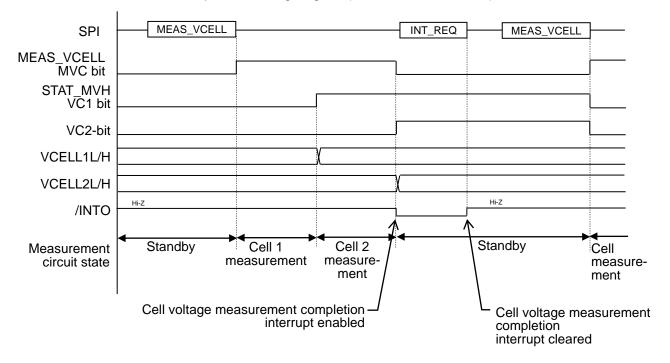

The EMVC bit sets whether or not to enable an interrupt on completion of cell voltage measurement.

| EMVC | Cell voltage measurement<br>completion interrupt |  |  |  |

|------|--------------------------------------------------|--|--|--|

| 0    | 0 Disabled (initial value)                       |  |  |  |

| 1    | Enabled                                          |  |  |  |

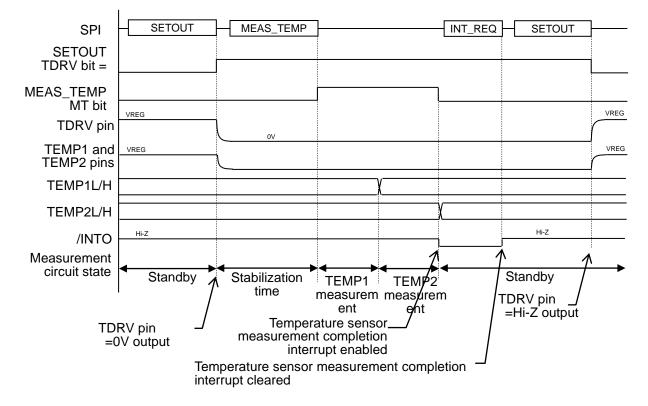

The EMT bit sets whether or not to enable an interrupt on completion of temperature sensor measurement.

| EMT | Temperature sensor<br>measurement completion interrupt |

|-----|--------------------------------------------------------|

| 0   | Disabled (initial value)                               |

| 1   | Enabled                                                |

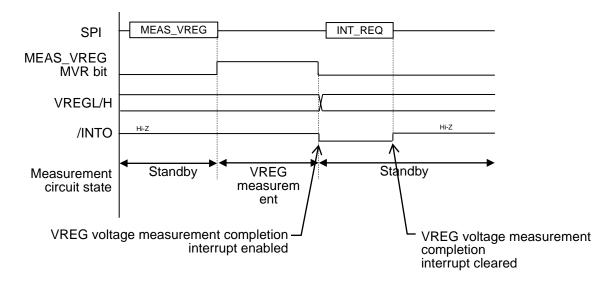

The EMVR bit sets whether or not to enable an interrupt on completion of VREG voltage measurement.

| EMVR                       | VREG voltage measurement<br>completion interrupt |

|----------------------------|--------------------------------------------------|

| 0 Disabled (initial value) |                                                  |

| 1                          | Enabled                                          |

The EID bit sets whether or not to enable an interrupt on completion of ID automatic setting.

| EID | ID automatic setting completion<br>interrupt |

|-----|----------------------------------------------|

| 0   | Disabled (initial value)                     |

| 1   | Enabled                                      |

The ECRC bit sets whether or not to enable an interrupt when a CRC error is detected.

| ECRC | CRC error interrupt      |

|------|--------------------------|

| 0    | Disabled (initial value) |

| 1    | Enabled                  |

The EVRGD bit sets whether or not to enable an interrupt when a VREG output voltage dropping is detected.

| VREG dropping<br>detection interrupt |

|--------------------------------------|

| Disabled (initial value)             |

| Enabled                              |

|                                      |

The EVRGR bit sets whether or not to enable an interrupt when a VREG output voltage return is detected.

| EVRGR | VREG return detection<br>interrupt |  |  |

|-------|------------------------------------|--|--|

| 0     | Disabled (initial value)           |  |  |

| 1     | Enabled                            |  |  |

The EWDOV bit sets whether or not to enable an interrupt when WDT overflows.

| EWDOV | WDT overflow interrupt  |

|-------|-------------------------|

| 0     | Prohibited              |

| 1     | Enabled (initial value) |

### 4. INT\_REQ Register (Adrs = 03H)

|                  | 7     | 6     | 5     | 4    | 3   | 2    | 1   | 0    |

|------------------|-------|-------|-------|------|-----|------|-----|------|

| Bit<br>name      | QWDOV | QVRGR | QVRGD | QCRC | QID | QMVR | QMT | QMVC |

| R/W              | R     | R/W   | R/W   | R/W  | R/W | R/W  | R/W | R/W  |

| Initial<br>value | 0     | 0 *   | 0 *   | 0    | 0   | 0    | 0   | 0    |

The INT\_REQ register contains interrupt request flags. Each request flag is set to "1" when an interrupt is generated, regardless of the setting of INT\_EN register. Only when an interrupt enabled by the INT\_EN register is generated, the "L" level is output to the /INTO pin.

An interrupt can be cleared by writing data "0". Writing data "1" is ignored. If you want to clear only one interrupt, write "1" to the other bits. When all enabled interrupt request flags are cleared to "0", the output to /INTO pin is set to the "Hi-Z" level.

\* Note: The initial values of the QVRGR bit and the QVRGD bit are values after software reset. Please initialize before use.

The QMVC bit indicates whether a cell voltage measurement completion interrupt has been generated.

| QMVC | Cell voltage measurement<br>completion interrupt |

|------|--------------------------------------------------|

| 0    | Without interrupt (initial value)                |

| 1    | An interrupt is generated                        |

The QMT bit indicates whether a temperature sensor measurement completion interrupt has been generated.

| OMT   | Temperature sensor                |

|-------|-----------------------------------|

| QIVIT | measurement completion interrupt  |

| 0     | Without interrupt (initial value) |

| 1     | An interrupt is generated         |

The QMVR bit indicates whether a VREG voltage measurement completion interrupt has been generated.

| QMVR | VREG voltage measurement<br>completion interrupt |

|------|--------------------------------------------------|

| 0    | Without interrupt (initial value)                |

| 1    | An interrupt is generated                        |

The QID bit indicates whether an ID automatic setting completion interrupt has been generated.

| QID | ID automatic setting completion<br>interrupt |  |  |

|-----|----------------------------------------------|--|--|

| 0   | Without interrupt (initial value)            |  |  |

| 1   | An interrupt is generated                    |  |  |

The QCRC bit indicates whether an interrupt has been generated when a CRC error is detected.

| QCRC | CRC error interrupt               |

|------|-----------------------------------|

| 0    | Without interrupt (initial value) |

| 1    | An interrupt is generated         |

The QVRGD bit indicates whether an interrupt has been generated when a VREG output voltage dropping is detected.

If a dropping is detected during the VREG output voltage return state, an interrupt occurs, and it is cleared during the VREG output voltage dropping detection state, then an interrupt does not occur even in the dropping detection state.

| QVRGD | VREG dropping detection<br>interrupt |  |  |  |

|-------|--------------------------------------|--|--|--|

| 0     | Without interrupt (initial value *)  |  |  |  |

| 1     | An interrupt is generated            |  |  |  |

The QVRGR bit indicates whether an interrupt has been generated when a VREG output voltage return is detected.

If a return from VREG output voltage dropping detection state is detected, an interrupt occurs.

| QVRGR | VREG return detection interrupt     |

|-------|-------------------------------------|

| 0     | Without interrupt (initial value *) |

| 1     | An interrupt is generated           |

The QWDOV bit indicates whether an interrupt occurs when WDT overflows.

| QWDOV | WDT overflow interrupt            | 1 |

|-------|-----------------------------------|---|

| 0     | Without interrupt (initial value) | 1 |

| 1     | An interrupt is generated         | 1 |

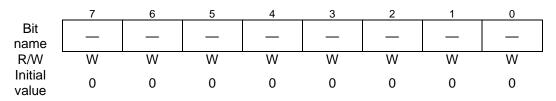

#### 5. PDACP Register (Adrs = 04H)

|                  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------|---|---|---|---|---|---|---|---|

| Bit<br>name      |   | _ | _ | _ | _ | _ | _ | _ |

| R/W              | W | W | W | W | W | W | W | W |

| Initial<br>value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

The PDACP register enables writing to PDWN of the POWER register to avoid entering the power-down mode accidentally. Writing 0x55 and 0xAA successively to this register enables setting PDWN of POWER register to "1".

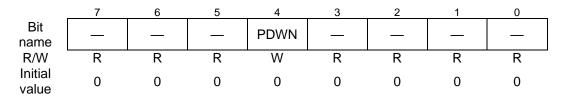

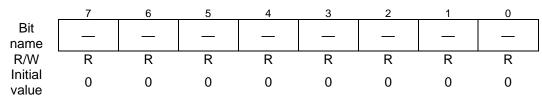

# 6. POWER Register (Adrs = 05H)

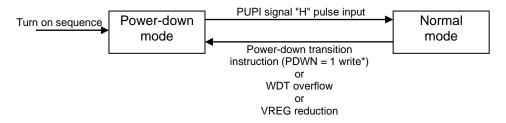

The POWER register controls the power-down.

The PDWN bit is used to enable the power-down state.

| PDWN | Power-down            |

|------|-----------------------|

| 0    | Normal state (initial |

| 0    | value)                |

| 1    | Power-down            |

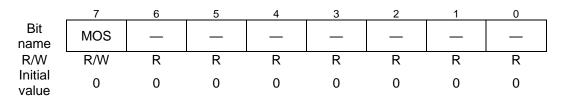

# 7. MEAS\_VCELL Register (Adrs = 06H)

|                  | 7   | 6 | 5 | 4   | 3   | 2   | 1   | 0   |

|------------------|-----|---|---|-----|-----|-----|-----|-----|

| Bit<br>name      | MVC | _ | — | SCV | C3  | C2  | C1  | C0  |

| R/W              | R/W | R | R | R/W | R/W | R/W | R/W | R/W |

| Initial<br>value | 0   | 0 | 0 | 0   | 0   | 0   | 0   | 0   |

The MEAS\_VCELL register controls the cell voltage measurement.

Use the SCV bit and the C0 to C3 bits to select the measurement mode and the battery cell(s) to be measured.

| eu. |     |    |    |    |    |                                                 |  |  |  |  |

|-----|-----|----|----|----|----|-------------------------------------------------|--|--|--|--|

|     | SCV | C3 | C2 | C1 | C0 | Cell voltage measurement                        |  |  |  |  |

|     | 0   | 0  | 0  | 0  | 0  | Only cell 1 is measured                         |  |  |  |  |

|     | 0   | 0  | 0  | 0  | 1  | Only cell 2 is measured                         |  |  |  |  |

|     | 0   | 0  | 0  | 1  | 0  | Only cell 3 is measured                         |  |  |  |  |

|     | 0   | 0  | 0  | 1  | 1  | Only cell 4 is measured                         |  |  |  |  |

|     | 0   | 0  | 1  | 0  | 0  | Only cell 5 is measured                         |  |  |  |  |

|     | 0   | 0  | 1  | 0  | 1  | Only cell 6 is measured                         |  |  |  |  |

|     | 0   | 0  | 1  | 1  | 0  | Only cell 7 is measured                         |  |  |  |  |

|     | 0   | 0  | 1  | 1  | 1  | Only cell 8 is measured                         |  |  |  |  |

|     | 0   | 1  | 0  | 0  | 0  | Only cell 9 is measured                         |  |  |  |  |

|     | 0   | 1  | 0  | 0  | 1  | Only cell 10 is measured                        |  |  |  |  |

|     | 0   | 1  | 0  | 1  | 0  | Only cell 11 is measured                        |  |  |  |  |

|     | 0   | 1  | 0  | 1  | 1  | Only cell 12 is measured                        |  |  |  |  |

|     | 0   | 1  | 1  | 0  | 0  | Only cell 13 is measured                        |  |  |  |  |

|     | 0   | 1  | 1  | 0  | 1  | Only cell 14 is measured                        |  |  |  |  |

|     | 0   | 1  | 1  | 1  | 0  | Only cell 15 is measured                        |  |  |  |  |

|     | 0   | 1  | 1  | 1  | 1  | Only cell 16 is measured                        |  |  |  |  |

|     | 1   | 0  | 0  | 0  | 0  | Only cell 1 is measured                         |  |  |  |  |

|     | 1   | 0  | 0  | 0  | 1  | Cell 1 to cell 2 are measured in the scan mode  |  |  |  |  |

|     | 1   | 0  | 0  | 1  | 0  | Cell 1 to cell 3 are measured in the scan mode  |  |  |  |  |

|     | 1   | 0  | 0  | 1  | 1  | Cell 1 to cell 4 are measured in the scan mode  |  |  |  |  |

|     | 1   | 0  | 1  | 0  | 0  | Cell 1 to cell 5 are measured in the scan mode  |  |  |  |  |

|     | 1   | 0  | 1  | 0  | 1  | Cell 1 to cell 6 are measured in the scan mode  |  |  |  |  |

|     | 1   | 0  | 1  | 1  | 0  | Cell 1 to cell 7 are measured in the scan mode  |  |  |  |  |

|     | 1   | 0  | 1  | 1  | 1  | Cell 1 to cell 8 are measured in the scan mode  |  |  |  |  |

|     | 1   | 1  | 0  | 0  | 0  | Cell 1 to cell 9 are measured in the scan mode  |  |  |  |  |

|     | 1   | 1  | 0  | 0  | 1  | Cell 1 to cell 10 are measured in the scan mode |  |  |  |  |

|     | 1   | 1  | 0  | 1  | 0  | Cell 1 to cell 11 are measured in the scan mode |  |  |  |  |

|     | 1   | 1  | 0  | 1  | 1  | Cell 1 to cell 12 are measured in the scan mode |  |  |  |  |

|     | 1   | 1  | 1  | 0  | 0  | Cell 1 to cell 13 are measured in the scan mode |  |  |  |  |

|     | 1   | 1  | 1  | 0  | 1  | Cell 1 to cell 14 are measured in the scan mode |  |  |  |  |

|     | 1   | 1  | 1  | 1  | 0  | Cell 1 to cell 15 are measured in the scan mode |  |  |  |  |

|     | 1   | 1  | 1  | 1  | 1  | Cell 1 to cell 16 are measured in the scan mode |  |  |  |  |

|     |     |    |    |    |    |                                                 |  |  |  |  |

The MVC bit is used to control the start/stop of cell voltage measurement and to verify the cell voltage measurement completion status. The cell voltage measurement results are stored in the VCELLnL and VCELLnH registers (20H to 3FH).

|     | Write                | Read |                   |  |

|-----|----------------------|------|-------------------|--|

| MVC | Cell voltage         | MVC  | Cell voltage      |  |

|     | measurement          | NIVC | measurement       |  |

| 0   | Stop (initial value) | 0    | Completed/stopped |  |

| 0   | Stop (Initial value) | 0    | (initial value)   |  |

| 1   | Start                | 1    | Measuring         |  |

It is possible to stop the cell voltage measurement by writing "0" to the MVC bit while measuring the cell voltage. In that case, the measurement stops after the cell voltage measurement in progress is completed. The read value of MVC bit remains "1" until the measurement stops, and it is reset to "0" after the measurement stops.

Any change in the settings of the SCV bit and C3 to C0 bits is ignored during the measurement (while the read value of MVC bit is "1").

Also, setting the MVC bit to "1" is ignored while measuring temperature sensor, VREG voltage, and open/short detection.

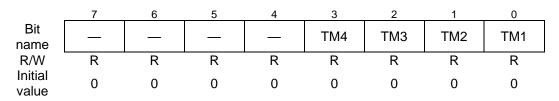

### 8. MEAS\_TEMP Register (Adrs = 07H)

|                    | 7   | 6 | 5 | 4   | 3 | 2 | 1   | 0   |

|--------------------|-----|---|---|-----|---|---|-----|-----|

| Bit<br>name<br>R/W | MT  | — | — | SCT | — | — | T1  | Т0  |

|                    | R/W | R | R | R/W | R | R | R/W | R/W |

| Initial<br>value   | 0   | 0 | 0 | 0   | 0 | 0 | 0   | 0   |

The MEAS\_TEMP register controls the measurement of the temperature sensors (TEMP1 to TEMP4 pins input voltage).

| SCT | T1  | Т0 | Temperature sensor measurement mode                         |  |  |

|-----|-----|----|-------------------------------------------------------------|--|--|

| 0   | 0   | 0  | TEMP1 pin input voltage measurement only<br>(initial value) |  |  |

| 0   | 0   | 1  | TEMP2 pin input voltage measurement only                    |  |  |

| 0   | 1   | 0  | TEMP3 pin input voltage measurement only                    |  |  |

| 0   | 1   | 1  | TEMP4 pin input voltage measurement only                    |  |  |

| 1   | 0   | 0  | TEMP1 pin input voltage measurement only                    |  |  |

| 1   | 0   | 1  | TEMP1 to TEMP2 pins input voltage scan                      |  |  |

|     | · · |    | measurement                                                 |  |  |

| 1   | 1   | 0  | TEMP1 to TEMP3 pins input voltage scan                      |  |  |

| 1   | 1   | 0  | measurement                                                 |  |  |

| 1   | 1   | 1  | TEMP1 to TEMP4 pins input voltage scan                      |  |  |

| 1   | 1   | I  | measurement                                                 |  |  |

The SCT, <u>T0</u>, and T1 bits select the temperature sensor measurement mode.

The MT bit is used to control the start/stop of temperature sensor measurement and to verify the temperature sensor measurement completion status. The temperature sensor measurement results are stored in the TEMPnL and TEMPnH registers (40H to 47H).

|    | Write                | Read |                   |  |

|----|----------------------|------|-------------------|--|

| МТ | TEMP pin voltage     | МТ   | TEMP pin voltage  |  |

|    | measurement          |      | measurement       |  |

| 0  | Stop (initial value) | 0    | Completed/stopped |  |

| 0  | Stop (Initial value) |      | (initial value)   |  |

| 1  | Start                | 1    | Measuring         |  |

It is possible to stop the temperature sensor measurement by writing "0" to the MT bit while measuring the temperature sensor. In that case, the measurement stops after the temperature sensor measurement in progress is completed. The read value of MT bit remains "1" until the measurement stops, and it is reset to "0" after the measurement stops.

Any change in the settings of the SCT, T0, T1 bits is ignored during the measurement (while the read value of the MT bit is "1").

Also, setting the MT bit to "1" is ignored while measuring cell voltage, VREG voltage, and open/short detection.

#### 9. MEAS\_VREG Register (Adrs = 08H)

|                  | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------|-----|---|---|---|---|---|---|---|

| Bit<br>name      | MVR |   | — | — | _ |   |   | — |

| R/W              | R/W | R | R | R | R | R | R | R |

| Initial<br>value | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

The MEAS\_VREG register controls the VREG voltage measurement. The voltage actually measured by this register is VREG $\times 1/2$  instead of VREG itself.