#### FEDL5810A-05

30, Oct. 2020

# **ML5810A**

High-Side Switch Driver IC for Battery Pack

#### ■General Description

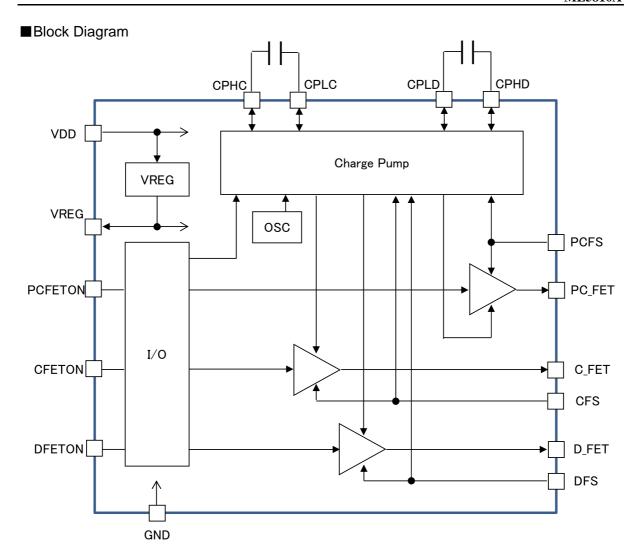

ML5810A is charge/discharge high-side switch Nch power MOSFET gate driver for battery pack. ML5810A assert external input reference voltage(CFS, DFS)+12V(typ) as the voltage for drive by charge pump. And also, built-in PchMOSFET gate driver for low current precharge in battery over-discharge state.

#### ■ Features

•High-side switch Nch power MOSFET gate driver for battery pack protection

•Built-in Pch MOSFET gate driver for low current precharge/predischarge

•80V breakdown voltage applicable to 48V battery system

•Built-in charge pump

•Gate driver for charge/discharge "H" output voltage : Reference voltage(CFS, DFS)+10V (min) •Gate driver for precharge/predischarge "L" output voltage : Reference voltage (PCFS)-9V (min)

• Current consumption : 210uA(typ), 480uA(max)

• Power supply voltage range : +6.5V to +64V

(Absolute Maximum Rating: 80V)

Operating temperature range : -40°C to +105°C

Package : 20pin TSSOP

• Application : 12V to 48V Battery pack for industrial

eBikes, Energy Storage Systems (ESS) and Uninterruptible Power Supplies (UPS)

Note) This product is not intended for automotive use and for any equipment, device, or system that requires a specific quality or high level of reliability (e.g., medical equipment, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller, various safety devices). If you are not sure whether your application corresponds to such special purposes, please contact your local ROHM sales representative in advance.

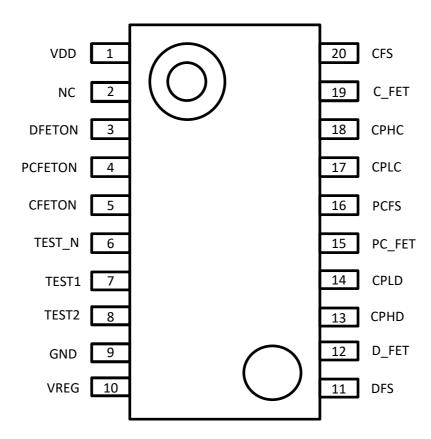

## ■Pin Configuration(Top View)

■Pin Description

| Pin No. | Pin     | I/O | Description                                                                                                                                                                                              |

|---------|---------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VDD     | _   | Power supply.  Connect an external CR filter for noise rejection.                                                                                                                                        |

| 2       | NC      | _   |                                                                                                                                                                                                          |

| 3       | DFETON  | I   | D_FET enable input.(pulldown resistance:1M $\Omega$ )                                                                                                                                                    |

| 4       | PCFETON | ı   | PC_FET enable input.(pulldown resistance:1MΩ)                                                                                                                                                            |

| 5       | CFETON  | I   | C_FET enable input.(pulldown resistance:1MΩ)                                                                                                                                                             |

| 6       | TEST_N  | 1   | TEST_N input. Should be fixed to VDD.                                                                                                                                                                    |

| 7       | TEST1   | 1   | TEST1 input.(pulldown resistance:1M $\Omega$ )<br>Should be fixed to GND.                                                                                                                                |

| 8       | TEST2   | ı   | TEST2 input.(pulldown resistance:1M $\Omega$ )<br>Should be fixed to GND.                                                                                                                                |

| 9       | GND     |     | Ground.                                                                                                                                                                                                  |

| 10      | VREG    | 0   | Built-in 3.3V regurator output. Connect a 4.7μF capacitor between this pin and GND.                                                                                                                      |

| 11      | DFS     | 1   | Reference voltage input for the D_FET drive charge pump. Connect to the source pin of the discharge FET.                                                                                                 |

| 12      | D_FET   | 0   | Discharge Nch-FET gate drive. Connect to the gate pin of the external Nch-FET. In the ON state, the DFS level +12V (typ) is asserted. In the OFF state DFS level is asserted.                            |

| 13      | CPHD    | 0   | Charge pump capacitor input for D_FET drive. Connect a capacitor which                                                                                                                                   |

| 14      | CPLD    | 0   | approximately 8-times of the discharge FET gate capacitance, between the CPHD and CPLD pins.                                                                                                             |

| 15      | PC_FET  | 0   | Precharge/predischarge Pch-FET gate drive. Connected to the gate pin of the external Pch-FET. In the ON state, the PCFS level -12V (typ) is asserted, while the PCFS level is asserted in the OFF state. |

| 16      | PCFS    | I   | Reference voltage input for the PC_FET drive charge pump. Connected to the source pin of the precharge/predischarge FET.                                                                                 |

| 17      | CPLC    | 0   | Charge pump capacitor input for C_FET drive. Connect a capacitor with                                                                                                                                    |

| 18      | СРНС    | 0   | approximately twice the gate capacitance of the charge FET between the CPHC and CPLC pins.                                                                                                               |

| 19      | C_FET   | 0   | Charge Nch-FET gate drive. Connected to the gate pin of the external Nch-FET. In the ON state, the CFS level +12V (typ) is asserted, while the CFS level is asserted in the OFF state.                   |

| 20      | CFS     | 1   | Reference voltage input for the C_FET drive charge pump. Connected to the source pin of the charge FET.                                                                                                  |

# ■ Absolute Maximum Ratings

|                              |                                    |                                                                                         | G                              | SND=0V, Ta=25°C |

|------------------------------|------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------|-----------------|

| Parameter                    | Symbol                             | Condition                                                                               | Rating                         | Unit            |

| Supply voltage               | $V_{DD}$                           | Applied to VDD pin                                                                      | -0.3 to +86.5                  | V               |

|                              | V <sub>IN1</sub>                   | Applied to CFS,DFS, and PCFS pins                                                       | -0.3 to +86.5                  | V               |

| Input voltage                | V <sub>IN2</sub>                   | Applied to CFETON, DFETON,PCFETON,TEST1, and TEST2,TEST_N pins                          | -0.3 to VDD+0.3                | V               |

|                              | V <sub>OUT1</sub>                  | Applied to D_FET pin V <sub>DFS</sub> =DFS pin voltage                                  | V <sub>DFS</sub> -0.5 to +86.5 | V               |

| Output voltage               | V <sub>OUT2</sub>                  | Applied to C_FET pin  V <sub>CFS</sub> =CFS pin voltage  V <sub>CFS</sub> -0.5 to +86.5 |                                | V               |

|                              | V <sub>ОUТ3</sub>                  | Applied to PC_FET pin                                                                   | -0.5 to +71.5                  | V               |

|                              | l <sub>OS1</sub>                   | VDD=50V<br>Applied to VREG pin                                                          | 5                              | mA              |

| Short circuit output current | I <sub>OS2</sub>                   | VDD=50V Applied to C_FET and D_FET pins                                                 | 20                             | mA              |

|                              | los3                               | VDD=50V<br>Applied to PC_FET pin                                                        | 2                              | mA              |

| Power dissipation            | dissipation P <sub>D</sub> Ta=25°C |                                                                                         | 2.3                            | W               |

| Package thermal resistance   | θ ja                               | JEDEC double-side board mounted                                                         | 33.7                           | °C/W            |

| Storage temperature          | T <sub>STG</sub>                   | _                                                                                       | -55 to +150                    | °C              |

## ■ Recommended Operating Conditions

(GND= 0 V)

| Parameter             | Symbol Condition |                     | Range             | Unit |

|-----------------------|------------------|---------------------|-------------------|------|

| Power supply voltage  | $V_{DD}$         | Applied to VDD pin  | 6.5~64            | V    |

| Operating temperature | Та               | No VREG output load | -40 <b>~</b> +105 | °C   |

### ■ Electrical Characteristics

$V_{DD}$ =6.5 $\sim$ 64V,GND=0V,Ta=-40 to +105°C, no VREG output load

| V <sub>DD</sub> =6.5~64V,GND=0V,Ta=-40 to +105°C, no VREG output load |                                                                           |                                                                                                                                                          |                       |      |          |      |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|----------|------|

| Parameter                                                             | Symbol                                                                    | Condition                                                                                                                                                | Min.                  | Тур. | Max.     | Unit |

| Digital "H" input<br>voltage(*1)                                      | ViH                                                                       | _                                                                                                                                                        | 2.15                  | _    | VDD+0.3  | V    |

| Digital "L" input<br>voltage(*1)                                      | VIL                                                                       | _                                                                                                                                                        | 0                     | _    | 0.35     | V    |

| Digital "H" input<br>current(*1)                                      | Іін                                                                       | V <sub>IH</sub> = VDD                                                                                                                                    | _                     | _    | 130      | μΑ   |

| Digital "L" input<br>current(*1)                                      | lı∟                                                                       | V <sub>IL</sub> = GND                                                                                                                                    | -2                    | _    | _        | μΑ   |

| C_FET / D_FET output voltage( C_FET-CFS,                              | V <sub>OH11</sub>                                                         | I <sub>OH</sub> =-1.5µА<br>(V <sub>DD</sub> *0.95)≧10V                                                                                                   | 10                    | 12   | 15       | V    |

| D_FET-DFS)                                                            | V <sub>OH12</sub>                                                         | I <sub>OH</sub> =-1.5µА<br>(V <sub>DD</sub> *0.93)<10V                                                                                                   | V <sub>DD</sub> *0.93 | _    | $V_{DD}$ | V    |

| PC_FET output voltage                                                 | V <sub>OL21</sub>                                                         | l <sub>OL=+</sub> 1.5μΑ<br>(V <sub>DD</sub> *0.8)≧9V                                                                                                     | 9                     | 12   | 15       | V    |

| (PCFS-PC_FET)                                                         | V <sub>OL22</sub>                                                         | I <sub>OL</sub> =+1.5μΑ<br>(V <sub>DD</sub> *0.8)<9V                                                                                                     | V <sub>DD</sub> *0.8  | _    | $V_{DD}$ | V    |

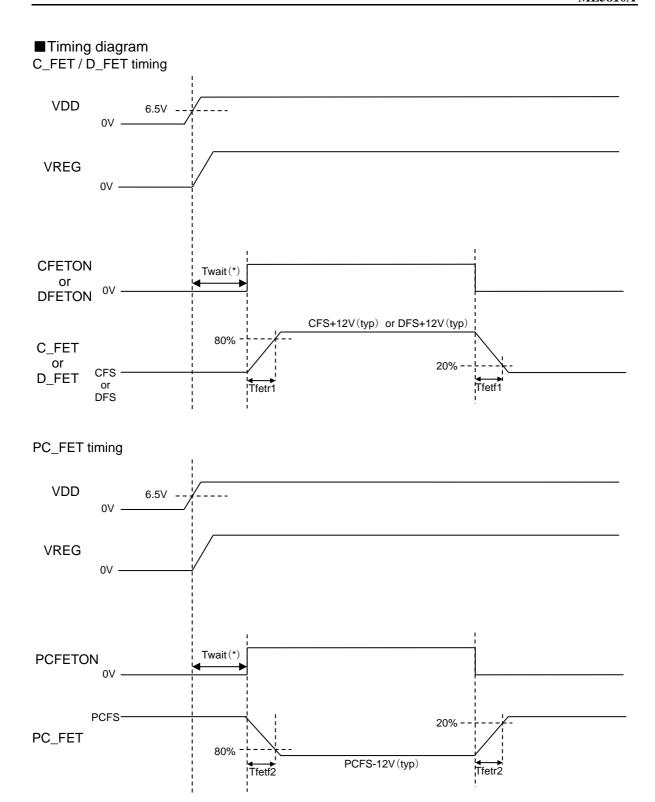

| C_FET / D_FET rise time                                               | Tfetr1                                                                    | Ccp=80nF, Rg=1kΩ, Rfs=100Ω, FET gate capacitance=10nF From FET-on to 80% of output voltage Voh11, Voh12                                                  | _                     | 150  | 350      | us   |

| C_FET / D_FET fall time                                               | Tfetf1                                                                    | Ccp=80nF, Rg=1kΩ, Rfs=100Ω, FET gate capacitance=10nF From FET-off to 20% of output voltage VoH11, VoH12                                                 | _                     | 40   | 70       | us   |

| PC_FET fall time                                                      | Tfetf2                                                                    | $\label{eq:ccp=80nF} Ccp=80nF, \\ Rg=1k\Omega, Rfs=1k\Omega, \\ FET gate capacitance=1nF \\ From FET-on to 80\% of \\ output voltage V_{OL21}, V_{OL22}$ | _                     | 110  | 400      | us   |

| PC_FET Rg= rise time Tfetr2 FET gar From                              |                                                                           | Ccp=80nF,<br>Rg=1k $\Omega$ , Rfs=1k $\Omega$ ,<br>FET gate capacitance=1nF<br>From FET-off to 20% of<br>output voltage Vol21, Vol22                     | _                     | 20   | 70       | us   |

| Current consumption in operation ( charge and discharge ) (*2)        | ration ration   IDD1   CFETON=1 & DFETON=1 & PCFETON=0   VDD-CFS-DFS-PCFS |                                                                                                                                                          | _                     | 210  | 480      | uA   |

| Current consumption in operation ( precharge or predischarge )(*2)    | IDD2                                                                      | CFETON=0 & DFETON=0 & PCFETON=1 VDD=CFS=DFS=PCFS                                                                                                         | _                     | 135  | 380      | uA   |

| VREG output voltage V <sub>REG1</sub> |                   | V <sub>DD</sub> =6.5V∼64V Output load current<1mA | 3.0  | 3.3    | 3.6 | V   |

|---------------------------------------|-------------------|---------------------------------------------------|------|--------|-----|-----|

| C_FET / D_FET charge pump frequency   | F <sub>CPCD</sub> | _                                                 | 6.25 | 7.8125 | 9.4 | kHz |

| PC_FET charge pump frequency          | FCPPC             | _                                                 | 0.78 | 0.9766 | 1.2 | kHz |

<sup>\*1:</sup> Applied to CFETON, DFETON, PCFETON, TEST1, TEST2 and TEST\_N pins

<sup>\*2:</sup> Current consumption are sum of VDD,CFS,DFS, and PCFS currents

### ■Functional Description

Operating state of ML5810A in each input status of 3 control input(PCFETON, DFETON, CFETON) is indicated in the following table.

"Charge pump ON, FET stand-by" is in which a charge pump powers up and each FET gate voltage output enable. The wait time is required at transition from power-up, and please refer to the "Timing diagram" mentioned later for details.

"FET ON state" is the state in which each FET gate voltage is asserted by a relevant pin actually. Please refer to "

electrical characteristic" about rise and fall time of gate voltage.

|         | Input          |        | ML5810A                      |

|---------|----------------|--------|------------------------------|

| PCFETON | DFETON         | CFETON | Operating status             |

| 0       | 0              | 0      | Charge pump ON, FET stand-by |

| Mo      | re than one is | "1"    | FET ON                       |

C\_FET and D\_FET can be turn on at the same time, but PC\_FET is exclusively other FETs and can't be turn on at the same time. A truth table of FET ON/OFF is following. As it's shown on the table, CFETON, DFETON is priority more than PCFETON .

|         | Input  |        | Output |       |       |

|---------|--------|--------|--------|-------|-------|

| PCFETON | DFETON | CFETON | PC_FET | D_FET | C_FET |

| 0       | 0      | 0      | OFF    | OFF   | OFF   |

| 0 or 1  | 0      | 1      | OFF    | OFF   | ON    |

| 0 or 1  | 1      | 0      | OFF    | ON    | OFF   |

| 0 or 1  | 1      | 1      | OFF    | ON    | ON    |

| 1       | 0      | 0      | ON     | OFF   | OFF   |

(\*) Twait must be more than 50ms, when CFETON, DFETON, and PCFETON are set to H from L (0v).

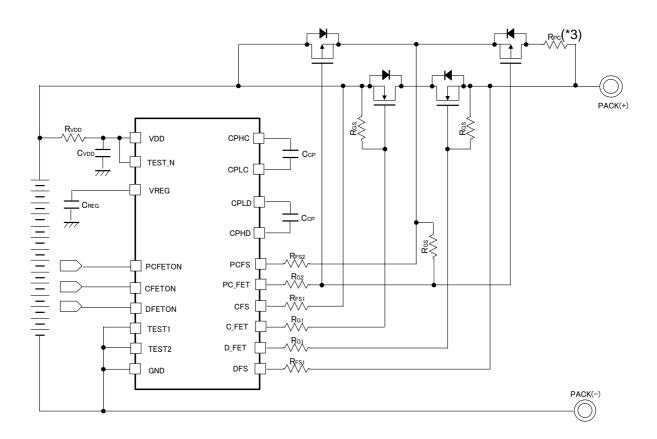

### ■Application Circuit Example

### Recommended Values for External Components

| Component             | Recommended value       |

|-----------------------|-------------------------|

| R <sub>VDD</sub> (*1) | $510\Omega$ to $1.5$ kΩ |

| $C_{VDD}$             | 2.2μF to 10μF           |

| C <sub>REG</sub>      | 4.7μF                   |

| R <sub>G1</sub>       | 1kΩ                     |

| R <sub>FS1</sub>      | 100Ω                    |

| R <sub>G2</sub>       | 1kΩ                     |

| R <sub>FS2</sub>      | 1kΩ                     |

| R <sub>GS</sub>       | 10ΜΩ                    |

| C <sub>CP</sub>       | 82nF (*2)               |

- (\*1) Recommended  $R_{VDD}{=}1.5k\Omega$  for  $C_{VDD}{=}2.2\mu F.$

- (\*2) Set 80nF to 100nF, when gate capacitance of external Nch-FET is 10nF. Set about 8-times of gate capacitance of external Nch-FET to C<sub>CP</sub>.

- (\*3) Set R<sub>PC</sub> according to current of Pch-FET.

Notice: Example of application circuit and the recommended values to parts list shall not guarantee performance under all conditions. Full and detailed tests are suggested on your actual application.

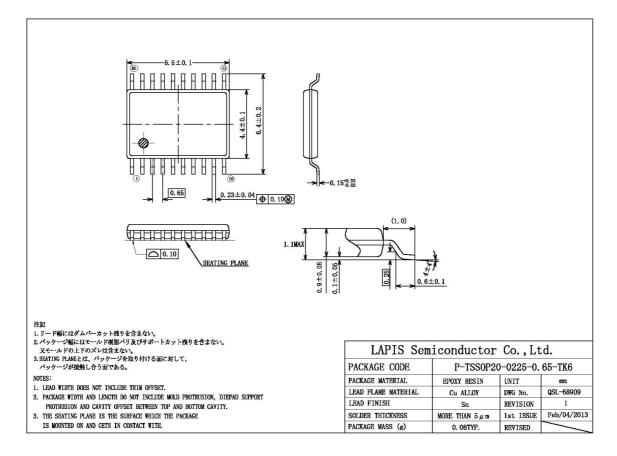

#### ■ Package Dimensions

Causion regarding surface mount type packages

Surface mount type packages are susceptible to applied heat in solder reflow or moisture absorption during storage. Please contact your local ROHM sales representative for the recommended mounting conditions (reflow sequence, temperature and cycles) and storage environment.

## ■ Revision History

| Document No. | Issue date | Page     |      | Descriptions                                                 |  |

|--------------|------------|----------|------|--------------------------------------------------------------|--|

| Document No. | issue date | Previous | New  | Descriptions                                                 |  |

| Version-02   | 2019.07.18 | _        |      | English version first edition issued                         |  |

| Version-03   | 2019.07.19 | 3        | 3    | Error in writing corrected                                   |  |

| Version-03   | 2019.07.25 | 5,10     | 5,10 | Error in writing corrected                                   |  |

| Version-04   | 2020.06.05 | 3        | 3    | Error in Pin Configuration corrected (pin 2,8,15,16)         |  |

| Version-04   | 2020.06.05 | 10       | 10   | ■Application Circuit Example Added TEST1, TEST2, TEST_N pin. |  |

| Version-05   | 2020.10.30 | _        |      | Changed Company name and "notes" page.                       |  |

#### Notes

- 1) The information contained herein is subject to change without notice.

- 2) When using LAPIS Technology Products, refer to the latest product information (data sheets, user's manuals, application notes, etc.), and ensure that usage conditions (absolute maximum ratings, recommended operating conditions, etc.) are within the ranges specified. LAPIS Technology disclaims any and all liability for any malfunctions, failure or accident arising out of or in connection with the use of LAPIS Technology Products outside of such usage conditions specified ranges, or without observing precautions. Even if it is used within such usage conditions specified ranges, semiconductors can break down and malfunction due to various factors. Therefore, in order to prevent personal injury, fire or the other damage from break down or malfunction of LAPIS Technology Products, please take safety at your own risk measures such as complying with the derating characteristics, implementing redundant and fire prevention designs, and utilizing backups and fail-safe procedures. You are responsible for evaluating the safety of the final products or systems manufactured by you.

- 3) Descriptions of circuits, software and other related information in this document are provided only to illustrate the standard operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. And the peripheral conditions must be taken into account when designing circuits for mass production. LAPIS Technology disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, and other related information.

- 4) No license, expressly or implied, is granted hereby under any intellectual property rights or other rights of LAPIS Technology or any third party with respect to LAPIS Technology Products or the information contained in this document (including but not limited to, the Product data, drawings, charts, programs, algorithms, and application examples, etc.). Therefore LAPIS Technology shall have no responsibility whatsoever for any dispute, concerning such rights owned by third parties, arising out of the use of such technical information.

- 5) The Products are intended for use in general electronic equipment (AV/OA devices, communication, consumer systems, gaming/entertainment sets, etc.) as well as the applications indicated in this document. For use of our Products in applications requiring a high degree of reliability (as exemplified below), please contact and consult with a LAPIS Technology representative: transportation equipment (cars, ships, trains, etc.), primary communication equipment, traffic lights, fire/crime prevention, safety equipment, medical systems, servers, solar cells, and power transmission systems, etc. LAPIS Technology disclaims any and all liability for any losses and damages incurred by you or third parties arising by using the Product for purposes not intended by us. Do not use our Products in applications requiring extremely high reliability, such as aerospace equipment, nuclear power control systems, and submarine repeaters, etc.

- 6) The Products specified in this document are not designed to be radiation tolerant.

- 7) LAPIS Technology has used reasonable care to ensure the accuracy of the information contained in this document. However, LAPIS Technology does not warrant that such information is error-free and LAPIS Technology shall have no responsibility for any damages arising from any inaccuracy or misprint of such information.

- 8) Please use the Products in accordance with any applicable environmental laws and regulations, such as the RoHS Directive. LAPIS Technology shall have no responsibility for any damages or losses resulting non-compliance with any applicable laws or regulations.

- 9) When providing our Products and technologies contained in this document to other countries, you must abide by the procedures and provisions stipulated in all applicable export laws and regulations, including without limitation the US Export Administration Regulations and the Foreign Exchange and Foreign Trade Act..

- 10) Please contact a ROHM sales office if you have any questions regarding the information contained in this document or LAPIS Technology's Products.

- 11) This document, in part or in whole, may not be reprinted or reproduced without prior consent of LAPIS Technology.

(Note) "LAPIS Technology" as used in this document means LAPIS Technology r Co., Ltd.

Copyright 2020 LAPIS Technology Co., Ltd.

# LAPIS Technology Co., Ltd.

2-4-8 Shinyokohama, Kouhoku-ku, Yokohama 222-8575, Japan http://www.lapis-tech.com