# ML62Q2033/2035/2043/2045

16-bit micro controller

### **GENERAL DESCRIPTION**

ML62Q2033/2035/2043/2045 are high performance CMOS 16-bit microcontrollers equipped with an 16-bit CPU nX-U16/100 and integrated with program memory (Flash memory), data memory (RAM), data Flash (Erase unit:128byte, Write unit:1byte) and rich peripheral functions such as the multiplier/divider, Clock generator, PWM generator, Timer, General Purpose Ports, UART, I2C bus interface unit(Master, Slave ), Successive approximation type 12bit A/D converter, 8bit D/A converter, PGA (Programable Gain Amp) and so on.

The CPU nX-U16/100 is capable of efficient instruction execution in 1-instruction 1-clock mode by pipeline architecture parallel processing.

The built-in on-chip debug function enables debugging and programming the software. Also, ISP (In-System Programming) function supports the Flash programming in production line.

#### Applications

Consumer and Industrial equipment (e.g., Household appliances, Housing equipment, Office equipment, Measurement instrumentation, etc)

Note:

This product cannot be applicable for automotive use, automatic train control systems, and railway safety systems.

Please contact ROHM sales office in advance if contemplating the integration of this product into applications that requires high reliability, such as transportation equipment for ships and railways, communication equipment for trunk lines, traffic signal equipment, power transmission systems, core systems for financial terminals and various safety control devices.

#### Product list

Table1 shows the conbination of ML62Q2033/2035/2043/2045 memory variations and package type.

|                   | Table 1 Product List |               |                  |                 |  |  |  |  |  |  |  |

|-------------------|----------------------|---------------|------------------|-----------------|--|--|--|--|--|--|--|

| Program<br>memory | Data memory<br>(RAM) | Data<br>Flash | 20pin<br>TSSOP20 | 24pin<br>WQFN24 |  |  |  |  |  |  |  |

| 32Kbyte           | 2Kbvte               | 4Kbyte        | ML62Q2035        | ML62Q2045       |  |  |  |  |  |  |  |

| 16Kbyte           | Zicoyle              | 4NDyte        | ML62Q2033        | ML62Q2043       |  |  |  |  |  |  |  |

Please see the last 2 pages "Notes for product usage" and "Notes" in this document on use with this product.

### ROHM Co...Ltd.

### FEATURES

- CPU

- 16-bit RISC CPU : nX-U16/100 (A35 core)

- Instruction system : 16-bit length instructions

- : Transfer, arithmetic operations, comparison, logic operations, Instruction set multiplication/division, bit manipulations, bit logic operations, jump, conditional

- jump, call return stack, manipulations, arithmetic shift, and so on

- Built-in On-chip debug function (connect to the ROHM on-chip debug emulator)

- Minimum instruction execution time : 1 count of system clock Approximately 30.5µs/62.5ns (at 32.768kHz/16MHz system clock)

- Coprocessor for multiplication and division

- Signed or Unsigned is selectable

| Parameter                            | Expression            | Operation time [cycle] |

|--------------------------------------|-----------------------|------------------------|

| Multiplication                       | 16bit × 16bit         | 4                      |

| Division                             | 32bit ÷ 16bit         | 8                      |

| DIVISION                             | 32bit ÷ 32bit         | 16                     |

| Multiply-accumulate (non-saturating) | 16bit × 16bit + 32bit | 4                      |

- Operating voltage and temperature

- Operating voltage : V<sub>DD</sub> = 4.5 to 5.5V

- Operating temperature : -40°C to +105°C

#### Flash memory

| Parameter                    | Program memory area | Data Flash memory area |

|------------------------------|---------------------|------------------------|

| Erase/Write count            | 100cycles           | 10,000cycles           |

| Write unit                   | 16bit (2byte)       | 8bit (1byte)           |

| Erase unit                   | 16Kbyte/1Kbyte      | all area/128byte       |

| Erase/Write temperature (Ta) | 0°C to +40°C        | -40°C to +85°C         |

- Background Operation (CPU can work while erasing and rewriting to the Data Flash memory area.)

- The built-in on-chip debug function and ISP (In-System Programming) function enable Flash programming

This product uses Super Flash® technology licensed from Silicon Storage Technology, Inc. Super Flash® is a registered trademark of Silicon Storage Technology, Inc.

- Data RAM area

- Rewrite unit: 8bit/16bit (1byte/2byte)

- Parity check function is available (interrupt or reset is generatable at Parity error)

- Clock generation circuit

- Low-speed clock (LSCLK0)

- Internal low-speed RC oscillation (RC32K) : Approx. 32.768kHz

- High-speed source clock (HSOCLK) : Available for PWM generation circuit clock PLL oscillation : 64MHz

- High-speed system clock (HSCLK)

- : 16MHz, generated by dividing HSOCLK

- Reset

- System Resets by reset input pin, Power-On Reset, Low Level Detector (LLD) reset, Watchdog timer (WDT) overflow, WDT invalid clear, RAM parity error reset, and Progran Counter error reset (instruction access to unused ROM area)

- Software reset by BRK instruction (reset CPU only)

- Reset the peripherals individually/collectively by software

- Power management

- Two stand-by mode.

- STOP mode (All clocks are stopped)

- HALT mode (clocks for System are stopped)

- Individual clock input control to the peripheral blocks by software

- Clock gear: High-speed system clock frequency is changeable dynamically

- (1/1, 1/2, 1/4, 1/8, 1/16, 1/32 of HSCLK)

- Interrupt controller

- Non-maskable interrupt source : 1 (Internal sources: WDT)

- Maskable interrupt sources : 22 (included the external interrupt 4 sources)

- Four step interrupt levels

- External interrupt ports (EXI)

- : 4 (selectable from Max.8 pins) with sampling filter and edge(rise, fall, both) selection.

- General-purpose ports (GPIO)

I/O port

- : Max. 20 (Including pins for shared functions)

- Carrier frequency output function (for IR communication)

- Watchdog timer (WDT) : 1 channel

- Overflow period : 8selectable (7.8, 15.6, 31.3, 62.5, 125, 500, 2000, 8000ms)

- Selectable window function (enable or disable): configurable clear enable period (50% or 75% of overflow period) with invalid clear. When disable, interrupts the first overflow and resets the second overflow. When enable, reset occurs for the first overflow.

- Selectable WDT operation : select Enable or Disable by code option

- Selectable operation during HALT mode (Continue counting/Stop counting)

- WDT counter operation monitoring function (Readable WDT counter)

- Operational timer : 6 channels

- Various modes (Continuous, One shot, capture, and PWM mode)

- Event trigger (external terminal, 16bit timer, operational timer, comparator) input is available

- Selectable counter clock from various sources (LSCLK0, HSCLK(16MHz), HSOCLK(64MHz), divided by 1 to 8 of external pin input)

- Logic AND output with several channel output (Operational timer output, comparator output, and external pin input) is available

- 16-bit General timers : 1 channel

- Selectable counter clock from various sources (LSCLK, HSCLK (16MHz), and external clock divided by 1 to 8)

- UART (Half-duplex/Full-duplex communication mode): 2 channels Selectable from 5 to 8bit length, parity or no parity, odd parity or even parity, 1 stop bit or 2 stop bits, Positive logic or Negative logic, LSB first or MSB first

- Sampling filter for receiving data and start bit

- Built-in baud rate generator (HSCLK@16MHz: 300bps to 2Mbps, LSCLK: up to 2400bps)

- I<sup>2</sup>C bus : 1 channel

- Select from Master mode or Slave mode: 1channel. Master mode only: 1channel

- Standard mode (100kbps), fast mode (400kbps) and 1Mbps mode (1Mbps)

- 7bit address format

- Master mode: Handshake (Clock synchronization), 10bit Master address format is supported

- Slave mode: Clock stretch function,

- Successive approximation type 12bit A/D converter (SA-ADC) : input 5 channels

- Conversion time: Min. 1.375µs / ch (When the conversion clock frequency is 16MHz)

- Reference voltages (V<sub>ADCREF</sub>) are selectable from VDD pin input voltage or Internal reference voltage (V<sub>ADCREF</sub>, Approx. 2.5V)

- Dedicated result register for each channel

- Interrupt by Continuous conversion and Trigger start

- Programable-Gain-Amp (PGA) : 1 channel

- Amplification factor : 4/ 8/16/ 32

- Voltage input pin is selectable (AIN0/ AIN1/ AIN2/ AIN3)

- Analog comparator (CMP): 3 channels

- Selectable interrupt from the comparator output (rising edge or falling edge) and sampling

- Selectable reference voltage (V<sub>CMPREFn n=0 to 2</sub>) from external pin input, internal reference voltage (0.8V) (V<sub>CMPREFI</sub>), and D/A converter

- D/A converter (DAC) : 2 channels : 8 bit

- Resolution

- Output impedance : 10kΩ (Typ.)

- R-2R ladder type

- Reference voltages (V<sub>DACREF</sub>) are selectable from VDD pin input voltage or Internal reference voltage (0.8V) (V<sub>DACREF</sub>)

- Low Level Detector (LLD) : 1 channel

- Reset generating

- Sampling filter

- Low power operation

- Safety Function

- RAM/SFR guard

- RAM parity error detection

- ROM unused area access reset (instruction access)

- WDT counter monitoring

- SA-ADC test

- Communication loop back test (UART, I<sup>2</sup>C bus(master))

- GPIO test

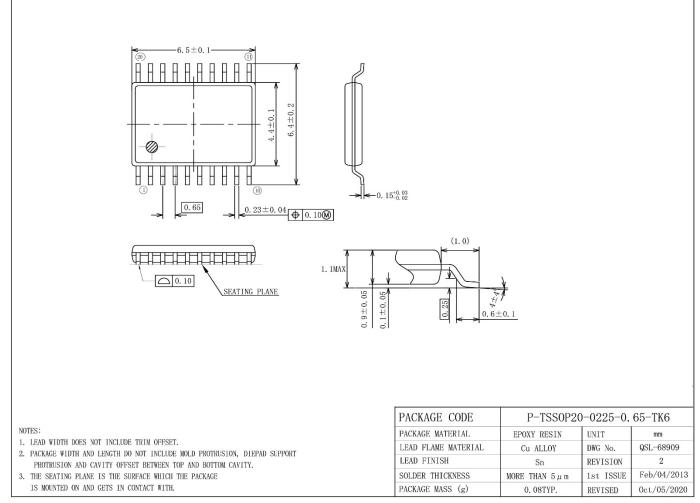

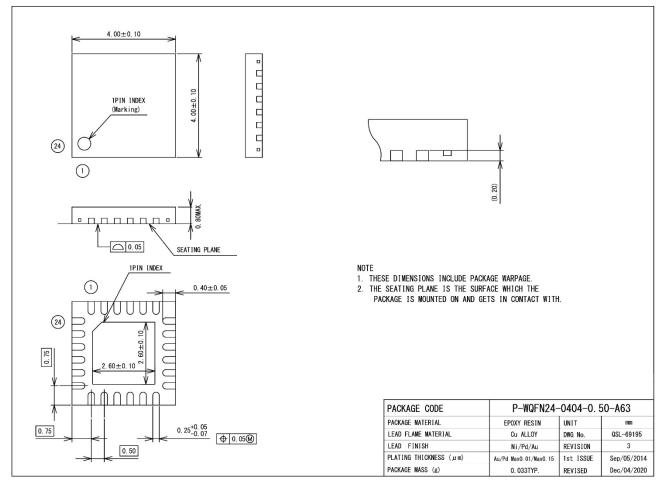

- Shipping package

| Package              | Body size                     | Pin pitch | Packing form and Product name                |                                              |  |  |  |  |

|----------------------|-------------------------------|-----------|----------------------------------------------|----------------------------------------------|--|--|--|--|

| Раскауе              | (including lead)<br>[mm × mm] | [mm]      | Tray                                         | Tape & Reel                                  |  |  |  |  |

| 20 pin plastic TSSOP | 6.5 × 4.4<br>(6.5 × 6.4)      | 0.65      | ML62Q2033-xxxTDZWARZ<br>ML62Q2035-xxxTDZWARZ | ML62Q2033-xxxTDZWATZ<br>ML62Q2035-xxxTDZWATZ |  |  |  |  |

| 24 pin plastic WQFN  | 4.0 × 4.0<br>( - )            | 0.50      | ML62Q2043-xxxGDZW5AY<br>ML62Q2045-xxxGDZW5AY | ML62Q2043-xxxGDZW5BY<br>ML62Q2045-xxxGDZW5BY |  |  |  |  |

xxx: ROM code number, (NNN: ROM code is blank)

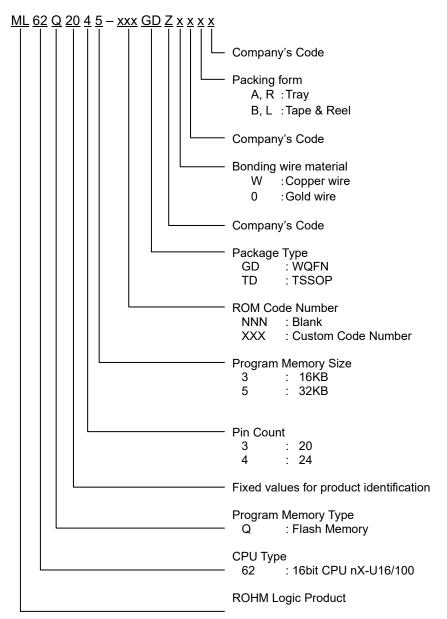

### How To Read The Part Number

Figure 1 Part Number

### **Main Function List**

|                        |           |           |                 |                                       |                                                  |                        | Table                     | 2 Ma                          | ain Fu                             | unctio           |                             |                                |                     | T         |                                                 |                                          |                        |                    |          |

|------------------------|-----------|-----------|-----------------|---------------------------------------|--------------------------------------------------|------------------------|---------------------------|-------------------------------|------------------------------------|------------------|-----------------------------|--------------------------------|---------------------|-----------|-------------------------------------------------|------------------------------------------|------------------------|--------------------|----------|

|                        |           | 1         |                 | Pin                                   |                                                  | 1                      | In                        | iterru                        | pt                                 |                  | Tin                         | ner                            |                     | Commu     | nication                                        |                                          | Ana                    | alog               | 1        |

| Part number            | Total pin | Power pin | Reset Input pin | General purpose I/O pin <sup>*1</sup> | General purpose I/O pin (LED drive is supported) | External interrupt pin | External interrupt source | Non maskable interrupt source | Internal maskable interrupt source | 16bit Timer [ch] | 16bit oprational Timer [ch] | 16bit operational Timer [Port] | Watchdog Timer [ch] | UART [ch] | I <sup>2</sup> C bus unit (Master / Slave) [ch] | 12bit Successive type A/D converter [ch] | Analog Comparator [ch] | D/A converter [dh] | PGA [ch] |

| ML62Q2033<br>ML62Q2035 | 20        |           |                 |                                       | 15                                               |                        |                           |                               |                                    |                  |                             | 10                             |                     |           |                                                 |                                          |                        |                    |          |

| ML62Q2035<br>ML62Q2043 |           | 3         | 1               | 1                                     |                                                  | 8                      | 4                         | 1                             | 18                                 | 1                | 6                           |                                | 1                   | 2         | 1                                               | 5                                        | 3                      | 2                  | 1        |

| ML62Q2045              | 24        |           |                 |                                       | 19                                               |                        |                           |                               |                                    |                  |                             | 13                             |                     |           |                                                 |                                          |                        |                    |          |

\*1: Shared with pins debug input.

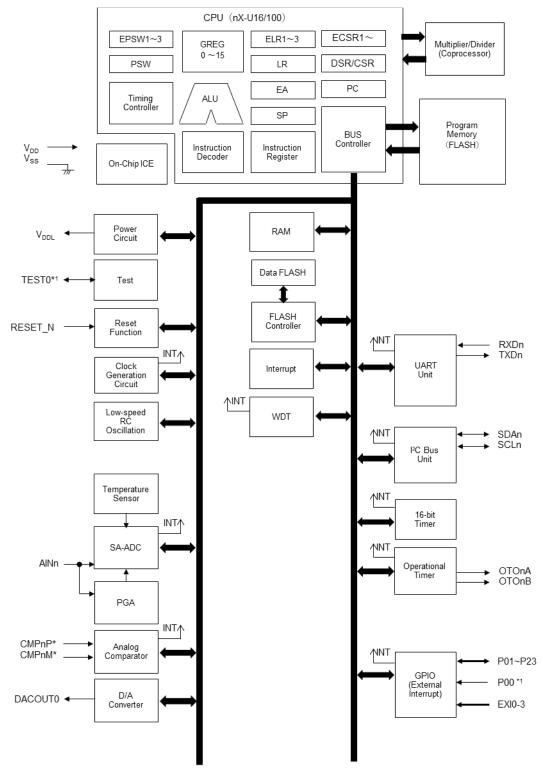

### **BLOCK DIAGRAM**

\*1 : Not available as the input port when connecting to the on-chip debug emulator.

Figure 2 Block Diagram

#### FEDL62Q2045-02 ML62Q2033/2035/2043/2045

# ROHM Co., Ltd.

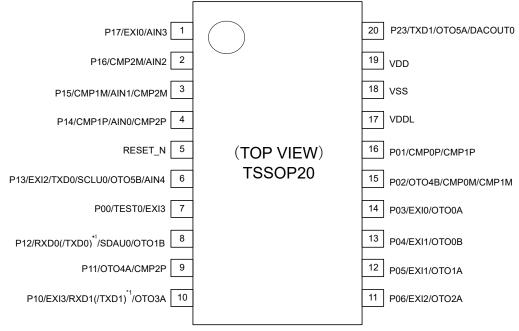

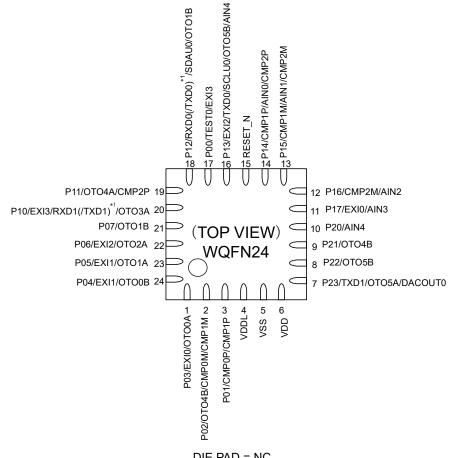

### **PIN CONFIGURATION**

\*1: RXDn pin is shareable with TXDn pin by SFR setting

Fig.3-1 20 pin TSSOP

DIE PAD = NC \*1: RXDn pin is shareable with TXDn pin by SFR setting

Fig.3-2 24 pin WQFN

### **PIN LIST**

Table 3 Pin List

| Pin       | No        |           | 1 <sup>st</sup> | 2 <sup>nd</sup>                             | 3 <sup>rd</sup>  | 4 <sup>th</sup> | 5 <sup>th</sup> | 6 <sup>th</sup> | 7 <sup>th</sup> | 8 <sup>th</sup> |

|-----------|-----------|-----------|-----------------|---------------------------------------------|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| Pin       | INO.      |           | function        | function                                    | function         | function        | function        | function        | function        | function        |

| ML62Q203x | ML62Q204x | Pin name  | GPI/<br>EXI     | UART*                                       | I <sup>2</sup> C | ОТМ             | CMP/DAC         | ADC             | CMP             | CMP/ADC         |

| 19        | 6         | VDD       | -               | -                                           | -                | -               | -               | -               | -               | -               |

| 18        | 5         | VSS       | -               | -                                           | -                | -               | -               | -               | -               | -               |

| 17        | 4         | VDDL      | -               | -                                           | -                | -               | -               | -               | -               | -               |

| 16        | 3         | P01       | -               | -                                           | -                | -               | CMP0P           | -               | CMP0P/<br>CMP1P | CMP0P           |

| 15        | 2         | P02       | -               | -                                           | -                | OTO4B           | CMP0M           | -               | CMP0M/<br>CMP1M | CMP0M           |

| 14        | 1         | P03       | EXI0            | -                                           | -                | OTO0A           | -               | -               | -               | -               |

| 13        | 24        | P04       | EXI1            | -                                           | -                | OTO0B           | -               | -               | -               | -               |

| 12        | 23        | P05       | EXI1            | -                                           | -                | OTO1A           | -               | -               | -               | -               |

| 11        | 22        | P06       | EXI2            | -                                           | -                | OTO2A           | -               | -               | -               | -               |

| -         | 21        | P07       | -               | -                                           | -                | OTO1B           | -               | -               | -               | -               |

| 10        | 20        | P10       | EXI3            | RXD1* <sup>1</sup><br>(/TXD1)* <sup>2</sup> | -                | ОТОЗА           | -               | -               | -               | -               |

| 9         | 19        | P11       | -               | -                                           | -                | OTO4A           | CMP2P           | -               | CMP2P           | CMP2P           |

| 8         | 18        | P12       | -               | RXD0*1<br>(/TXD0)*2                         | SDAU0            | OTO1B           | -               | -               | -               | -               |

| 7         | 17        | P00/TEST0 | EXI3            | -                                           | -                | -               | -               | -               | -               | -               |

| 6         | 16        | P13       | EXI2            | TXD0*1                                      | SCLU0            | OTO5B           | -               | AIN4            | -               | -               |

| 5         | 15        | RESET_N   | -               | -                                           | -                | -               | -               | -               | -               | -               |

| 4         | 14        | P14       | -               | -                                           | -                | -               | CMP1P           | AIN0            | CMP1P/<br>CMP2P | AIN0<br>/CMP1P  |

| 3         | 13        | P15       | -               | -                                           | -                | -               | CMP1M           | AIN1            | CMP1M/<br>CMP2M | AIN1<br>/CMP1M  |

| 2         | 12        | P16       | -               | -                                           | -                | -               | CMP2M           | AIN2            | CMP2M           | AIN2<br>/CMP2M  |

| 1         | 11        | P17       | EXI0            | -                                           | -                | -               | -               | AIN3            | -               | -               |

| -         | 10        | P20       | -               | -                                           | -                | -               | -               | AIN4            | -               | -               |

| -         | 9         | P21       | -               | -                                           | -                | OTO4B           | -               | -               | -               | -               |

| -         | 8         | P22       | -               | -                                           | -                | OTO5B           | -               | -               | -               | -               |

| 20        | 7         | P23       | -               | TXD1* <sup>1</sup>                          | -                | OTO5A           | DACOUT0         | -               | -               | -               |

| DIE       |           | NC        | -               | -                                           | -                | -               | -               | -               | -               | -               |

\*1: The UARTpin use with a combination of the same suffix pins

$^{\star 2}$ : RXDn pin is shareable with TXDn pin by SFR setting

### **PIN DESCRIPTION**

"I/O" Field in the below table define the pin type ("-" : power supply pin, "I" : Input pin, "O" : Out put pin, "I/O" bi-directional pin)

|                             |                        |                 | ole 4 Pir | n Description                                                                                                                                                                           |

|-----------------------------|------------------------|-----------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function                    | Functional pin<br>name | LSI pin<br>name | I/O       | Description                                                                                                                                                                             |

|                             | -                      | VSS             | -         | Negative power supply pin (-)<br>Define this terminal potential as Vss.                                                                                                                 |

| Power                       | _                      | VDD             | -         | Positive power supply pin (+).<br>Connect a capacitor $C_V$ (more than 1µF) between this pin and VSS. Define this terminal potential as $V_{DD}$                                        |

|                             | -                      | VDDL            | -         | Power supply for internal logic (internal regulator's output).<br>Connect a capacitor $C_L(1\mu F)$ between this pin and VSS                                                            |

| Debug<br>ISP                | TEST0                  | P00/<br>TEST0   | I/O       | Input/output for testing<br>This pin which is shared with P00 is used as on-chip debug<br>interface and ISP function and is initialized as pull-up input<br>mode by the system reset.   |

| Reset                       | RESET_N                | RESET_N         | I         | Reset input.<br>Appling this pin "L" level shifts MCU to system reset mode.<br>Appling this pin "H" level shifts MCU to program running mode.<br>No pull-up resistor is built-in.       |

| General input port<br>(GPI) | P00                    | P00/<br>TEST0   | I/O       | General purpose input.<br>- Input with Pull-up (initial value)<br>- Input without Pull-up<br>Not available as general inputs when using the on-chip debug<br>interface or ISP function. |

|                             | P01 to P07             | P01 to P07      |           | General purpose input/output<br>- High-impedance (initial value)                                                                                                                        |

| General port<br>(GPIO)      | P10 to P17             | P10 to P17      | I/O       | - Input with Pull-up<br>- Input without Pull-up<br>- CMOS output                                                                                                                        |

|                             | P20 to P23             | P20 to P23      |           | - N channel (N-ch) open drain output<br>- P channel (P-ch) open drain output                                                                                                            |

| Career frequency<br>output  | -                      | P13 P23         | 0         | Career frequency output                                                                                                                                                                 |

| i                           | EXI0                   | P03 P17         |           | External Maskable Interrupt 0 input                                                                                                                                                     |

| External Interrupt          | EXI1                   | P04 P05         |           | External Maskable Interrupt 1 input                                                                                                                                                     |

| (1 <sup>st</sup> function)  | EXI2                   | P06 P13         |           | External Maskable Interrupt 2 input                                                                                                                                                     |

|                             | EXI3                   | P00 P10         |           | External Maskable Interrupt 3 input                                                                                                                                                     |

|                             | OTO0A                  | P03             |           | Operational Timer 0 A output                                                                                                                                                            |

|                             | OTO0B                  | P04             |           | Operational Timer 0 B output                                                                                                                                                            |

|                             | OTO1A                  | P05             |           | Operational Timer 1 A output                                                                                                                                                            |

|                             | OTO1B                  | P07 P12         |           | Operational Timer 1 B output                                                                                                                                                            |

| Operational Timer           | OTO2A                  | P06             |           | Operational Timer 2 A output                                                                                                                                                            |

| (4 <sup>th</sup> function)  | OTO3A                  | P10             | 0         | Operational Timer 3 A output                                                                                                                                                            |

|                             | OTO4A                  | P11             |           | Operational Timer 4 A output                                                                                                                                                            |

|                             | OTO4B                  | P02 P21         | 1         | Operational Timer 4 B output                                                                                                                                                            |

|                             | OTO5A                  | P23             | 1         | Operational Timer 5 A output                                                                                                                                                            |

|                             | OTO5B                  | P13 P22         | 1         | Operational Timer 5 B output                                                                                                                                                            |

| l <sup>2</sup> C Bus        | SCLU0                  | P13             |           | I <sup>2</sup> C Unit0 Clock input/output                                                                                                                                               |

| (3 <sup>rd</sup> function)  | SDAU0                  | P12             | I/O       | I <sup>2</sup> C Unit0 Data input/output                                                                                                                                                |

| Function                                                                                      | Functional pin<br>name | LSI pin<br>name               | I/O | Description                            |

|-----------------------------------------------------------------------------------------------|------------------------|-------------------------------|-----|----------------------------------------|

|                                                                                               | RXD0                   | P12                           | Ι   | UART0 received data input              |

| UART                                                                                          | TXD0                   | P13                           | 0   | UART0 transmission data output         |

| (2 <sup>nd</sup> function)                                                                    | RXD1                   | P10                           | I   | UART1 received data input              |

|                                                                                               | TXD1                   | P23                           | 0   | UART1 transmission data output         |

| Successive<br>approximation<br>type A/D converter<br>(SA-ADC)<br>(6/8 <sup>th</sup> function) | AIN0 to AIN4           | P14 P15<br>P16 P17<br>P13 P20 | I   | SA-ADC channel 0 to 4 analog input     |

| D/A converter<br>(5 <sup>th</sup> function)                                                   | DACOUT0                | P23                           | ο   | D/A converter 0 output (select by SFR) |

|                                                                                               | CMP0P                  | P01                           |     | Analog comparator 0 Noninverting input |

|                                                                                               | CMP0M                  | P02                           |     | Analog comparator 0 Inverting input    |

| Analog                                                                                        | CMP1P                  | P01 P14                       |     | Analog comparator 1 Noninverting input |

| comparator<br>(5/7/8 <sup>th</sup> function)                                                  | CMP1M                  | P02 P15                       |     | Analog comparator 1 Inverting input    |

|                                                                                               | CMP2P                  | P11 P14                       |     | Analog comparator 2 Noninverting input |

|                                                                                               | CMP2M                  | P15 P16                       |     | Analog comparator 2 Inverting input    |

### **TERMINATION OF UNUSED PINS**

Table 5 shows the processing of unused pins.

Table 5 Termination of unused pins

| Pin                                    | pin termination                                                                       |

|----------------------------------------|---------------------------------------------------------------------------------------|

| RESET_N                                | Connect to VDD                                                                        |

| P00/TEST0                              | Open with the initial condition of pulled-up input mode                               |

| P01 to P07<br>P10 to P17<br>P20 to P23 | Open the pins with the initial condition of Hi-impedance (input/output invalid) mode. |

[Note]

Terminate unused input pins according to the table 5 in order to avoid unexpected through-current in the pins.

### **ELECTRICAL CHARACTERISTICS**

#### Absolute Maximum Ratings

|                          |                  |                 |        |                                | (Vss = 0V) |  |

|--------------------------|------------------|-----------------|--------|--------------------------------|------------|--|

| Parameter                | Symbol           | Cone            | dition | Rating                         | Unit       |  |

| Power supply voltage 1   | V <sub>DD</sub>  |                 |        | -0.3 to +6.5                   |            |  |

| Power supply voltage 2   | Vddl             | т. –            | +25°C  | -0.3 to +2.0                   | - V        |  |

| Input voltage            | Vin              | ia = ·          | +25°C  | -0.3 to V <sub>DD</sub> +0.3*1 | V          |  |

| Output voltage1          | Vout1            |                 |        | -0.3 to V <sub>DD</sub> +0.3*1 |            |  |

| "L" lovel output ourrept | 1                |                 | 1pin   | -40*2                          |            |  |

| "H" level output current | Іоитн            | T 10500         | Total  | -150* <sup>2</sup>             |            |  |

|                          |                  | Ta = +25°C 1pin |        | +40                            | – mA       |  |

| "L" level output current | Ιουτι            |                 | Total  | +150                           |            |  |

| Power dissipation        | PD               | Ta = +25°C      |        | 1                              | W          |  |

| Storage temperature      | T <sub>STG</sub> |                 | -      | -55 to +150 <sup>*3</sup>      | °C         |  |

\*1: 6.5V or lower

\*2: The current flowing out the LSI through the pin is described in the negative number. The applicable maximum current is the absolute value.

For example, -1mA means the maximum current 1mA flows out the LSI through the pin.

\*3: Please observe a storage conditions shown in the document "Board Mounting (soldering)" about the storage conditions until implementation.

#### [Note]

Stresses above the absolute maximum ratings listed in the above table may cause permanent damage to the device.

These are stress ratings only and functional operation of the device at these conditions is not implied.

#### **Recommended Operating Conditions**

|                                       |                 |                              |             | (Vss = 0V) |

|---------------------------------------|-----------------|------------------------------|-------------|------------|

| Parameter                             | Symbol          | Condition                    | Range       | Unit       |

| Operating temperature (Ambient)       | Та              | -                            | -40 to +105 |            |

| Operating temperature (Chip-Junction) | Tj              | -                            | -40 to +115 | - °C       |

| Operating voltage 1                   | V <sub>DD</sub> | -                            | 4.5 to 5.5  | V          |

| Operating frequency (CPU)             | f <sub>OP</sub> | V <sub>DD</sub> =4.5 to 5.5V | 30k to 16M  | Hz         |

| VDDL pin external capacitance         | CL              | -                            | 1.0 ±30%    | μF         |

#### Thermal characteristics

The maximum chip-junction temperature, T<sub>jmax</sub>, is estimated using the following equation.

$T_{j max} = T_{a max} + P_{D max} \times \theta_{ja}$   $T_{a max}$ : maximum ambient temperature  $P_{D max}$ : LSI maximum power dissipation  $\theta_{ja}$ : Package junction to ambient thermal resistance

Design a Mounting board by considering heat radiation such as power dissipation and ambient temperature to satisfy the recommended conditions.

The following table shows the each package's thermal resistance for thermal design reference estimated by simulation based on the PCB (printed circuit board) conditions define as a below.

| Parameter  | Symbol | Deekege type | PCB co | Linit |        |

|------------|--------|--------------|--------|-------|--------|

|            | Symbol | Package type | L1     | L2    | - Unit |

| Thermal    | 0      | TSSOP20      | 72.32  | 68.83 |        |

| resistance | θja    | WQFN24       | 38.86  | 34.81 | °C/W   |

PCB conditions:

| PCB name             | L1                  | L2                         | Unit  |  |  |  |

|----------------------|---------------------|----------------------------|-------|--|--|--|

| PCB size (L / W / T) | 114.3 / 76.2 / 1.6  | 114.3 / 76.2 / 1.6         | mm    |  |  |  |

| Number of layers     | 1                   | 2                          | layer |  |  |  |

| Wiring density       | 60% (top layer)     | 60% (top and bottom layer) | -     |  |  |  |

| Wind condition       | Windlessness (0m/s) |                            |       |  |  |  |

The thermal resistance of WQFN is the simulated value when the exposed die pad part (100%) is soldered with the board.

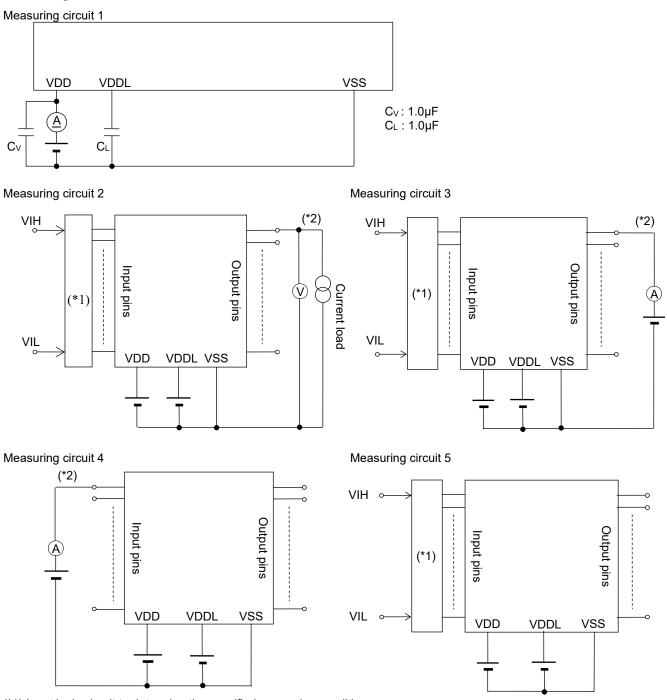

### **Current Consumption**

#### (V\_DD=4.5 to 5.5V, V\_SS =0V, Ta=-40 to +105°C, unless otherwise specified)

|           | Cond                                        |                                                        |         |        |          | ring<br>uit |      |                      |  |  |  |

|-----------|---------------------------------------------|--------------------------------------------------------|---------|--------|----------|-------------|------|----------------------|--|--|--|

| Parameter | Operating mode                              | circuit state *1                                       | Min.    | Typ.*2 | Ma       | ax.         | Unit | Measuring<br>circuit |  |  |  |

|           | Operating mode                              | Circuit State                                          | IVIIII. | Typ.   | Tj≤+95°C | Tj≤+115°C   |      | Me                   |  |  |  |

| IDD1      | STOP                                        | All clocks are stopped.                                | -       | 80     | 120      | 130         |      |                      |  |  |  |

| IDD2-1R   | HALT<br>(Hi-speed oscillation off)          | RC32K is oscillating.<br>PLL is stopped.               | -       | 90     | 140      | 150         | μA   | 1                    |  |  |  |

| IDD3      | CPU running in<br>SYSCLK=32.768kHz          | RC32K is oscillating.<br>PLL is stopped.               | -       | 100    | 160      |             |      | I                    |  |  |  |

| IDD5-H16  | CPU running in<br>wait-mode<br>SYSCLK=16MHz | PLL is oscillating as<br>PLL16M mode.<br>HSCLK = 16MHz | -       | 3.3    | 4        | .2          | mA   |                      |  |  |  |

\*1: WDT is operating except IDD1, and all clocks peripheral circuits are stopped by block control.

\*2: On the condition of  $V_{DD}$ =5.0V, Ta=+25°C

#### **On-chip Oscillator**

#### (V<sub>DD</sub>=4.5 to 5.5V, V<sub>SS</sub> =0V, Ta=-40 to +105°C, unless otherwise specified)

|                                    |                   |                                 | •             |        | •             |           | · · ·   |

|------------------------------------|-------------------|---------------------------------|---------------|--------|---------------|-----------|---------|

| Parameter                          | Symbol            | Condition                       |               | Rating | Unit          | Measuring |         |

| Falameter                          | Symbol            | Condition                       | Min.          | Тур.   | Max.          | Unit      | circuit |

| RC32K                              | f <sub>RCL1</sub> | Ta= -20 to +85°C                | Тур.<br>-1.5% | 32.768 | Тур.<br>+1.5% | kHz       |         |

| frequency                          | IRCL1             | Ta= -40 to +105°C               | Тур.<br>-2.0% | 32.708 | Тур.<br>+2.0% | κπz       |         |

| PLL oscillation                    | f                 | Ta= -20 to +85°C<br>with RC32K  | Тур.<br>-1.5% | 64     | Тур.<br>+1.5% | MHz       | 1       |

| frequency                          | f <sub>PLL1</sub> | Ta= -40 to +105°C<br>with RC32K | Тур.<br>-2.0% | 04     | Тур.<br>+2.0% |           |         |

| PLL oscillation stabilization time | T <sub>PLL</sub>  | -                               | -             | -      | 2             | ms        |         |

\*: The frequency is the factory default specification. It may vary depending on the board mounting.

#### Input / Output pin 1

|                                                             |                                     | (V <sub>DI</sub>                                   | ; =0V, Ta=-4            | 10 to +105°             | C, unless c | therwis | e specified) |           |

|-------------------------------------------------------------|-------------------------------------|----------------------------------------------------|-------------------------|-------------------------|-------------|---------|--------------|-----------|

| Parameter                                                   | Symbol                              | Condition                                          |                         |                         | Rating      |         | Unit         | Measuring |

| Falameter                                                   | Symbol                              |                                                    |                         | Min.                    | Тур.        | Max.    | Unit         | circuit   |

| Output voltage1<br>"H"/"L" level<br>(all input/output port) | VOH1                                | IOH1=-10n                                          | V <sub>DD</sub><br>-1.5 | -                       | -           |         |              |           |

|                                                             | VOHI                                | IOH1=-4m/                                          | ٩                       | V <sub>DD</sub><br>-0.5 | -           | -       |              |           |

|                                                             | VOL1                                | IOL1=+10r                                          | nA                      | -                       | -           | 1.5     |              |           |

|                                                             |                                     | IOL1=+4m                                           | -                       | -                       | 0.5         |         |              |           |

| Output voltage2                                             |                                     |                                                    | IOL2=+15mA              | -                       | -           | 0.7     | V            | 2         |

| "L" level<br>(all input/output port                         | VOL2                                | When N-ch open<br>drain output mode<br>is selected | IOL2=+8mA               | -                       | -           | 0.5     |              |           |

| except TEST0)                                               |                                     | 10 00100100                                        | IOL2=+3mA               | -                       | -           | 0.4     |              |           |

| Output voltage2<br>"H" level                                | When P-ch open<br>drain output mode | IOL2=-10mA                                         | V <sub>DD</sub><br>-1.5 | -                       | -           |         |              |           |

| (all input/output port<br>except TEST0)                     |                                     | is selected                                        | IOL2=-4mA               | V <sub>DD</sub><br>-0.5 | -           | -       |              |           |

| (V <sub>DD</sub> =4.5 to 5.5V, V <sub>SS</sub> =0V, Ta=-40 to +105°C, unless otherwise specified) |        |                                              |                          |                     |                          |      |           |  |  |  |  |

|---------------------------------------------------------------------------------------------------|--------|----------------------------------------------|--------------------------|---------------------|--------------------------|------|-----------|--|--|--|--|

| Parameter                                                                                         | Symbol | Condition                                    |                          | Rating              |                          | Unit | Measuring |  |  |  |  |

| Falameter                                                                                         | Symbol | Condition                                    | Min.                     | Тур.                | Max.                     | Unit | circuit   |  |  |  |  |

| Input current1                                                                                    | IIH1   | VIH1=V <sub>DD</sub>                         | -                        | -                   | 1                        |      |           |  |  |  |  |

| (RESET_N)                                                                                         | IIL1   | VIL1=Vss                                     | -1 <sup>*1</sup>         | -                   | -                        | μA   |           |  |  |  |  |

|                                                                                                   | IIL2   | VIL2=V <sub>SS</sub> (pull-up mode) *2       | -1500 <sup>*1</sup>      | -1000 <sup>*1</sup> | -300 <sup>*1</sup>       |      |           |  |  |  |  |

| Input current2<br>(P00/TEST0)                                                                     | V/IIL2 | VIL2=V <sub>SS</sub> (pull-up mode) *2       | 3.7                      | 5.0                 | 15                       | kΩ   |           |  |  |  |  |

|                                                                                                   | IIH2Z  | VIH2=V <sub>DD</sub> (High impedance mode) 1 |                          |                     | 4                        |      |           |  |  |  |  |

|                                                                                                   | IIL2Z  | VIL2=V <sub>SS</sub> (High impedance mode)   | -1 <sup>*1</sup>         | -                   | -                        | μA   | 4         |  |  |  |  |

|                                                                                                   | IIL3   | VIL1=V <sub>SS</sub> (pull-up mode) *2       | -250 <sup>*1</sup>       | -125 <sup>*1</sup>  | -30 <sup>*1</sup>        |      |           |  |  |  |  |

| Input current3<br>(all input port except<br>RESET_N,                                              | V/IIL3 | VIL1= Vss (pull-up mode) *2                  | 22                       | 40                  | 150                      | kΩ   |           |  |  |  |  |

| P00/TEST0,<br>input/output port)                                                                  | IIH3Z  | VIH1=V <sub>DD</sub> (High impedance mode)   | -                        | -                   | 1                        |      |           |  |  |  |  |

|                                                                                                   | IIL3Z  | VIL1=V <sub>SS</sub> (High impedance mode)   | -1 <sup>*1</sup>         | -                   | -                        | μA   |           |  |  |  |  |

| Input voltage1                                                                                    | VIH1   | -                                            | 0.7<br>× V <sub>DD</sub> | -                   | V <sub>DD</sub>          | v    | _         |  |  |  |  |

| (all input port,<br>input/output port)                                                            | VIL1   | -                                            | 0                        | -                   | 0.3<br>× V <sub>DD</sub> | V    | 5         |  |  |  |  |

| Pin capacitance<br>(RESET_N, all input<br>port, input/output port)                                | CPIN   | f=10kHz<br>Ta=25°C                           | -                        | -                   | 10                       | pF   | -         |  |  |  |  |

\*1: The current flowing out the LSI through the pin is described in the negative number. The applicable maximum current is the absolute value. For example, -1mA means the maximum current 1mA flows out the LSI through the pin. \*2: Measurement conditions: Typ: VDD = 5.0V, Max: VDD = 4.5V, Min: VDD = 5.5V

#### Input / Output pin 2

#### (V<sub>DD</sub>=4.5 to 5.5V, V<sub>SS</sub> =0V, Ta=-40 to +105°C, unless otherwise specified)

|                                                     |        |                                            | D-4.0 to 0.0 v, vss - |                     | Rating | - ,                 | Linit | Measuring |

|-----------------------------------------------------|--------|--------------------------------------------|-----------------------|---------------------|--------|---------------------|-------|-----------|

| Parameter                                           | Symbol | Conditio                                   | n                     | Min.                | Тур.   | Max.                | Unit  | circuit   |

| "H" level output<br>current1 * <sup>6</sup>         | IOH1   | 1pin                                       | -                     | -10* <sup>3*5</sup> | -      | -                   |       |           |

| "H" level output<br>total current1 * <sup>1*4</sup> |        | Total of group A or B **                   | Ta=-40 to 85 °C       | -25 <sup>*5</sup>   | -      | -                   |       |           |

|                                                     | IOH3   | (duty ≤ 50%)                               | Ta=-40 to 105 °C      | -12 <sup>*5</sup>   | -      | -                   |       |           |

|                                                     | 10113  | All pin total                              | Ta=-40 to 85 °C       | -50 <sup>*5</sup>   | -      | -                   |       |           |

|                                                     |        | (duty ≤ 50%)                               | Ta=-40 to 105 °C      | -24 <sup>*5</sup>   | -      | -                   |       |           |

| "L" level output<br>current1 *6                     | IOL1   | 1pin<br>(CMOS output mode)                 | -                     | -                   | -      | 10* <sup>3</sup> mA |       |           |

| "L" level output<br>current2 * <sup>6</sup>         | IOL2   | 1pin<br>(N-ch open drain output<br>mode)   | -                     | -                   | -      | 15* <sup>3</sup>    |       | 3         |

|                                                     |        | Total of group A or B **                   | Ta=-40 to 85°C        | -                   | -      | 25                  |       |           |

| "L" level output total                              |        | (N-ch open drain output<br>mode, duty≤50%) | Ta=-40 to105°C        | -                   | -      | 15                  |       |           |

| current *2*4                                        | IOL3   |                                            | Ta=-40 to 85°C        | -                   | -      | 50                  |       |           |

|                                                     |        | (N-ch open drain output<br>mode, duty≤50%) | Ta=-40 to 105°C       | -                   | -      | 30                  |       |           |

| Output leak                                         | IOOH   | VOH=V <sub>DD</sub> (High imp              | edance mode)          | -                   | -      | +1                  |       |           |

| (all input/output port)                             | IOOL   | VOL=Vss (High impe                         | edance mode)          | -1* <sup>5</sup>    | -      | -                   | μA    |           |

\*\* : Group A is "P00 to P07 and P10 to P12", group B is "P13 to P17 and P20 to P23".

\*1: Sink-out current from VDD to the output pin, which can guarantee the device operation.

\*2: Sink-in current from the output pin to VSS, which can guarantee the device operation.

\*3: Do not exceed total current.

\*4: The total current is on the condition of Duty≤50% (same applies to IOH1). When the duty>50% the total current is calculated by following formula. Total current = IOL3 x 50/n (When the duty is n%)

<For an example> When IOL3=100mA and n=80%, Total current = IOL3 x 50/80 = 62.5mA Current allowed per 1pin is independent of the duty and specified as IOL1 and IOL2.

Do not apply current larger than Absolute Maximum Ratings.

\*5: The current flowing out the LSI through the pin is described in the negative number. The applicable maximum current is the absolute value.

For example, -1mA means the maximum current 1mA flows out the LSI through the pin.

\*6: These values are satisfied with VOH1, VOL1 and VOL2.

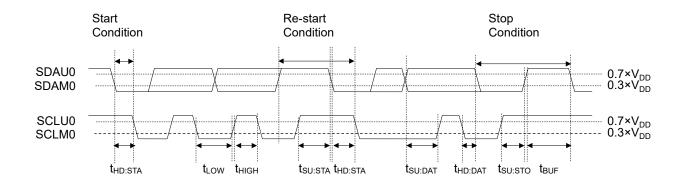

#### I<sup>2</sup>C Bus Interface

| (V <sub>DD</sub> =4.5 to 5.5V, V <sub>SS</sub> =0V, Ta=-40 to +105°C, unless otherwise sp |                     |      |         |      |           |        |           |      |      |      | pecified) |

|-------------------------------------------------------------------------------------------|---------------------|------|---------|------|-----------|--------|-----------|------|------|------|-----------|

|                                                                                           |                     |      |         |      |           | Rating |           |      |      |      |           |

| Parameter                                                                                 | Symbol              | Sta  | ndard M | ode  | Fast Mode |        | 1Mbps Moo |      | de   | Unit |           |

|                                                                                           |                     | Min. | Тур.    | Max. | Min.      | Тур.   | Max.      | Min. | Тур. | Max. |           |

| Operating Voltage                                                                         | V <sub>DD</sub>     | 4.5  | -       | 5.5  | 4.5       | -      | 5.5       | 4.5  | -    | 5.5  | V         |

| SCL clock frequency                                                                       | fscl                | 0    | -       | 100  | 0         | -      | 400       | 0    | -    | 1000 | kHz       |

| SCL hold time (start/restart condition)                                                   | t <sub>HD:STA</sub> | 4.0  | -       | -    | 0.6       | -      | -         | 0.26 | -    | -    |           |

| SCL "L" level time                                                                        | t <sub>LOW</sub>    | 4.7  | -       | -    | 1.3       | -      | -         | 0.5  | -    | -    |           |

| SCL "H" level time                                                                        | t <sub>ніGн</sub>   | 4.0  | -       | -    | 0.6       | -      | -         | 0.26 | -    | -    |           |

| SCL setup time (restart condition)                                                        | tsu:sta             | 4.7  | -       | -    | 0.6       | -      | -         | 0.26 | -    | -    | ue        |

| SDA hold time                                                                             | t <sub>HD:DAT</sub> | 0    | -       | -    | 0         | -      | -         | 0    | -    | -    | μs        |

| SDA setup time                                                                            | t <sub>SU:DAT</sub> | 0.25 | -       | -    | 0.1       | -      | -         | 0.1  | -    | -    |           |

| SDA setup time (stop condition)                                                           | t <sub>su:sto</sub> | 4.0  | -       | -    | 0.6       | -      | -         | 0.26 | -    | -    |           |

| Bus-free time                                                                             | <b>t</b> BUF        | 4.7  | -       | -    | 1.3       | -      | -         | 0.5  | -    | -    |           |

When using the I<sup>2</sup>C as the master, configure the I<sup>2</sup>C master 0 mode register(I2M0MOD) and I<sup>2</sup>C bus 0 mode register (master side, I2U0MOD) so that meet these specifications.

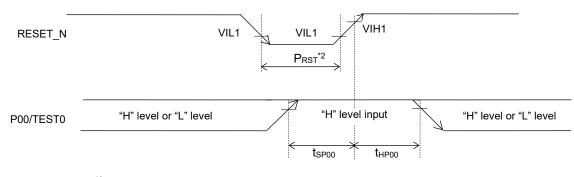

#### Reset

#### (V<sub>DD</sub>=4.5 to 5.5V, V<sub>SS</sub> =0V, Ta=-40 to +105°C, unless otherwise specified)

|                                      | ,                 |           |      |        |       |           | ,       |

|--------------------------------------|-------------------|-----------|------|--------|-------|-----------|---------|

| Deveryoter                           | Current el        |           |      | Rating | Linit | Measuring |         |

| Parameter                            | Symbol            | Condition | Min. | Тур.   | Max.  | Unit      | circuit |

| Reset pulse width <sup>*1</sup>      | P <sub>RST</sub>  | -         | 2    | -      | -     |           |         |

| P00"H" level setup time              | tsp00             | -         | 1    | -      | -     | ms        | 1       |

| P00"H" level hold time <sup>*1</sup> | t <sub>HP00</sub> | -         | 1    | -      | -     |           |         |

\*1: except ISP mode. Refer to the User's manual "25.4 In-System Programing Function" for the timing in ISP mode.

$^{*2}: V_{\text{DD}}\text{=}4.5\text{V}$  or over at power on.

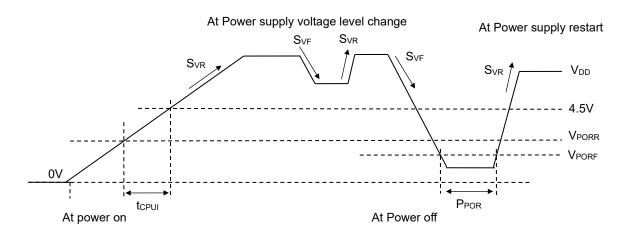

#### Slope of Power supply and Power On Reset

|                                                                                     |        |                         | (Vss =0V, T | a=-40 to +10 | )5°C, unless | otherwis | se specified) |

|-------------------------------------------------------------------------------------|--------|-------------------------|-------------|--------------|--------------|----------|---------------|

| Parameter                                                                           | Symbol | Condition               |             | Rating       |              | Unit     | Measuring     |

| Symbol                                                                              | Symbol | Condition               | Min.        | Тур.         | Max.         | Unit     | circuit       |

| Power supply voltage rising<br>inclination                                          | Svr    | -                       | -           | -            | 60           | V/ms     |               |

| Power supply voltage falling<br>inclination                                         | Svf    | -                       | -           | -            | 2            | v/ms     |               |

| Power on reset                                                                      | VPORR  | At Power up (rising)    | 3.70        | 4.10         | 4.50         | v        | 1             |

| detection voltage                                                                   | VPORF  | At Power down (falling) | 3.60        | 4.00         | 4.40         | V        |               |

| Power on reset minimum pulse width                                                  | PPOR   | -                       | 200         | -            | -            | μs       |               |

| CPU operation start time<br>(from the release of reset to<br>the CPU starts to run) | tcpui  | _                       | 11.5        | 16.5         | -            | ms       | -             |

[Note]

- If a pulse shorter than the Power on reset minimum pulse width is asserted to V<sub>DD</sub>, it may cause the MCU malfunction. Apply prevent measurement such as bypass capacitors or external reset input, and so on.

- Set V<sub>DD</sub> to 4.5V or higher before starting CPU operation.

#### LLD characteristics

|                                 |                  |              | (VSS = 0V, |        | 05 C, unless | ounerwis | e specilieu) |  |

|---------------------------------|------------------|--------------|------------|--------|--------------|----------|--------------|--|

| Demension                       | Oursels al       | O an diti an |            | Rating |              | 1.1      | Measuring    |  |

| Parameter                       | Symbol           | Condition    | Min.       | Тур.   | Max.         | Unit     | circuit      |  |

| LLD Low voltage detection level | Vlld             | -            | 4.08       | 4.25   | 4.42         | V        | 1            |  |

| LLD current consumption         | I <sub>LLD</sub> | -            | -          | 10     | -            | nA       | 1            |  |

#### (V<sub>SS</sub> =0V. Ta=-40 to +105°C. unless otherwise specified)

### Successive Approximation Type A/D Converter

|                                     |                   | 0                                                                                |                                                                                  | Rating  |       |        |     |

|-------------------------------------|-------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------|-------|--------|-----|

| Parameter                           | Symbol            | Condition                                                                        | Min.                                                                             | Тур.    | Max.  | - Unit |     |

| Resolution                          | n <sub>AD</sub>   | -                                                                                | -                                                                                | -       | 12    | bit    |     |

| Conversion clock                    | fadclk            | nominal value                                                                    | 32.768                                                                           | -       | 16000 | kHz    |     |

|                                     |                   | f <sub>ADCLK</sub> = 16MHz                                                       | 1.375                                                                            | -       | -     |        |     |

|                                     | -                 | $f_{ADCLK} = 32.768 \text{kHz}$                                                  | -                                                                                | 518.799 | -     |        |     |

| Conversion time                     | t <sub>CONV</sub> | At temperature conversion<br>(f <sub>ADCLK</sub> = 4MHz)                         | 10.5                                                                             | -       | -     | μs     |     |

|                                     |                   | PGA is used<br>(f <sub>ADCLK</sub> = 16MHz)                                      | 8                                                                                | -       | -     |        |     |

| Overall error                       | -                 | $4.5V \le V_{\text{REF}} \le 5.5V$                                               | -6                                                                               | -       | +6    |        |     |

|                                     |                   | f <sub>ADCLK</sub> = 16MHz                                                       | -4                                                                               | -       | +4    |        |     |

|                                     |                   | f <sub>ADCLK</sub> = 8MHz                                                        | -7                                                                               | -       | +7    |        |     |

| Integral non-linearity              |                   | f <sub>ADCLK</sub> ≤ 4MHz                                                        | -8                                                                               | -       | +8    |        |     |

| error                               | INL <sub>AD</sub> | Reference voltage = Internal<br>reference voltage<br>(f <sub>ADCLK</sub> ≤ 8MHz) | -                                                                                | ±64     | -     |        |     |

|                                     |                   | Reference voltage = Internal<br>reference voltage<br>(f <sub>ADCLK</sub> ≤ 4MHz) | -30                                                                              | -       | +30   |        |     |

|                                     |                   | f <sub>ADCLK</sub> = 16MHz                                                       | -3                                                                               | -       | +3    |        |     |

|                                     |                   | f <sub>ADCLK</sub> = 8MHz                                                        | -5                                                                               | -       | +5    |        |     |

| Differential non linearity          |                   | f <sub>ADCLK</sub> ≤ 4MHz                                                        | -7                                                                               | -       | +7    |        |     |

| Differential non-linearity<br>error | DNLad             | DNLad                                                                            | Reference voltage = Internal<br>reference voltage<br>(f <sub>ADCLK</sub> ≤ 8MHz) | -       | ±63   | -      | LSE |

|                                     |                   | Reference voltage = Internal<br>reference voltage<br>(f <sub>ADCLK</sub> ≤ 4MHz) | -29                                                                              | -       | +29   |        |     |

|                                     |                   | f <sub>ADCLK</sub> = 16MHz                                                       | -8                                                                               | -       | +8    |        |     |

| 7 .                                 | 705               | f <sub>ADCLK</sub> = 8MHz                                                        | -8                                                                               | -       | +8    |        |     |

| Zero-scale error                    | ZSE               | f <sub>ADCLK</sub> ≤ 4MHz                                                        | -10                                                                              | -       | +10   |        |     |

|                                     |                   | Reference voltage = Internal<br>reference voltage                                | -80                                                                              | -       | +80   |        |     |

|                                     |                   | f <sub>ADCLK</sub> = 16MHz                                                       | -8                                                                               | -       | +8    |        |     |

| E.U. s s s                          |                   | fadclk = 8MHz                                                                    | -8                                                                               | -       | +8    |        |     |

| Full-scale error                    | FSE               | f <sub>ADCLK</sub> ≤ 4MHz                                                        | -10                                                                              | -       | +10   |        |     |

|                                     | [                 | Reference voltage = Internal<br>reference voltage                                | -80                                                                              | -       | +80   |        |     |

| Internal reference<br>voltage       | VADCREFI          | -                                                                                | 2.45                                                                             | 2.5     | 2.55  | V      |     |

| Temperature conversion              |                   | f <sub>ADCLK</sub> = 4MHz                                                        | -10                                                                              |         | -8    | LSB/   |     |

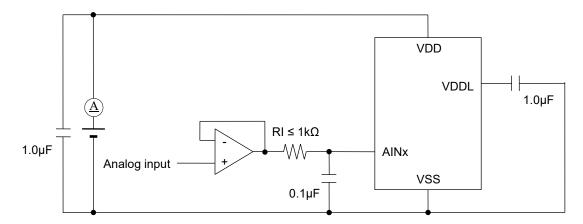

The current flows during the ADC sampling as it takes charging. Make the output impedance of the analog signal source  $1k\Omega$  or smaller. Also, putting  $0.1\mu$ F capacitor on the ADC input pin is recommended for noise reduction.

#### Analog comparator

#### (V<sub>DD</sub>=4.5 to 5.5V, V<sub>SS</sub>=0V, Ta=-40 to +105°C, unless otherwise specified)

| Parameter                                     | Symbol            | Symbol Condition                                  |      | Rating | -                       | Unit   | Measuring |

|-----------------------------------------------|-------------------|---------------------------------------------------|------|--------|-------------------------|--------|-----------|

| i arameter                                    | Oymbol            | Condition                                         | Min. | Тур.   | Max.                    | Onic   | circuit   |

| Comparator<br>in-phase Input<br>voltage range | Vcmr              | -                                                 | 0.1  | -      | V <sub>DD</sub><br>-0.1 | V      |           |

| Comparator<br>Input offset                    | Vcmof             | Ta=+25°C, V <sub>DD</sub> =5.0V                   | -    | ±5     | -                       | mV     |           |

| Comparator reference voltage                  | Vcmrefi           | -                                                 | 0.75 | 0.8    | 0.85                    | $\vee$ | 1         |

| Comparator<br>Hysteresis                      | V <sub>CHYS</sub> | -                                                 | -    | 15     | -                       | mV     |           |

| Comparator                                    |                   | Hysteresis mode OFF (Input amplitude $\pm$ 100mV) | -    | -      | 100                     | 50     |           |

| Operation delay time                          | V <sub>CTS</sub>  | Hysteresis mode ON (Input amplitude $\pm$ 100mV)  | -    | 120    | -                       | ns     |           |

#### **D/A Converter**

(V\_DD=4.5 to 5.5V, V\_SS =0V, Ta=-40 to +105°C, unless otherwise specified)

| Parameter                        | Symbol            | Condition                                            | Rating                    |                 |                           | Unit |

|----------------------------------|-------------------|------------------------------------------------------|---------------------------|-----------------|---------------------------|------|

|                                  | Symbol            | Condition                                            | Min.                      | Тур.            | Max.                      | Unit |

| Resolution                       | NDA               | -                                                    | -                         | -               | 8                         | bit  |

| Conversion cycle                 | tc                | -                                                    | 10                        | -               | -                         | μs   |

| Integral non-linearity error     | INL <sub>DA</sub> | RL=4MΩ                                               | -2                        | -               | 2                         | LSB  |

| Differential non-linearity error | DNL <sub>DA</sub> | RL=4MΩ                                               | -1                        | -               | 1                         |      |

| Output impedance                 | Ro                | -                                                    | 5                         | 10              | 15                        | kΩ   |

| Full-scale error                 | FSE               | $V_{REF}=V_{DD}$                                     | V <sub>DD</sub><br>-0.025 | V <sub>DD</sub> | V <sub>DD</sub><br>+0.025 |      |

|                                  |                   | V <sub>REF</sub> =internal 0.8V<br>reference voltage | 0.725                     | 0.8             | 0.875                     | V    |

| DAC internal reference voltage   | VDACREFI          | -                                                    | 0.75                      | 0.8             | 0.85                      |      |

#### Programable Gain Amp

(V\_DD=4.5 to 5.5V, V\_SS =0V, Ta=-40 to +105°C, unless otherwise specified)

|                      | •        |                                  |        |      |                       | . ,   |  |

|----------------------|----------|----------------------------------|--------|------|-----------------------|-------|--|

| Parameter            | Quinchal | Condition                        | Rating |      |                       | Linit |  |

|                      | Symbol   | Condition                        | Min.   | Тур. | Max.                  | Unit  |  |

| Gain deviation*1     | -        | Gain=4                           | -0.7   | -    | +0.7                  | %     |  |

|                      |          | Gain=8                           | -1.0   | -    | +1.0                  |       |  |

|                      |          | Gain=16                          | -1.5   | -    | +1.5                  |       |  |

|                      |          | Gain=32                          | -2.0   | -    | +2.0                  |       |  |

| Input offset         | VINPGAOS | Ta=+25 °C, V <sub>DD</sub> =5.0V | -      | ±5   | -                     | mV    |  |

| Input voltage range  | VINPGA   | -                                | 0.0    | -    | V <sub>DD</sub> /Gain | V     |  |

| Output voltage range | Voutpga  | -                                | 0.0    | -    | V <sub>DD</sub> -0.5  | V     |  |

| Slew rate            | Vpgasr   | Gain=4, 8                        | 2.5    | -    | -                     |       |  |

|                      |          | Gain=16, 32                      | 1.4    | -    | -                     | V/µs  |  |

<sup>\*1</sup>:VINPGA=0.1\*VDD/Gain to 0.9\*VDD/Gain

#### **Flash Memory**

|                       |                 |                                   |                     |              | (Vss= 0V)        |  |

|-----------------------|-----------------|-----------------------------------|---------------------|--------------|------------------|--|

| Parameter             | Symbol          | Cond                              | dition              | Range        | Unit             |  |

| Operating temperature | TOP             | Data flash memo                   | ory, At write/erase | -40 to +85   |                  |  |

|                       |                 | Flash ROM, At write/erase         |                     | 0 to +40     | °C               |  |

| Operating voltage     | V <sub>DD</sub> | At write/erase                    |                     | +4.5 to +5.5 | V                |  |

| Maximum rewrite count | CEPD            | Data Flash                        |                     | 10000        | <b>t</b> ime = = |  |

|                       | CEPP            | Program Flash                     |                     | 100          | - times          |  |

| Erasing unit          | - E             | Block erasing                     | Program Flash       | 16K          |                  |  |

|                       |                 |                                   | Data Flash          | all area     |                  |  |

|                       |                 |                                   | Program Flash       | 1K           | Byte             |  |

|                       | -               | Sector erasing                    | Data Flash          | 128          |                  |  |