Dear customer

ROHM Co., Ltd. ("ROHM"), on the 1st day of April, 2024, has absorbed into merger with 100%-owned subsidiary of LAPIS Technology Co., Ltd.

Therefore, all references to "LAPIS Technology Co., Ltd.", "LAPIS Technology" and/or "LAPIS" in this document shall be replaced with "ROHM Co., Ltd." Furthermore, there are no changes to the documents relating to our products other than the company name, the company trademark, logo, etc.

Thank you for your understanding.

ROHM Co., Ltd. April 1, 2024

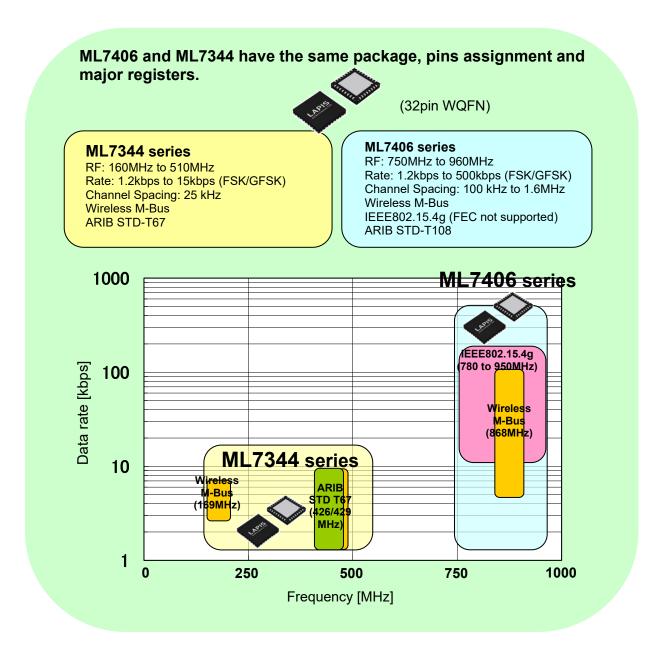

# **ML7406**

ML7406 is a low power consumption sub GHz RF transceiver, which includes RF, IF, MODEM, baseband processor, HOST interface. ML7406 can be used for mainly ISM(Industrial, Scientific and Medical) or SRD(Short Range Device). (EN13757-4:2011: Wireless M-BUS) packet format can be processed by on-chip hardware.

•Product Name ML7406TGD

•Application Remote control Home, Building Security Sensor Network Smart Meters

### Features

- Supported standard

- ETSI EN 300 220 (Europe)

- EN 13757-4:2011 (Wireless M-BUS)

- IEEE802.15.4g

- ARIB STD T108 (Japan)

- RF frequency: 750MHz to 960MHz

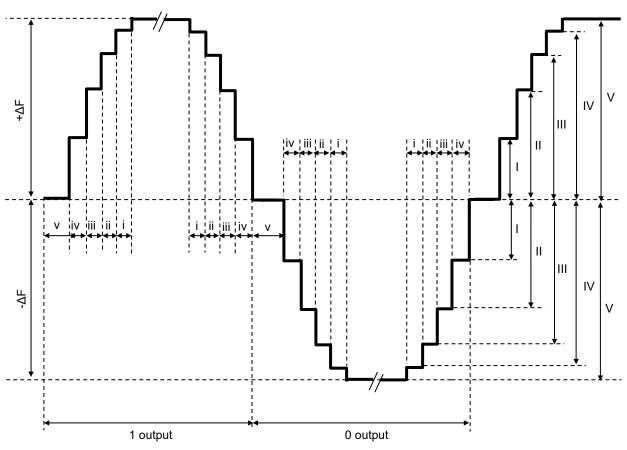

- Realized high resolution modulation by using fractional N type PLL direct GFSK modulation

- Modulation: GFSK/GMSK/FSK/MSK (MSK is a case that FSK modulation index = 0.5)

- Data transmission rate: 1.2 to 500 kbps

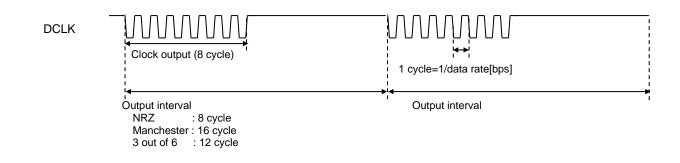

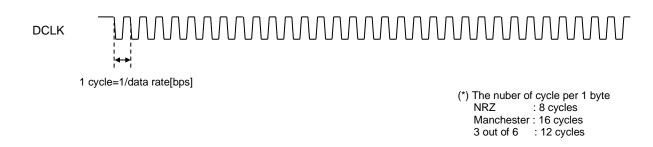

- Data encoding/decoding by HW: NRZ, Manchester, 3 out of 6

- Data whitening by HW

- Programmable frequency channel filters

- Programmable frequency deviation function

- TX/RX data inverse function

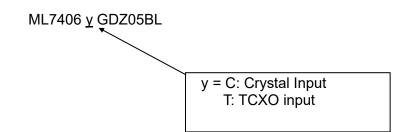

- 26 MHz oscillator circuits version (ML7406C)

- TCXO (26 MHz) direct input version (ML7406T)

- Oscillator capacitance fine tuning function

- On chip low speed RC oscillation circuit

- Low speed clock adjustment function

- frequency fine tuning function (using fractional N type PLL)

- Synchronous serial peripheral interface(SPI)

- On-chip TX PA. (20 mW / 10 mW / 1 mW selectable)

- TX power fine tuning function (±0.2 dB)

- TX power automatic ramping control

- External TX PA control function

- RSSI indicator and threshold judgment function

- High speed carrier checking function

- AFC function (IF frequency automatic adjustment by Fractional N type PLL adjustment)

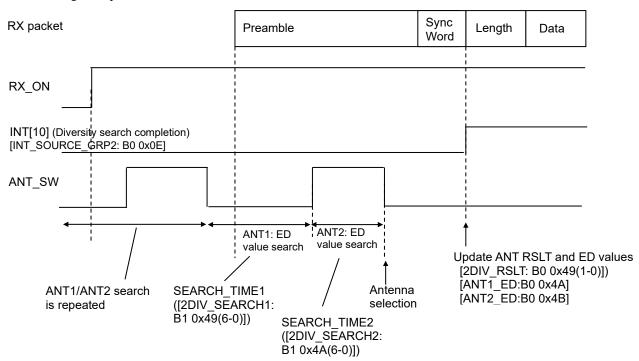

- Antenna diversity function

- Automatic Wake UP, auto SLEEP function (external RTC input or internal RC oscillator selectable)

- General purpose timer (2ch)

- Test pattern generator (PN9,CW, 01 PATTERN, ALL"1", ALL"0" OUTPUT)

- Packet mode function

- Wireless M-BUS packet format (Format A/B)

- General purpose packet format (Format C)

- Max.255 byte (Format A/B), 204t byte (Format C)

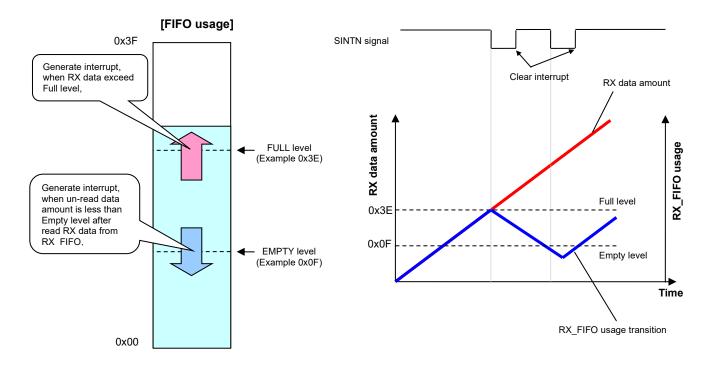

- TX FIFO (64 byte), RX FIFO (64 byte)

- RX Preamble pattern detection (Max.4 byte)

- Automatic TX preamble length generation (Max.length 16383 byte)

- SyncWord setting function (Max. 4byte × 2 type)

- Program CRC function (CRC32/CRC16/CRC8 selectable, fully programmable polynomial)

- Wireless M-BUS field checking function (C-field/M-field/A-field can be detected automatically) (Note) Proprietary packet format is possible depending on setting

- Supply voltage

- 1.8 V to 3.6 V (TX power 1 mW mode)

- 2.3 V to 3.6 V (TX power 10 mW mode)

- 2.6 V to 3.6 V (TX power 20 mW mode)

- Operational temperature -40 °C to 85 °C

#### • Current consumption (868 MHz)

| Deep sleep mode | 0.1 μA (Typ.)  |                           |

|-----------------|----------------|---------------------------|

| Sleep mode2     | 0.56 µA (Typ.) | (retains registers, FIFO) |

| Idle mode       | 1.4 mA (Typ.)  |                           |

| TX 20 mW        | 34 mA (Typ.)   |                           |

| 10 mW           | 24 mA (Typ.)   |                           |

| 1 mW            | 13 mA (Typ.)   |                           |

| RX              | 15 mA (Typ.)   | (@100kbps)                |

|                 |                |                           |

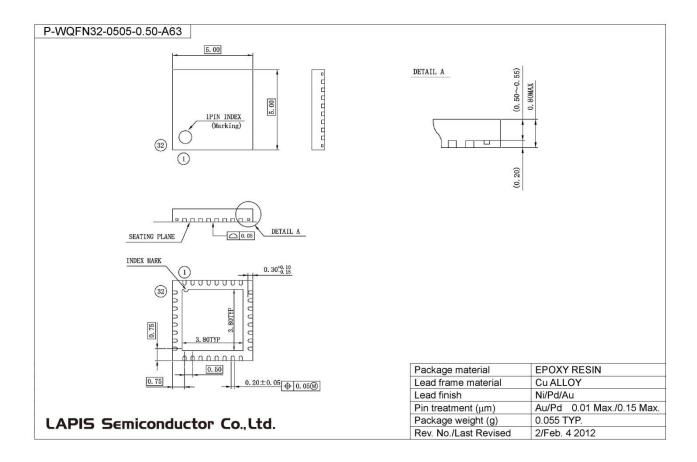

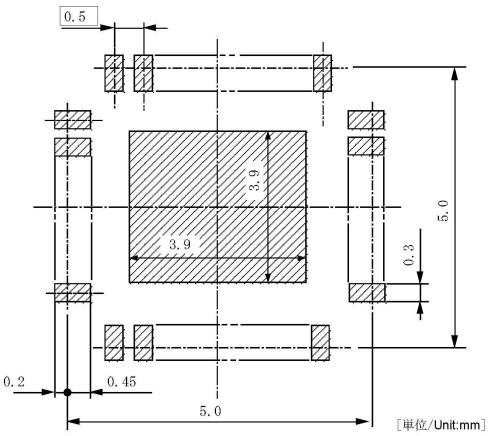

#### • Package

32pins WQFN (5mm  $\times$  5mm) P-WQFN32-0505-0.50 Lead free, RoHS compliance

### ■Product Name

## Description Convention

Numbers description

'0xnn' indicates hexa decimal. '0bnn' indicates binary.

Example: 0x11= 17(decimal), 0b11= 3(decimal)

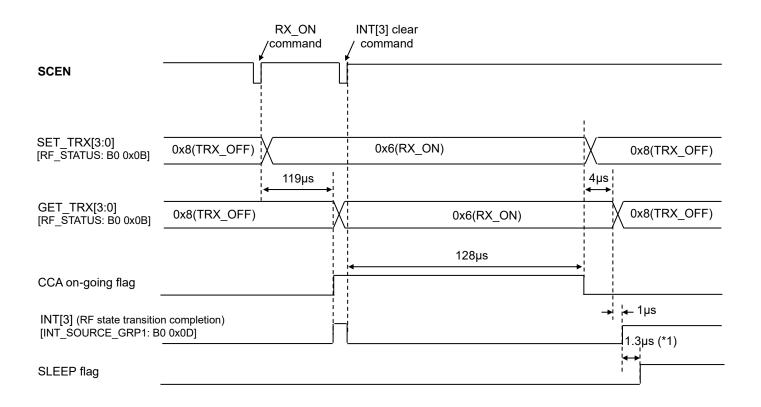

2) Registers description [<register name>: B<Bank No> <register address>] register

Example: [RF\_STATUS: B0 0x0B] register Register name: RF\_STATUS Bank No: 0 Register address: 0x0B

Example: SET\_TRX[3:0] ([RF\_STATUS: B0 0x0B(3-0)])

Bit name: SET\_TRX Register name: RF\_STATUS Bank No: 0 Register address: 0x0B Bit location: bit3 to bit0

4) In this document

**"TX"** stands for transmittion. **"RX"** stands for reception.

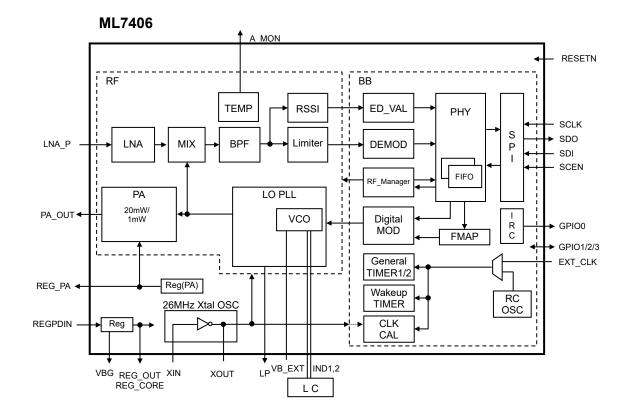

## ■Block Diagram

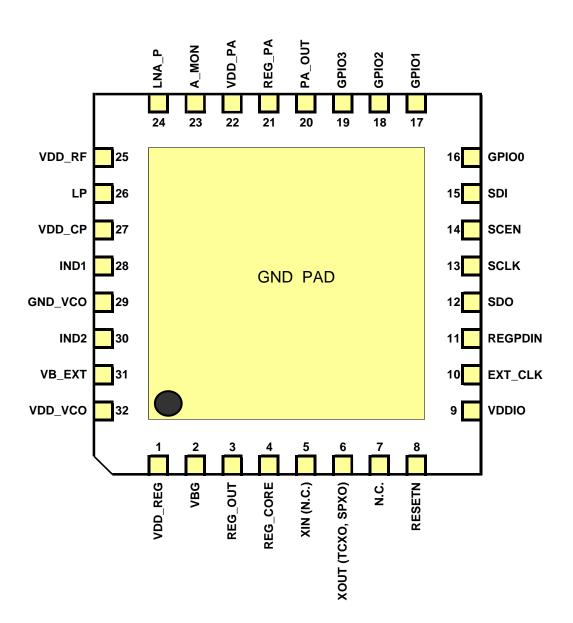

### ■PIN Configuration

32 pin WQFN

### ■PIN Definitions

#### Definiion of Symbols

|       |   | I/O                  |      |   | Reset state    |    |   | Active Level  |

|-------|---|----------------------|------|---|----------------|----|---|---------------|

|       | : | Digital input        | 1    | : | Digital Input  | Н  | : | High Level    |

| 0     | : | Digital output       | 0    | : | Digital Ouput  | L  | : | Low Level     |

| ls    | : | Shmidt Trigger input | Hi-Z | : | High-Impedance | OD | : | Open Drain    |

| 10    | : | Digital input/output |      |   |                | Р  | : | Positive Edge |

| A     | : | Analog input         |      |   |                | Ν  | : | Negative Edge |

| OA    | : | Analog output 1      |      |   |                |    |   |               |

| Оан   | : | Analog output 2      |      |   |                |    |   |               |

| IOA   | : | Analog input/output  |      |   |                |    |   |               |

| IRF   | : | RF input             |      |   |                |    |   |               |

| Orf   | : | RF output            |      |   |                |    |   |               |

| Vddio | : | I/O power supply     |      |   |                |    |   |               |

| Vddrf | : | RF power supply      |      |   |                |    |   |               |

| GND   | : | Ground               |      |   |                |    |   |               |

### •RF and Analog pins

| Pin | Pin name | Reset<br>state | I/O             | Active<br>Level | function                                     |

|-----|----------|----------------|-----------------|-----------------|----------------------------------------------|

| 20  | PA_OUT   | -              | $O_{RF}$        | -               | RF antenna output                            |

| 23  | A_MON    | -              | OA              | -               | Temperature information output (*1)          |

| 24  | LNA_P    | -              | lA              | -               | RF antenna input                             |

| 26  | LP       | _              | IO <sub>A</sub> | -               | Pin for loop filter                          |

| 28  | IND1     | -              | IO <sub>A</sub> | -               | Pin for VCO tankl inductor                   |

| 30  | IND2     | -              | IO <sub>A</sub> | -               | Pin for VCO tank inductor                    |

| 31  | VB_EXT   | -              | ΙΟΑ             | -               | Pin for smothing capacitor for internal bias |

\*1 This pin can be configured by [MON\_CTRL:B0 0x4D] register, no signal assigned as default setting.

### •SPI Interface pins

| Pin | Pin name | Reset<br>state | I/O | Active<br>Level | function                                   |

|-----|----------|----------------|-----|-----------------|--------------------------------------------|

| 12  | SDO      | Hi-Z           | 0   | H or L          | SPI data output or DCLK (*1)               |

| 13  | SCLK     | Hi-Z           | IS  | P or N          | SPI clock input                            |

| 14  | SCEN     | Hi-Z           | IS  | L               | SPI chip enable<br>L: enable<br>H: disable |

| 15  | SDI      | Hi-Z           | IS  | H or L          | SPI data input or DIO (*1)                 |

\*1 Please refer to "DIO function"

#### •Regulator pins

| Pin | Pin name | Reset<br>state | I/O             | Active<br>Level | function                                                                                      |

|-----|----------|----------------|-----------------|-----------------|-----------------------------------------------------------------------------------------------|

| 2   | VBG      | -              | Оан             | -               | Pin for decouppling capacitor                                                                 |

| 3   | REG_OUT  | -              | Оан             | -               | Requlator1 ouput (typ. 1.5V)                                                                  |

| 4   | REG_CORE | -              | OA              | -               | Requlator2 ouput (typ. 1.5V)                                                                  |

| 11  | REGPDIN  | I              | I               | н               | Power down control pin for regulator<br>Fix to 'L' for nomal use. "H" is for deep sleep mode. |

| 21  | REG_PA   | -              | O <sub>AH</sub> | -               | Regulator output for PA block                                                                 |

#### Miscellaneous pins

| Pin | Pin name          | Reset<br>state | I/O                                   | Active<br>Level | function                                                                       |

|-----|-------------------|----------------|---------------------------------------|-----------------|--------------------------------------------------------------------------------|

| 5   | XIN<br>N.C. (*2)  | <br>-          | l <sub>A</sub><br>–                   | P or N<br>-     | 26MHz crystal pin1<br>(Note) In case of TCXO, it must be open.                 |

| 6   | XOUT<br>TCXO (*2) | 0              | O <sub>A</sub><br>I <sub>A</sub><br>I | P or N          | 26MHz crystal pin 2 or TCXO input                                              |

| 8   | RESETN            | Ι              | ls                                    | L               | Reset<br>L: Hardware reset enable (Forcing reset state)<br>H: Normal operation |

| 10  | EXT_CLK           | Hi-Z           | Ю                                     | P or N          | Digital I/O (*3)<br>Reset state: External RTC (32kHz) input.                   |

| 16  | GPIO0             | Hi-Z           | IO<br>or<br>OD(*1)                    | H or L          | Digital GPIO (*4)<br>Reset state: interrupt indication signal output           |

| 17  | GPIO1             | Hi-Z           | IO<br>or<br>OD(*1)                    | H or L          | Digital GPIO (*5)<br>Reset state: clock output                                 |

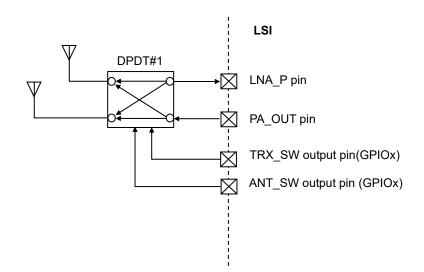

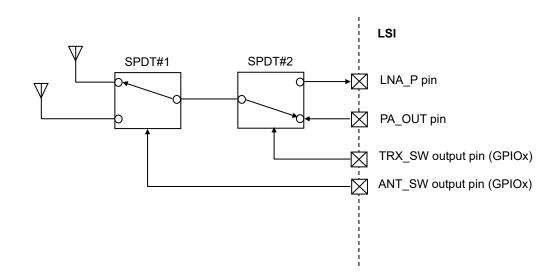

| 18  | ANT_SW/<br>GPIO2  | Hi-Z           | IO<br>or<br>OD(*1)                    | H or L          | Digital GPIO (*6)<br>Reset state: Antenna diversity selection control signal   |

| 19  | TRX_SW/<br>GPIO3  | Hi-Z           | IO<br>or<br>OD(*1)                    | H or L          | Digital GPIO (*7)<br>Reset state: TX –RX selection signal control              |

(Note) \*1 OD is open drain output.

\*2 The following pin names are different depend on products.

| Pin No. | ML7406C | ML7406T |  |  |

|---------|---------|---------|--|--|

| 5       | XIN     | N.C.    |  |  |

| 6       | XOUT    | тсхо    |  |  |

(Note)

In case of using TCXOset TCXO\_EN([CLK\_SET2: B0 0x03(6)])=0b1. Please make sure only one of the register TCXO\_EN, XTAL\_EN([CLK\_SET2: B0 0x03(4)]) is set to 0b1.

\*3 Please refer to [EXTCLK\_CTR: B0 0x52] register.

\*4 Please refer to [GPIO0\_CTRL: B0 0x4E] register

\*5 Please refer to [GPIO1\_CTRL: B0 0x4F] register. In case of ML7406T, clock doesn't output until TCXO\_EN is set to 0b1.

\*6 Please refer to [GPIO2\_CTRL: B0 0x50] register

\*7 Please refer to [GPIO3\_CTRL: B0 0x51] register

#### •Power supply/GND pins

| Pin | Pin name | Reset<br>state | I/O               | Active<br>Level | function                                                                       |

|-----|----------|----------------|-------------------|-----------------|--------------------------------------------------------------------------------|

| 1   | VDD_REG  | -              | Vddio             | -               | Power supply pin for Regulator<br>(input voltage: 1.8V to 3.3V)                |

| 9   | VDDIO    | -              | Vddio             | -               | Power supply for digital I/O<br>(input voltage: 1.8 to 3.6V)                   |

| 22  | VDD_PA   | _              | Vddio             | _               | Power supply for PA block<br>(input voltage: 18 to 3.6V, depending on TX mode) |

| 25  | VDD_RF   | -              | Vddrf             | -               | Power supply for RF blocks<br>(REG-OUT is connected, typ.1.5V)                 |

| 27  | VDD_CP   | -              | Vddrf             | -               | Power supply for charge pump<br>(REG-OUT is connected, typ.1.5V)               |

| 32  | VDD_VCO  | _              | V <sub>DDRF</sub> | _               | Power supply for VCO<br>(REG_OUT is connected, typ.1.5V)                       |

| 29  | GND_VCO  | -              | GND               | _               | GND for VCO                                                                    |

#### •Unused pins treatment

Unused pins treatments are as follows:

|          | Unused pins treatment |                       |  |  |  |  |  |  |  |

|----------|-----------------------|-----------------------|--|--|--|--|--|--|--|

| Pin name | Pins number           | Recommended treatment |  |  |  |  |  |  |  |

| N.C.     | 5                     | Open                  |  |  |  |  |  |  |  |

| N.C.     | 7                     | GND or Open           |  |  |  |  |  |  |  |

| EXT_CLK  | 10                    | GND                   |  |  |  |  |  |  |  |

| A_MON    | 23                    | GND                   |  |  |  |  |  |  |  |

| GPIO0    | 16                    | Open                  |  |  |  |  |  |  |  |

| GPIO1    | 17                    | Open                  |  |  |  |  |  |  |  |

| GPIO2    | 18                    | Open                  |  |  |  |  |  |  |  |

| GPIO3    | 19                    | Open                  |  |  |  |  |  |  |  |

(Note)

- \*1 If input pins are high-impedence state and leave open, excess current could be drawn. Care must be taken that unused input pins and unused I/O pins should not be left open.

- \*2 Upon reset, GPIO1 pin is CLK\_OUT function. If this function is not used, the clock must to be disabled by setting 0b000 to GPIO1\_IO\_CFG[2:0] ([GPIO1\_CTRL: B0 0x4F (2-0)]). If this pin is left open while outputing clock signal, it may affect RX sensitivity.

### ■Electrical Characteristics

### •Absolute Maximum Rating

Ta=-40°C to  $+85^{\circ}$ C and GND=0V is the typical condition if not defined specific condition.

| item                     | symbol            | condition           | Rating       | unit |

|--------------------------|-------------------|---------------------|--------------|------|

| I/O Power supply         | V <sub>DDIO</sub> |                     | -0.3 to +4.6 | V    |

| RF Power supply          | V <sub>DDRF</sub> |                     | -0.3 to +2.0 | V    |

| RF input power           | P <sub>RFI</sub>  | Antenna input in RX | 0            | dBm  |

| RF output Voltage        | V <sub>RFO</sub>  | PA_OUT(#20)         | -0.3 to +4.6 | V    |

| Voltage on Analog Pins 1 | V <sub>A</sub>    |                     | -0.3 to +2.0 | V    |

| Voltage on Analog Pins 2 | V <sub>AH</sub>   |                     | -1.0 to +4.6 | V    |

| Voltage on Digital Pins  | VD                |                     | -0.3 to +4.6 | V    |

| Digital Input Current    | IDI               |                     | -10 to +10   | mA   |

| Digital Output Current   | IDO               |                     | -8 to +8     | mA   |

| Power Dissipation        | Pd                | Ta= +25°C           | 1.2          | W    |

| Storage Temperature      | Tstg              | -                   | -55 to +150  | °C   |

| Item                                           | Symbol | Condition                           | Min   | Тур | Max  | Unit |

|------------------------------------------------|--------|-------------------------------------|-------|-----|------|------|

| Power Supply (I/O)                             | VDDIO  | VDDIO pin and<br>VDD_REG pin (*1)   | 1.8   | 3.3 | 3.6  | V    |

|                                                |        | VDD_PA pin<br>TX power 1mW mode     | 1.8   | 3.3 | 3.6  | V    |

| Power Supply (PA)                              | VDDPA  | VDD_PA pin<br>TX Power 10mW mode    | 2.3   | 3.3 | 3.6  | V    |

|                                                |        | VDD_PA pin<br>TX Power 20mW mode    | 2.6   | 3.3 | 3.6  | V    |

| Operational Temperature                        | Та     | -                                   | -40   | +25 | +85  | °C   |

| Digital Input Rising Time                      | TIR    | Digital Input pins (*1)             | -     | -   | 20   | ns   |

| Digital Input Falling Time                     | TIF    | Digital Input pins (*1)             | -     | -   | 20   | ns   |

| Digital Output Load                            | CDL    | All Digital Output pins             | -     | -   | 20   | pF   |

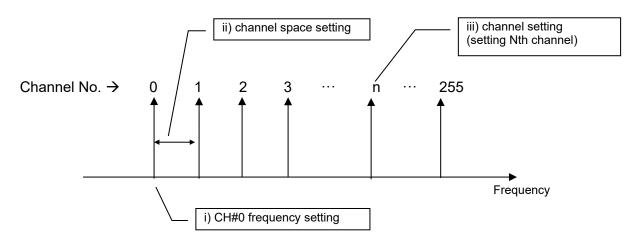

| Master Clock Frequency<br>(XIN,XOUT,TCXO pins) | FMCK1  | -                                   | (*2)  | 26  | (*2) | MHz  |

| Master Clock Accuracy (*2)                     | ACMCK1 | -                                   | -85   | -   | +85  | ppm  |

| TCXO Input Voltage                             | Vтсхо  | DC Cutoff<br>TCXO Optionis selected | 0.8   | -   | 1.5  | Vpp  |

| SPI Clock Input Frequency                      | FSCLK  | SCLK pin                            | 0.032 | 2   | 16   | MHz  |

| SPI Clock Input<br>Duty Cycle Ratio            | DSCLK  | SCLK pin                            | 45    | 50  | 55   | %    |

| RF Frequency                                   | FRF    |                                     | 750   | -   | 960  | MHz  |

\*1 In the pin description, I or Is are specified as the I/O.

\*2 Indicating frequency deviation during TX-RX operation. In order to support various standards, please apply the frequency accuracy for each standard to meet the requirements.

| Specification         | Required accuracy |  |  |

|-----------------------|-------------------|--|--|

| Wireless M-Bus S mode | ±60 ppm(Meter)    |  |  |

| Wireless M-Bus S mode | ±25 ppm(Other)    |  |  |

| Wireless M-Bus T mode | ±60 ppm(Meter)    |  |  |

| Wireless M-Bus T mode | ±25 ppm(Other)    |  |  |

| Wireless M-Bus C mode | ±25 ppm           |  |  |

| ARIB STD-T108         | ±20 ppm           |  |  |

(Note) Below values are not taking individual LSI variations into consideration.

#### •Power Consumption

| Item                            | Synbol            | Condition                                                       | Min | Тур (*2)      | Max (*5)    | Unit |

|---------------------------------|-------------------|-----------------------------------------------------------------|-----|---------------|-------------|------|

| IDD                             | IDD_DSLP          | Deep Sleep mode<br>(Not retaining Registers, all function halt) | -   | 0.1           | 9<br>(0.8)  | μΑ   |

|                                 | IDD_SLP2          | Sleep mode 2 (*3)                                               | -   | 0.56          | 20<br>(3.2) | μΑ   |

| Power Consumption IDD_SLP3 (*1) | Sleep mode 3 (*3) | -                                                               | 0.7 | 20.2<br>(3.2) | μΑ          |      |

|                                 | IDD_SLP4          | Sleep mode 4 (*3)                                               | -   | 2.5           | 22<br>(5.1) | μA   |

|                                 | IDD_IDLE          | Idle state                                                      | -   | 1.4           | -           | mA   |

|                                 | IDD_RX            | RF RX state (*4)                                                | -   | 15            | -           | mA   |

|                                 | IDD_TX1           | RF TX state (1mW)(*4)                                           | -   | 13            | -           | mA   |

|                                 | IDD_TX10          | RF TX state (10mW) (*4)                                         | -   | 24            | -           | mA   |

|                                 | IDD_TX20          | RF TX state (20mW) (*4)                                         | -   | 34            | I           | mA   |

\*1 Power consumption is sum of current consumption of all power supply pins.

\*2 "Typ" value is centre value under condition of VDDIO=3.3V, 25°C.

\*3 The definition od each sleep stae is shown in following table.

| State.       | Register | FIFO               | RC Osc.<br>(32kHz) | Low clock timer |

|--------------|----------|--------------------|--------------------|-----------------|

| Sleep mode 1 | r        | ML7406 does not su | pport Sleep mode   | 1               |

| Sleep mode 2 | Retain   | Retain             | OFF                | -               |

| Sleep mode 3 | Retain   | Retain             | External Input     | ON              |

| Sleep mode 4 | Retain   | Retain             | ON                 | ON              |

\*4 Current consumption when RF Frequency is 868MHz.

\*5 () means maximum value (reference value) under condition of 25°C.

(Note)

It is inhibited the trnasiton from sleep modes to deep sleep mode in one power supply cycle.

### •DC characteristics

| Item                                   | Symbol  | Condition                                                                    | Min          | Тур | Max          | Unit |

|----------------------------------------|---------|------------------------------------------------------------------------------|--------------|-----|--------------|------|

| Valtana lunut Link                     | VIH1    | Digital Input pins                                                           | VDDIO * 0.75 | -   | VDDIO        | V    |

| Voltage Input High                     | VIH2    | XIN pin                                                                      | 1.35         | -   | 1.5          | V    |

|                                        | VIL1    | Digital Input pins                                                           | 0            | -   | VDDIO * 0.18 | V    |

| Voltage Input Low                      | VIL2    | XIN pin                                                                      | 0            | -   | 0.15         | V    |

| Schmit Trigger<br>Threshold High Level | VT+     | RESETN pin<br>SDI, SCLK, SCEN pins<br>EXT_CLK pin                            | -            | 1.2 | VDDIO * 0.75 | v    |

| Schmit Trigger<br>Threshold Low Level  | VT-     | RESETN pin<br>SDI, SCLK, SCEN pins<br>EXT_CLK pin                            | VDDIO * 0.18 | 0.8 | -            | v    |

|                                        | liH1    | Digital input pins                                                           | -1           | -   | 1            | μA   |

| Innut Lookens Cument                   | lih2    | XIN pin                                                                      | -0.3         | -   | 0.3          | μA   |

| Input Leakage Current                  | liL1    | Digital input pins                                                           | -1           | -   | 1            | μA   |

|                                        | lil2    | XIN pin                                                                      | -0.3         | -   | 0.3          | μΑ   |

| Tri-state Output                       | Iоzн    | EXT_CLK, GPIO0-3 pins,                                                       | -1           | -   | 1            | μA   |

| Leakage Current                        | IOZL    | EXT_CLK, GPIO0-3 pins,                                                       | -1           | -   | 1            | μΑ   |

| Voltage Output Level H                 | Vон     | IOH=-4mA                                                                     | VDDIO * 0.8  | -   | VDDIO        | V    |

| Voltage Output Level L                 | VOL     | IOL=4mA                                                                      | 0            | -   | 0.3          | V    |

| Regulator Output                       | REGMAIN | REG_CORE pin, REG_OUT pin,<br>applicable to all states except SLEEP<br>state | 1.4          | 1.5 | 1.6          | V    |

| Voltage                                | REGSUB  | REG_CORE pin<br>Sleep state                                                  | 0.95         | 1.3 | 1.65         | V    |

|                                        | CIN     | Input pins                                                                   | -            | 6   | -            | pF   |

|                                        | Соит    | Output pins                                                                  | -            | 9   | -            | pF   |

| Pin Capacitance                        | CRFIO   | RF inout pins                                                                | -            | 9   | -            | pF   |

|                                        | CAI     | Analog input pins                                                            | -            | 9   | -            | pF   |

#### •RF characteristics

| Modulated Data Rate | : | 1.2kbps to 500kbps |

|---------------------|---|--------------------|

| Modulation fomats   | : | 2GFSK/2FSK         |

| Channel spacing     | : | 60kHz to 1.6MHz    |

The measurement point is at antenna end specified in the recommended circuits.

#### [RF Frequency]

| Item         | Condition          | Min | Тур | Max | Unit |

|--------------|--------------------|-----|-----|-----|------|

| RF frequency | LNA_P, PA_OUT pins | 750 | -   | 960 | MHz  |

(Note)

1)Frequency range can be adjusted from 750MHz to 960MHz by changing external components parameters.

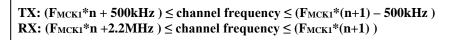

2)If channel frequency is similar frequency range of Integral multiple of the master clock, it may not be able to use this mode. Please refer to the "channel frequency setting" section for detail.

#### [TX Characteristics]

| Item                                          | Condition                 | Min   | Тур | Max | Unit |

|-----------------------------------------------|---------------------------|-------|-----|-----|------|

|                                               | 20mW(13dBm) mode          | 9     | 13  | 15  | dBm  |

| TX power                                      | 10mW(10dBm) mode          | 6     | 10  | 12  | dBm  |

|                                               | 1mW(0dBm) mode            | -4    | 0   | 4   | dBm  |

| Frequency deviation setting range [Fdev] (*1) |                           | 0.025 | -   | 400 | kHz  |

| Spurious emission level(10mW mode)            | The sencod order harmonic | -     | -35 | -30 | dBm  |

|                                               | The third order harmonic  | _     | -35 | -30 | dBm  |

\*1. Depending on the frequency, max.frequency may be changed.

#### [RX Characteristics]

| Item                                         | Condition              | Min | Тур  | Max  | Unit |

|----------------------------------------------|------------------------|-----|------|------|------|

| Minimum RX sensitity                         | 32.768kbps mode        | -   | -108 | -    | dBm  |

| BER<0.1%                                     | 100kbps mode           | -   | -106 | -100 | dBm  |

| Maximum RX input level                       | BER<0.1%               | 0   | _    | _    | dBm  |

| Minimum energy detection level<br>(ED value) |                        | _   | -107 | -100 | dBm  |

| Energy detection range                       | Dynamic range          | 60  | 70   | _    | dB   |

| Energy detection accuracy                    |                        | -6  | -    | +6   | dB   |

| Secondary emission level                     | Local frequency        | -   | -63  | -57  | dBm  |

|                                              | Frequency over 1000MHz | -   | -57  | -47  | dBm  |

#### •RC oscillation circuits characteristics

ML7406 has on-chip low speed RC clock generator. For details, please refer to "LSI state transition control/SLEEP setting" section.

| Item                        | Symbol | Condition | Min | Тур | Max | Unit |

|-----------------------------|--------|-----------|-----|-----|-----|------|

| RCOSC oscillation frequency | FRCOSC |           | -   | 44  | -   | kHz  |

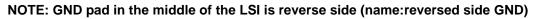

#### •SPI interface characteristics

| Item                  | Symbol  | Condition   | Min   | Тур | Max | Unit |

|-----------------------|---------|-------------|-------|-----|-----|------|

| SCLK clock frequency  | FSCLK   |             | 0.032 | 2   | 16  | MHz  |

| SCEN input setup time | TSCENSU |             | 30    | -   | -   | ns   |

| SCEN input hold time  | TSCENH  |             | 30    | -   | -   | ns   |

| SCLK high pulse width | TSCLKH  | Load        | 28    | -   | -   | ns   |

| SCLK low pulse width  | TSCLKL  | capacitance | 28    | -   | -   | ns   |

| SDI input setup time  | TSDISU  | CL=20pF     | 5     | -   | -   | ns   |

| SDI input hold time   | TSDIH   |             | 15    | -   | -   | ns   |

| SCEN negate period    | TSCENNI |             | 200   | -   | -   | ns   |

| SDO output delay time | TSDODLY |             | -     | -   | 22  | ns   |

(Note) All measurement condition for the timings are VDDIO \* 20% level and VDDIO \* 80% level.

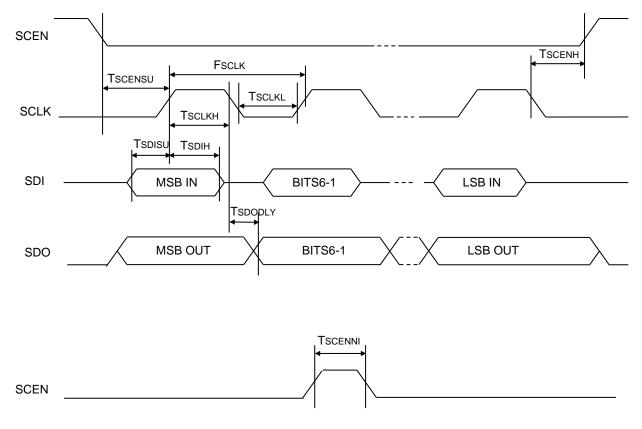

#### •DIO iInterface characteristics

| Item                                 | Symbol   | Condition                   | Min                              | Тур | Max                              | Unit |

|--------------------------------------|----------|-----------------------------|----------------------------------|-----|----------------------------------|------|

| DIO input setup time                 | TDISU    | -                           | 1                                | -   | -                                | µsec |

| DIO input hold time                  | TDIH     |                             | 0                                | -   | -                                | ns   |

| DIO output hold time                 | ТДОН     |                             | 20                               | -   | -                                | ns   |

| DCLK frequency accuracy (*1)<br>(TX) | FDCLK_TX | Load capacitance<br>CL=20pF | -clock<br>frequency<br>deviation | _   | +clock<br>frequency<br>deviation | kHz  |

| DCLK frequency accuracy (*2)<br>(RX) | FDCLK_RX |                             | -30                              | -   | +30                              | %    |

| DCLK output duty ratio<br>(TX)       | DDCLK_TX |                             | 45                               | _   | 55                               | %    |

| DCLKoutput duty ratio<br>(RX)        | DDCLK_RX |                             | 30                               | -   | 70                               | %    |

\*1 If there is no decimal point generated in the TX data rate setting caluclation, (see [TX\_RATE\_H: B1 0x02]), master clock frequency deviation is max.and min.of TX DCLK frequency.

\*2 Max.and min.of RX DCLK frequency indicates jitter of recovered clock from RX signal upon synchronization.

(Note)

All timing measurement conditions are VDDIO \* 20% and VDDIO \* 80%.

#### ML7406

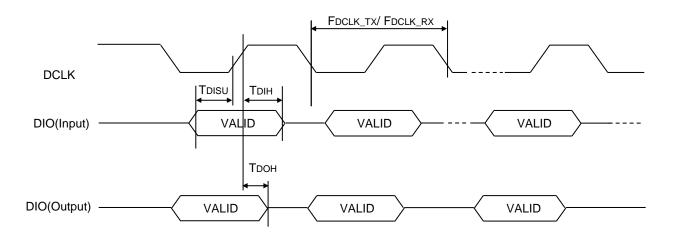

#### •Power-on characteristics

| Item         | Symbol | Condition                          | Min | Тур | Max | Unit |

|--------------|--------|------------------------------------|-----|-----|-----|------|

| Power-ontime | TPWON  | Power on state<br>(all power pins) | -   | -   | 5   | ms   |

(Note)

All timing measurement conditions are VDDIO \* 20% and VDDIO \* 80%.

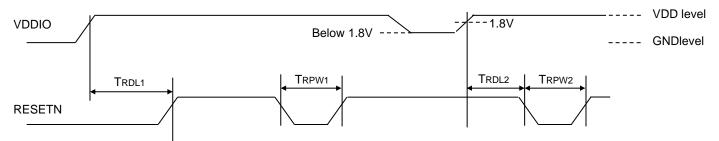

#### •Reset characteristics

| Item                                                  | Symbol | Condition                        | Min | Тур | Max | Unit |

|-------------------------------------------------------|--------|----------------------------------|-----|-----|-----|------|

| RESETN release delay time (power on period)           | TRDL1  | All power pins<br>After Power On | 150 | _   | _   | ms   |

| RESETN pulse period<br>(start-up from VDDIO=0V)       | TRPW1  |                                  | 200 | -   | -   | ns   |

| RESETN pulse period 2(*1)<br>(start-up from VDDIO≠0V) | TRPW2  | After VDDIO>1.8V                 | 150 | _   | -   | ms   |

| RESETN input delay time                               | TRDL2  |                                  | 1   | _   | _   | μs   |

(Note)

All timing measurement conditions are VDDIO \* 20% level and VDDIO \* 80% level.

(\*1) When starting from VDDIO≠0V, a pulse must be sent to VRESETN after DDIO exceeds 1.8V.

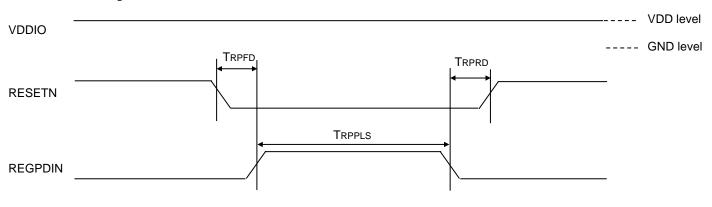

#### •Deep Sleep mode characteristics

| Item                           | Symbol Condition |           | Min | Тур | Max | Unit |

|--------------------------------|------------------|-----------|-----|-----|-----|------|

| REGPDIN rising edge delay time | TRPFD            | VDDIO="H" | 0   | -   | -   | μs   |

| REGPDIN assert time            | TRPPLS           | VDDIO="H" | 1.2 | -   | -   | ms   |

| REGPDIN release delay time     | TRPRD            | VDDIO="H" | 1.5 | -   | -   | ms   |

(Note)

All timing measurement conditions are VDDIO \* 20% and VDDIO \* 80%.

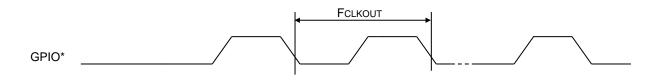

#### •Clock output characteristics

ML7406 has clock output function. Clock output can be controlled by DMON\_SET([MON\_CTRL: B0 0x4D(3-0)]) and [GPIOn\_CTRL: B0 0x4E-0x51] registers (n=0 to 3). Upon reset, clock is output through GPIO1 pin.

| Item                         | Symbol  | Co                             | ndition                     | Min | Тур  | Max | Unit |

|------------------------------|---------|--------------------------------|-----------------------------|-----|------|-----|------|

| Clock output frequency       | FCLKOUT |                                |                             |     | 3.33 | 26  | MHz  |

|                              |         | Load<br>capacitance<br>CL=20pF | 8 66MHz                     |     | -    | 67  | %    |

| Clock output duty ratio (*1) |         |                                | All conditions except above | 48  | 50   | 52  | %    |

\*1 Duty cycle is High:Low = 1:2, only when 8.66MHz is used. Please refer to [CLK\_OUT: B1 0x01] register.

#### (Note)

All timing measurement conditions are VDDIO \* 20% and VDDIO \* 80%.

### Functional Description

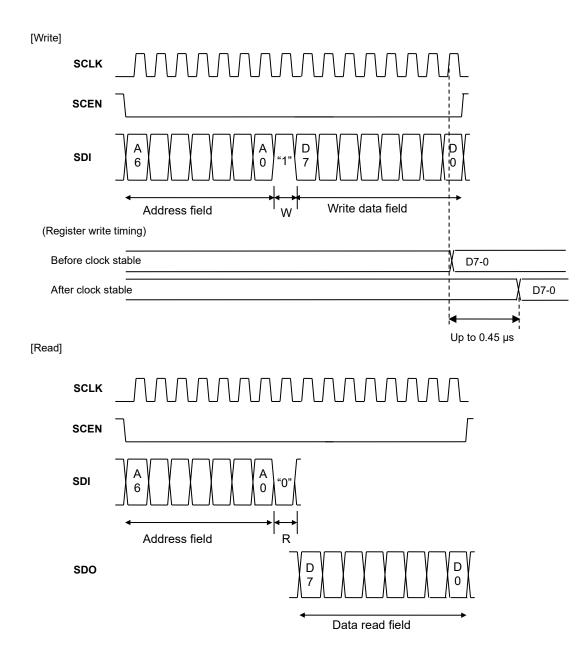

#### •Host Interface

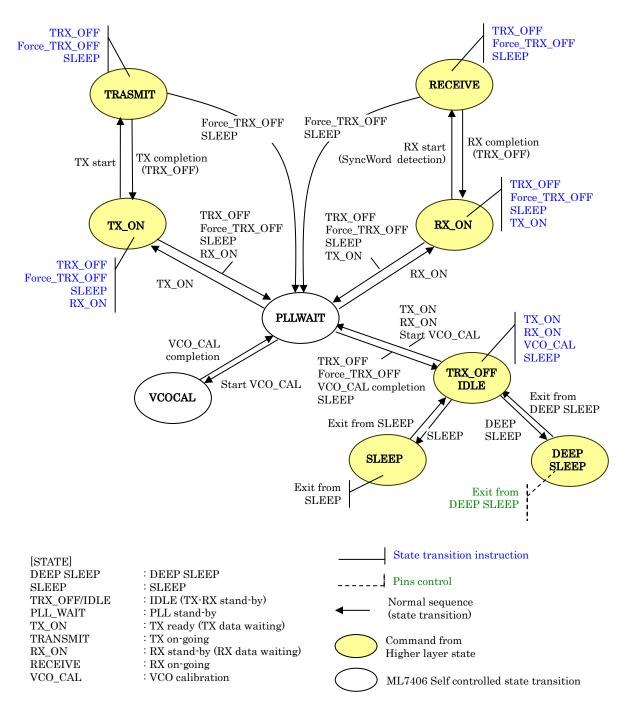

oSerial Peripheral Interface (SPI)

ML7406 has a SPI, which supports slave mode. Host MCU can read/write to the ML7406 registers and on-chip FIFO using MCU clock. Single access mode and burst access mode are also supported.

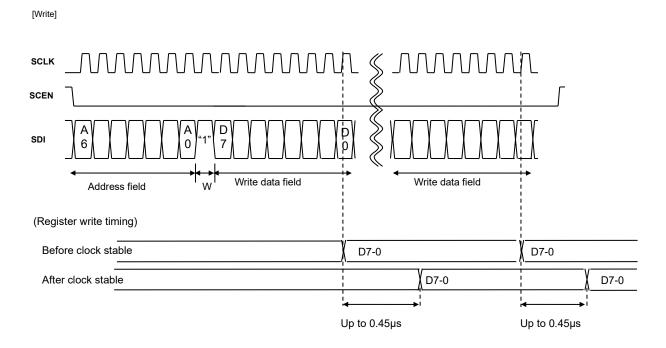

[Single access mode timing chart]

In write operation, data will be stored into internal register at rising edge of clock which is capturing D0 data. During write operation, if setting SCEN line to "H", the data will not be stored into register. For more details of SCEN invert perios, please refer to the "SPI interface characteristics". After the internal clock is stabilized, the data will be written into the register in synchronization with the internal clock.

[Burst access mode timing chart]

By maintaining SCEN line as "L", Burst access mode will be active. By setting SCEN line to "H", exiting from the burst access mode. During burst access mode, address will be automatically incremented.

When SCEN line becomes "H" before Clock for D0 is input, data transaction will be aborted.

#### (Note)

If destination is [WR\_TX\_FIFO: B0 0x7C] or [RD\_FIFO: B0 0x7F] register, address will not be incremented. And continuous FIFO access is possible.

[Read]

#### •LSI state transition control

#### oLSI state transition instruction

State can be controlled from MCU by setting registers below.

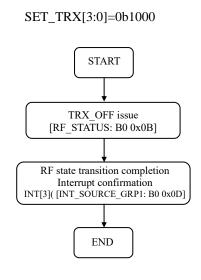

| State transition command | Instruction                                     |

|--------------------------|-------------------------------------------------|

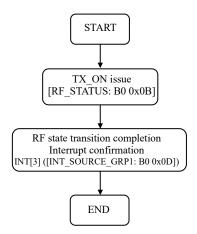

| TX_ON                    | SET_TRX ([RF_STATUS: B0 0x0B(3-0)]) = 0b1001    |

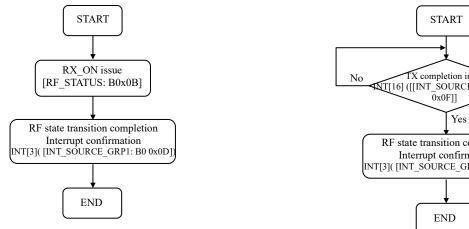

| RX_ON                    | SET_TRX ([RF_STATUS: B0 0x0B(3-0)]) = 0b0110    |

| TRX_OFF                  | SET_TRX ([RF_STATUS: B0 0x0B(3-0)]) = 0b1000    |

| Force_TRX_OFF            | SET_TRX ([RF_STATUS: B0 0x0B(3-0)]) = 0b0011    |

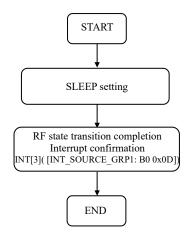

| SLEEP                    | SLEEP_EN([SLEEP/WU_SET: B0 0x2D(0)]) = 0b1      |

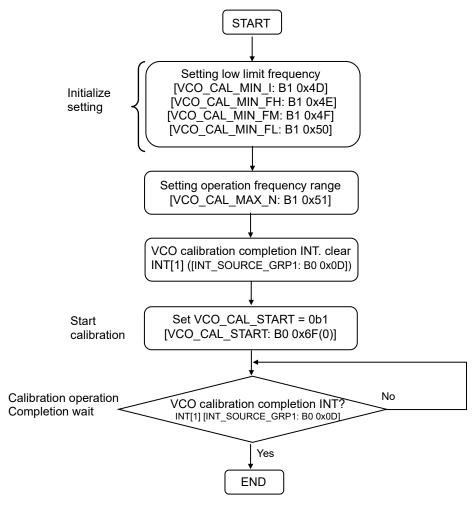

| VCO_CAL                  | VCO_CA_LSTART([VCO_CAL_START: B0 0x6F(0)])= 0b1 |

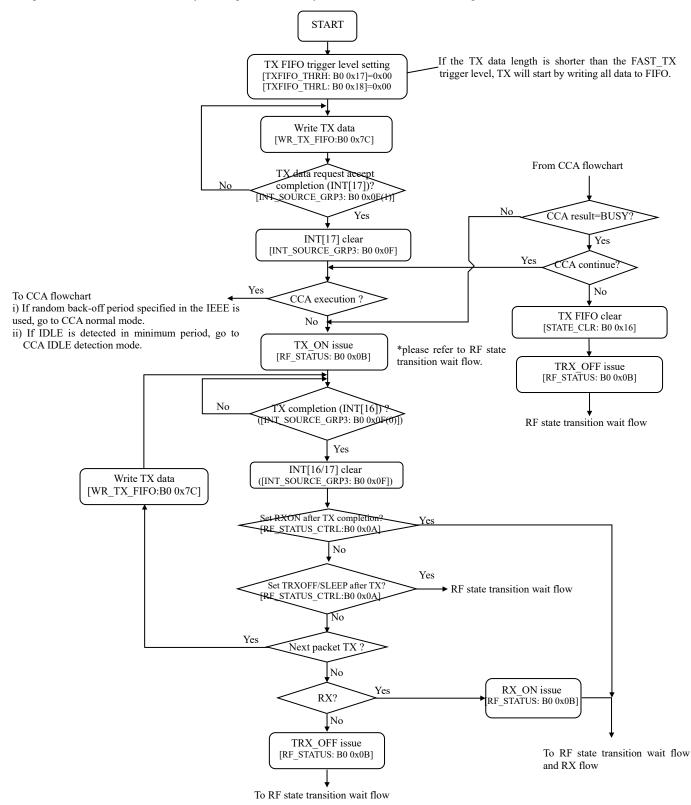

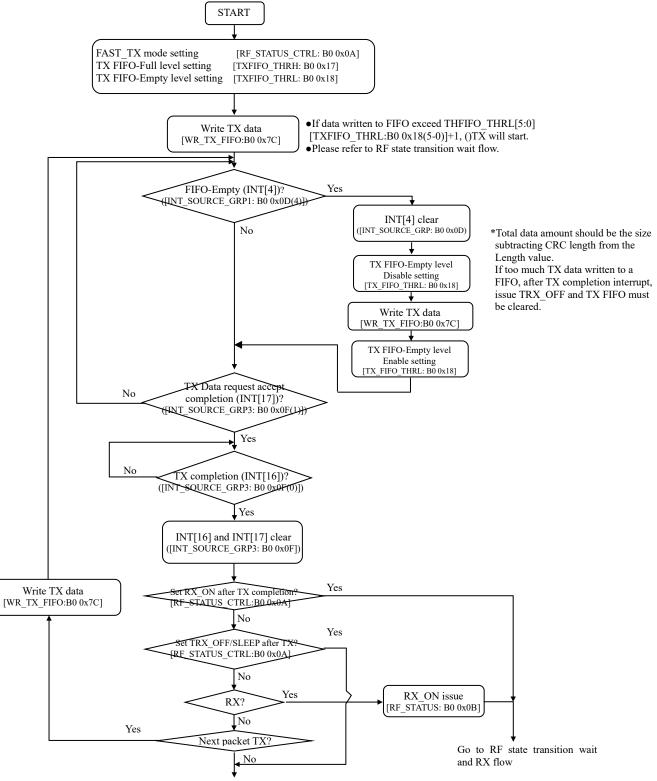

State can be changed without command from MCU. If one of the following condition is met, state is changed automatically according to the following table. In order to enable these functions, the following registers must be programmed.

| Function                                              | Control bit name                                                               |

|-------------------------------------------------------|--------------------------------------------------------------------------------|

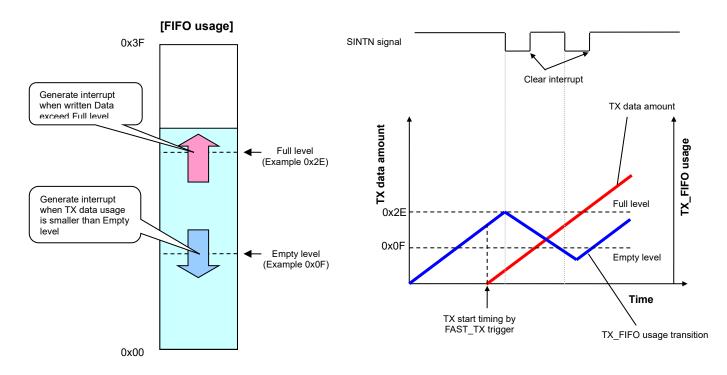

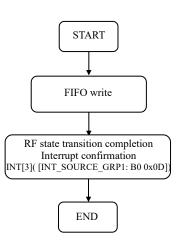

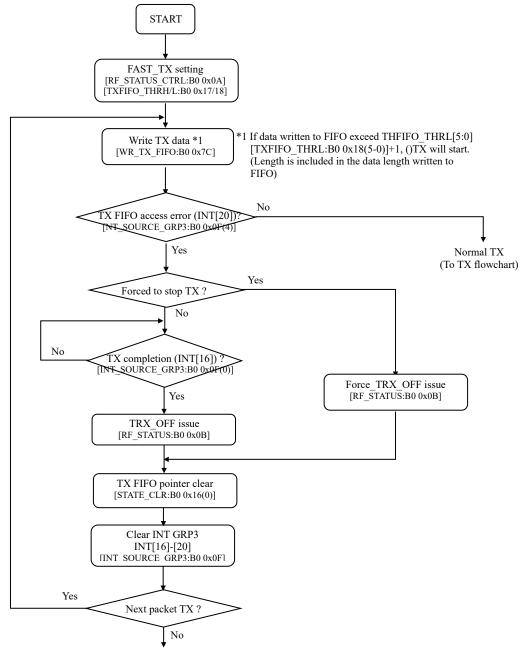

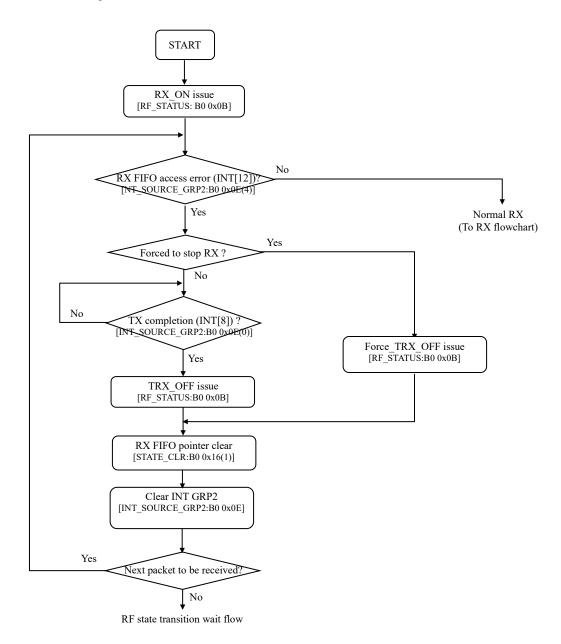

| Automatic TXON after FIFO write completion (AUTO_TX)  | AUTO_TX_EN([RF_STATUS_CTRL: B0 0x0A(4)])                                       |

| Automatic TXON during FIFO wrtie (FAST_TX)            | FAST_TX_EN([RF_STATUS_CTRL: B0 0x0A(5)])                                       |

| RF state setting after packet transmission completion | TXDONE_MODE([RF_STATUS_CTRL: B0 0x0A(1-0)])                                    |

| RF state setting after packet reception completion    | RXDONE_MODE([RF_STATUS_CTRL: B0 0x0A(3-2)])                                    |

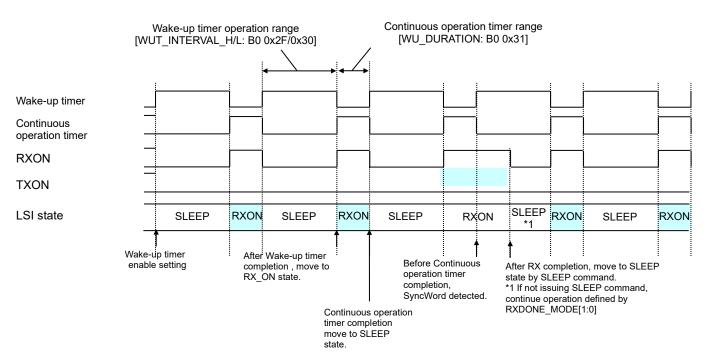

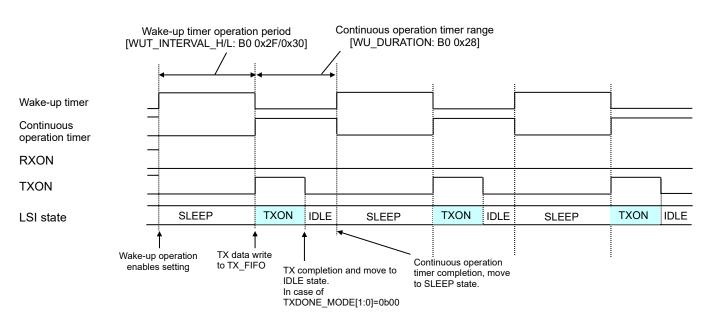

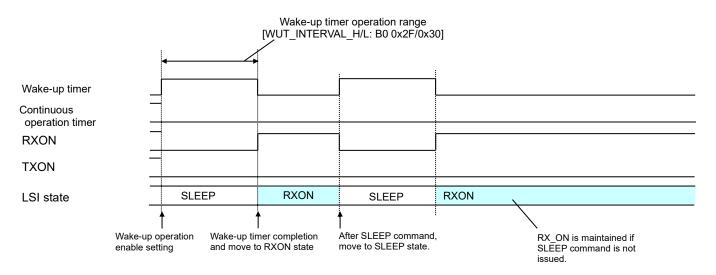

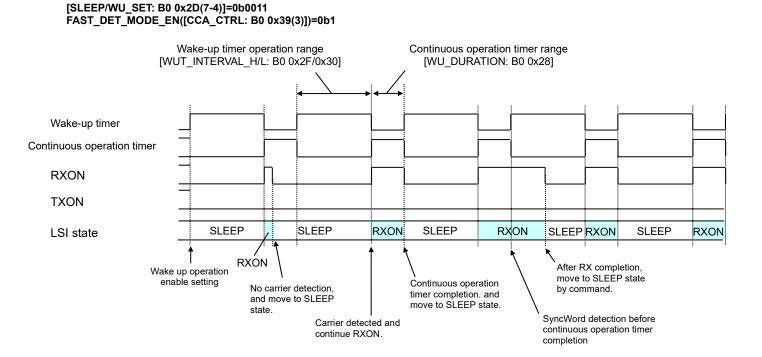

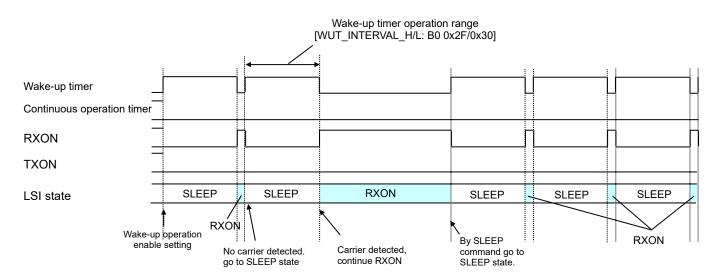

| Automatic RX_ON/TX_ON by Wake-up time                 | WAKEUP_MODE([SLEEP/WU_SET:B0 0x2D(6)])<br>WAKEUP_EN([SLEEP/WU_SET:B0 0x2D(4)]) |

| Automatic VCO calibration after exit from SLEEP       | AUTO_VCOCAL_EN([VCO_CAL_START: B0 0x6F(4)])                                    |

| Automatic SLEEP by Timer                              | WU_DURATION_EN([SLEEP/WU_SET: B0 0x2D(5)])                                     |

| Automatic SLEEP by high speed carrier checking mode   | FAST_DET_MODE_EN([CCA_CTRL:B0 0x39(3)])                                        |

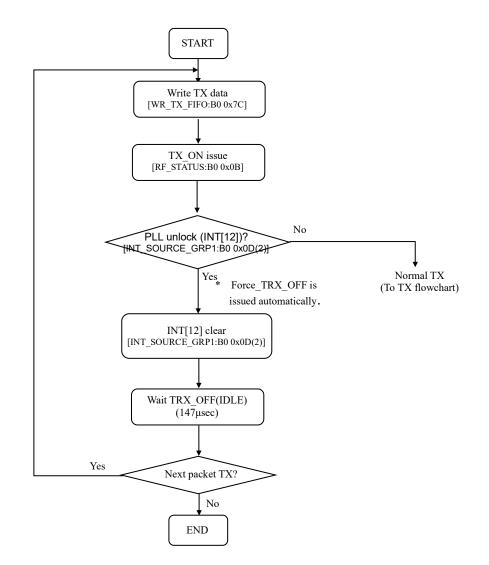

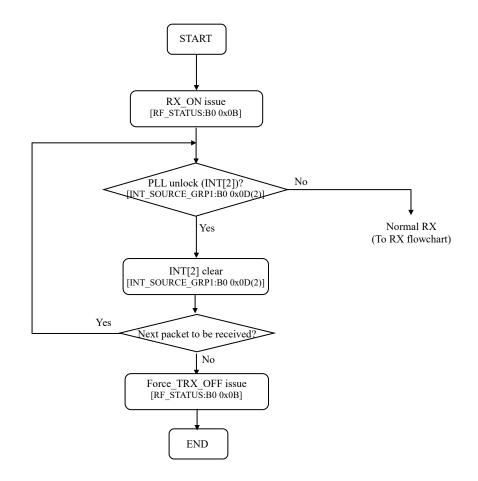

| Force_TRX_OFF after PLL unlock detection during TX    | PLL_LD_EN([PLL_LOCK_DETECT: B1 0x0B(7)])                                       |

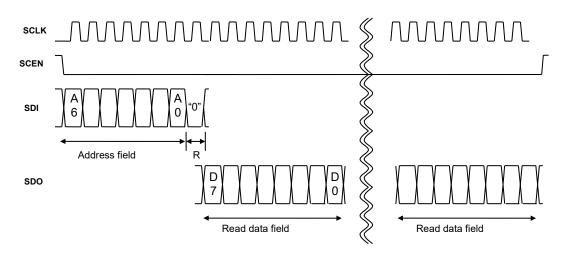

#### OState Diagram

Each state transition control is decribed in the follwing state diagram.

#### LSI state diagram

#### (Note)

The following state transition is inhibited; DEEP SLEEP  $\rightarrow$  any state  $\rightarrow$  SLEEP

#### **OSLEEP** setting

DEEP\_Sleep mode: Powers for all blocks except IO pins are turned off. Sleep mode: Main regulator and 26MHz oscillation circuits are tured off. But sub-regulator is turned-on. The following registers can be programmed to control SLEEP state.

| Function                           | Control bit name                           |

|------------------------------------|--------------------------------------------|

| Power control                      | PDN_EN([SLEEP/WU_SET: B0 0x2D(1)])         |

| Wake-up setting                    | WAKEUP_EN([SLEEP/WU_SET: B0 0x2D(4)])      |

| Wake-up timer clock source setting | WUT_CLK_SOURCE([SLEEP/WU_SET: B0 0x2D(2)]) |

| Internal RC oscillator control     | RC32K_EN ([CLK_SET2: B0 0x03(3)])          |

Setting method and internal state for DEEP\_SLEEP and various SLEEP modes are as follows:

| SLEEP mode | Setting method                                                                               | main<br>regulator | Sub<br>regulator | 26MHz<br>oscillator | RC<br>oscilator | Low clock<br>timer | FIFO |

|------------|----------------------------------------------------------------------------------------------|-------------------|------------------|---------------------|-----------------|--------------------|------|

| DEEP_SLEEP | RESETN pin="L"<br>REGPDIN pin="H"                                                            | OFF               | OFF              | OFF                 | OFF             | OFF                | OFF  |

| SLEEP1     | not supported                                                                                | -                 | -                | -                   | -               | -                  | -    |

| SLEEP2     | [SLEEP/WU_SET: B0 0x2D(4-0)] =<br>0b0_1001 (*2)<br>[CLK_SET2: B0 0x03(3)] = 0b0<br>(default) | OFF               | ON               | OFF                 | OFF(*1)         | OFF                | ON   |

| SLEEP3     | [SLEEP/WU_SET: B0 0x2D(4-0)] =<br>0b1_1001 (*2)<br>[CLK_SET2: B0 0x03(3)] = 0b0<br>(default) | OFF               | ON               | OFF                 | OFF             | ON                 | ON   |

| SLEEP4     | [SLEEP/WU_SET: B0 0x2D(4-0)] =<br>0b1_1101 (*2)<br>[CLK_SET2: B0 0x03(3)] = 0b1              | OFF               | ON               | OFF                 | ON              | ON                 | ON   |

(\*1) Low speed clock is supplied from EXT\_CLK pin.

(\*2) Please set proper value to [SLEEP/WU\_SET: B0 0x2D(3)].

(Note)

Contents of registers are not kept during DEEP\_SLEEP. Contents of registers are kept during SLEEP2, SLEEP3, SLEEP4. However, the SLEEP time should be less than the below time, to keep contents of registers normally.

| Operation maximum<br>Temperature[°C] | 25   | 45   | 65  | 85  |

|--------------------------------------|------|------|-----|-----|

| SLEEP period[msec]                   | 1900 | 1100 | 600 | 300 |

When the SLEEP time is longer than the above time, register value can be held by canceling SLEEP in the following procedure. However, the wakeup timer function can not be used.

i.  $[REGULATOR\_CTRL: B1 0x07] = 0xF 9$

ii. WAIT 500us

iii. [REGULATOR\_CTRL: B1 0x07] = 0xFD

iv. SLEEP\_EN ([SLEEP/WU\_SET: B0.0x2D(0)]) = 0b0

v. [REGULATOR\_CTRL: B1 0x07] = 0xFE

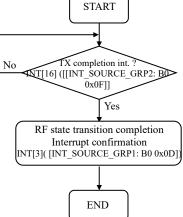

#### ONotes to set RF state

ML7406 is able to change the internal RF state transition autonomously (without commands from MCU) as well as RF state change commands from MCU. (please refer to "LSI state transition instruction"). If both timing of operation (autonomous state and state change from MCU command) overlapped, unintentional RF state may occur. Timing of autonomous state RF change is described in the following table.

Care must be taken not to overlap the conditions.

| Function                             | RF state change<br>(before→after)                                                                                                               | RF state transition timing (not from Host MCU command)                                                                                    | Recommended process                                                                                                                                               |  |  |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Automatic TX                         | TRX_OFF/RX_ON<br>→TX_ON                                                                                                                         | After TX data transfer completion interrut occurs,<br>{ value [TX_RATE_H/L: B1 0x02/03)] * 2 / 26}[µs]<br>period.                         |                                                                                                                                                                   |  |  |

| FAST_TX mode                         |                                                                                                                                                 | When FIFO write access exceed trigger level +1,<br>{ value [RX_RATE1_H/L:B1 0x04/05] * 5 / 26}[µs]<br>period.                             | Write access to [RF_STATUS:B0                                                                                                                                     |  |  |

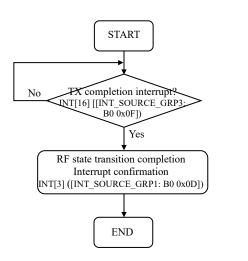

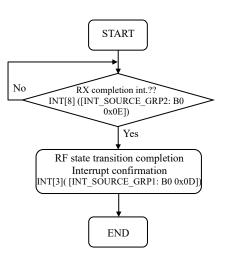

| RF state setting after TX completion | $\begin{array}{c} TX\_ON \rightarrow TRX\_OFF \\ \hline TX\_ON \rightarrow RX\_ON \\ \hline TX\_ON \rightarrow SLEEP \end{array}$               | After TX completion interrupt (INT[16] group3),<br>{ value [TX_RATE_H/L:B1 0x02/03] * 2 / 26} [μs]<br>period                              | 0x0B] is possible after RF state<br>transition completion interrupt<br>(INT[3] group1), or move to the<br>state defined by GET_TRX<br>([RF_STATUS:B0 0x0B(7-4)]). |  |  |

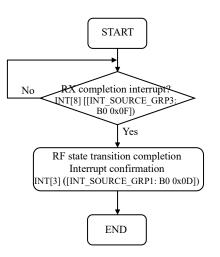

| RF state setting after RX completion | $\begin{array}{c} RX\_ON \rightarrow TRX\_OFF \\ RX\_ON \rightarrow TX\_ON \\ RX\_ON \rightarrow SLEEP \end{array}$                             | After data RX completion interrupt (INT[8] group2,<br>{ value [RX_RATE1_H/L:B1 0x04/05] * 2 / 26}[µs]<br>period                           |                                                                                                                                                                   |  |  |

| Wake-up timer                        | SLEEP→TX_ON<br>SLEEP→RX_ON                                                                                                                      | After wake-up timer completion interrupt (INT[6]<br>group1), 1 clock cycle period defined by<br>WUT_CLK_SET[3:0] ([WUT_CLK_SET:B0 0x2E    |                                                                                                                                                                   |  |  |

|                                      | $\begin{array}{c} - \\ SLEEP \rightarrow VCO\_CAL \\ \rightarrow TX\_ON \\ \hline SLEEP \rightarrow VCO\_CAL \\ \rightarrow RX\_ON \end{array}$ | (3-0)]).<br>After wake-up timer completion interrupt (INT[6]:<br>group1), before VCO calibration completion<br>interrupt (INT[1] group1). | Write access to [RF_STATUS:B0<br>0x0B] and BANK2 is possible<br>after VCO calibration completion<br>interrupt (INY[1] group1).                                    |  |  |

| Continuous operation<br>timer        | TX_ON→SLEEP                                                                                                                                     | After continuous operation timer completion, 1<br>clock cycle period defined by WUT_CLK_SET[3:0]<br>([WUT CLK SET:B0 0x2E (3-0)]).        | Write access to [RF_STATUS:B0<br>0x0B] is possible after RF state<br>transition completion interrupt                                                              |  |  |

| High speed carrier checking          | RX_ON→SLEEP<br>RX_ON→SLEEP                                                                                                                      | After CCA completion interrupt, duration 6.3[µs].                                                                                         | (INT[3] group1), or move to the<br>state defined by GET_TRX<br>([RF_STATUS:B0 0x0B(7-4)]).                                                                        |  |  |

| PLL unlock detection                 | TX_ON→TRX_OFF                                                                                                                                   | After PLL unlock detection interrupt (INT[2] group1) occurs, duration 147[µs].                                                            | Write access to [RF_STATUS:B0<br>0x0B] is possible 147µs after PLL<br>unlock interrupt (INT[2] group1)<br>detected.                                               |  |  |

#### • Packet Handling Function

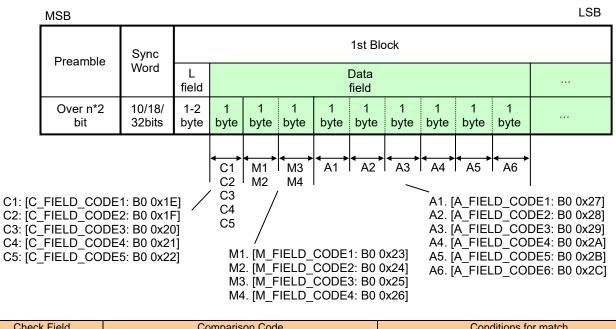

#### Packet format

ML7406 supports Wireless M-BUS frame FormatA/B, and Format C which is non Wireless M-BUS universal format. The following packet handling are supported in FIFO mode or DIO mode

| 1) Preamble and SyncWord automatic insertion (TX) | <br>DIO/FIFO mode |

|---------------------------------------------------|-------------------|

| 2) Preamble and SyncWord automatic detection (RX) | <br>DIO/FIFOmode  |

| 3) Preamble and SyncWord automatic deletion (RX)  | <br>DIO/FIFO mode |

| 4) CRC data insertion (TX)                        | <br>FIFO mode     |

| 5) CRC check and error notification (RX)          | <br>DIO/FIFO mode |

The following table shows control bits relative with the Packet format function.

| Function                            | Control bit name                              |

|-------------------------------------|-----------------------------------------------|

| Packet formatsetting                | PKT_FORMAT[1:0] ([PKT_CTRL1: B0 0x04(1-0)])   |

| IEEE 802.15.4g setting              | IEEE802_15_4G_EN ([PKT_CTRL1: B0 0x04(2)])    |

| RX extended link layer mode disable | RX_EXTPKT_OFF ([PKT_CTRL1: B0 0x04(3)])       |

| Data area bit order setting         | DAT_LF_EN ([PKT_CTRL1: B0 0x04(4)])           |

| Length area bit order setting       | LEN_LF_EN ([PKT_CTRL1: B0 0x04(5)])           |

| Extended link layer mode setting    | EXT_PKT_MODE[1:0] ([PKT_CTRL1: B0 0x04(7-6)]) |

| Length field setting                | LENGTH_MODE ([PKT_CTRL2: B0 0x05(0)])         |

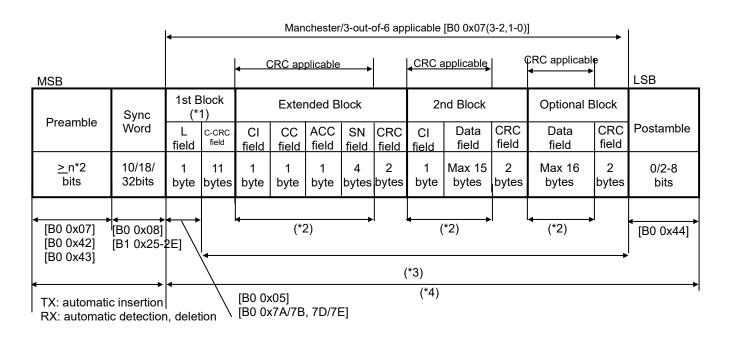

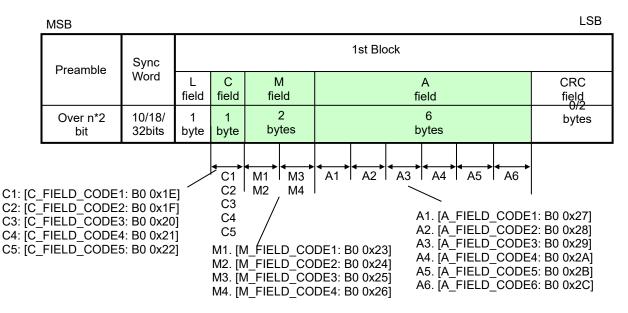

#### (1) Format A (Wireless M-BUS)

By setting PKT\_FORMAT[1:0] ([PKT\_CTRL1: B0 0x04(1-0)])=0b00, Wireless M-BUS Format A is selected.

Format A consists of 1<sup>st</sup> Block, 2<sup>nd</sup> Block and Optional Block(s). Each block has 2 bytes of CRC. "L-field" (1<sup>st</sup> byte of 1<sup>st</sup> Block ) indicates packet length, which includes subsequenct user data bytes from "C-field". However, CRC bytes and postamble are excluded. Depending on "L-field" value, 2<sup>nd</sup> Block and Optional Block(s) are added.

The following [] indicates register address [bank #, address].

|                                    |                        | ₊            | Manchester/3-out-of-6 applicable [B0 0x07(3-2,1-0)] |                  |            |              |             |                 |              |                 |              |               |

|------------------------------------|------------------------|--------------|-----------------------------------------------------|------------------|------------|--------------|-------------|-----------------|--------------|-----------------|--------------|---------------|

| CRC app<br>MSB                     |                        |              |                                                     | pplicabl         | e →        |              | _ CF        | C applicable    |              | CRC applicable  |              | LSB           |

| Preamble                           | Sync                   |              |                                                     | 1st Bloo         | ck         |              |             | 2nd Block       |              | Optional Bloc   | k            |               |

| Treamble                           | Word                   | L<br>field   | C<br>field                                          | M<br>field       | A<br>field | CRC<br>field | CI<br>field | Data<br>field   | CRC<br>field | Data<br>field   | CRC<br>field | Postamble     |

| <u>&gt;</u> n*2 (*1)<br>bits       | 10/18/<br>32bits       | 1<br>byte    | 1<br>byte                                           | 2<br>bytes       | 6<br>bytes | 2<br>bytes   | 1<br>byte   | Max.15<br>bytes | 2<br>bytes   | Max.16<br>bytes | 2<br>bytes   | 0/2-8<br>bits |

| B0 0x07]<br>[B0 0x42]<br>[B0 0x43] | [B0 0x08]<br>[B1 0x25- |              | •                                                   | (*2)             |            |              | 4           | (*2)            |              | (*2)            |              | [B0 0x44]     |

| []                                 |                        |              |                                                     |                  |            |              | (*3)        |                 |              |                 |              | ı<br><b>b</b> |

| TX: automatic<br>RX: automatic     |                        | <br>. deleti | ∖<br>⊃n                                             | [B0 02<br>[B0 02 | -          | 8, 7D/7E     | =]          | (*4)            |              |                 |              |               |

\*1: Each mode has different minimum value of n.

\*2: Indicates TX FIFO data storage area size.

\*3: Indicates RX FIFO data storage area size.

#### Extended Link Layer Format

If "CI-field" (1<sup>st</sup> byte of 2<sup>nd</sup> Block)=0x8C or 0x8D, Extended Link Layer is applied. The packet format is as follows:

(a) CI-field = 0x8C

For TX, if 2 bytes extention format is used, set EXT\_PKT\_MODE[1:0] ([PKT\_CTRL1: B0 0x04(7-6)])=0b01. For RX, if RX\_EXTPKT\_OFF([PKT\_CTRL1: B0 0x04(3)])=0b0, ML7406 recognizes "CI-field" and RX operation is processed.

|                                                                                            |                               | 4                                 | Manchester/3-out-of-6 applicable [B0 0x07(3-2,1-0)] |             |                    |              |             |                 |                |                 |              |               |

|--------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------|-----------------------------------------------------|-------------|--------------------|--------------|-------------|-----------------|----------------|-----------------|--------------|---------------|

| MSB                                                                                        |                               | CRC applicable     CRC applicable |                                                     |             |                    |              |             |                 | LSB            |                 |              |               |

| Preamble Sync                                                                              |                               |                                   |                                                     |             | Extended 2nd Block |              | 2nd Block   |                 | Optional Block |                 | Postamble    |               |

| Treamble                                                                                   | Word                          | L<br>field                        | C-CRC<br>field                                      | CI<br>field | CC<br>field        | ACC<br>field | CI<br>field | Data<br>field   | CRC<br>field   | Data<br>field   | CRC<br>field | 1 Ustallible  |

| <u>&gt;</u> n*2<br>bits                                                                    | 10/18/<br>32bits              | 1<br>byte                         | 11<br>bytes                                         | 1<br>byte   | 1<br>byte          | 1<br>byte    | 1<br>byte   | Max 12<br>bytes | 2<br>bytes     | Max 16<br>bytes | 2<br>bytes   | 0/2-8<br>bits |

|                                                                                            | 【■<br>[B0 0x08]<br>[B1 0x25-: |                                   |                                                     | •           |                    | (            | *2)         |                 |                | (*2)            |              | [B0 0x44]     |

|                                                                                            |                               | (*3)                              |                                                     |             |                    |              |             |                 |                | · · ·           |              |               |

| TX: automatic insertion [B0 0x05]<br>RX: automatic detection, deletion [B0 0x7A/7B, 7D/7E] |                               |                                   |                                                     |             |                    |              |             |                 |                |                 |              |               |

\*1: 1st Block is identical to normal Format A..

\*2: Indicates TX FIFO data storage area size.

\*3: Indicates RX FIFO data storage area size.

#### (b) CI-field = 0x8D

For TX, if 8 bytes extention format is used, set EXT\_PKT\_MODE[1:0] ([PKT\_CTRL1: B0 0x04(7-6)])=0b10. For RX, if RX\_EXTPKT\_OFF([PKT\_CTRL1: B0 0x04(3)])=0b0, ML7406 recognizes "CI-field" and RX operation is processed.

\*1: 1<sup>st</sup> Block is identical to normal Format A..

\*2: Indicating TX FIFO data storage area size.

\*3: Indicating RX FIFO data storage area size.

#### (2) Format B (Wireless M-BUS)

By setting PKT\_FORMAT([PKT\_CTRL1: B0 0x04(1-0)])=0b01, Wireless M-BUS Format B is selected.

Format B consists of 1st Block, 2nd Block or Optional Block. Each block after 2nd Block has 2 bytes of CRC. "L-field" indicates packet length, which includes subsequent user data bytes from "C-field". However, unlike Format A, CRC bytes are included (Pastamble are excluded). Depending on "L-field" value, 2nd Block and Optional Block(s) are added.

The following [] indicates register address [bank #, address].

|                                                                                                                                                     |                        | Manchester/3-out-of-6 applicable [B0 0x07(3-2,1-0)] |              |            |            |             |                  |                |                  |              |                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------------------------------|--------------|------------|------------|-------------|------------------|----------------|------------------|--------------|-------------------|

| MSB                                                                                                                                                 | ◀                      | CRC applicable                                      |              |            |            |             |                  |                | LSB              |              |                   |

| Preamble                                                                                                                                            | Sync                   |                                                     | 1st Block    |            |            |             | 2nd Block        | Optional Block |                  | Destauchte   |                   |

| Freattible                                                                                                                                          | Word                   | Word L<br>field                                     | C<br>field   | M<br>field | A<br>field | CI<br>field | Data<br>field    | CRC<br>field   | Data<br>field    | CRC<br>field | Postamble         |

| <u>&gt;</u> n*2 (*1)<br>bits                                                                                                                        | 10/18/<br>32bits       | 1<br>byte                                           | 1<br>byte    | 2<br>bytes | 6<br>bytes | 1<br>byte   | Max 115<br>bytes | 2<br>bytes     | Max 126<br>bytes | 2<br>bytes   | 0/2-8<br>bits     |

| [B0 0x42]                                                                                                                                           | [B0 0x08]<br>[B1 0x25- |                                                     | E] (*2) (*2) |            |            |             |                  |                |                  |              | [B0 0x44]<br>←─── |

| [B0 0x43]       (*3)         TX: automatic insertion       [B0 0x05]       (*4)         RX: automatic detection, deletion       [B0 0x7A/7B, 7D/7E] |                        |                                                     |              |            |            |             |                  |                |                  |              |                   |

\*1: Each mode has different minimum value of n.

\*2: Indicates TX FIFO data storage area size.

\*3: Indicates RX FIFO data storage area size.

#### Extended Link Layer Format

If "CI-field" (1<sup>st</sup> byte of  $2^{nd}$  Block ) = 0x8C or 0x8D, Extended Link Layer is applied. The packet format is as follows:

(a) CI-field = 0x8C

For TX, if 2bytes extention format is used, set EXT\_PKT\_MODE[1:0] ([PKT\_CTRL1: B0 0x04(7-6)])=0b01. For RX, if RX\_EXTPKT\_OFF([PKT\_CTRL1: B0 0x04(3)])=0b0, ML7406 recognizes "CI-field" and RX operation is processed.

|                                                                                                       |                        | <b></b>    | Manchester/3-out-of-6 applicable [B0 0x07(3-2,1-0)] |             |                   |              |             |                  |                |                  | 1            |             |

|-------------------------------------------------------------------------------------------------------|------------------------|------------|-----------------------------------------------------|-------------|-------------------|--------------|-------------|------------------|----------------|------------------|--------------|-------------|

| MSB                                                                                                   | ◀                      |            |                                                     |             | CRC a             | oplicable    | •           |                  | CRC applicable | •                | LSB          |             |

| Preamble                                                                                              | Sync                   |            | 1st Block<br>(*1)                                   |             | Extended<br>Block |              |             | 2nd Block        |                | Optional Block   |              | Postamble   |

|                                                                                                       | Word                   | L<br>field | C-A<br>field                                        | CI<br>field | CC<br>field       | ACC<br>field | CI<br>field | Data<br>field    | CRC<br>field   | Data<br>field    | CRC<br>field | T UStamble  |

| <u>&gt; </u> n*2<br>bits                                                                              | 10/18/<br>32bits       | 1<br>byte  | 9<br>bytes                                          | 1<br>byte   | 1<br>byte         | 1<br>byte    | 1<br>byte   | Max 112<br>bytes | 2<br>bytes     | Max 126<br>bytes | 2<br>bytes   | 2-8<br>bits |

| ■ [B0 0x07]<br>[B0 0x42]<br>[B0 0x43]                                                                 | [B0 0x08]<br>[B1 0x25- |            | 2E] (*2)                                            |             |                   |              |             | •                | (*2)           |                  | •            |             |

| [D0 0x43]                                                                                             |                        |            |                                                     |             |                   | (*3)         |             |                  |                |                  |              |             |

| (*4)<br>TX: automatic insertion<br>RX: automatic detection, deletion [B0 0x05]<br>[B0 0x7A/7B, 7D/7E] |                        |            |                                                     |             |                   |              |             |                  |                |                  |              |             |

\*1: 1st Block is identical to normal Format B..

\*2: Indicating TX FIFO data storage area size.

\*3: Indicating RX FIFO data storage area size.

(b) CI-field = 0x8D

For TX, if 8 bytes extention format is used, set EXT\_PKT\_MODE[1:0]([PKT\_CTRL1: B0 0x04(7-6)])=0b10.

For RX, if RX\_EXTPKT\_OFF([PKT\_CTRL1: B0 0x04(3)])=0b0, ML7406 recognizes "CI-field" and RX operation is processed.

|                                                                                               | Manchester/3-out-of-6 applicable [B0 0x07(3-2,1-0)] |                                  |              |             |             |              |             |              |                |                   |              |                  |              |             |

|-----------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------|--------------|-------------|-------------|--------------|-------------|--------------|----------------|-------------------|--------------|------------------|--------------|-------------|

| MSB                                                                                           | ←                                                   | CRC applicable                   |              |             |             |              |             |              | cable          | LSB               |              |                  |              |             |

| Sync                                                                                          |                                                     | 1st Block Extended<br>(*1) Block |              |             |             | 2nd Block    |             |              | Optional Block |                   | Postamble    |                  |              |             |

| Preamble Word                                                                                 | Word                                                | L<br>field                       | C-A<br>field | CI<br>field | CC<br>field | ACC<br>field | SN<br>field | CRC<br>field | CI<br>field    | Data<br>field     | CRC<br>field | Data<br>field    | CRC<br>field | TOSIAITIDIE |

| <u>&gt;</u> n*2<br>bits                                                                       | 10/18/<br>32bits                                    | 1<br>byte                        | 9<br>bytes   | 1<br>byte   | 1<br>byte   | 1<br>byte    | 4<br>bytes  | 2<br>bytes   |                | Max. 106<br>bytes | 2<br>bytes   | Max.126<br>bytes | 2<br>bytes   | 2-8<br>bits |

|                                                                                               | ← →<br>[B0 0x08]<br>[B1 0x25-                       |                                  | - 4          |             |             |              |             |              | (*             | 2)                |              | (*2)             |              | (B0 0x44)   |

| TX: automatic insertion<br>RX: automatic detection, deletion [B0 0x05]<br>[B0 0x7A/7B, 7D/7E] |                                                     |                                  |              |             |             |              |             |              |                |                   |              |                  |              |             |

\*1: 1<sup>st</sup> Block is identical to normal Format B..

\*2: Indicating TX FIFO data storage area size.

\*3: Indicating RX FIFO data storage area size.

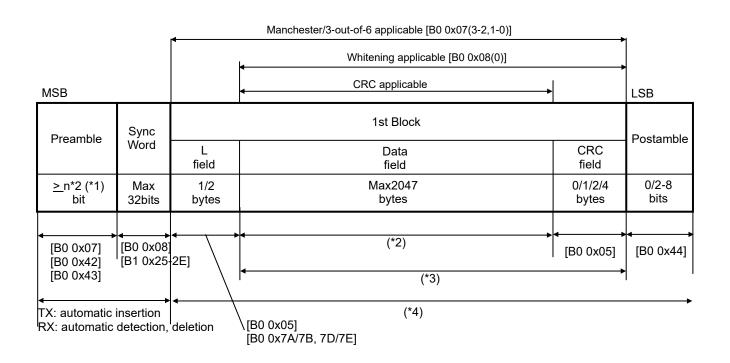

#### (3) Format C (non Wireless M-BUS, general purpose format)

By setting PKT\_FORMAT([PKT\_CTRL1: B0 0x04(1-0)])=0b10, Format C, which is non Wireless M-BUS format, is selected. Format C consists of 1<sup>st</sup> Block only, which has 2 bytes of CRC. "L-field" indicates packet length, which includes subsequent user data bytes, including CRC bytes. The length of "L-field" is defined by LENGTH\_MODE([PKT\_CTRL2:B0 0x5(0]). Data Whitening function is supported.

The following [] indicates register address [bank #, address].

\*1 Preamble length (n) is programmable by [TXPR\_LEN\_H/L: B0 0x42/43] registers.

\*2 indicating TX FIFO data strorage area size.

\*3 Indicating RX FIFO data storage area size.

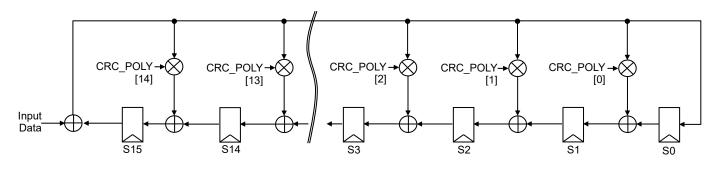

#### oCRC function

ML7406 has CRC32,CRC16 and CRC8 function. CRC is calculated and appended to TX data. CRC is checked for RX data. The following modes are used for automatic CRC function.

| •FIFO mode: | RXDIO_CTRL ([DIO_SET: B0 0x0C(7-6)]) = 0b00 |

|-------------|---------------------------------------------|

| •DIO mode:  | RXDIO_CTRL ([DIO_SET: B0 0x0C(7-6)]) = 0b11 |

| Function                         | Control bit name / Register                   |

|----------------------------------|-----------------------------------------------|

| TX CRC setting                   | TX_CRC_EN([PKT_CTRL2: B0 0x05(2)])            |

| RX CRC setting                   | RX_CRC_EN([PKT_CTRL2: B0 0x05(3)])            |

| CRC length setting               | CRC_LEN([PKT_CTRL2: B0 0x05(5-4)])            |

| CRC complement value OFF setting | CRC_COMP_OFF([PKT_CTRL2: B0 0x05(6)])         |

| CRC polynomial setting           | [CRC_POLY3/2/1/0: B1 0x16/17/18/19] registers |

| CRC error status                 | [CRC_ERR_H/M/L: B0 0x13/14/15] registers      |

Any CRC polynomials for CRC32/CRC16/CRC8 can be specified. Reset value is as follows:

CRC16 polynomial =  $x^{16} + x^{13} + x^{12} + x^{11} + x^{10} + x^8 + x^6 + x^5 + x^2 + 1$  (reset value)

(Note) CRC result data can be inverted by CRC complement value OFF setting,.

CRC data will be generated by the following circuits. By programming [CRC\_POLY3/2/1/0] registers, any CRC polynomials can be supported. Generated CRC will be transfer from the left most bit (S15). If data length is shorter than CRC length (3 bytes of CRC32 only), data "0"s will be added for CRC calculation. CRC check result is stored in [CRC\_ERR\_H/M/L] registers. Unlike Format C, Format A/B can include multiple CRC fields in one packet. For multiple CRCs check results, CRC value closest to L-field will be stored in CRC\_ERR[0] ([CRC\_ERR\_L:B0 0x15(0)]). Subsequent bit will be stored in CRC\_ERR from MSB order.

(Note)  $\bigoplus$  :exclusive OR

#### **CRC** polynomial circuits

General CRC polynomial can be programmed by below [CRC\_POLY3/2/1/0] register setting. CRC length can be set by CRC\_LEN.

|       | CPC polynomial                                                                                                | [CRC_POLY3/2/1/0] |           |           |           |  |  |

|-------|---------------------------------------------------------------------------------------------------------------|-------------------|-----------|-----------|-----------|--|--|

|       | CRC polynomial                                                                                                | (B1 0x16)         | (B1 0x17) | (B1 0x18) | (B1 0x19) |  |  |

| CRC8  | $x^8 + x^2 + x + 1$                                                                                           | 0x00              | 0x00      | 0x00      | 0x03      |  |  |

|       | $x^{16} + x^{12} + x^5 + 1$                                                                                   | 0x00              | 0x00      | 0x08      | 0x10      |  |  |

| CRC16 | $x^{16} + x^{15} + x^2 + 1$                                                                                   | 0x00              | 0x00      | 0x40      | 0x02      |  |  |

|       | $x^{16} + x^{13} + x^{12} + x^{11} + x^{10} + x^8 + x^6 + x^5 + x^2 + 1$                                      | 0x00              | 0x00      | 0x1E      | 0xB2      |  |  |

| CRC32 | $x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^8 + x^7 + x^5 + x^4 + x^2 + x + 1$ | 0x02              | 0x60      | 0x8E      | 0xDB      |  |  |

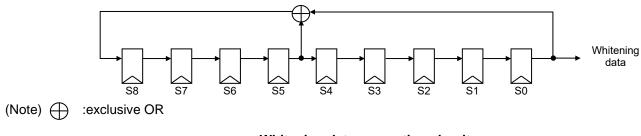

OData whitening function (non Wireless M-BUS standard)

ML7406 supports Data whitening function. In packet format A/B, subsequent data followed by C-field can be processed data whitening. In packet format C, data Whitening is applied from data field. Data generated by the following 9 bit pseudo random sequence (PN9) will be "XOR" with TX data (encoded data if Manchester or 3-out-of 6 coding is selected) before transmission. Intialization value of the PN9 generation shift register can be defined by [WHT\_INIT\_H/L: B1 0x64/65] registers. PN9 polynomial can be programmed with [WHT\_CFG: B1 0x66] register.

| Function                         | Control bit name                                   |

|----------------------------------|----------------------------------------------------|

| Data Whiteing setting enable     | WHT_SET ([DATA_SET2: B0 0x08(0)])                  |

| Data Whiteing initiazation value | WHT_INIT[8:0] ([WHT_INIT_H/L: B1 0x64(0)/65(7-0)]) |

| Whitening polynomia              | WHT_CFG[7:0] ([WHT_CFG: B1 0x66(7-0)])             |

In order to make feedback from S1 register, setting 0b1 to WHT\_CFG0 ([WHT\_CFG: B1 0x66(0)]). Similally in order to make feedback from S2 register, setting 0b1 to WHT\_CFG1 ([WHT\_CFG: B1 0x66(1)]). Other bits of [WHT\_CFG: B1 0x66] register has same function. Two or more bits can be also set to 0b1. Therefore any type of PN9 polynominal can be programmed.

Whitening data generation circuits

(generator polynomial:  $x^9 + x^5 + 1$ )

General PN9 polynomial can be defined by [WHT\_CFG].

| PN9 polynomial  | WHT_CFG[7:0]<br>[WHT_CFG: B1 0x66] |

|-----------------|------------------------------------|

| $x^9 + x^4 + 1$ | 0x08                               |

| $x^9 + x^5 + 1$ | 0x10                               |

#### •SyncWord detection function

ML7406 supports automatic SyncWord recognition function. By having two sets of SyncWord pattern storage area, it is possible to detect two different packet format (Format A/B) which are defined by Wireless M-Bus. (For details, please refer to Wireless M-BUS standard) Receiving packet format is indicated by SW\_DET\_RSLT([STM\_STATE:B0 0x77(5)]). In Format C, it is possible to search for two SyncWords but detected result is not indicated.

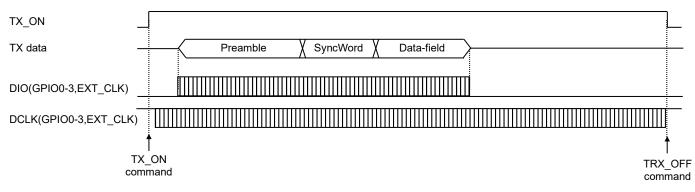

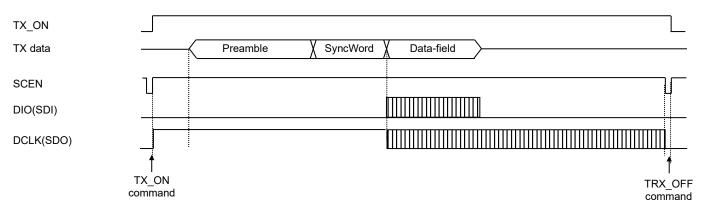

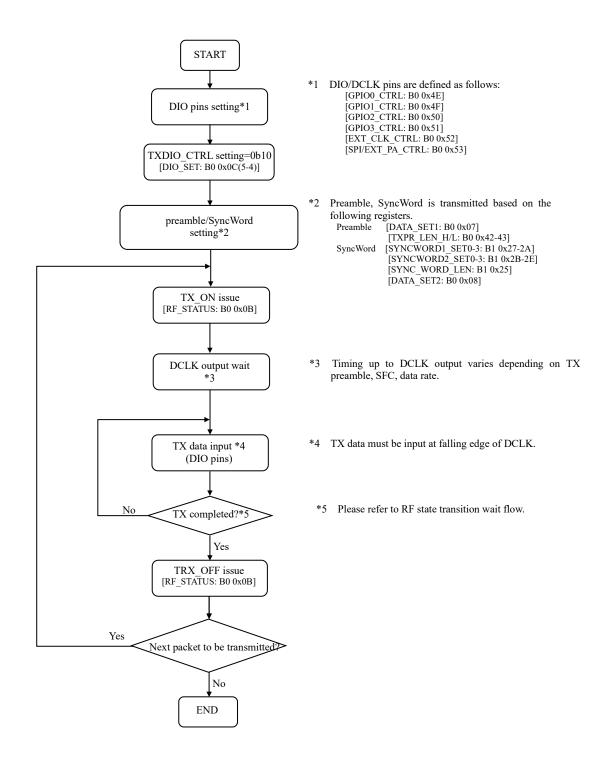

#### 1) TX

SyncWord pattern defined by SYNCWORD\_SEL ([DATA\_SET2: B0 0x08(4)]) will be selected. SyncWord length for TX is defined by SYNC\_WORD\_LEN[5:0] ([SYNC\_WORD\_LEN: B1 0x25(5-0)]). From high bit of each SyncWord pattern will be transmitted.

| SYNCWORD_SEL | TX SyncWord pattern                                            |

|--------------|----------------------------------------------------------------|

| 0            | SYNC_WORD1[31:0]<br>([SYNCWORD1_SET3/2/1/0: B1 0x27/28/29/2A]) |

| 1            | SYNC_WORD2[31:0]<br>([SYNCWORD2_SET3/2/1/0: B1 0x2B/2C/2D/2E]) |

Example) SyncWord patten and SyncWord length

If the follwing registers are programmed, from higher bit of SYNC\_WORD1[17:0] will be transmitted sequencially. [SYNC\_WORD\_LEN: B1 0x25]=0x12

SYNCWORD\_SEL ([DATA\_SET2: B0 0x08(4)]) = 0b0

If the following registers are programmed, from higher bit of SYNC\_WORD2[23:0] will be transmitted sequencially. [SYNC\_WORD\_LEN: B1 0x25]=0x18 SYNCWORD\_SEL (IDATA\_SET2: R0 0x08(4)]) = 0b1

SYNCWORD\_SEL ([DATA\_SET2: B0 0x08(4)]) = 0b1

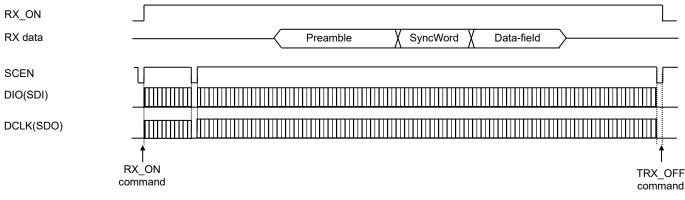

#### 2) RX

By setting SYNCWORD\_SEL and 2SW\_DET\_EN ([DATA\_SET2: B0 0x08(4,3)]), one SyncWord pattern waiting or two SyncWord patterns waiting can be selected as follows: Packet format automatic detection is valid if 2SW\_DET\_EN=0b1 and Format A or Fromat B is selected by PKT\_FORMAT[1:0] ([PKT\_CTRL1:B0 0x04(1-0)]).

| 2SW_DET_<br>EN | SYNCWORD_<br>SEL | SyncWord pattern<br>During Sync Detection | SyncWord<br>Detection<br>operation | Automatic<br>packet<br>format<br>detection | Data process after SyncWord                                                                                                                                                                         |

|----------------|------------------|-------------------------------------------|------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

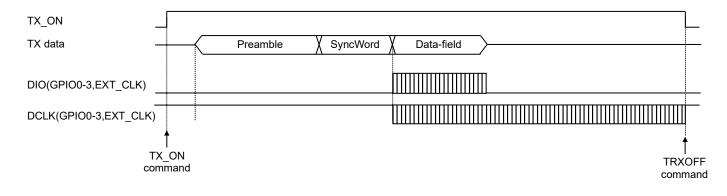

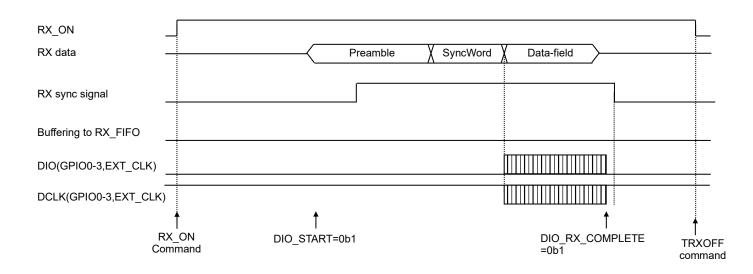

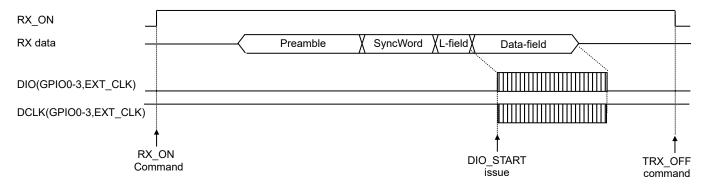

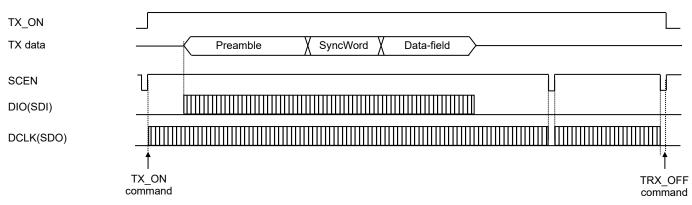

| 0              | 0                | SYNC_WORD1[31:0]                          | Waiting for<br>1 pattern           | no                                         | Process according to each Format<br>setting                                                                                                                                                         |