Dear customer

ROHM Co., Ltd. ("ROHM"), on the 1st day of April, 2024, has absorbed into merger with 100%-owned subsidiary of LAPIS Technology Co., Ltd.

Therefore, all references to "LAPIS Technology Co., Ltd.", "LAPIS Technology" and/or "LAPIS" in this document shall be replaced with "ROHM Co., Ltd." Furthermore, there are no changes to the documents relating to our products other than the company name, the company trademark, logo, etc.

Thank you for your understanding.

ROHM Co., Ltd. April 1, 2024

# **ML7436N**

Sub-GHz/2.4GHz Narrowband/Wideband RF Tranceiver with Built-in MCU

## ■1. Overview

ML7436N is a LSI for Sub-GHz/2.4GHz narrowband/wideband radio communication, which integrates Microcontroller and RF Transceiver in a single chip.

Product Name ML7436N-480ATB

Application Remote control Home, Building Security Sensor Network Smart Meters

#### Features:

- ♦ RF

- Supported Standard

- ♦ ARIB STD-T66, T67, T108

- ♦ ETSI EN 300 220(Europe)

- RF Frequency

- ♦ 389 550MHz band

- ♦ 778 1100MHz band

- ♦ 2.4Ghzband

- Realize high resolution modulation by using fractional N type PLL direct modulation

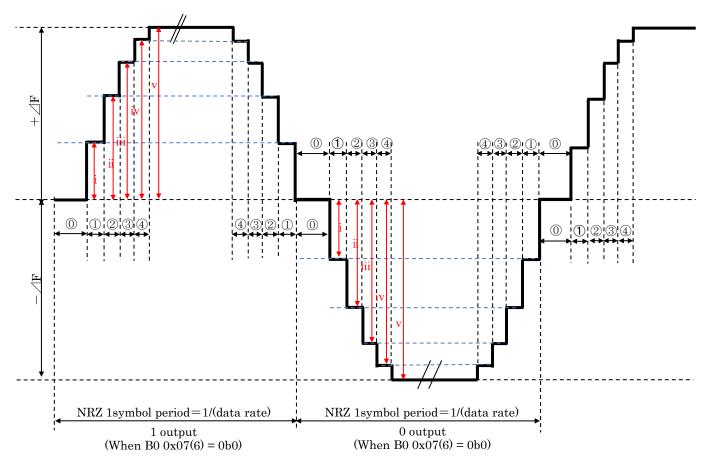

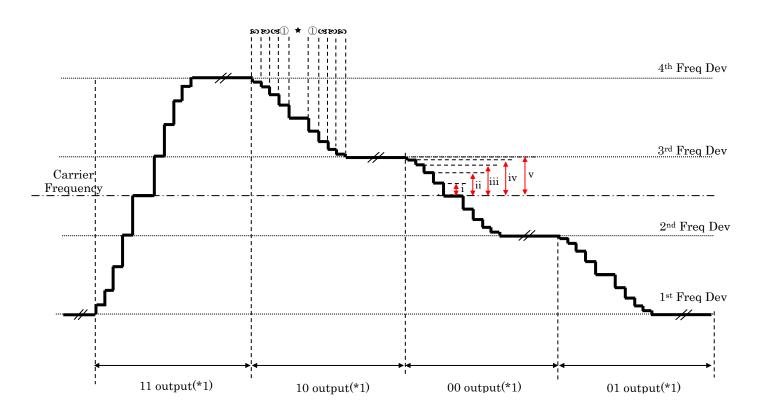

- Modulation : 4GFSK/4GMSK, GFSK/GMSK, 4FSK/FSK/MSK (MSK is FSK at modulation index =0.5)

- Data transmission rate: 1.2kbps to 300 kbps

- Data encoding/decoding by HW: NRZ, Manchester, 3-out-of-6

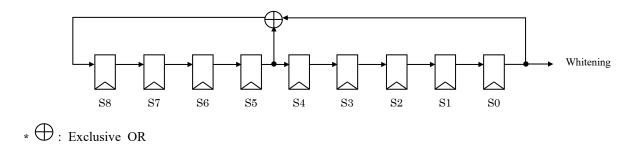

- Data Whitening by HW

- Programmable chnnel filters

- Programmable frequency diviation function

- TX/RX data inverse function

- TCXO direct input supported

- Programmable osillator's load capacitance

- Low speed clock adjustment function

- Frequency fine tuning function (using fractional N type PLL)

- On-chip TX PA

- TX Power 20mW /10mW/1mW selectable function

- TX power tuning function(±0.2dB)

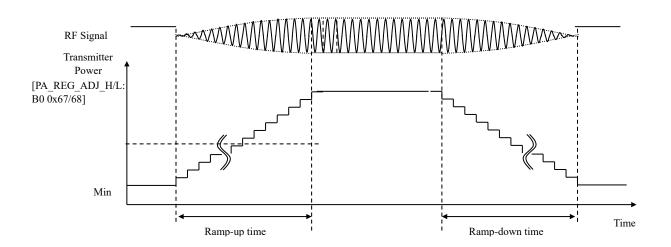

- TX power automatic ramping control

- External TX PA control function

- RSSI indicator and threshold judgment function

- High speed carrier checking function

- FEC function

- AFC function (IF frequency automatic adjustment by fractional N type PLL)

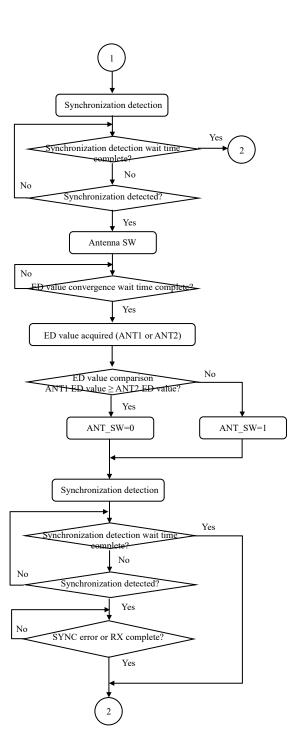

- Antenna diversity function

- Automatic Wake-up, auto SLEEP function

- General purpose timer(2ch)

- Test pattern generator(PN9, CW, 01 pattern、ALL"1"、ALL"0" output)

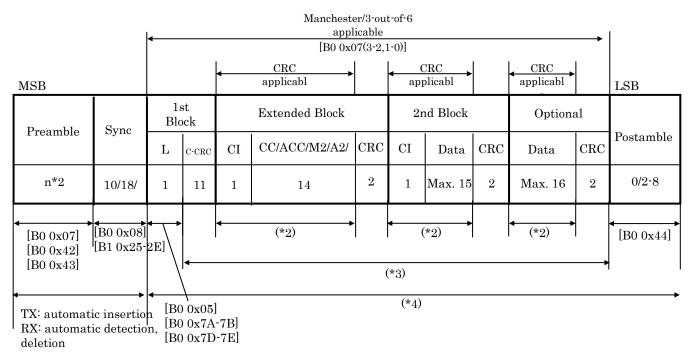

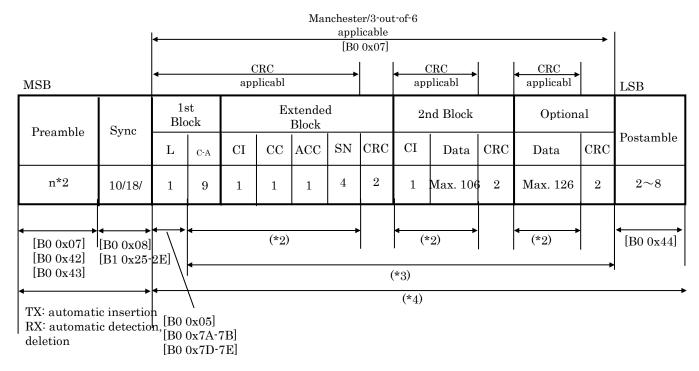

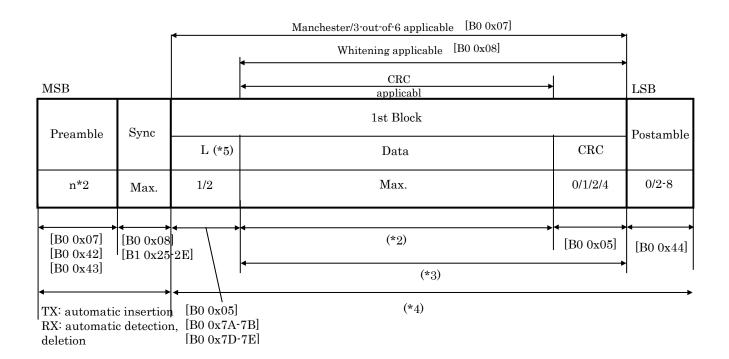

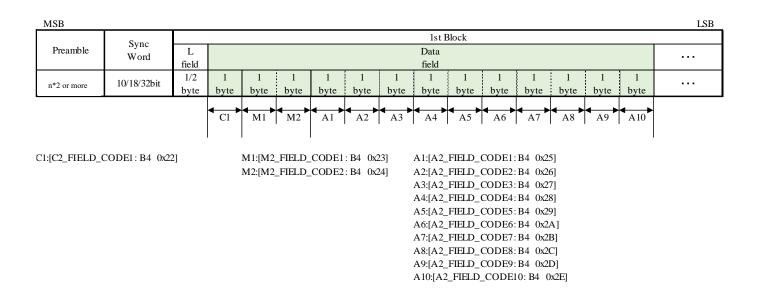

- Packet mode function

- ♦ IEEE802.15.4g packet format (Format C)

- ♦ Wireless M-Bus packet format(Format A/B)

- ♦ General purpose packet format (Format C/D)

- ♦ Max. 255byes (Format A/B), 2047bytes (Format C/D) packet length

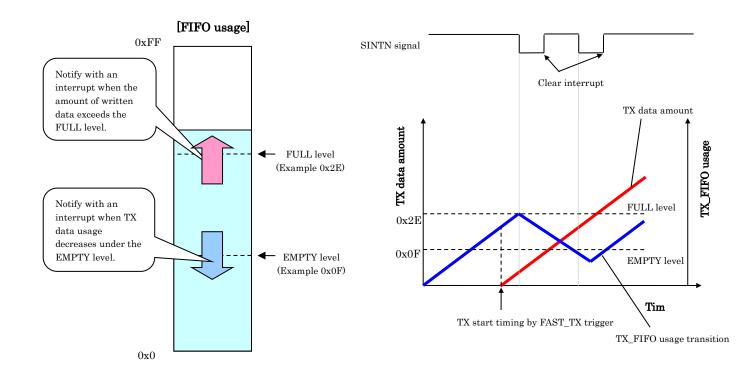

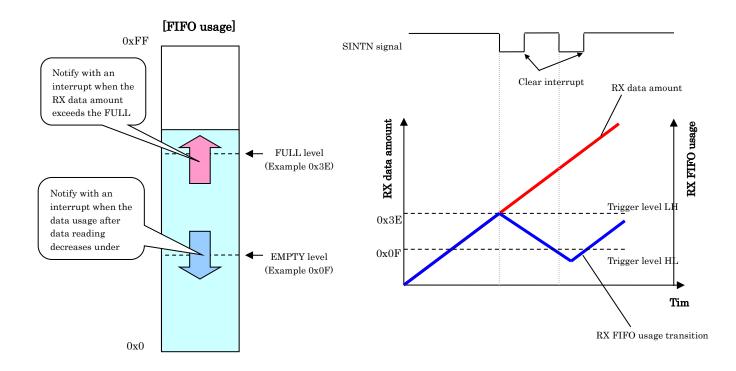

- ♦ TX FIFO(256bytes) , RX FIFO(256bytes)

- RX preamble pattern detection(Max. 4bytes)

- ♦ Automatic TX preamble length generator(Max 16383bytes)

- SyncWord setting function(Max4bytes x2type)

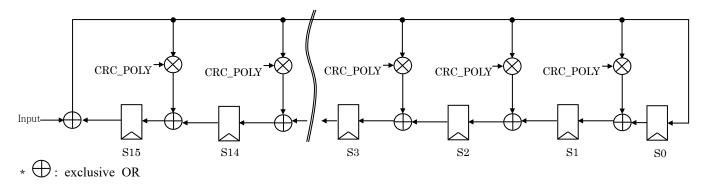

- Programable CRC function(CRC32/CRC16/CRC8 selectable, fully programmable polynomial)

- Address checking function (Max 13Bytes x3)

Wireless M-Bus field (C-field/M-field/A-field)

- IEEE802.15.4g (PANID/SHORT address/ 64bits address)

#### MCU

- ARM<sup>®</sup>Cortex<sup>®</sup>-M3 RISC processor(maximum speed: 81MHz)

- Memory Protection Unit(MPU)

- ♦ SysTick Timer

- Nested Vectored Interrupt Contoller (NVIC)

- ♦ Embedded Trace Macro (ETM)

- 1MB Flash ROM

- ♦ 512Kbytes ×2BANK

- ♦ 32Kbytes within 1MByte can be used as data area

- $\diamond$  1K erase cycles for program area/ 100K erase cycles for data aera, 10years data retention

- ♦ Write Protection/Read Protection (Flash Control)

- 256KBytes RAM(Multi banks, controllable data retention function for each banks during low power mode, minimus 1kBytes retention)

- ECC function for 32KBytes of 256Kbytes

- True Random Number Generator (TRNG)

- Cryptograph Accellarator (CRYPTO)

- ♦ AES(128/192/256bits, ECB/CBC/CFB/OFB/CTR/CCM/GCM/GMAC mode operation)

- ♦ SHA-1/SHA-224/SHA-256

- Secure Key Storage

- Universal Asynchronous Receiver Transceiver (UART) (Max 3ch)

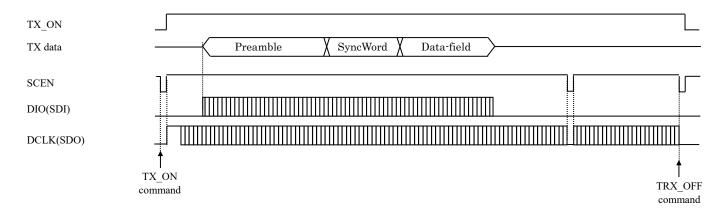

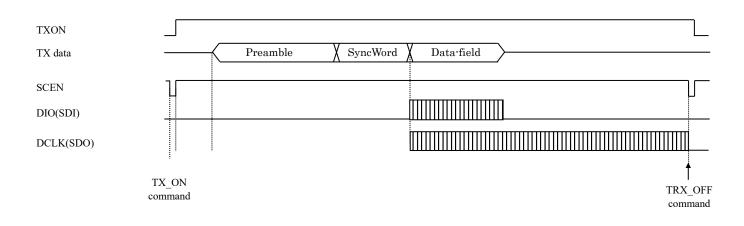

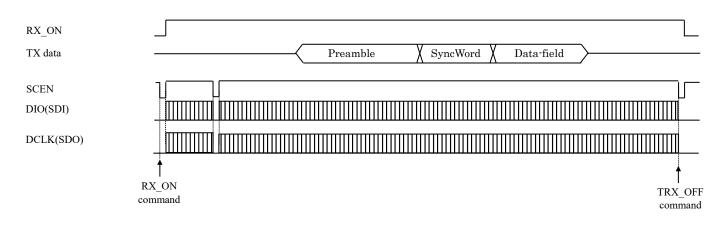

- Synchronous Serial Interface (SPI) (Max3ch)(1ch(SPI2) is for MCU/RF communication)

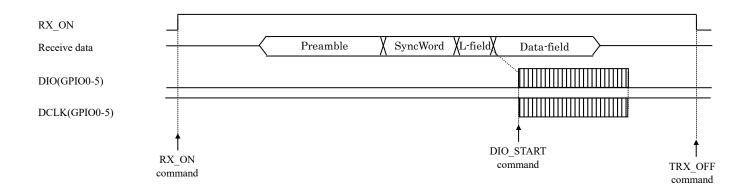

- Digital Interface for RFcontrol(DIO) (Max1ch)

- Watchdog Timer(WDT)

- General Purpose IO(GPIO)

- 32bit Timer %4ch(Timer)

- Real Time Clock(RTC)

- 32bit Flexible Timer(auto-reload/Compare/PWM/Capture mode)(FTM) 6ch

- I2C

Standard-Mode(100kHz)/ Fast-Mode(400kHz)/ Fast-Mode+(1MHz)/High Speed-Mode(3.4MHz)

- DMA Contoller (8ch)

- Serial Wire Debug Port(SWD)

- XTAL oscillator %32.768KHz

- PLL 32.768KHz(Xtal oscilator) \* 2475 or 64.86kHz(RF clockout)\*1249

- Analog-to-Digital Converter (ADC) 10bits SAR, 120ksps, 1ch (extensible 3ch depending on package)

- Power-on Reset (POR)

- RC oscillator

- Supply Voltage 2.6V to 3.6V

- ◆ Operation Temperature -40°C to 85°C(Operation Guarantee)

Current cosumption

| ТХ | 20mW | 28.8mA(CPU=1.26MHz)        |

|----|------|----------------------------|

|    | 1mW  | 12.8mA(CPU=1.26MHz)        |

| RX |      | 11.6mA (RF DCDC operation) |

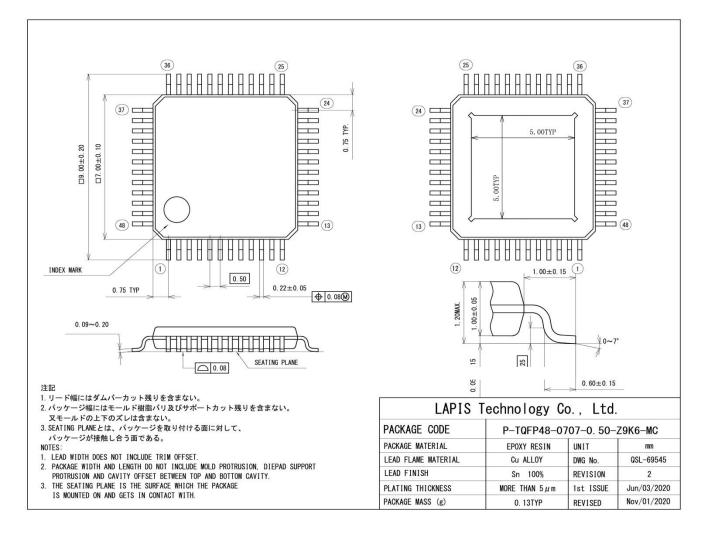

Package

48pin TQFP

Lead-free package conforming to RoHS

ARM<sup>®</sup>, Thumb, Cortex<sup>®</sup>, AHB and APB are registered trademarks of ARM Limited in the EU and other countries.

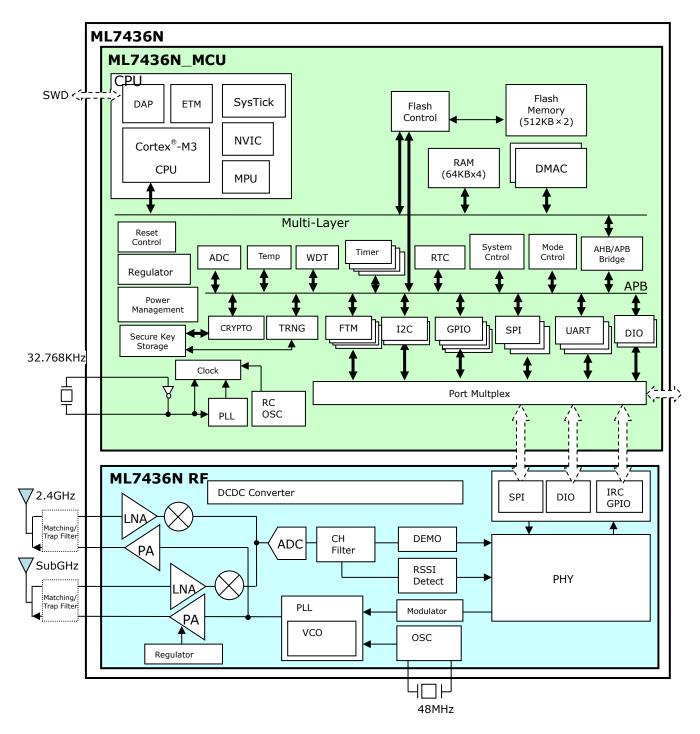

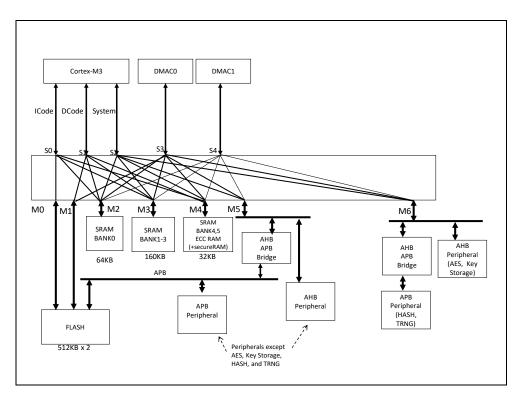

## ■2. Block Diagram

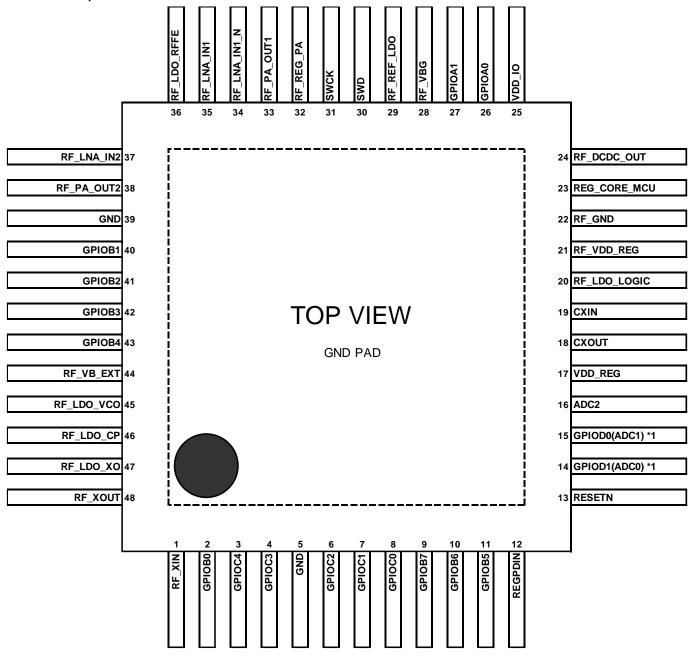

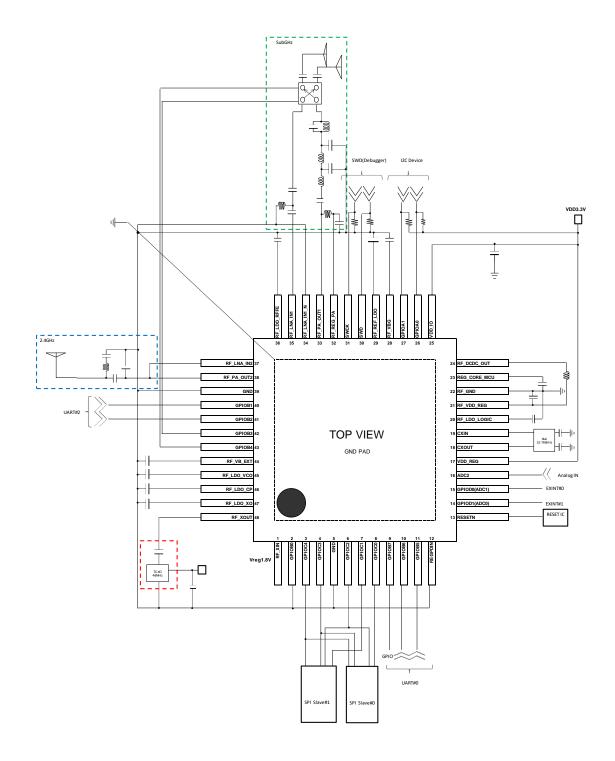

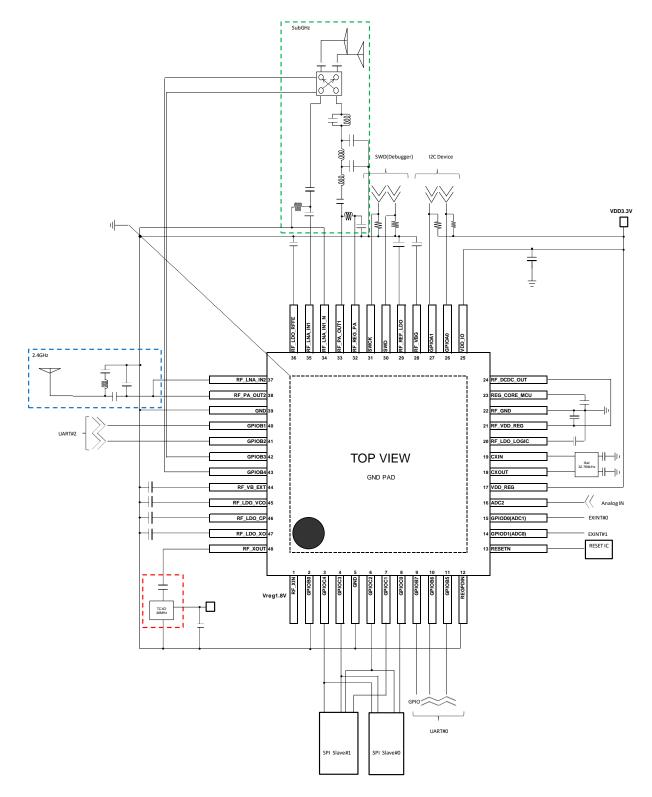

■3. Pin Layout

#### Table 3-1. Pin Table

| No.  | Port Name     | 1 <sup>st</sup> | 2 <sup>nd</sup> | 3 <sup>rd</sup> | 4 <sup>th</sup> | 5 <sup>th</sup> | 6 <sup>th</sup> | 7 <sup>th</sup> |

|------|---------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| 140. | No. Fort Name | Function        |

| 1    | RF_XIN        | RF_XIN          | -               | -               | -               | -               | -               | -               |

| 2    | GPIOB0        | GPIOB0          | RF_GPIO2        | -               | FTMA            | -               | -               | CLKOUT          |

|      |               |                 | UART0           | SPI1            | SPI01           | I2C0            |                 | RF_SDO          |

| 3    | GPIOC4        | GPIOC4          | RXD             | MISO            | MISO            | SCL             | -               |                 |

|    |              |              |           | SPI1 MOSI | SPI01  | I2C0 | RF_GPIO4   | RF_SDI  |

|----|--------------|--------------|-----------|-----------|--------|------|------------|---------|

| 4  | GPIOC3       | GPIOC3       | UART0 TXD |           | MOSI   | SDA  |            |         |

| 5  | GND          | -            | -         | -         | -      | -    | -          | -       |

|    |              |              | UART1     | SPI1      | SPI01  | I2C1 | RF_GPIO5   | RF_SCK  |

| 6  | GPIOC2       | GPIOC2       | RXD       | SCK       | SCK    | SCL  | 0.100      |         |

|    |              |              | UART1     | SPI1      | FTMF   | I2C1 | I2C0       | RF_SCEN |

| 7  | GPIOC1       | GPIOC1       | TXD       | SSN       | 1 1111 | SDA  | SDA        |         |

|    |              |              | UART2     | SPI0      | FTME   | I2C0 |            | RF_SDO  |

| 8  | GPIOC0       | GPIOC0       | RXD       | SSN       | FIME   | SCL  | -          |         |

|    |              |              | UART2     | SPI0      |        | I2C0 | I2C1       | RF_SDI  |

| 9  | GPIOB7       | GPIOB7       | TXD       | MISO      | FTMD   | SDA  | SDA        |         |

|    |              |              | UART0     | SPI0      |        | I2C1 |            | RF_SCK  |

| 10 | GPIOB6       | GPIOB6       | RXD       | MOSI      | FTMC   | SCL  | -          |         |

|    |              |              | UART0     | SPI0      |        | I2C1 |            | RF_SCEN |

| 11 | GPIOB5       | GPIOB5       | TXD       | SCK       | FTMB   | SDA  | -          |         |

| 12 | REGPDIN      | REGPDIN      | -         | -         | -      | -    | -          | -       |

| 13 | RESETN       | RESETN       | _         | -         | -      | -    | -          | -       |

|    | GPIOD1/ADC0  |              | UART0     |           |        | I2C1 |            |         |

| 14 | (*1)         | GPIOD1       | CTS       | -         | FTMF   | SCL  | -          | -       |

|    | GPIOD0/ADC1  |              | UART0     |           |        | I2C1 |            |         |

| 15 | (*1)         | GPIOD0       | RTS       | -         | FTME   | SDA  | -          | -       |

| 16 | ADC2         | _            | _         | _         | _      | _    | -          | -       |

| 17 | VDD_REG      | -            | _         | _         | _      | _    | _          | _       |

| 18 | CXOUT        | CXOUT        | -         | -         | _      | -    | -          | _       |

| 19 | CXIN         | CXIN         | _         | -         | _      | _    | -          | _       |

| 20 | RF_LDO_LOGIC | RF_LDO_LOGIC | -         | _         | _      | _    | -          | _       |

| 20 | RF_VDD_REG   | RF_VDD_REG   | -         | -         | -      | -    | -          | -       |

| 21 | RF_GND       | RF_GND       | -         | -         | -      | -    | -          | -       |

|    |              |              |           |           |        |      |            |         |

| 23 | REG_CORE_MCU | REG_CORE_MCU | -         | -         | -      | -    | -          | -       |

| 24 | RF_DCDC_OUT  | RF_DCDC_OUT  | -         | -         | -      | -    | -          | -       |

|    | VDD_IO       | VDD_IO       |           |           |        |      |            | -       |

| 25 | (RF/MCU)     | (RF/MCU)     | -         | -         | -      | -    | -          |         |

|    |              |              |           | SPI2      |        | I2C0 | ETM        | -       |

| 26 | GPIOA0       | GPIOA0       | RF_GPIO1  | MISO      | FTMC   | SDA  | TRACEDATA0 |         |

|    |              |              |          | SPI2 |       | I2C0 | ETM      | _          |

|----|--------------|--------------|----------|------|-------|------|----------|------------|

| 27 | GPIOA1       | GPIOA1       | RF GPIO0 | SSN  | FTMD  | SCL  | TRACECLK |            |

| 28 | RF_VBG       | RF_VBG       | -        | -    | -     | -    | -        | -          |

| 29 | RF_REF_LDO   | RF_REF_LDO   | -        | -    | -     | _    | -        | -          |

|    |              |              |          | SPI2 |       | I2C1 |          | -          |

| 30 | SWD          | SWD          | GPIOA2   | MOSI | FTMB  | SCL  | -        |            |

|    |              |              |          | SPI2 |       | I2C1 |          | -          |

| 31 | SWCK         | SWCK         | GPIOA3   | SCK  | FTMA  | SDA  | -        |            |

| 32 | RF_REG_PA    | RF_REG_PA    | -        | -    | -     | -    | -        | -          |

| 33 | RF_PA_OUT1   | RF_PA_OUT1   | -        | -    | -     | -    | -        | -          |

| 34 | RF_LNA_IN1_N | RF_LNA_IN1_N | -        | -    | -     | -    | -        | -          |

| 34 | RF_LNA_IN1   | RF_LNA_IN1   | -        | -    | -     | -    | -        | -          |

| 36 | RF_LDO_RFFE  | RF_LDO_RFFE  | -        | -    | -     | -    | -        | -          |

| 37 | RF_LNA_IN2   | RF_LNA_IN2   | -        | -    | -     | -    | -        | -          |

| 38 | RF_PA_OUT2   | RF_PA_OUT2   | -        | -    | -     | -    | -        | -          |

| 39 | GND          | -            | -        | -    | -     | -    | -        | -          |

|    |              |              | UART2    | SPI0 | FTMD  | I2C0 |          | RF_RESET   |

| 40 | GPIOB1       | GPIOB1       | TXD      | SSN  | FIMD  | SCL  | -        |            |

|    |              |              | UART2    | SPI0 | FTMC  | I2C0 | I2C1     | RF_REGPDIN |

| 41 | GPIOB2       | GPIOB2       | RXD      | MISO | Тімс  | SDA  | SDA      |            |

|    |              |              | UART1    | SPI0 | FTMB  | I2C1 | I2C0     | RF_GPIO2   |

| 42 | GPIOB3       | GPIOB3       | TXD      | MOSI | FIMD  | SCL  | SCL      |            |

|    |              |              | UART1    | SPI0 | FTM A | I2C1 |          | RF_GPIO3   |

| 43 | GPIOB4       | GPIOB4       | RXD      | SCK  | FTMA  | SDA  | -        |            |

| 44 | RF_VB_EXT    | RF_DSM_VREF  | -        | -    | -     | -    | -        | -          |

| 45 | RF_LDO_VCO   | RF_VB_EXT    | -        | -    | -     | -    | -        | -          |

| 46 | RF_LDO_CP    | RF_LDO_VCO   | -        | -    | -     | -    | -        | -          |

| 47 | RF_LDO_XO    | RF_LDO_CP    | -        | -    | -     | -    | -        | -          |

| 48 | RF_XOUT      | RF_XOUT      | -        | -    | -     | -    | -        | -          |

(\*1) Those pins are configured as package option (ADC0/1 or GPIOD1/0). On GPIOD1/0 configured product,  $1^{st}-7^{th}$  function can be used. On ADC0/1 configured products, they are analog input only.

## ■4. Pin Description

Input/Output definition

- I :Digital input

- O :Digital output

- Is :Schmitt trigger input

- O<sub>D</sub> :Open drain

- O<sub>A</sub> :Analog output

- O<sub>AH</sub> :Analog output2

- I<sub>A</sub> :Analog input

- IO<sub>A</sub> :Analog inout

- I<sub>RF</sub> :RF input

- O<sub>RF</sub> :RF output

- $I_{OSL}$  :32.768KHz osillator input

- O<sub>OSL</sub> :32.768KHz osillator output

#### Input/Output attribute definition

- I :Input

- O :Output

- oZ :High-impedance output

## 4-1. Power/Ground

| Pin    | IO     | Active<br>Level | Attribute/Value<br>At reset | Description                                              |

|--------|--------|-----------------|-----------------------------|----------------------------------------------------------|

| VDDIO  | Power  | -               | -                           | Power supply for digital IO (2.6 to 3.6V)(MCU/RF common) |

| RF_GND | Ground | -               | -                           | Ground for RF.                                           |

| GND    | Ground | -               | -                           | Common Ground                                            |

## 4-2. Regulator Interface

| Pin          | IO | Active<br>Level | Attribute/Value<br>At reset | Description                                                    |

|--------------|----|-----------------|-----------------------------|----------------------------------------------------------------|

| REGPDIN      | Ι  | Н               | I / -                       | Regulator power down control(Fixed to Low in normal operation) |

| VDD_REG      | _  | -               | -                           | Power supply for Regulator (Typ:<br>3.3V)(MCU)                 |

| REG_CORE_MCU | -  | -               | -                           | Regulator output(Typ: 1.2V)(MCU))                              |

| RF_VBG       | -  | -               | -                           | C connect pin(RF))                                             |

| RF_DCDC_OUT  | -  | -               | -                           | Switching regulator output (RF)                                |

| RF_VDD_REG   | -  | -               | -                           | Switching regulator input(RF)                                  |

| RF_REG_PA    | -  | -               | -                           | PA regulator output (RF)                                       |

| RF_REF_LDO   | -  | -               | -                           | Linear regulator reference voltage<br>output(RF)               |

| RF_LDO_RFFE  | -  | -               | -                           | RFFR circuit Linear regulator output(RF)                       |

| RF_LDO_CPO   | -  | -               | -                           | CP circuit Linear regulator output(RF)                         |

| RF_LDO_VCO   | -  | -               | -                           | VCO circuit Linear regulator output(RF)                        |

| RF_LDO_XO    | -  | -               | -                           | Oscillator circuit Linear regulator<br>output(RF)              |

| RF_LDO_LOGIC | -  | -               | -                           | Logic circuit Linear regulator output(RF)                      |

## 4-3. RF Interface

| Pin          | IO             | Active<br>Level | Attribute/Value<br>At reset | Description                                      |

|--------------|----------------|-----------------|-----------------------------|--------------------------------------------------|

| RF_PA_OUT1   | Orf            | -               | -                           | RF Antenna output pin (160M - 920MHz)            |

| RF_LNA_IN1   | IA             | -               | I / -                       | RF Antenna input pin (160M - 920MHz)             |

| RF_LNA_IN1_N | I <sub>A</sub> | -               | I / -                       | RF Antenna input pin (160M - 920MHz)             |

| RF_PA_OUT2   | Orf            | -               | -                           | RF Antenna output pin (2.4GHz)                   |

| RF_LNA_IN2   | I <sub>A</sub> | -               | I / -                       | RF Antennainput pin (2.4GHz)                     |

| RF_VB_EXT    | Ioa            | -               | -                           | Internal bias smoothing capacitor connection pin |

## 4-4. MCU Interface

| Pin    | ΙΟ   | Active<br>Level | Attribute/Value<br>At reset | Description                                      |

|--------|------|-----------------|-----------------------------|--------------------------------------------------|

|        | I/O  | -               | oZ / -                      | 1st : General Purpose IO(GPIOA0)                 |

|        | 0    | -               | -                           | 2nd : RF General Purpose IO(RF_GPIO1)(Clock out) |

| CDIOAO | I/O  | -               | -                           | 3rd : SPI2 MISO                                  |

| GPIOA0 | I/O  | -               | -                           | 4th : Flexible TimerC I/O (FTMC_IO)              |

|        | I/Od | -               | -                           | 5th : I2C0 serial data (I2C0 SDA)                |

|        | 0    | -               | -                           | 6th : ETM TRACEDATA0                             |

|        | I/O  | -               | oZ / -                      | 1st : General Purpose IO(GPIOA1)                 |

|        | 0    | -               | -                           | 2nd : General Purpose IO (RF_GPIO0)(SINTN)       |

| GPIOA1 | I/O  | L               | -                           | 3rd : SPI2 SSN                                   |

| GPIOAI | I/O  | -               | -                           | 4th : Flexible TimerD I/O (FTMD_IO)              |

|        | I/Od | -               | -                           | 5th : I2C0 serial clock(I2C0 SCL)                |

|        | 0    | -               | -                           | 6th : ETM TRACECLK                               |

|        | I/O  | -               | I / -                       | 1st : Serial wire debug port data(SWD)           |

|        | I/O  | -               | -                           | 2nd : General Purpose IO(GPIOA2)                 |

| SWD    | I/O  |                 |                             | 3rd : SPI2 MOSI                                  |

|        | I/O  |                 |                             | 4th : Flexible TimerB I/O (FTMB_IO)              |

|        | I/Od | -               | -                           | 5th : I2C1 serial clock(I2C1 SCL)                |

| SWCK   | I/O  | -               | I / -                       | 1st : Serial wire debug port clock(SWCK)         |

| SWCK   | I/O  | -               | -                           | 2nd : General Purpose IO(GPIOA3)                 |

|        | I/O  | - | -      | 3rd : SPI2 SCK                                      |

|--------|------|---|--------|-----------------------------------------------------|

|        | I/O  |   |        | 4th : Flexible TimerA I/O (FTMA_IO)                 |

|        | I/Od | - | -      | 5th : I2C1 serial data(I2C1 SDA)                    |

|        |      |   |        | 1st : General Purpose IO (GPIOB0)                   |

|        |      |   |        | Use this pin for MCU mode detection during power on |

| GPIOB0 | I/O  | - | I / -  | reset sequence.                                     |

|        |      |   |        | L level at power on: normal mode                    |

|        |      |   |        | H Level at power on: ISP mode                       |

|        | I/O  | - | oZ / - | 1st : General Purpose IO (GPIOB1)                   |

|        | 0    | L | -      | 2nd : UART2 transmit data(UART2_TXD)                |

| GPIOB1 | I/O  | L | -      | 3rd : SPI0 SSN                                      |

|        | I/O  | - | -      | 4th : Flexible TimerD I/O(FTMD_IO)                  |

|        | I/Od | - | -      | 5th : I2C0 serial clock(I2C0 SCL)                   |

| Pin    | IO   | Active<br>Level | Attribute/Value<br>At reset | Description                          |

|--------|------|-----------------|-----------------------------|--------------------------------------|

|        | I/O  | -               | oZ / -                      | 1st : General Purpose IO (GPIOB2)    |

|        | Ι    | -               | -                           | 2nd : UART2 receive data(UART1_TXD)  |

| GPIOB2 | I/O  | -               | -                           | 3rd : SPI0 MISO                      |

| GPIOBZ | I/O  | -               | -                           | 4th : Flexible TimerC I/O (FTMC_IO)  |

|        | I/Od | -               | -                           | 5th : I2C0 serial data(I2C0 SDA)     |

|        | I/Od | -               | -                           | 6th : I2C1 serial data(I2C1 SDA)     |

|        | I/O  | -               | oZ / -                      | 1st : General Purpose IO (GPIOB3)    |

|        | 0    | -               | -                           | 2nd : UART1 transmit data(UART1_TXD) |

| GPIOB3 | I/O  | -               | -                           | 3rd : SPI0 MOSI                      |

| GPIOB3 | I/O  | -               | -                           | 4th : Flexible TimerB I/O (FTMB_IO)  |

|        | I/Od | -               | -                           | 5th : I2C1 serial clock(I2C1 SCL)    |

|        | I/Od | -               | -                           | 6th : I2C0 serial clock(I2C0 SCL)    |

|        | I/O  | -               | oZ / -                      | 1st : General Purpose IO (GPIOB4)    |

|        | Ι    | -               | -                           | 2nd : UART1 receive data(UART1_RXD)  |

| GPIOB4 | I/O  | -               | -                           | 3rd : SPI0 SCK                       |

|        | I/O  | -               | -                           | 4th : Flexible TimerA I/O (FTMA_IO)  |

|        | I/Od | -               | -                           | 5th : I2C1 serial data(I2C1 SDA)     |

| CDIODE | I/O  | -               | oZ / -                      | 1st : General Purpose IO (GPIOB5)    |

| GPIOB5 | 0    | -               | -                           | 2nd : UART0 transmit data(UART0_TXD) |

|        | I/O  | _ | _      | 3rd : SPI0 SCK                        |

|--------|------|---|--------|---------------------------------------|

|        | I/O  |   |        | 4th : Flexible TimerB I/O (FTMB IO)   |

|        | -    |   |        |                                       |

|        | I/Od | - | -      | 5th : I2C1 serial data(I2C1 SDA)      |

|        | I/O  | - | oZ / - | 1st : General Purpose IO (GPIOB6)     |

|        | Ι    | - | -      | 2nd : UART0 receive data(UART0_RXD)   |

| GPIOB6 | I/O  | - | -      | 3rd : SPI0 MOSI                       |

|        | I/O  | - | -      | 4th : Flexible TimerC I/O (FTMC_IO)   |

|        | I/Od | - | -      | 5th : I2C1seridal clock(I2C1 SCL)     |

|        | I/O  | - | oZ / - | 1st : General Purpose IO (GPIOB7)     |

|        | 0    | - | -      | 2nd : UART2 transmit data (UART2_TXD) |

| 001007 | I/O  | - | -      | 3rd : SPI0 MISO                       |

| GPIOB7 | I/O  | - | -      | 4th : Flexible TimerD I/O (FTMD_IO)   |

|        | I/Od | - | -      | 5th : I2C0 serial data(I2C0 SDA)      |

|        | I/Od | - | -      | 6th : I2C1 serial data(SDA)           |

| Pin    | IO   | Active<br>Level | Attribute/Value<br>At reset | Description                                    |

|--------|------|-----------------|-----------------------------|------------------------------------------------|

|        | I/O  | -               | oZ / -                      | 1st : General Purpose IO(GPIOC0)               |

|        | Ι    | -               | -                           | 2nd : UART2 receive data(UART2_RXD)            |

| GPIOC0 | I/O  | L               | -                           | 3rd : SPI0 slave select(SPI0_SSN)              |

|        | I/O  | -               | -                           | 4th : Flexible TimerE I/O(FTME_IO)             |

|        | I/Od | -               | -                           | 5th : I2C0 serial clock(I2C0_SCL)              |

|        | I/O  | -               | oZ / -                      | 1st : General Purpose IO(GPIOC1)               |

|        | 0    | -               | -                           | 2nd : UART1 transmit data(UART1_TXD)           |

|        | I/O  | L               | -                           | 3rd : SPI1 slave select(SPI1_SSN)              |

| GPIOC1 | I/O  | -               | -                           | 4th : Flexible TimerF I/O (FTMF_IO)            |

|        | I/Od | -               | -                           | 5th : I2C1 serial data(I2C1_SDA)               |

|        | I/Od | -               | -                           | 6th : I2C0 serial data(I2C0_SDA)               |

|        | I/O  | -               | oZ / -                      | 1st : General Purpose IO(GPIOC2)               |

|        | Ι    | -               | -                           | 2nd : UART1 receive data (UART1_RXD)           |

| GPIOC2 | I/O  | -               | -                           | 3rd : SPI1 serial clock(SPI1_SCK)              |

|        | I/O  | -               | -                           | 4th : SPI0/SPI1 shared serial clock(SPI01_SCK) |

|        | I/Od | -               | -                           | 5th : I2C1 serial clock(I2C1_SCL)              |

| CDIOCO | I/O  | -               | oZ / -                      | 1st : General Purpose IO(GPIOC3)               |

| GPIOC3 | 0    | -               | -                           | 2nd : UART0 transmit data (UART1_TXD)          |

|        | I/O  | - | -      | 3rd : SPI1 Master Out/Slave In(SPI1_MOSI)               |

|--------|------|---|--------|---------------------------------------------------------|

|        | I/O  | - | -      | 4th : SPI0/SPI1 shared Master Out/Slave In(SPI01_MOSI)  |

|        | I/Od | - | -      | 5th : I2C1 serial data(I2C1_SDA)                        |

|        | I/O  | - | oZ / - | 1st : General Purpose IO(GPIOC4)                        |

|        | 0    | L | -      | 2nd : UART0 receive data(UART0_RXD)                     |

| GPIOC4 | I/O  | - | -      | 3rd : SPI1 Master In/Slave Out (SPI1_MISO)              |

|        | I/O  | - | -      | 4th : SPI0/SPI1 shared Master In/Slave Out (SPI01_MISO) |

|        | I/Od | - | -      | 5th : I2C0 serial clock (I2C0_SCL)                      |

| Pin    | IO         | Active<br>Level | Attribute/Value<br>At reset | Description                            |

|--------|------------|-----------------|-----------------------------|----------------------------------------|

|        | I/O        | -               | oZ / -                      | 1st : General Purpose IO(GPIOD0)       |

| CRIODO | 0          | L               | -                           | 2nd : UART0 request to send(UART0_RTS) |

| GPIODU | GPIOD0 I/O | -               | -                           | 4th : Flexible TimerE I/O(FTME_IO)     |

|        | I/Od       | -               | -                           | 5th : I2C1 Serial data(I2C0_SDA)       |

|        | I/O        | -               | oZ / -                      | 1st : General Purpose IO(GPIOD1)       |

| GPIOD1 | Ι          | L               | -                           | 2nd : UAR01 Clear to send(UART0_CTS)   |

| GPIODI | I/O        | -               | -                           | 4th : Flexible TimerF I/O(FTMF_IO)     |

|        | I/Od       | _               | _                           | 5th : I2C1 serial clock(I2C0_SCL)      |

## 4-5. Others

| Pin     | ΙΟ  | Active<br>Level | Attribute/Value<br>At reset | Description                         |

|---------|-----|-----------------|-----------------------------|-------------------------------------|

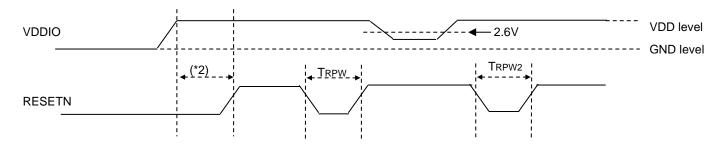

| RESETN  | Is  | L               | I / -                       | RESET                               |

| RF_XIN  | IA  | P or N          | I / -                       | 48MHz Xtal Oscillator(IN)(RF)       |

| RF_XOUT | ΟΑ  | P or N          | -                           | 48MHz Xtal Oscillator(OUT)(RF)      |

| CXIN    | Ios | P or N          | I                           | 32.768kHz Xtal Oscillator(IN)(MCU)  |

| CXOUT   | Oos | P or N          | 0                           | 32.768kHz Xtal Oscillator(OUT)(MCU) |

| ADC2    | IA  | -               | I / -                       | ADC input                           |

#### 4-6. Handling of Unused pins

See below for handling of unused pins.

| Pin name     | Recommended treatment                        |

|--------------|----------------------------------------------|

| SWCK/SWD     | Connect pull-down or pull-up register (*2)   |

| GPIOB0       | Connect pull-down register or Tie Low(*1)    |

| GPIO*(except | open                                         |

| GPIB0)       |                                              |

| ADC2         | open                                         |

| XIN          | open (To be used when the TCXO is connected) |

#### (\*1)

Connect Ground or small pull-down register in order to stable Low level during power-on sequence. (\*2)

Connect pull-up or pull-down register.

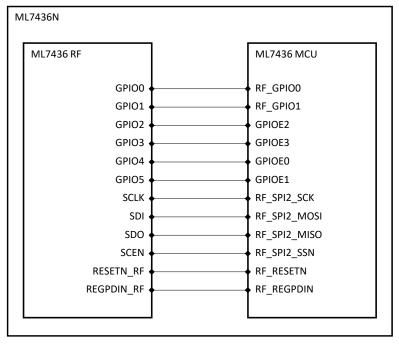

#### 4-7. Internal pins

ML7436N is configured by RF and MCU. This chapter explains the internal pins.

The following figure shows each chips connection.

#### 4-7-1. MCU

| Pin          | IO  | Active<br>Level | Attribute/Value<br>At reset | Description                                          |

|--------------|-----|-----------------|-----------------------------|------------------------------------------------------|

|              | Ι   | -               | oZ / -                      | 1st : External interrupt input pin (EXTINT function) |

| RF_GPIO0     | I/O | -               | -                           | 4th : General purpose IO (GPIOF0)                    |

|              | I   | -               | oZ / -                      | 1st : External interrupt input pin (EXTINT function) |

| RF_GPIO1     | I/O | -               | -                           | 4th : General purpose IO (GPIOF1)                    |

|              | Ι   | -               | oZ / -                      | 1st : External interrupt input pin (EXTINT function) |

| GPIOE2       | I/O | -               | -                           | 4th : General purpose IO (GPIOF2)                    |

| GPIOE3       | Ι   | -               | oZ / -                      | 1st : External interrupt input pin (EXTINT function) |

| GPIOES       | I/O | -               | -                           | 4th : General purpose IO (GPIOF3)                    |

|              | Ι   | -               | oZ / -                      | 1st : External interrupt input pin (EXTINT function) |

| GPIOE0       | I/O | -               | -                           | 2ns : DIO0 DATA                                      |

|              | I/O | -               | -                           | 4th : General purpose IO (GPIOF4)                    |

|              | Ι   | -               | oZ / -                      | 1st : External interrupt input pin (EXTINT function) |

| GPIOE1       | Ι   | -               | -                           | 2nd : DIO0 CLK                                       |

|              | I/O | -               | -                           | 4th : General purpose IO (GPIOF5)                    |

| RF_SPI2_SCK  | I/O | -               | O/L                         | 1st : SPI2 SCK                                       |

|              | I/O | -               | O/L                         | 1st : SPI2 MOSI                                      |

| RF_SPI2_MOSI | I/O | -               | -                           | 2nd : DIO0 DATA                                      |

|              | I/O | -               | oZ / -                      | 1st : SPI2 MISO                                      |

| RF_SPI2_MISO | Ι   | -               | -                           | 2nd : DIO0 CLK                                       |

| RF_SPI2_SSN  | I/O | -               | O/H                         | 1st : SPI2 SSN                                       |

| RF_RESETN    | 0   | -               | O/L                         | RF chip reset control pin                            |

| RF_REGPDIN   | 0   | -               | O/L                         | RF chip regulator power down control pin             |

#### 4-7-2. RF

| Pin | IO | Active Level | During the<br>RF resetting | The initial<br>value after RF<br>resetting | Description |

|-----|----|--------------|----------------------------|--------------------------------------------|-------------|

|-----|----|--------------|----------------------------|--------------------------------------------|-------------|

|            |       |              |      |                                     | 1                                               |

|------------|-------|--------------|------|-------------------------------------|-------------------------------------------------|

|            |       |              |      |                                     | Digital input/output pin                        |

| GPIO0      | I/O   | H or L or OD | oZ/- | O/L                                 | Initial function: Interrupt notification signal |

|            |       |              |      |                                     | output                                          |

| GPIO1      | I/O   | H or L or OD | oZ/- | O/Clock                             | Digital input/output pin                        |

| GFIOI      | 1/0   |              | 02/- | U/ CIUCK                            | Initial function: Clock out                     |

|            |       |              |      |                                     | Digital input/output pin                        |

| GPIO2      | I/O   | H or L or OD | oZ/- | O/Clock                             | Initial function: Antenna switching control     |

|            |       |              |      |                                     | signal output                                   |

| CDIO2      | 1/0   |              | .7/  | 0/1                                 | Digital input/output pin                        |

| GPIO3      | I/O   | H or L or OD | oZ/- | O/L                                 | Initial function: TX/RX switching signal output |

| 0010.4     | 1/0   |              |      | o."                                 | Digital input/output pin                        |

| GPIO4      | I/O   | H or L or OD | oZ/- | O/L                                 | Initial function: Data (DIO DATA)               |

|            | - / - |              | _/   | - // ·                              | Digital input/output pin                        |

| GPIO5      | I/O   | H or L or OD | oZ/- | O/H                                 | Initial function: Data (DIO DCLK)               |

| SCLK       | Is    | -            | oZ/- | I                                   | SPI clock input pin                             |

| SDI        | Is    | -            | oZ/- | I SPI data input pin / DIO DATA pin |                                                 |

|            |       |              |      |                                     | SPI data output pin / DCLK output pin           |

|            |       |              |      |                                     | * OpenDrain output is the initial setting.      |

| SDO        | 0     | -            | oZ/- | Ι                                   | Set SDO_OD([SPI/EXT_PA_CTRL:B0                  |

|            |       |              |      |                                     | 0x53(7)])=0b0 when SDO pin is used as output    |

|            |       |              |      |                                     | pin before SPI reading operation.               |

|            |       |              |      |                                     | SPI chip enable pin                             |

| SCEN       | Is    | L            | oZ/- | Ι                                   | L: Enable                                       |

|            |       |              |      |                                     | H: Disable                                      |

|            |       |              |      |                                     | Reset pin                                       |

|            |       |              |      |                                     | L: Operation stop                               |

| RESETN_RF  | Is    | L            | Ι    | Ι                                   | H: Executable                                   |

|            |       |              |      |                                     | *LSI is reset when RESETN_RF is set to $``L''$  |

|            |       |              |      |                                     | Set "L" when RF set DEEPSLEEP                   |

|            |       |              |      |                                     | Regulator power down control pin                |

| REGPDIN_RF | Is    | Н            | Ι    | Ι                                   | *Set "L" at normal operation.                   |

|            |       |              |      |                                     | Set "H" when RF set DEEPSLEEP                   |

## 4-7-3. Handling of Unused pins (Internal pins)

#### Handling of unused pins

| Pin name | Recommended treatment    |

|----------|--------------------------|

| RF GPIO0 | MCU RF_GPIO0=oZ(default) |

| RF GPIO1 | MCU RF_GPIO1=oZ(default) |

| RF GPIO2 | MCU GPIOE2=oZ(default)   |

| RF GPIO3 | MCU GPIOE3=oZ(default)   |

| RF GPIO4 | MCU GPIOE0=oZ(default)   |

| RF GPIO5 | MCU GPIOE1=oZ(default)   |

#### <Note>

\*1. GPIO1 pin's initial state is clock output (CLK\_OUT function). When the clock output function is unnecessary, set [GPIO1\_CTRL: B0 0x4F] bit2-0=0b000. The setting stops clock output. RF GPIO1 pin's state is clock output and MCU is set to open, it causes RF receive sensitivity deterioration.

## ■5. Electrical Characteristics

## 5-1. Absolute Maximum Ratings

| Under Ta=-40 to +85°C. | GND=0V, if any special  | condition is not described. |

|------------------------|-------------------------|-----------------------------|

|                        | UND-UV, II dily special |                             |

| Item                      | Symbol | Conditions          | Rating       | Unit |

|---------------------------|--------|---------------------|--------------|------|

| Power supply I/O (*1)     | VDDIO  | _                   | -0.3 to +4.6 | V    |

| RF input voltage          | PRFI   | Antenna input at RX | 0            | dBm  |

| RF output voltage         | VRFO   | _                   | -0.3 to +4.6 | V    |

| Digital input voltage     | VDIN   | _                   | -0.3 to 5.8  | V    |

| Analog input voltage(*2)  | VAIN   | _                   | -0.3 to 1.8  | V    |

| Digital output voltage    | VDO    | _                   | -0.3 to 4.6  | V    |

| Analog output             | VAO    | _                   | -0.3 to 1.8  | V    |

| Analog output voltage2    | VAO2   | —                   | -0.3 to 4.6  | V    |

| Digital input current     | IDI    | _                   | -10 to +10   | mA   |

| Analog input current (*2) | IAI    | _                   | -2 to +2     | mA   |

| Digital output current    | IDO    | _                   | -8 to +8     | mA   |

| Analog output current(*3) | IAO    | _                   | -2 to +2     | mA   |

| Analog output current2    | IAO2   | _                   | -2 to +2     | mA   |

| Power dissipation         | PD     | Ta=+25°C            | 1            | W    |

| Storage Temperature       | Tstg   | —                   | -55 to +150  | °C   |

(\*1) VDDIO\_MCU、VDD\_REG\_MCU

(\*2) RF\_XIN、CXIN

(\*3) RF\_XOUT、CXOUT

#### 5-2. Recommended operation conditions

| Item                      | Symbol | Conditions             | MIN    | ТҮР    | MAX    | UNIT |

|---------------------------|--------|------------------------|--------|--------|--------|------|

| Power supply voltage(I/O) |        |                        |        |        |        |      |

| VDDIO and                 | VDDIO  |                        | 2.6    | 3.3    | 3.6    | V    |

| VDD_REG_MCU               |        |                        |        |        |        |      |

| Operating temperature     | Та     | -                      | -40    | +25    | +85    | °C   |

| Digital input rise time   | tIR1   | Digital input (*1)     | -      | -      | 20     | ns   |

| Digital input fall time   | tIF1   | Digital input (*1)     | -      | -      | 20     | ns   |

| Digital output load       | CDL    | All digital output pin | _      | _      | 20     | pF   |

| Slow Clock                |        |                        | -20pp  |        | +20pp  |      |

| 32.768kHz Xtal Frequency  | FXCK1  | CXIN,CXOUT             | m (*2) | 32.768 | m (*2) | kHz  |

| IOSC Clock                |        |                        |        |        |        |      |

| Internal high-speed RC    | FICK1  |                        | -10%   | 16     | +10%   | MHz  |

| IOSC Clock                |        |                        |        |        |        |      |

| Internal low-speed RC     | FICK2  |                        | -10%   | 32     | +10%   | kHz  |

| RF Master Frequency       | FMCK1  | RF_XIN/RF_XOUT         | 30     | 48     | 52     | MHz  |

| RF Master clock Acculancy | ACMCK1 |                        | (*4)   | (*4)   | (*4)   | ppm  |

| RF Xtal Equivalent series | _      |                        |        |        |        |      |

| resistance                | Esr    |                        | _      | _      | 80     | ohm  |

|                           |        |                        | 389    | _      | 80     | MHz  |

| RF channel Frequency      | FRF    | -                      | 778    | _      | 1100   | MHz  |

|                           |        |                        | 2402.0 | _      | 2483.5 | MHz  |

(\*1) Pins described as I or Is in the Input/output column in "Pin Description".

(\*2) These values are provided under the condition of 25 °C. Under the condition of -40 to 85 °C, the maximum value is +150 ppm, and the minimum value -150 ppm.

- (\*3) In case of TX operation, this value is specified by minimum value of VDDIO.

- (\*4) Indicating frequency deviation during TX-RX operation. In order to support various standards, apply the frequency accuracy for each standard to meet the requirements as described below.

| Specification               | Required Accuracy |

|-----------------------------|-------------------|

| ARIB STD-T108               | ±20 ppm           |

| RCR STD-30 type III (Japan) | ±10 ppm           |

| RCR STD-30 type IV (Japan)  | ±4 ppm            |

| Wireless M-Bus F mode       | ±16 ppm           |

[Notices]

The electrical characteristics are measured under the recommended operating conditions above, unless otherwise specially noted.

The timings are measured at the 20 % and 80 % levels of VDDIO, unless otherwise specially noted.

## 5-3. Common Characteristics

| Item                                                         | Symbol   | Conditions/Pins                                           | MIN            | TYP(*2) | MAX(*11)       | Unit |

|--------------------------------------------------------------|----------|-----------------------------------------------------------|----------------|---------|----------------|------|

| Supply<br>Current(*1)                                        | IDD_IDLE | MCU : Active (*10)<br>RF : RF Sleep state 1               | _              | 1.3     | 9.9            | mA   |

|                                                              | IDD_RX   | MCU : Active(*10)<br>RF : RX Operation (*5)(*6)           | -              | 11.6    | 32.3           | mA   |

|                                                              | 100_101  | MCU : Active(*10)<br>RF : RX Operation (*5)(*7)           | -              | 17.9    | 33.9           | mA   |

|                                                              | IDD_TX1  | MCU : Active(*10)<br>RF : TX Operation(1mW) (*5)<br>(*6)  | -              | 12.8    | 39.5           | mA   |

|                                                              |          | MCU : Active(*10)<br>RF : TX Operation(20mW)<br>(*5) (*6) | -              | 28.8    | 67.5           | mA   |

|                                                              | IDD_TX20 | MCU : Active(*10)<br>RF : TX Operation(20mW)<br>(*5) (*6) | -              | 44.3    | 67.5           | mA   |

|                                                              |          | MCU : Active(*10)<br>RF : TX Operation(20mW)<br>(*5) (*7) | -              | 39.3    | 69.5           | mA   |

| High level input<br>voltage (*12)                            | VIH1     | Digital input                                             | VDDIOx0.7<br>5 | _       | 5.5            | V    |

| High level input<br>voltage (*13)                            | VIH2     | Digital input                                             | VDDIOx0.7<br>5 | _       | VDDIO          | V    |

| Low level input<br>voltage                                   | VIL1     | Digital input                                             | 0              | _       | VDDIOx0.1<br>8 | V    |

| Schmitt trigger<br>high level<br>decision<br>threshold value | VT+      | Digital pin with schmit<br>trigger                        | _              | _       | VDDIOx0.7<br>5 | V    |

| Schmitt trigger<br>low level<br>decision<br>threshold value | VT-   | Digital pin with schmit<br>trigger                                                                                                                                                                                                                                              | VDDIOx0.1<br>8 | _ | _     | V  |

|-------------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---|-------|----|

| Input leakage                                               | IIH1  | Digital input                                                                                                                                                                                                                                                                   | -1             | _ | 1     | μA |

| Current                                                     | IIH2  | XIN, CXIN                                                                                                                                                                                                                                                                       | -0.3           | _ | 0.3   | μA |

|                                                             | IIL1  | Digital input                                                                                                                                                                                                                                                                   | -1             | _ | 1     | μA |

|                                                             | IIL2  | XIN, CXIN                                                                                                                                                                                                                                                                       | -0.3           | _ | 0.3   | μA |

| Tri-state                                                   | IOZH1 | Digital I/O                                                                                                                                                                                                                                                                     | -1             | — | 1     | μA |

| Output leakage<br>Current                                   | IOZL1 | Digital I/O                                                                                                                                                                                                                                                                     | -1             | - | 1     | μA |

| High level<br>output voltage                                | VOH   | $3.0V \leq VDDIO \leq 3.6V$ $PIN2,PIN1=0,0$ $IOH=-3.5mA$ $PIN2,PIN1=0,1$ $IOH=-7.0mA(*19)$ $PIN2,PIN1=1,1$ $IOH=-14.0mA(*4)$ $IOH=-9.0mA(*16) (*20)$ $2.6V \leq VDDIO < 3.0V$ $PIN2,PIN1=0,0$ $IOH=-1.25mA$ $PIN2,PIN1=0,1$ $IOH=-2.5mA(*19)$ $PIN2,PIN1=1,1$ $IOH=-5.0mA(*20)$ | VDDIOx0.7<br>5 | _ | VDDIO | V  |

| Low level<br>output voltage                                 | VOL   | 3.0V≦VDDIO≦3.6V<br>PIN2,PIN1=0,0<br>IOL=3.5mA<br>PIN2,PIN1=0,1<br>IOL=7.0mA(*19)<br>PIN2,PIN1=1,1<br>IOL=14.0mA(*20)                                                                                                                                                            | 0              | _ | 0.55  | v  |

|                 |     | F<br>1<br>F | <pre>/≤VDDIO&lt;3.0V PIN2,PIN1=0,0 IOH=1.25mA PIN2,PIN1=0,1 IOH=2.5mA(*19) PIN2,PIN1=1,1 IOH=5.0mA(*20)</pre> | 0 | _  | 0.45 |    |

|-----------------|-----|-------------|---------------------------------------------------------------------------------------------------------------|---|----|------|----|

| Pin capacitance | CIN | Inpu        | ut (*14)                                                                                                      | _ | 6  | -    | pF |

|                 | CIO | Inou        | ut(*15)                                                                                                       | _ | 9  | _    | pF |

|                 | CAI | Anal        | log input                                                                                                     | _ | 20 | _    | pF |

- (\*1) The power supply current is the total current of all power supply pins.

- (\*2) The "Typ." value is the center value under the condition of VDDIO = 3.3 V and 25 °C.

- (\*3) Under the condition 25°C for both Typ and Max.

- (\*4) Applied to GPIOA0, GPIOA1. Default drive strength is under the condition PIN2, PIN1=0,0 and can be configured by IO set registers.

- (\*5) Data rate is 100kbps.

- (\*6) With DCDC. Then, minimum supply voltage is 2.6v.

- (\*7) Without DCDC.

- (\*8) With DCDC and Changing PA Voltage Supply.

- (\*9) 32.768kHz Xtal osillator, RTC operation, SRAM(1KB[BANK4]) retension.

- (\*10) MCU=81.1MHz、FCLK\_DIV=64 division, All peripheral clocks are disabled (All existing bits of SYSCON\_PCLK\_DIS, SYSCON\_EPCLK\_DIS, SYSCON\_SPCLK\_DIS are "1".)

- (\*11) For supply current characteristics, Worst value under the conditoin VDD=3.3v.

- (\*12) All GPIOs except GPIOB0, GPIOD0 and GPIOD1.

- (\*13) All digital ports except (\*12).

- (\*14) REGPDIN, RESETN

- (\*15) All digital ports except (\*14).

- (\*16) Applied to all GPIOs except (\*4). Default setting is under the condition PIN2,PIN1=0,0 and can beconfigured by IO set registers.

- (\*19) PIN2, PIN1=0,1 Simultaneous switching pins are under 5 pins.

- (\*20) PIN2, PIN1=1,1 Simultaneous switching pins are under 1 pins.

## 5-4. RF Characteristics

| Modulated Data Rate | : | 1.2kbps to 300kbps |

|---------------------|---|--------------------|

| Modulation fomats   | : | 2/4-level GFSK/FSK |

| Rx Bandwidth        | : | Up to 600kHz       |

The measurement point is at antenna end specified in the recommended circuits.

## 5-4-1 [TX characteristics]

Value is under condition of the master clock frequency = 48MHz (Typ.).

| 5411    | o400MHz Band |

|---------|--------------|

| J.4.I.I |              |

| Item                     | Condition                             |                   | Min   | Тур | Max  | Unit  |

|--------------------------|---------------------------------------|-------------------|-------|-----|------|-------|

|                          | 20mW (13dBm) (*2)                     |                   | 10 13 |     | 12.0 | dBm   |

|                          | After power adjustment                |                   | 10    | 13  | 13.8 | UDIII |

| TX power                 | 10mW (10dBm) (*2)                     |                   | 7     | 10  | 10.8 | dBm   |

|                          | After power adjustment                |                   | /     | 10  | 10.8 | UDIII |

|                          | 1mW (0dBm) (*2)                       |                   | -3    | 0   | 0.8  | dBm   |

|                          | After power adjustment                |                   | -5    | 0   | 0.8  | UDIII |

| Programmable frequency   | -                                     |                   | 0.025 | _   | 400  | kHz   |

| deviation [Fdev] (*1)    |                                       |                   | 0.025 |     | 400  | KHZ   |

|                          | 99% power bandwidth, I                | PN9               |       |     |      |       |

| Occupied bandwidth       | 4.8kbps mode (*2)                     |                   | _     | -   | 8.5  | kHz   |

|                          | Modulation frequency deviation =      |                   | _     |     |      |       |

|                          | ±2.4kHz                               |                   |       |     |      |       |

|                          | PN9, 4.8kbps mode,                    |                   |       |     |      |       |

| Adjacent channel leakage | Modulation frequency deviation =      |                   |       |     |      |       |

| power [ACPR]             | ±2.4kHz                               |                   | -     | -   | -40  | dBc   |

|                          | Leakage power in 12.5kHz offset $\pm$ |                   |       |     |      |       |

|                          | 8.5kHz bandwidth                      |                   |       |     |      |       |

|                          | 10dBm TX                              |                   |       |     |      |       |

|                          | Data rate: 4.8kbps (*2),              | , PN9,            |       |     |      |       |

|                          | 2.4kHz deviation,                     |                   | -     | -   | -26  | dBm   |

|                          | 62.5k to 162.5kHz offset integration  |                   |       |     |      |       |

| Spurious emission        | value                                 |                   |       |     |      |       |

|                          | Harmonics (*2)                        |                   |       |     |      |       |

|                          | 10dBm CW TX                           | 2 <sup>nd</sup>   |       |     | -36  | dBm   |

|                          | (Note) With LC trap                   | 3 <sup>rd</sup> < | -     | -   | -30  | UDIII |

|                          | circuit                               |                   |       |     |      |       |

\*1 Depends on the master clock frequency.

\*2 For 426MHz.

| 5.4.1.2 08 | 68M/920MHz Band |

|------------|-----------------|

|------------|-----------------|

| Item                                         | Conditio                                                                                                                                      | on           | Min   | Тур | Max | Unit       |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|-----|-----|------------|

|                                              | 20mW (13dBm)                                                                                                                                  |              | 9     | 13  | 15  | dBm        |

| TX power                                     | 10mW (10dBm)                                                                                                                                  |              | 6     | 10  | 12  | dBm        |

|                                              | 1mW (0dBm)                                                                                                                                    |              | -6.5  | 0   | 7.5 | dBm        |

| Programmable frequency deviation [Fdev] (*1) | -                                                                                                                                             |              | 0.025 | _   | 400 | kHz        |

| Occupied bandwidth                           | 99% power bandwidth, PN9<br>100kbps mode<br>Modulation frequency deviation =<br>±50kHz                                                        |              | -     | -   | 200 | kHz        |

| Adjacent channel leakage<br>power [ACP]      | PN9, 100kbps mode, TX power =<br>13dBm,<br>Modulation frequency deviation =<br>±50kHz<br>Leakage power in 300kHz offset ±<br>100kHz bandwidth |              | -     | -   | -20 | dBm        |

|                                              |                                                                                                                                               | 710MHz ≥     | -     | -   | -36 | dBm/100kHz |

|                                              | 20mW (13dBm)                                                                                                                                  | 710-900MHz   | -     | -   | -55 | dBm/1MHz   |

|                                              | adjustment,                                                                                                                                   | 900-915MHz   | -     | -   | -55 | dBm/100kHz |

|                                              | Data rate:100kbps,                                                                                                                            | 915-930MHz   | -     | -   | -36 | dBm/100kHz |

| Courieus emission                            | 50kHz deviation,<br>Pattern:PN9,                                                                                                              | 930-1000MHz  | -     | -   | -55 | dBm/100kHz |

| Spurious emission                            | (*2)                                                                                                                                          | 1000-1215MHz | -     | -   | -45 | dBm/1MHz   |

|                                              |                                                                                                                                               | 1215MHz <    | -     | -   | -30 | dBm/1MHz   |

|                                              | Harmonics (2 <sup>nd</sup> / 3 <sup>rd</sup> )<br>13dBm CW TX<br>(Note) With LC trap circuit                                                  |              | -     | -35 | -30 | dBm        |

\*1 Depends on the master clock frequency.

\*2 For 920MHz band.

5.4.1.3 02.4GHz Band

| Item                                         | Condition                                                                                      | Min   | Тур | Max | Unit |

|----------------------------------------------|------------------------------------------------------------------------------------------------|-------|-----|-----|------|

| TX power                                     | 1mW (0dBm)                                                                                     | -4    | 0   | 4   | dBm  |

| Programmable frequency deviation [Fdev] (*1) |                                                                                                | 0.025 | -   | 400 | kHz  |

| Occupied bandwidth                           | 99% power bandwidth, PN9<br>100kbps mode<br>Modulation frequency deviation =<br>±50kHz setting | -     | 180 | -   | kHz  |

| Spurious emission                            | Harmonics (2 <sup>nd</sup> / 3 <sup>rd</sup> )<br>0dBm CW TX<br>(Note) With LC trap circuit    | -     | -29 | -26 | dBm  |

\*1 Depends on the master clock frequency.

# 5.4.2[RX characteristics]

## 5.4.2.1 o400MHz Band

| Item                                           | Condition                                                                                                                         |                | Min | Тур    | Max    | Unit |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------|-----|--------|--------|------|

| Sensitivity                                    | 4.8kbps mode<br>Center frequency 426MHz<br>BER<1%,<br>GFSK, 2.4kHz deviation                                                      | Fref<br>=48MHz | -   | -120.5 | -112.0 | dBm  |

|                                                | 9.6kbps mode<br>Center frequency 426MHz<br>BER<1%,<br>GFSK, 4.8kHz deviation                                                      | Fref<br>=48MHz | -   | -116.5 | -109   | dBm  |

| Adjacent channel                               | 12.5kHz spacing,<br>Ta = 25°C,<br>4.8kbps mode<br>Center frequency 426MHz<br>Undesire: PN9                                        | Fref<br>=48MHz | 30  | 33     | -      | dB   |

| rejection ratio (*1)                           | 25kHz spacing,<br>Ta = 25°C,<br>9.6kbps mode<br>Center frequency 426MHz<br>Undesire: PN9                                          | Fref<br>=48MHz | 30  | 33     | -      | dB   |

| Blocking (*1)                                  | 2MHz offset, Ta = 25°C,<br>4.8kbps mode<br>Center frequency 426MHz                                                                | Fref<br>=48MHz | -   | 73     | -      | dB   |

|                                                | 10MHz offset, Ta = 25°C,<br>4.8kbps mode<br>Center frequency 426MHz                                                               | Fref<br>=48MHz | -   | 82     | -      | dB   |

|                                                | -IF frequency*2[Hz]<br>offset (image frequency),<br>Ta=25°C, after IQ<br>adjustment                                               | Fref<br>=48MHz | 30  | 50     | -      | dB   |

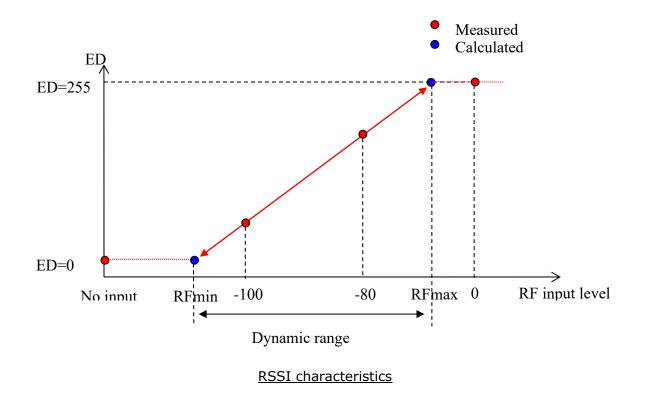

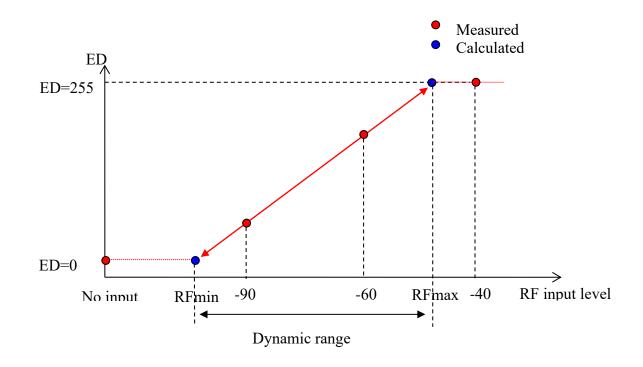

| Minimum power<br>detection level (ED<br>value) | RFmin in RSSI<br>characteristics diagram<br>(*2)<br>4.8kbps,<br>Center frequency 426MHz<br>Channel filter band =<br>10kHz setting | Fref<br>=48MHz | -   | -115   | -105   | dBm  |

| Item              | Condition                                              |                | Min | Тур | Max | Unit |

|-------------------|--------------------------------------------------------|----------------|-----|-----|-----|------|

| ED dynamic range  | Dynamic range in ED<br>characteristics diagram<br>(*2) | Fref<br>=48MHz | 60  | 65  | -   | dB   |

| Spurious emission |                                                        | Fref<br>=48MHz | -   | -   | -54 | dBm  |

- \*1 Adjacent channel rejection ratio and Blocking measurement condition is as follows. Desired signal level is set to receiver sensitivity level (BER=1%)+3dB. By sweeping undesired signal level, search the undesired signal level at BER=1%. U/D[dB]= (undesired signal level) - (sensitivity level(BER=1%))

- \*2 The following diagram shows the RSSI characteristics.

(Note)

If channel frequency is the neighborhood to multiply of the reference clock frequency or the neighborhood to 2 dividing of the reference clock frequency or the neighborhood to 4 dividing of the reference clock frequency, they may cause a deterioration of RX characteristics.

| 5.4.2.2 | ○868M/920MHz Band |

|---------|-------------------|

|---------|-------------------|

| Item                                           | Condition                                                                                                                         |         |                | Min  | Тур  | Max  | Unit |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------|----------------|------|------|------|------|

| Sensitivity                                    | 100kbps mode<br>Center frequency 920.7MHz<br>BER<0.1%,<br>GFSK, 50kHz deviation                                                   |         | Fref<br>=48MHz | -    | -105 | -98  | dBm  |

| Adjacent channel rejection ratio (*1)          | Ta = 25°C, 100kbps<br>mode                                                                                                        | +400kHz | Fref<br>=48MHz | 25   | 40   | -    | dB   |

|                                                | Center frequency<br>920.7MHz<br>Undesire: CW                                                                                      | -400kHz | Fref<br>=48MHz | 22   | 37   | -    | dB   |

| Blocking (*1)                                  | 2MHz offset, Ta = 25°C, 100kbps<br>mode<br>Center frequency 920.7MHz                                                              |         | Fref<br>=48MHz | 36.5 | 55   | -    | dB   |

|                                                | 10MHz offset, Ta = 25°C, 100kbps<br>mode<br>Center frequency 920.7MHz                                                             |         | Fref<br>=48MHz | 41.5 | 65   | -    | dB   |

| Minimum power<br>detection level (ED<br>value) | RFmin in RSSI characteristics<br>diagram (*2)<br>100kbps,<br>Center frequency 920.7MHz<br>Channel filter band = 200kHz<br>setting |         | Fref<br>=48MHz | -    | -106 | -100 | dBm  |

| ED dynamic range                               | Dynamic range in ED<br>characteristics diagram (*2)<br>100kbps,<br>Center frequency 920.7MHz                                      |         | Fref<br>=48MHz | 60   | 65   | -    | dB   |

| Spurious emission                              |                                                                                                                                   |         | Fref<br>=48MHz | -    | -    | -57  | dBm  |

- \*1 Adjacent channel rejection ratio and Blocking measurement condition is as follows. Desired signal level is set to receiver sensitivity level (BER=0.1%)+3dB.

- By sweeping undesired signal level, search the undesired signal level at  ${\sf BER=0.1\%}.$

- U/D[dB]= (undesired signal level) (desired singnal level)

- \*2 The following diagram shows the ED characteristics.

#### (Note)

If channel frequency is the neighborhood to multiply of the reference clock frequency or the neighborhood to 2 dividing of the reference clock frequency or the neighborhood to 4 dividing of the reference clock frequency, they may cause a deterioration of RX characteristics.

5.4.2.3 o2.4GHz Band

| Item                                           | Condition                                                                                                                                  |         |             | Min | Тур  | Max | Unit |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------|-----|------|-----|------|

| Sensitivity                                    | 100kbps mode<br>Center frequency 2.45GHz<br>BER<0.1%,<br>GFSK, 50kHz deviation                                                             |         | Fref =48MHz | -   | -97  | -89 | dBm  |

| Adjacent channel rejection ratio (*1)          | Ta = 25°C, 100kbps                                                                                                                         | +400kHz | Fref =48MHz | 25  | 36   | -   | dB   |

|                                                | mode<br>Center frequency<br>2.45GHz<br>Undesired : CW                                                                                      | -400kHz | Fref =48MHz | 10  | 31   | -   | dB   |

| Blocking (*1)                                  | 2MHz offset, Ta = 25°C, 100kbps<br>mode<br>Center frequency 2.45GHz                                                                        |         | Fref =48MHz | 38  | 55   | -   | dB   |

|                                                | 10MHz offset, Ta = 25°C, 100kbps<br>mode<br>Center frequency 2.45GHz                                                                       |         | Fref =48MHz | 58  | 65   | -   | dB   |

| Minimum power<br>detection level (ED<br>value) | RFmin in RSSI characteristics<br>diagram (*2)<br>100kbps mode,<br>Center frequency 2.45GHz<br>Channel filter bandwidth = 200kHz<br>setting |         | Fref =48MHz | -   | -105 | -90 | dBm  |

| ED dynamic range                               | Dynamic range in ED<br>characteristics diagram(*2),<br>100kbps mode<br>Center frequency 2.45GHz                                            |         | Fref =48MHz | 50  | 60   | -   | dB   |

| Spurious emission                              |                                                                                                                                            |         | Fref =48MHz | -   | -72  | -36 | dBm  |

\*1 Adjacent channel rejection ratio and Blocking measurement condition is as follows.

Desired signal level is set to receiver sensitivity level (BER=0.1%)+3dB.

By sweeping undesired signal level, search the undesired signal level at BER=0.1%.

U/D[dB]= (undesired signal level) - (desired singnal level)

\*2 The following diagram shows the ED characteristics.

#### (Note)

If channel frequency is the neighborhood to multiply of the reference clock frequency or the neighborhood to 2 dividing of the reference clock frequency or the neighborhood to 4 dividing of the reference clock frequency, they may cause a deterioration of RX characteristics.

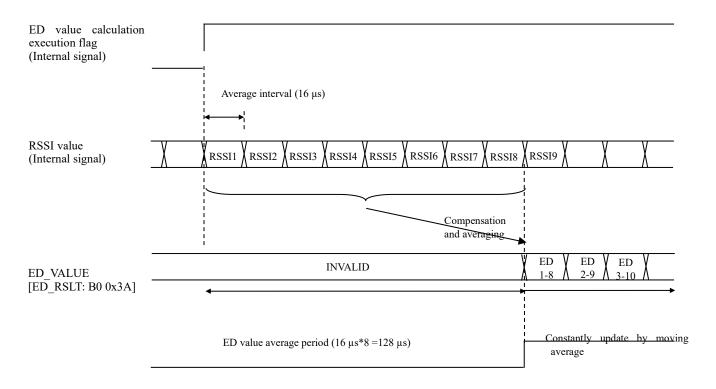

ED characteristics

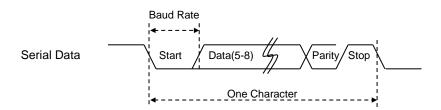

# 5-5. UART interface characteristics

| Item      | Symbol            | Conditions                         | Min                 | Тур | Max      | Unit |

|-----------|-------------------|------------------------------------|---------------------|-----|----------|------|

| Baud Rate | F <sub>BAUD</sub> | Load<br>capacitanc<br>e<br>CL=20pF | Fuart/(16*(2^16-1)) | -   | Fuart/16 | bps  |

\*  $F_{UART}$  is frequency of UART clock. It is derived clock which divides main clock by 1-64.

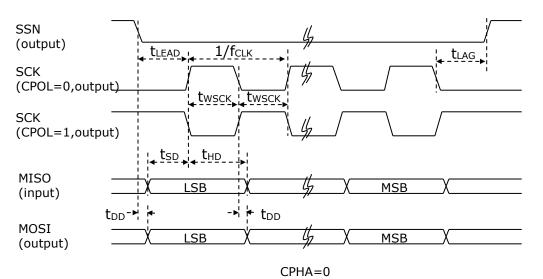

# 5-6. SPI Interface Charactaristics

# 5-6-1. Master

| Item                       | Symbol            | Condition | Min                    | Тур | Max                   | Unit |

|----------------------------|-------------------|-----------|------------------------|-----|-----------------------|------|

| Serial clock cycle time    | f <sub>CLK</sub>  |           | -                      | -   | 13.52                 | MHz  |

| Serial clock High/Low time | t <sub>wscк</sub> |           | 30                     | -   | -                     | ns   |

| Data delay time(output)    | t <sub>DD</sub>   |           | -                      | -   | 10                    | ns   |

| Data setup time(input)     | t <sub>sD</sub>   |           | 20                     | -   | -                     | ns   |

|                            |                   | -         | System                 |     |                       |      |

|                            | t <sub>HD</sub>   |           | clock x 1              | -   | -                     | ns   |

| Data hold time(input)      |                   | CL=20pF   | frequency              |     |                       |      |

|                            |                   | -         |                        |     | 1.5t <sub>scк</sub>   | 20   |

| SSN-SCK lead time          | t <sub>LEAD</sub> |           | 0.5t <sub>scк</sub> -5 | -   | +10                   | ns   |

|                            | L                 | -         |                        |     | 1.5t <sub>scк</sub>   |      |

| SCK-SSN lag time           | $t_{LAG}$         |           | 0.5t <sub>scк</sub> -5 | -   | +10                   | ns   |

|                            | L                 |           | 14 5                   |     | 511t <sub>scк</sub> + | 22   |

| SSN H minimum width        | t <sub>wssн</sub> |           | 1t <sub>scк</sub> -5   | -   | 5                     | ns   |

\*  $t_{SCK} = (1000/f_{CLK}) [ns]$

Characteristics when SDLY=1

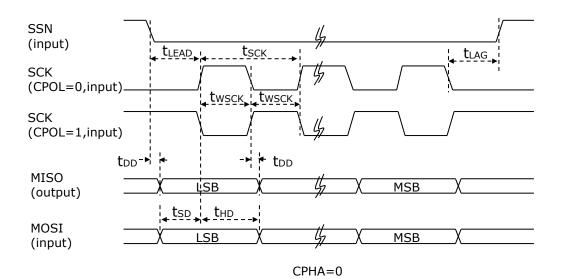

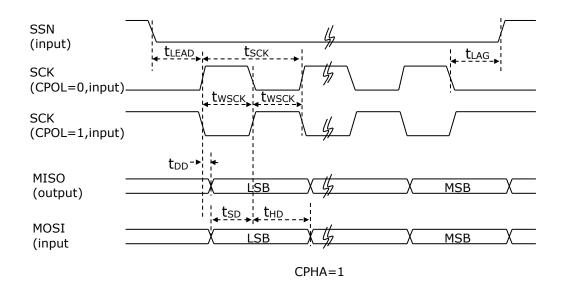

◎ SPI Master mode timing (CPHA=0)

◎ SPI Master mode timing (CPHA=1)

\* CPHA and CPOL registers set the data output timing and clock polarity.

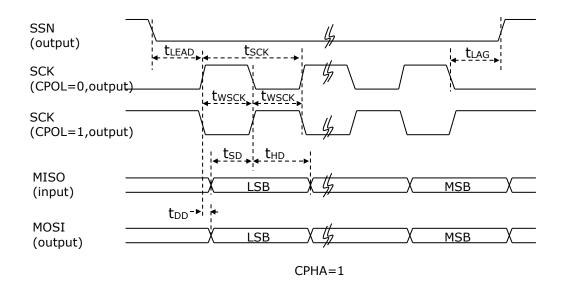

# 5-6-2. Slave

| Item                       | Symbol            | Conditions | Min | Тур | Max  | Unit |

|----------------------------|-------------------|------------|-----|-----|------|------|

| Serial clock cycle time    | f <sub>CLK</sub>  |            | -   | -   | 12   | MHz  |

| Serial clock High/Low time | t <sub>wscк</sub> |            | 40  | -   | -    | ns   |

| Data delay time (output)   | $t_{DD}$          |            | -   | -   | 41.5 | ns   |

| Data setup time (input)    | $t_{SD}$          | CL=20pF    | 10  | -   | -    | ns   |

| Data hold time (input)     | t <sub>HD</sub>   |            | 10  | -   | -    | ns   |

| SSN-SCK lead time          | t <sub>LEAD</sub> |            | 40  | -   | -    | ns   |

| SCK-SSN lag time           | t <sub>LAG</sub>  |            | 40  | -   | -    | ns   |

%t<sub>SCK</sub> = (1000/f<sub>CLK</sub>) [ns]

◎ SPI slave mode timing (CPHA=0)

◎ SPI slave mode timing (CPHA=1)

$\ast$  CPHA and CPOL registers set the data output timing and clock polarity.

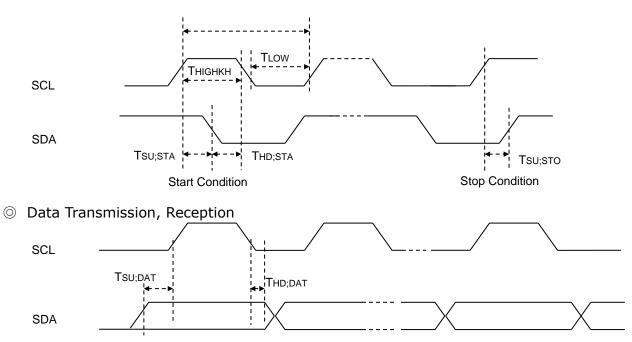

|                           |                  |                 | Standa | rd-Mode | Fast- | Mode | Fast-Mo | de+ Plus |      |

|---------------------------|------------------|-----------------|--------|---------|-------|------|---------|----------|------|

| Item                      | Symbol           | Conditions      | MIN    | MAX     | MIN   | MAX  | MIN     | MAX      | Unit |

| SCL clock frequency       | Fscl             |                 | 0      | 100     | 0     | 400  | 0       | 1000     | kHz  |

| SCL H pulse width         | Тнідн            |                 | 4.0    | -       | 0.6   | -    | 0.26    | -        | μs   |

| SCL L pulse width         | T <sub>LOW</sub> | Capacitive Load | 4.7    | -       | 1.3   | -    | 0.5     | -        | μs   |

| Start condition hold time | THD;STA          | CL=             | 4.0    | -       | 0.6   | -    | 0.26    | _        | μs   |

| Stop condition setup time | TSU:STA          | 10pF            | 4.7    | -       | 0.6   | -    | 0.26    | -        | μs   |

| SDA output hold time      | Tsu;sto          |                 | 4.7    | -       | 0.6   | -    | 0.26    | _        | μs   |

| SCL output delay time     | THD;DAT          |                 | 0      | -       | 0     | -    | 0       | -        | μs   |

| SDA input setup time      | TSU;DAT          |                 | 250    | -       | 100   |      | 50      | _        | ns   |

# 5-7. I2C Interface characteristics