Dear customer

ROHM Co., Ltd. ("ROHM"), on the 1st day of April, 2024, has absorbed into merger with 100%-owned subsidiary of LAPIS Technology Co., Ltd.

Therefore, all references to "LAPIS Technology Co., Ltd.", "LAPIS Technology" and/or "LAPIS" in this document shall be replaced with "ROHM Co., Ltd." Furthermore, there are no changes to the documents relating to our products other than the company name, the company trademark, logo, etc.

Thank you for your understanding.

ROHM Co., Ltd. April 1, 2024

# ML86V7675

Digital Video Decoder

## **General Description**

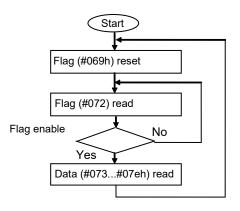

The ML86V7675 is a digital video decoder LSI that converts NTSC, PAL analog video signals, 480i/576i/480p/576p analog video signals, analog EGA(400 x 234, 480 x 234), analog RGB WVGA(800 x 480) signals into the YCbCr standard digital format defined by ITU-R recommendations BT.601/BT.656.

The device has built-in 10-bit A/D converters and can accept only composite video signal, S-video signal, or Component video signal as an analog input.

An input composite video signal is separated into a luminance signal and a chrominance signal with a 2-dimensional Y/C separation filter. These two signals are then output as digital video signals.

In addition to the asynchronous sampling method, which is a special feature of LAPIS Semiconductor's video decoders, video signals can also be sampled with a line lock clock sampling method using the built-in PLL.

Further, the pixel position compensation function provided makes it possible to eliminate video jitter even with the asynchronous sampling method, ensuring the output of jitter-free video data.

#### Features

| • Analog video input - input format |                                                                           |             |

|-------------------------------------|---------------------------------------------------------------------------|-------------|

| Composite video :                   | NTSC/PAL/SECAM (ITU-R BT.470)                                             |             |

| S vide :                            | NTSC/PAL/SECAM (ITU-R BT.470)                                             |             |

| Component video input :             | 480i/576i/480p/576p, EGA, WVGA                                            |             |

| (YPbPr/RGB)                         | (Sync on Y/G. CSYNC input supported only at RGB inp                       | ut)         |

| • Analog input port :               | Composite video input                                                     | 4ch         |

|                                     | Component video input (YPbPr/RGB)                                         | 1ch         |

|                                     | Component video input (YPbPr/RGB) or S video input                        | 1ch         |

| • A/D converter :                   | 10bit ADC                                                                 |             |

| • Supported sampling frequency      |                                                                           |             |

| NTSC/ PAL/ SECAM :                  | 27.0000MHz                                                                |             |

| (ITU-R BT.601)                      |                                                                           |             |

| NTSC                                | 28.6363 MHz                                                               |             |

| D1 (480i/576i) :                    | 27.0000 MHz                                                               |             |

| D2 (480p/576p) :                    | 27.0000 MHz                                                               |             |

| EGA (400×234) :                     | 7.993006 MHz                                                              |             |

| EGA (480×234) :                     | 9.582167 MHz                                                              |             |

| WVGA (800×480) :                    | 33.231, 33.333MHz                                                         |             |

| • Sampling method :                 | Asynchronous sampling method / Line lock clock sampling                   | ng method   |

| • Y/C separation :                  | Adaptive two-dimensional Y/C separation filter                            |             |

| • Luminance level adjustment :      | AGC (automatic luminance adjustment) /                                    |             |

|                                     | MGC (manual luminance adjustment) / Peak AGC                              |             |

| • Color level adjustment :          | ACC (automatic color adjustment) / MCC (manual color                      | adjustment) |

| • Contrast adjustment:              | Adjustable around 128 with a slope ranging from 1/32 to                   | 63/32       |

| • Luminance offset adjustment :     | Adjustable between -7IRE to 7IRE(except analog RGB i<br>-128LSB to 127LSB | nputs),     |

| • Contour correction:               | Emphasizes higher frequencies                                             |             |

| • Hue adjustment:                   | Adjustable between -178.6° to 180°(NTSC,PAL only),<br>-45° to 44.6°       |             |

|                                     |                                                                           |             |

| • Automatic judgment of input video signal method :                   | NTSC / PAL / SECAM automatic                                                                                                     | c recognition                                                                            |  |  |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|--|

| • VBI data detection :                                                | Closed caption<br>CGMS<br>WSS                                                                                                    | Supports only NTSC (480i)<br>Supports only NTSC (480i, 480p)<br>Supports only PAL (576i) |  |  |

| • Output format :                                                     | YCbCr 4:2:2 (8bit duplex data + s<br>ITU-R BT.656 (YCbCr 4:2:2 8-b<br>synchronization information)<br>SDR, DDR output selectable |                                                                                          |  |  |

| • Host interface :                                                    | I <sup>2</sup> C (Slave)<br>Slave address selectable from 80h (1000 000x) or 82h (1000 001x).                                    |                                                                                          |  |  |

| • Clock                                                               |                                                                                                                                  |                                                                                          |  |  |

| Sampling clock :                                                      | Line lock PLL method                                                                                                             |                                                                                          |  |  |

|                                                                       | An external crystal oscillator (32.00 as a reference clock                                                                       | MHz or 25.00MHz) is attached                                                             |  |  |

| • Power supply voltage :                                              | I/O                                                                                                                              | $3.3V \pm 0.3V$                                                                          |  |  |

|                                                                       | Analog section (AFE / ADC)                                                                                                       | $3.3V \pm 0.3V$                                                                          |  |  |

|                                                                       | - · · · · · · · · · · · · · · · · · · ·                                                                                          | $1.5V \pm 0.15V$                                                                         |  |  |

|                                                                       | Logic section                                                                                                                    | $1.5V \pm 0.15V$                                                                         |  |  |

| <ul><li>Operating frequency :</li><li>Operating temperature</li></ul> | Maximum input 28.63MHz, maxi                                                                                                     | imum output 57.26MHz                                                                     |  |  |

| (ambient temperature) :                                               | -40°C to +85°C                                                                                                                   |                                                                                          |  |  |

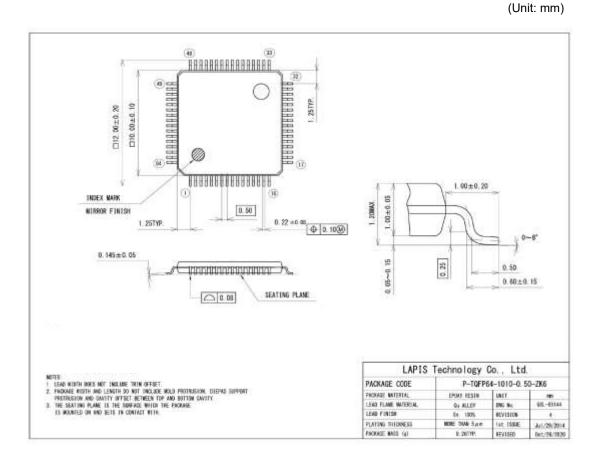

| • Package :                                                           | 64 pin plastic TQFP                                                                                                              |                                                                                          |  |  |

## Application

•Car navigation •Display audio •RSE (Rear Seat Entertainment)

## Line up

| Part Number     | Shipping form |

|-----------------|---------------|

| ML86V7675TPZ0AX | Tray          |

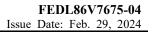

## **Block Diagram**

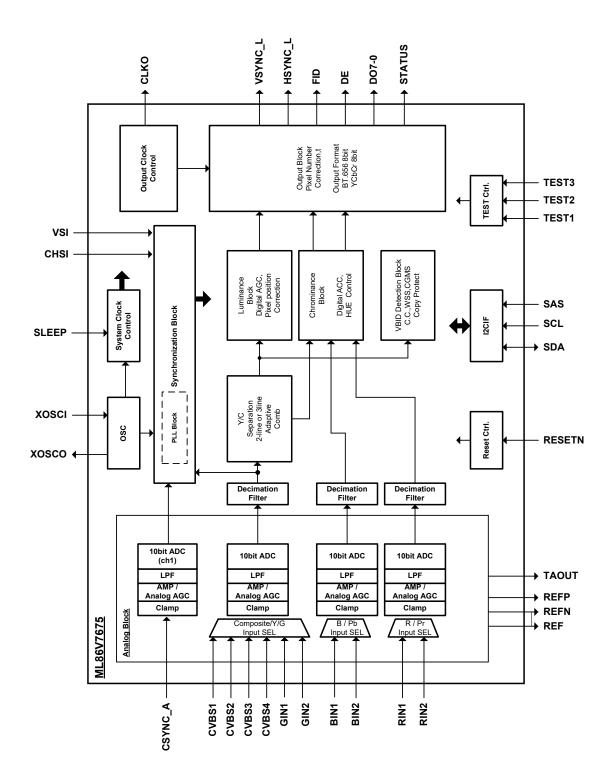

Pin Connections (Top View)

Note: Apply the same power supply voltage to the power supply pins of the same pin name. Fix the unused input pins to the "L" level or the "H" level. However, if the unused input pin is a pull-up resistor pin, fix it to the "H" level, and if it is a pull-down pin, fix it to the "L" level.

## List of Pins

| Pin    | Din nomo | 1/0 | Туре                    |               | Time                                                                                                     |

|--------|----------|-----|-------------------------|---------------|----------------------------------------------------------------------------------------------------------|

| number | Pin name | I/O | Input                   | Output        | Туре                                                                                                     |

| 1      | GIN1     | Ι   | Analog                  |               | Analog video input (G/Y)                                                                                 |

| 2      | GIN2     | Ι   | Analog                  |               | Analog video input (G/Y/SY)                                                                              |

| 3      | AVDD     |     | Power supply            |               | Power supply for analog (3.3V)                                                                           |

| 4      | AGND     |     | Power supply            |               | Ground for analog                                                                                        |

| 5      | BIN1     |     | Analog                  |               | Analog video input (B/Pb)                                                                                |

| 6      | BIN2     |     | Analog                  |               | Analog video input (B/Pb/SC)                                                                             |

| 7      | REF      | 0   |                         | Analog        | Reference voltage for ADC (external grounding through 0.01uF)                                            |

| 8      | REFP     | 0   |                         | Analog        | Reference voltage for ADC (external grounding through 0.22uF)                                            |

| 9      | REFN     | 0   |                         | Analog        | Reference voltage for ADC (external grounding through 0.22uF)                                            |

| 10     | AGND     |     | Power supply            |               | Ground for analog                                                                                        |

| 11     | TAOUT    | 0   |                         | Analog        | Output for testing (open)                                                                                |

| 12     | RIN1     |     | Analog                  |               | Analog video input (R/Pr)                                                                                |

| 13     | RIN2     | —   | Analog                  |               | Analog video input (R/Pr)                                                                                |

| 14     | AVDD     |     | Power supply            |               | Power supply for analog (3.3V)                                                                           |

| 15     | AGND     |     | Power supply            |               | Ground for analog                                                                                        |

| 16     | CSYNC_A  | Ι   | Analog                  | _             | Analog composite synchronous input                                                                       |

| 17     | DVDD_C   |     | Power supply            |               | Power supply for digital core (1.5V)                                                                     |

| 18     | DGND     |     | Power supply            |               | Ground for digital                                                                                       |

| 19     | DVDD_IO  |     | Power supply            |               | Power supply for digital input/output (3.3V)                                                             |

| 20     | CHSI     | I   | LVTTL,ST<br>5V-tolerant | _             | Digital composite synchronous input or<br>Digital horizontal synchronous input<br>(For analog RGB input) |

| 21     | VSI      | I   | LVTTL,ST<br>5V-tolerant |               | Digital vertical synchronous input<br>(for analog RGB input)                                             |

| 22     | TEST1    | -   | LVTTL,PD                |               | Test mode selection                                                                                      |

| 23     | TEST2    |     | LVTTL,PD                |               | Test mode selection                                                                                      |

| 24     | TEST3    |     | LVTTL,PD                |               | Test mode selection                                                                                      |

| 25     | DVDD_C   |     | Power supply            |               | Power supply for digital core (1.5V)                                                                     |

| 26     | DGND     |     | Power supply            |               | Ground for digital                                                                                       |

| 27     | SLEEP    | -   | LVTTL,PD                |               | Sleep enable input                                                                                       |

| 28     | STATUS   | 0   |                         | 4-mA drive    | Status output                                                                                            |

| 29     | DVDD_C   |     | Power supply            |               | Power supply for digital core (1.5V)                                                                     |

| 30     | DGND     |     | Power supply            |               | Ground for digital                                                                                       |

| 31     | DVDD_IO  |     | Power supply            |               | Power supply for digital input/output (3.3V)                                                             |

| 32     | DE       | 0   |                         | 2-/4-mA drive | Data enable output                                                                                       |

PD = pull-down. ST = Schmitt Trigger.

Note: The pull-up or pull-down resistance is  $40k\Omega$ .

| Pin    | Din nome | I/O | T            | уре                               | Turce                                                   |

|--------|----------|-----|--------------|-----------------------------------|---------------------------------------------------------|

| number | Pin name | 1/0 | Input        | Output                            | Туре                                                    |

| 33     | FID      | 0   |              | 2-/4-mA drive                     | Field output                                            |

| 34     | HSYNC_L  | 0   |              | 2-/4-mA drive                     | Vertical synchronous output                             |

| 35     | VSYNC_L  | 0   |              | 2-/4-mA drive                     | Horizontal synchronous output                           |

| 36     | DO0      | 0   |              | 2-/4-mA drive                     | Output data 0                                           |

| 37     | DO1      | 0   |              | 2-/4-mA drive                     | Output data 1                                           |

| 38     | DO2      | 0   |              | 2-/4-mA drive                     | Output data 2                                           |

| 39     | DO3      | 0   |              | 2-/4-mA drive                     | Output data 3                                           |

| 40     | DO4      | 0   |              | 2-/4-mA drive                     | Output data 4                                           |

| 41     | DO5      | 0   |              | 2-/4-mA drive                     | Output data 5                                           |

| 42     | DO6      | 0   |              | 2-/4-mA drive                     | Output data 6                                           |

| 43     | DO7      | 0   |              | 2-/4-mA drive                     | Output data 7                                           |

| 44     | DVDD_C   |     | Power supply |                                   | Power supply for digital core (1.5V)                    |

| 45     | DGND     |     | Power supply |                                   | Ground for digital                                      |

| 46     | DVDD_IO  |     | Power supply |                                   | Power supply for digital input/output (3.3V)            |

| 47     | CLKO     | 0   |              | 2-/4-mA drive                     | Output clock                                            |

| 48     | RESETN   | Ι   | LVTTL,ST     | — System reset input (active "L") |                                                         |

| 49     | XOSCI    | I   | LVTTL        | _                                 | Clock oscillation input<br>(HPLL reference clock input) |

| 50     | XOSCO    | 0   |              | 6 mA drive                        | Clock oscillation output                                |

| 51     | SDA      | I/O | LVTTL,ST     | 4 mA drive<br>open-drain          | I <sup>2</sup> C bus serial data                        |

| 52     | SCL      | -   | LVTTL,ST     |                                   | I <sup>2</sup> C bus serial clock                       |

| 53     | DVDD_C   |     | Power supply |                                   | Power supply for digital core (1.5V)                    |

| 54     | DGND     |     | Power supply |                                   | Ground for digital                                      |

| 55     | SAS      | —   | LVTTL,PD     |                                   | I <sup>2</sup> C bus slave address selection            |

| 56     | DVDD_IO  |     | Power supply |                                   | Power supply for digital input/output (3.3V)            |

| 57     | PVDD_A   |     | Power supply |                                   | Power supply for HPLL (1.5V)                            |

| 58     | PGND_A   |     | Power supply |                                   | Ground for HPLL                                         |

| 59     | CVBS1    | Ι   | Analog       |                                   | Analog video input (CVBS)                               |

| 60     | CVBS2    |     | Analog       |                                   | Analog video input (CVBS)                               |

| 61     | CVBS3    |     | Analog       |                                   | Analog video input (CVBS)                               |

| 62     | CVBS4    | Ι   | Analog       |                                   | Analog video input (CVBS)                               |

| 63     | AVDD     |     | Power supply |                                   | Power supply for analog (3.3V)                          |

| 64     | AGND     | _   | Power supply |                                   | Ground for analog                                       |

PD = pull-down. ST = Schmitt Trigger.

Note: The pull-up or pull-down resistance is  $40k\Omega$ .

## **Pin Descriptions**

| Din nama          |                    | Primary function                                                                                     | Secondary function                                                                                                                                                     |                         | Initial |  |  |  |

|-------------------|--------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------|--|--|--|

| Pin name          |                    | Description                                                                                          |                                                                                                                                                                        | Description             | Status  |  |  |  |

| Analog video inpu | Analog video input |                                                                                                      |                                                                                                                                                                        |                         |         |  |  |  |

| RIN1, GIN1, BIN1  | I                  | Analog component video signal in<br>RIN1: For R/Pr<br>GIN1: For G/Y<br>BIN1: For B/Pb                | GIN1: For G/Y                                                                                                                                                          |                         |         |  |  |  |

| RIN2, GIN2, BIN2  | I                  | Analog component video signal<br>input 2 (RGB2)<br>RIN2: For R/Pr<br>GIN2: For G/Y<br>BIN2: For B/Pb | Analog component video signal<br>input 2 (RGB2)Analog video S signal input<br>BIN2: For SC<br>GIN2: For G/YAnalog video S signal input<br>BIN2: For SC<br>GIN2: For SY |                         |         |  |  |  |

| CVBS1-4           | Ι                  | Analog composite video signal input                                                                  |                                                                                                                                                                        |                         |         |  |  |  |

| CSYNC_A           | Ι                  | Analog composite sync input (for a                                                                   | Analog composite sync input (for analog RGB input)                                                                                                                     |                         |         |  |  |  |

| CHSI              | I                  | Digital composite sync input, digita (For analog RGB input)                                          | Digital composite sync input, digital horizontal synchronous input<br>(For analog RGB input)                                                                           |                         |         |  |  |  |

| VSI               | Ι                  | Digital vertical synchronous input(                                                                  | For ar                                                                                                                                                                 | nalog RGB input)        |         |  |  |  |

| REF               | 0                  | Reference voltage for ADC (extern                                                                    | nal gro                                                                                                                                                                | ounding through 0.01uF) |         |  |  |  |

| REFN              | 0                  | Reference voltage for ADC (extern                                                                    | nal gro                                                                                                                                                                | ounding through 0.22uF) |         |  |  |  |

| REFP              | 0                  | Reference voltage for ADC (extern                                                                    | Reference voltage for ADC (external grounding through 0.22uF)                                                                                                          |                         |         |  |  |  |

| TAOUT             | 0                  | Output for testing (open)                                                                            |                                                                                                                                                                        |                         |         |  |  |  |

| External CLK      | External CLK       |                                                                                                      |                                                                                                                                                                        |                         |         |  |  |  |

| XOSCI             | Ι                  | Clock oscillation input (HPLL referen                                                                | nce cl                                                                                                                                                                 | ock input)              | Input   |  |  |  |

| XOSCO             | 0                  | Clock oscillation output "X"                                                                         |                                                                                                                                                                        |                         |         |  |  |  |

Note: The initial state is the primary function.

| Dianama          |                 | Primary function                                                                                |                                                  | Secondary function | Initial     |  |  |

|------------------|-----------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------|-------------|--|--|

| Pin name         | I/O Description |                                                                                                 | I/O                                              | Description        | Status      |  |  |

| Host interface   |                 |                                                                                                 |                                                  |                    |             |  |  |

| SDA              | I/O             | I <sup>2</sup> C bus serial data                                                                |                                                  |                    | Input       |  |  |

| SCL              | Ι               | I <sup>2</sup> C bus serial clock                                                               |                                                  |                    | Input       |  |  |

| SAS              | I               | I <sup>2</sup> C bus address selection<br>"L": 80h (1000_000x)∕"H": 82h (1000_                  | _001x)                                           |                    | Input<br>PD |  |  |

| STATUS           | 0               | Status or interrupt ("L" active) output                                                         |                                                  |                    | "H"         |  |  |

| System           | -               |                                                                                                 |                                                  |                    |             |  |  |

| RESETN           | Ι               | System reset input (active "L")                                                                 |                                                  |                    | Input       |  |  |

| SLEEP            | Ι               | Sleep enable, "L": Normal operation / "H                                                        | Sleep enable, "L": Normal operation / "H": Sleep |                    |             |  |  |

| TEST1-3          | Ι               | Test mode selection, "L": Normal operation / "H": Test mode       Inp         Plant       Plant |                                                  |                    |             |  |  |

| Power supply     | -               |                                                                                                 |                                                  |                    | -           |  |  |

| AVDD<br>AGND     | _               | Power supply and ground for analog                                                              |                                                  |                    |             |  |  |

| PVDD_A<br>PGND_A | _               | <ul> <li>Power supply and ground for HPLL (analog sampling clock generation)</li> </ul>         |                                                  |                    |             |  |  |

| DVDD_C           | _               | Power supply for digital core                                                                   |                                                  |                    |             |  |  |

| DVDD_IO          | _               | Power supply for digital input/output                                                           |                                                  |                    |             |  |  |

| DGND             | _               | Ground for digital                                                                              |                                                  |                    |             |  |  |

Note: The initial state is the primary function. PD = pull-down. Note: The output at power down is the same as for the initial state.

Note: The pull-up or pull-down internal resistance is  $40k\Omega$ .

#### Description

#### 1. Analog Video Input

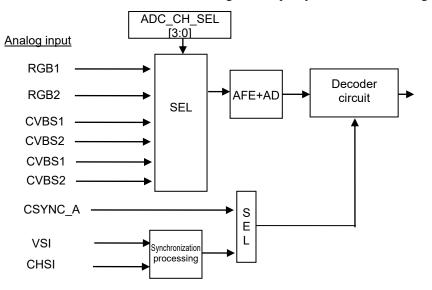

The ML86V7675 offers component video input, S video input, and composite video input for analog video input.

The analog input supports the composite video defined in ITU-R BT.470 and the component signal (interlace/progressive) defined in SMPTE 293M / ITU-R BT.601, 1358.

For the component video YPbPr input, superimpose the composite synchronization signal (Sync-On-Y) on the Y signal.

For the component video RGB input, select from superimposition of the composite synchronization signal on the G signal (Sync-On-G), analog input composite sync (CSYNC\_A), digital input composite sync (CHSI), and operation with vertical/horizontal synchronous signals (VSI, CHSI).

Analog video signal is input using capacitance coupling. Level of the synchronization signal is detected through the internal clamp circuit to reproduce in DC. (Sync-chip clamp)

The internal ADC performs sampling on the analog signals that are clamped. Unused A/D converter enters sleep mode to reduce power consumption.

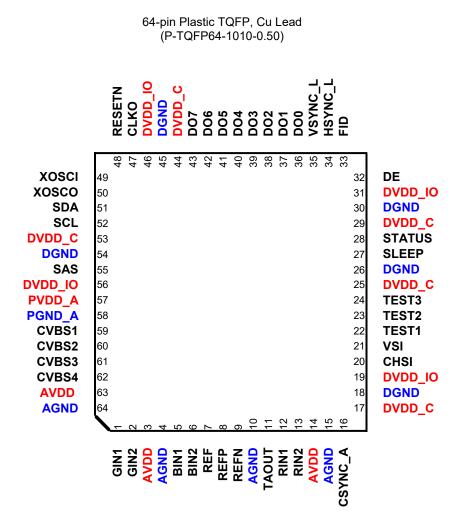

When inputting a signal to the decoder, the analog video input terminal must compose an external-circuit by figure described below.

The input-resistance which was loaded from the decoder must be about 75  $\Omega$ .

When it isn't possible to terminate by 75  $\Omega$  in the influence of the selector, the amplifier of the input stage and so on, connect equal to or less than 300  $\Omega$  even if maximum.

- Cin: Laminated ceramic capacitor (electrostatic capacity allowance ±10%, temperature characteristics ±10%)

- Rin: Resistor (accuracy of ±5%)

The ML86V7675 selects and uses one analog video input system to convert to digital video.

#### Input selection of internal processing circuit (#50h ADC\_CH\_SEL[3:0])

| Input     | Port for input |              |       |       |       |       |  |  |

|-----------|----------------|--------------|-------|-------|-------|-------|--|--|

| selection | RGB1           | RGB 2        | CVBS1 | CVBS2 | CVBS3 | CVBS4 |  |  |

| 0000      | O<br>(YPbPr)   | _            | _     | _     | _     | _     |  |  |

| 0001      | _              | O<br>(YPbPr) | _     | _     | —     | -     |  |  |

| 1000      | O<br>(RGB)     | _            | _     | -     | _     | -     |  |  |

| 1001      | -              | O<br>(RGB)   | _     | -     | _     | -     |  |  |

| 1011      | _              | O<br>(SY/SC) | _     | _     | —     | -     |  |  |

| 0100      | -              | _            | 0     | -     | —     | -     |  |  |

| 0101      | —              | —            | _     | 0     | —     | -     |  |  |

| 0110      | _              | —            | _     | _     | 0     | —     |  |  |

| 0111      | _              | —            | _     | _     | —     | 0     |  |  |

| Others    | Analog sleep   |              |       |       |       |       |  |  |

Note: CVBS = Composite video signal, SY/SC = S video signal, Other = Component signal

| Synchronous input at cor | mponent input(#01h | SEP_S_MD[1:0]) |

|--------------------------|--------------------|----------------|

|                          |                    |                |

| Input format    | Synchronous input      | Pin        |

|-----------------|------------------------|------------|

| Component YPbPr | Sync on Y              | GIN1, GIN2 |

| Component RGB   | Sync on G              | GIN1, GIN2 |

|                 | Analog composite sync  | CSYNC_A    |

|                 | Digital composite sync | CHSI       |

|                 | Digital separate sync  | VSI, CHSI  |

#### 2. Sampling Clock

#### 2.1 Sampling Clock Method

As a sampling clock of analog video input, the following two types can be selected. The related control registers are #5Ch to #5Dh.

(1) Asynchronous sampling method

This sampling method is based on the fixed clock. The sampling clock is selectable from following two operation types:

•Directly input from an external pin (enabled only for interlace input, 27MHz sampling operation without HPLL)

•Generated by the built-in HPLL using an external reference clock

When using the built-in HPLL, the clock is generated using a 32MH or 25MHz external reference clock at a fixed dividing ratio(#8Fh/bit[0] OSC\_SEL). Since the clock is asynchronous with the video input signal in any case, clock phase is adjusted internally by each line.

There is an advantage with high synchronous traceability for disordered synchronization signal such as a nonstandard video signal or others. However, for composite and S video inputs, a performance of color separation is somewhat influenced if the deflection from a specified clock frequency is large.

(2) Line lock method (HPLL)

Sampling method by line lock PLL.

Because a sampling clock is adjusted to divide a time of one line by a specified number of clocks, this method has an advantage that the number of clocks of one line and one frame (field) always obtain a constant output. However, since traceability is poor for a nonstandard video signal input, a normal output image may not be obtained in some cases.

When the line lock method is selected, the line lock operation mode can be selected by the control register (#5Ch bit[3] PLL\_LK\_TM). When the #5Ch bit[3] PLL\_LK\_TM is set to "1" (Fast-lock mode), the trace rate of PLL can be faster while the traceability may be deteriorated if a nonstandard signal is input. Moreover, the trace rate of the line lock operation can be adjusted by the control register (#5Dh). Stability may be deteriorated when the trace rate is made faster.

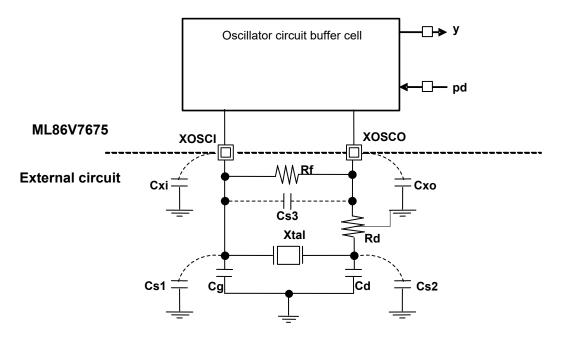

### 2.2 External Reference Clock

The following figure shows the external circuit configuration chart of the external clock to which the internal PLL refers, and an example of the component layout. Use the 32MHz or 25MHz for the external crystal frequency.

To ensure the line clock stability, use an external crystal with the frequency accuracy of 100 ppm or less.

#### **Circuit constants**

As a reference, the following table shows an example of circuit constants.

| Rf  | Rd   | Cg(*)           | Cd(*)           | Load capacity of available<br>oscillator |

|-----|------|-----------------|-----------------|------------------------------------------|

| 1MΩ | 100Ω | $8 \mathrm{pF}$ | $8 \mathrm{pF}$ | 8pF                                      |

(\*)These values are excluding the input-capacitance Cxi, Cxo and stray-capacitance Cs1, Cs2 and Cs3. The stray-capacitance values are varied by mounting conditions on Print circuit board and so on. The experimental examination and evaluation of these values are strongly recommended. Please refer the details to the vender of the crystal oscillator.

```

CL \doteq (Cg + Cs1 + Cxi) // (Cd + Cs2 + Cxo) + Cs3 = ((Cg + Cs1 + Cxi)*(Cd + Cs2 + Cxo)) / ((Cg + Cs1 + Cxi) + (Cd + Cs2 + Cxo)) + Cs3

```

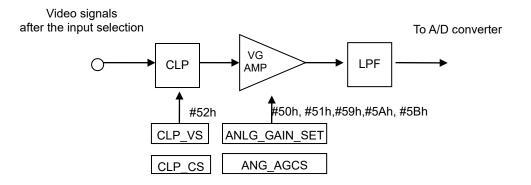

### 3. Analog Front End Section (Clamp, LPF, Amplifier)

The analog front end (AFE) performs the following processes:

- Detection of the analog video signal sync chip

- Clamp operation for converting to the built-in ADC input range

- Anti-aliasing using the LPF

- Level adjustment using the analog AGC (Auto Gain Control) function

AGC function has the output level adjustment function of the digital section (luminance block) as well as the input adjustment function by the internal amplifier. Manual gain setting is also available for the internal amplifier.

ML86V7675 has individual gain coefficient for each 4ch internal amplifier.

### 4. CVBS Video Decoder Section

The CVBS video decoder section has the Y/C separation, luminance processing, chrome processing, synchronization processing, and VBID detection functions.

#### 4.1 Y/C Separation

Y/C separation function separates the composite video data into Y (luminance) component and C (composite color difference) component.

The Y/C separation method is two-dimensional separation method without inter-field calculation. The format of Y/C separation filter used differs depending on the input video signal method. You can specify the mode to select the Y/C separation filter for each signal type.

| Mode      | Y/C separation method                                  |                      |             |  |  |  |

|-----------|--------------------------------------------------------|----------------------|-------------|--|--|--|

| selection | NTSC PAL                                               |                      | SECAM       |  |  |  |

| Mode 0    | Iode 0         Adaptive filter         Adaptive filter |                      |             |  |  |  |

| Mode 1    | Three-line comb filter                                 | Two-line comb filter |             |  |  |  |

| Mode 2    | Trap filter                                            | Trap filter          | Trap filter |  |  |  |

| Mode 3    | Three-line comb/trap<br>Adaptive filter                | Not defined          |             |  |  |  |

#### 4.2 CVBS Input Signal System

The CVBS input signal system is discriminated based on the following specifications.

| Signal system                | Number<br>of lines<br>(frames) | Field frequency<br>(Hz) | Sub-carrier<br>frequency<br>(MHz) | Black level<br>(IRE) |

|------------------------------|--------------------------------|-------------------------|-----------------------------------|----------------------|

| NTSC-M                       | 525                            | 59.94                   | 3.58                              | 7.5                  |

| NTSC-Japan                   | 525                            | 59.94                   | 3.58                              | 0                    |

| PAL-B, B1, D, D1, G, H, I, K | 625                            | 50                      | 4.43                              | 0                    |

| NTSC-443                     | 525                            | 59.94                   | 4.43                              | 0                    |

| PAL-M                        | 525                            | 59.94                   | 3.576                             | 7.5                  |

| PAL-N                        | 625                            | 50                      | 4.43                              | 7.5                  |

| PAL-Nc                       | 625                            | 50                      | 3.582                             | 0                    |

| PAL-60                       | 525                            | 59.94                   | 4.43                              | 0                    |

| SECAM                        | 625                            | 50                      | -                                 | 0                    |

For input signal systems, you choose to automatically detect from the cycle of horizontal and vertical synchronization signals reproducing from synchronizing separation and the color burst signal or to fix to use the specified system.

Among the input signal systems, automatic discrimination is available to the NTSC system (including -M / -Japan) defined in the ITU-R BT.470 recommendation, to the PAL system (B, B1, D, D1, G, H, I, K, M, N, and Nc, and to the SECAM system. For other systems such as NTSC-443 and PAL-60, NTSC-M and NTSC-J, you have to explicitly select by using the control register.

### 4.3 Luminance Processing

Level adjustment (AGC) processing is available for Y (luminance) data after Y/C separation. As the level adjustment, there are digital AGC (Automatic Gain Control) and analog amplifier AGC. Analog amplifier AGC is adjusted by the control register #51h.

The upper limit of the digital AGC scaling factor is about four times. If the amplitude of input signal is small, analog amplifier AGC adjusts it. The analog amplifier AGC scaling factor is from about 0.507 times to 4.5 times.

Digital AGC refers the depth of SYNC of Y (luminance) data after Y/C separation, and then adjusts the scaling factor of the luminance processing. The control register #21h enables fine adjustment of the luminance level.

In addition, digital MGC (Manual Gain Control) mode which determines luminance scaling factor by the register is available, regardless of depth of SYNC.

Digital AGC/MGC mode is divided into the following combinations, depending on the combination of settings of control registers #20h[7:6] and #20h[4]:

| #20h[7:6] | #20h[4] | Operation  |

|-----------|---------|------------|

| 00        | 0       | AGC slow   |

| 01        | 0       | AGC medium |

| 10        | 0       | AGC fast   |

| 11        | 0       | Inhibit    |

| XX        | 1       | MGC        |

#### 4.4 Color Difference Processing Section

C (composite color difference) data after Y/C separation is separated into two components of Cb and Cr by the color difference processing section. Color difference processing section adjusts the level of the data based on the color burst signals (digital ACC: Automatic Color Control), demodulates them by reproducing color sub-carriers based on each video signal format, and then separates them into Cb data and Cr data. The hue of Cb and Cr data can be adjusted.

Color difference processing is adjusted by the control registers #30h to #39h.

| #30h[7:6] | Operation  |

|-----------|------------|

| 00        | ACC fast   |

| 01        | ACC slow   |

| 10        | ACC medium |

| 11        | MCC        |

If the color demodulation is determined not to be performed correctly, the color killer processing (erases colors) is performed.

Color killer processing is adjusted by the control registers #33h to #34h.

### 4.5 Synchronization Processing Section

Separates into the vertical synchronization signals and the horizontal synchronization signals using Y (luminance) data of composite video data.

Synchronization processing section generates synchronizing separation threshold from input signals automatically, and then generates vertical valid range/horizontal valid range.

Synchronizing separation is adjusted by the control registers #14h to #16h. The following settings are available:

- •Selection of synchronizing separation threshold between automatic and manual

- •Adjustment of synchronizing separation threshold

- •Method of automatic generation of the synchronizing separation threshold

You can select from the method to generate based on the digital AGC gain value and the method to generate based on the depth of SYNC.

•Filter selection for Y (luminance) data at synchronous detection

Anti-noise filter can be selected in case of the light electric field signal.

•[Horizontal synchronization signal detection] Window

After detecting horizontal synchronization signals, you can set the range to detect the next horizontal synchronization signals.

•[Vertical synchronization signal detection] Window

After detecting vertical synchronization signals, you can set the range to detect the next vertical synchronization signals.

Because the detection of vertical synchronization signal detection supports light electric field signals, it can be reflected to the internal operations after checking validity of the result of the vertical synchronization detection.

Vertical synchronization signal detection is adjusted by the control registers #1Ah.

Because the detection of horizontal synchronization signals supports light electric field signals, it can be reflected to the internal operations after correcting the shift in the result of the horizontal synchronization detection by using horizontal AFC (Automatic Frequency Control) circuit. Horizontal AFC is adjusted by the control register #18h.

The horizontal AFC includes the PLL-AFC using line lock PLL, and the digital AFC that corrects pixel errors in horizontal synchronization detection. PLL-AFC operates in the line lock state and generates a horizontal synchronization signal per one line with the line lock clock. Digital AFC operates in the states other than line lock. It multiplies the result of horizontal synchronization detected by the specified gain (DAFC\_GAIN #2Ah), and then generates horizontal synchronization signals that have been applied error correction. Operation status of the horizontal AFC can be monitored by status register #71h bit[2].

Based on the results of horizontal synchronization signals detection and vertical synchronization signal detection, blue-back processing is performed to display blue on the full screen. Blue-back processing is adjusted by the control registers #40h to #44h. Results of the blue-back detection can be monitored by status register #71h bit[1].

There is a built-in judgment circuit that judges the current state as light electric field signal state based on the pixel errors at horizontal synchronization detection and the number of lines that contain these errors. Additionally, there is a built-in circuit that detects the VTR signal input status based on the pixel errors at horizontal synchronization detection and the line errors of horizontal synchronization detection. Each detection result can be monitored by the status register #71h.

The process to make the length of lines constant is performed since the number of clocks in one line may increase/decrease due to the disorder of the input synchronization signals in the case of asynchronous sampling method.

Detects errors in accuracy of 1/16 pixel based on the luminance data between pixels before and after synchronizing separation threshold in the horizontal synchronization detection, and then corrects the pixel position of luminance data and color difference data.

#### 4.6 VBI Data Slicer, Detection of Copy Protection

Copy protect information and various data superimposed to the vertical blanking interval (VBI: Vertical Blanking Interval) of input video signals can be extracted and read from the control register. The following data can be read:

(1) Copy protection

VBI nonstandard signal (NTSC/PAL), nonstandard color burst signal (NTSC only) (2) Closed caption

Keeps characters information such as caption, odd number line/even number line (NTSC/PAL)

- (3) WSS (Wide Screen Signaling)

Wide video identification signal defined by ETS 300 294 (PAL only)

- (4) CGMS-A (Copy Generation Management System Analog)

Copy generation management information defined by IEC61880 (NTSC)

#### 5. COMPONENT Video Decoder Section

The COMPONENT video decoder section has the luminance/color difference processing, synchronization processing, and VBID detection functions.

#### 5.1 COMPONENT Input Signal Format

The component input signal format is discriminated based on the following specifications.

| D1 setup | (#00h/bit[2: | 1] ISPMD | [1:0]=00) |

|----------|--------------|----------|-----------|

|----------|--------------|----------|-----------|

| Signal avetam | Number of    | Field frequency | Line frequency | Correspondence |

|---------------|--------------|-----------------|----------------|----------------|

| Signal system | lines(frame) | [Hz]            |                | standard       |

| 480i          | 525          | 59.94           | 15734          | ITU-R BT.601   |

| 576i          | 625          | 50              | 15625          | ITU-R BT.601   |

#### D2 setup (#00h/bit[2:1] ISPMD[1:0]=00)

| Simple water  | Number of    | Field frequency | Line frequency | Correspondence |

|---------------|--------------|-----------------|----------------|----------------|

| Signal system | lines(frame) | [Hz]            |                | standard       |

| 480p          | 525          | 59.94           | 31468          | SMPTE 293M     |

| 576p          | 625          | 50              | 31250          | ITU-R BT.1358  |

For input signal formats, you can choose to automatically detect from the cycle of the horizontal and vertical synchronization signals reproducing from synchronizing separation or to fix to use the specified format.

#### WVGA setup (#00h/bit[2:1] ISPMD[1:0]=01, sampling frequency 33.231MHz)

| Signal system | Number of<br>lines(frame) | Field frequency<br>[Hz] | Line frequency | Correspondence<br>standard |

|---------------|---------------------------|-------------------------|----------------|----------------------------|

| 480p          | 525                       | 59.94                   | 31468          | SMPTE293M                  |

WVGA setup (#00h/bit[2:1] ISPMD[1:0]=10, sampling frequency 33.333MHz)

| Signal system | Number of<br>lines(frame) | Field frequency<br>[Hz] | Line frequency | Correspondence<br>standard |

|---------------|---------------------------|-------------------------|----------------|----------------------------|

| 480p          | 525                       | 60.57                   | 31800          | -                          |

#### EGA setup (#00h/bit[2:1] ISPMD[1:0]=11)

| Signal system | Number of<br>lines(frame) | Field frequency<br>[Hz] | Line frequency | Correspondence<br>standard |

|---------------|---------------------------|-------------------------|----------------|----------------------------|

| 262p          | 262                       | 60                      | 15734          | _                          |

Automatic detection of an EGA input signal system cannot be performed.

The automatic judgment at component input has the following operation restriction:

•At component input, "SYNC depth" and "Blank Level (7.5IRE setup)" cannot be automatically judged. The "SYNC depth" and "Blank Level" at component input can be set using the control register #01h bit[5] and bit[4].

•EGA(400x234 or 480x234), WVGA cannot be automatically judged.

#### 5.2 COMPONENT Luminance/Color Difference Processing

The gain coefficient is automatically calculated from the synchronous signal on Y or G signal. Level adjustment (AGC) processing is available for all Y/PbPr or RGB input signals. The operation that inputs synchronization signals via CHSI, VSI and CSYNC\_A at the LVTTL level supports only the MGC mode.

#### 5.3 Synchronization Processing Section

For the component YPbPr and RGB inputs, superimpose the composite synchronization signal on the Y or G signal. The synchronization signal input from CSYNC\_A, CHSI and VSI can be supported only for the component RGB input. Processings such as synchronous detection are equivalent to those for composite video input.

#### 5.4 VBI Data Slicer, Detection of Copy Protection

Copy protect information and various data superimposed to the vertical blanking interval (VBI: Vertical Blanking Interval) of input video signals can be extracted and read from the control register. The following data can be read:

- (1) Copy protection

- VBI nonstandard signal (480i/576i/480p/576p)

- (2) CGMS-A (Copy Generation Management System Analog)

- Copy generation management information defined by IEC61880 (480i/480p)

#### 5.5 Sampling frequency set mode

In sampling frequency set mode, sampling processing is done by the clock corresponding to the dot clock of YPbPr or RGB progressive 525 line video signals except TV signals defined in the ITU-R BT.601 or SMPTE293M.

To select sampling frequency set mode as input video format, then related registers are available. Sampling frequency variable mode processing is controlled by the control registers #00h and #84h to #8Eh.

- •Set the input video format to sampling frequency set mode (#00h)

- •Set the sampling frequency corresponding to the dot clock of input video signal (#84h to #87h)

- Set the total pixels (#88h,#89h), the horizontal valid start position and horizontal valid width (#8Ah to #8Ch) according to horizontal timing of input signal.

- •For Sync on Y/G input, AGC processing is enabled by adjusting sync tip position and pedestal position (#8Dh, #8Eh)

The sampling frequency set mode has the following restriction:

- •Only available when fixed mode for video mode setting is set(#00h/bit[0] AVMD)

- •Only available when D1/D2 for sampling clock setting is selected(#00h/bit[2:1] ISPMD)

- •Horizontal total pixels can be set 576 to 1280 pixels

- •Horizontal total pixels, valid start position and valid width registers can be set even number.

- •Only available for vertical line number is 525(Vertical timing is same as 480P)

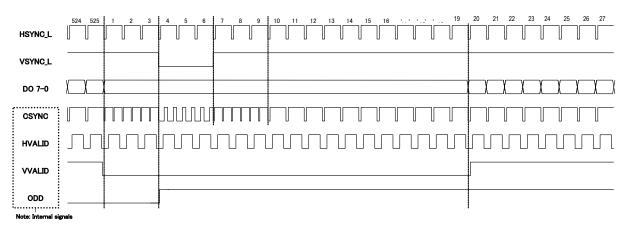

## 6. Synchronization Signal internal Timing

#### 6.1 Vertical Timing

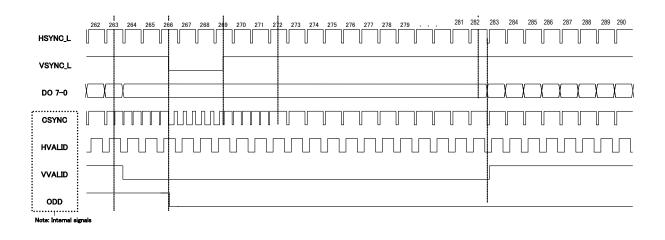

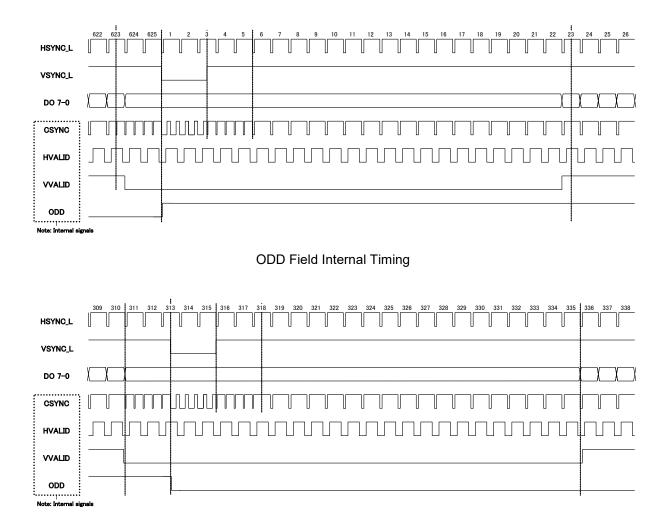

◆ NTSC Vertical Timing

#### ODD Field Internal Timing

EVEN Field Internal Timing

ML86V7675

◆ PAL Vertical Timing

**EVEN Field Internal Timing**

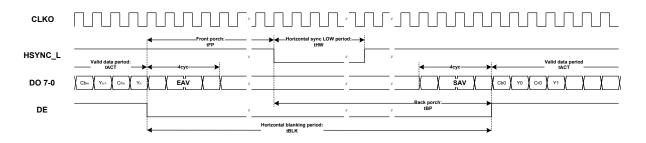

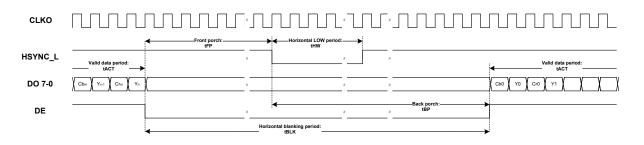

#### 6.2 Horizontal Timing

ML86V7675 output format offers ITU-R BT.656 style or YCbCr 8bit.

| #04[2:0]               | Data format | Output pin |

|------------------------|-------------|------------|

| 000 ITU-R BT.656 style |             | DO7-0      |

| 001                    | 8bit YCbCr  | DO7-0      |

Following figures describe digital video, sync signal output timing.

#### 6.2.1 Horizontal Timing in ITU-R BT.656 Mode

## 6.2.2 Horizontal Timing in "8-Bit Multiplexed + Sync Signal" Mode

|                                  |                    |             | Horizon        | tal(number    | of pixels)    |                 | Vertic            | al(number o         | f lines)                |

|----------------------------------|--------------------|-------------|----------------|---------------|---------------|-----------------|-------------------|---------------------|-------------------------|

| Video format                     | Sampling frequency | 1H<br>total | Front<br>porch | Sync<br>Width | Back<br>porch | Valid<br>period | Blank<br>period   | Valid<br>period     | 1V<br>total             |

|                                  | 1 5                |             | tFP            | tHW           | tBP           | tACT            | •                 | •                   |                         |

| NTSC (ITU-R BT.601 )<br>D1(480I) | 27.000MHz          | 1716        | 32             | 120           | 244           | 1440            | Odd/19<br>Even/19 | Odd/244<br>Even/243 | Odd/262.5<br>Even/262.5 |

| NTSC ( 4fsc )                    | 28.636MHz          | 1820        | 32             | 120           | 252           | 1536            | Odd/19<br>Even/19 | Odd/244<br>Even/243 | Odd/262.5<br>Even/262.5 |

| PAL / SECAM<br>D1(576I)          | 27.000MHz          | 1728        | 24             | 120           | 264           | 1440            | Odd/24<br>Even/25 | Odd/288<br>Even/288 | Odd/312.5<br>Even/312.5 |

| D2(480P)                         | 27.000MHz          | 1716        | 32             | 120           | 244           | 1440            | 42                | 483                 | 525                     |

| D2(576P)                         | 27.000MHz          | 1728        | 24             | 120           | 264           | 1440            | 49                | 576                 | 625                     |

| EGA<br>400 x 234                 | 7.9930MHz          | 1016        | 44             | 80            | 172           | 800             | 28                | 234                 | 262                     |

| EGA<br>480 x 234                 | 9.58216MHz         | 1218        | 54             | 80            | 204           | 960             | 28                | 234                 | 262                     |

| WVGA                             | 33.333MHz          | 2120        | 144            | 120           | 376           | 1600            | 42                | 483                 | 525                     |

| 800 x 480                        | 33.231MHz          | 2112        | 40             | 120           | 300           | 1772            | 42                | 483                 | 525                     |

Note: Where the FIFO mode is used in asynchronous sampling operations with fixed clock, the 1-field sampling error accumulated in the line immediately following the fall of VVALID is reset. Therefore, the pixel count for the line that was reset will change. In addition, where the condition of VTR and other signals is poor in the FIFO-2 mode, the FIFO reset line might break in before the fall of VVALID.

"V blank", "Active lines", and "Total lines" in the table above indicate the period

The digital lines 1716T (NTSC, 525) and 1728T (PAL, 625) varies due to the sampling error when this LSI is operated in the asynchronous sampling mode.

When used in the FIFO mode, although there is no variation in the number of pixels between valid lines due to the pixel count compensation function, the line immediately after VVALID has fallen varies due to FIFO reset. In particular, when non-standard signals such as of a VTR are input, the line immediately after VVALID falls varies widely depending on the degree of the instability of that input signal, and when the error is large the change occurs immediately before the fall of VVALID.

Further, EAV or SAV may not be guaranteed in the case of non-standard signals in which the number of lines increases or decreases with respect to the reference value.

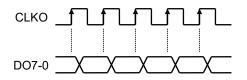

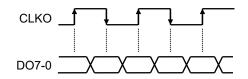

#### 6.2.3 Data Clock Output

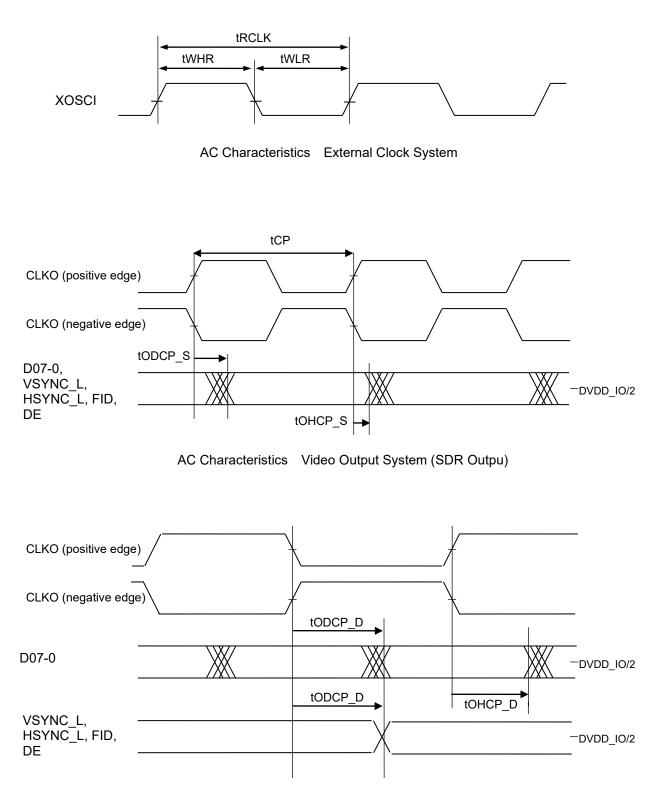

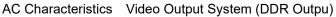

Data clock (CLKO) selectable single data rate mode(SDR) or dual data rate mode(DDR). In SDR mode output data is synchronous to positive edge or negative edge of CLKO. In DDR mode output data is synchronous to both positive edge and negative edge.

(a) SDR mode (positive edge)

| #05h/bit[1:0] | Data clock format |

|---------------|-------------------|

| 10            | SDR mode          |

| 01            | DDR mode          |

| 00/11         | Inhibit           |

## 7. Image Quality Adjustment

There are the following control registers for image quality adjustment in video decoder section and scaler section. The registers in the video decoder section are effective for analog video input, while the registers in scaler section are effective for both analog and digital video input.

Registers for image quality adjustment in video decoder section

| •Luminance level adjustment    | : | Adjusts luminance level of analog video input.<br>Capable of setting AGC (automatic luminance<br>adjustment) / MGC (manual luminance adjustment) /<br>Peak AGC.                                                                                                                                                                              |

|--------------------------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •Color level adjustment        | : | Adjusts color difference level of analog video input.<br>Capable of setting ACC (automatic color<br>adjustment) / MCC (manual color adjustment).                                                                                                                                                                                             |

| •Contour correction and coring | : | Corrects contour correction of analog video input.                                                                                                                                                                                                                                                                                           |

| •Contrast adjustment           | : | Adjustable around 128 with a slope ranging from $1/32$ to $63/32$ .                                                                                                                                                                                                                                                                          |

| •Luminance offset adjustment   | : | Capable of adjusting the analog video input luminance<br>between -7 and +7 IRE(for Composite, YPbPr inputs).<br>Capable of adjusting the analog video input luminance<br>between -128 and +127 LSB(for Composite, YPbPr<br>RGB inputs).                                                                                                      |

| •Hue control                   | : | Capable of adjusting the analog video input color<br>phase at an adjustment angle ranging from $-178.6^{\circ}$ to<br>$+180^{\circ}$ .<br>(Setting disabled for the SECAM or component video input.)<br>Capable of adjusting the analog video input color<br>phase at an adjustment angle ranging from $-45^{\circ}$ to<br>$+44.6^{\circ}$ . |

#### 8. STATUS and Interruption Outputs

The status detection result is output as the STATUS or interrupt signal.

The STAUS output outputs the current status detection result on the video decoder section (e.g., HPLL lock detection, NTSC/PAL automatic discrimination, VBID detection status). The internal register selects the status detection result to output.

The interruption output outputs an interrupt when there is a change to any of the video decoder section status detection results. Each status detection result is maskable.

(The status retention until the interrupt is cleared is not performed.)

- •Discrimination result of input format

- •Detection/non-detection of VBID

- •Detection/non-detection of light electric field state and VTR input (interrupt output only, not output from a STATUS terminal)

- •Monitoring of AFC operation status

- •Monitoring of input synchronization detection status

- •Monitoring of line lock state by internal PLL

#### 9. Sleep Function

The ML86V7675 has the sleep function for suppressing the power consumption by using SLEEP input or a control register.

| Sleep control              | Internal clock                        | Analog operation | Output port                                            |

|----------------------------|---------------------------------------|------------------|--------------------------------------------------------|

| Control register<br>(#FFh) | Stops except the I2C<br>control clock | AFE. ADC. HPLL.  | VSYNC_L, HSYNC_L, FID, DE, CLKO,<br>DO7-0 : "L" output |

| SLEEP input                | Stops oscillation                     | Sleep            | VSYNC_L, HSYNC_L, FID, DE, CLKO, DO7-0 : "HIZ"         |

#### 10. I<sup>2</sup>C Bus Interface

Each function block of the ML86V7675 controls the operation by writing data to the control register. The control register is accessible via the  $I^2C$  bus interface.

The I<sup>2</sup>C bus slave address is selectable from the following two addresses according to the pin setting.

| Slave address   | SAS |

|-----------------|-----|

| 80h (1000_000x) | 0   |

| 82h (1000_001x) | 1   |

In the I<sup>2</sup>C bus communication, the 1-byte data following the slave address is used as the register address (beginning address).

The 2 types of addressing modes are available for accessing a control register.

#### (1) Address increment mode

This mode is selected in the default state. When two or more data are sequentially accessed, the register address is incremented starting from the specified beginning address. This is useful to access a contiguous register address area.

(2) Address circulating mode

One to four addresses from the beginning address of the register can be accessed in a circular fashion. It is useful to access the same address for multiple times (the number of circulating is 1) or access 2 - 4 addresses in a circular fashion.

| (a) Register Write Format                                           |  |  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Write data to the specified register address.                       |  |  |  |  |  |  |  |  |  |

| S Slave address W A Beginning address of the A Written data 1 A     |  |  |  |  |  |  |  |  |  |

| S: Start condition Written data n A P                               |  |  |  |  |  |  |  |  |  |

| A: Acknowledge (slave)<br>P: Stop condition<br>W = "0" (write)      |  |  |  |  |  |  |  |  |  |

| (b) Register Read Format                                            |  |  |  |  |  |  |  |  |  |

| Read data from the specified register address.                      |  |  |  |  |  |  |  |  |  |

| S Slave address W A Beginning address of the A Sr Slave address R A |  |  |  |  |  |  |  |  |  |

| $\longrightarrow$ Read data 1 Am $\cdots$ Read data n Am P          |  |  |  |  |  |  |  |  |  |

| S: Start<br>Sr: Restart                                             |  |  |  |  |  |  |  |  |  |

| A: Acknowledge (slave)<br>A <sub>m</sub> : Acknowledge (master)     |  |  |  |  |  |  |  |  |  |

| P: Stop<br>W = "0" (write)<br>R = "1" (Read)                        |  |  |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |  |  |

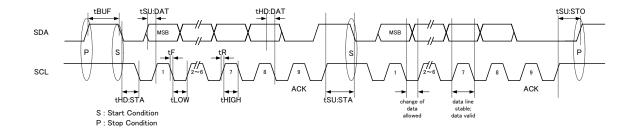

#### I<sup>2</sup>C Bus Interface Basic Timing

The SDA value should not be changed while SCL is "H" except for the start condition/stop condition (S/P). Communicate in the  $I^2C$  bus. after all the power supplies have reached the specified values and a stable clock has been input.

#### I<sup>2</sup>C Standard Table (Standard Mode)

| Symbol  | Parameter                  | Min    | Тур | Max  | Unit |

|---------|----------------------------|--------|-----|------|------|

| fSCL    | SCL Frequency              | 0      | -   | 100  | KHz  |

| tBUF    | Bus Open Time              | 4.7    | -   | -    | μs   |

| tHD:STA | Start Condition Hold Time  | 4.0    | -   | -    | μs   |

| tLOW    | Clock LOW Period           | 4.7    | -   | -    | μs   |

| tHIGH   | Clock HIGH Period          | 4.0    | -   | -    | μs   |

| tSU:STA | Start Condition Setup Time | 4.7    | -   | -    | μs   |

| tHD:DAT | Data Hold Time             | 0(300) | -   | -    | ns   |

| tSU:DAT | Data Setup Time            | 250    | -   | -    | ns   |

| tR      | Line Rise Time             | -      | -   | 1000 | ns   |

| tF      | Line Fall Time             | -      | -   | 300  | ns   |

| tSU:STO | Stop Condition Setup Time  | 4.0    | -   | -    | μs   |

#### I<sup>2</sup>C Standard Table (Fast Mode)

| Symbol  | Parameter                  | Min    | Тур | Max | Unit |

|---------|----------------------------|--------|-----|-----|------|

| fSCL    | SCL Frequency              | 0      | -   | 400 | KHz  |

| tBUF    | Bus Open Time              | 1.3    | -   | -   | μs   |

| tHD:STA | Start Condition Hold Time  | 0.6    | I   | -   | μs   |

| tLOW    | Clock LOW Period           | 1.3    | I   | -   | μs   |

| tHIGH   | Clock HIGH Period          | 0.6    | I   | -   | μs   |

| tSU:STA | Start Condition Setup Time | 0.6    | -   | -   | μs   |

| tHD:DAT | Data Hold Time             | 0(300) | -   | -   | ns   |

| tSU:DAT | Data Setup Time            | 100    | I   | -   | ns   |

| tR      | Line Rise Time             | -      | I   | 300 | ns   |

| tF      | Line Fall Time             | -      | -   | 300 | ns   |

| tSU:STO | Stop Condition Setup Time  | 0.6    | -   | -   | μs   |

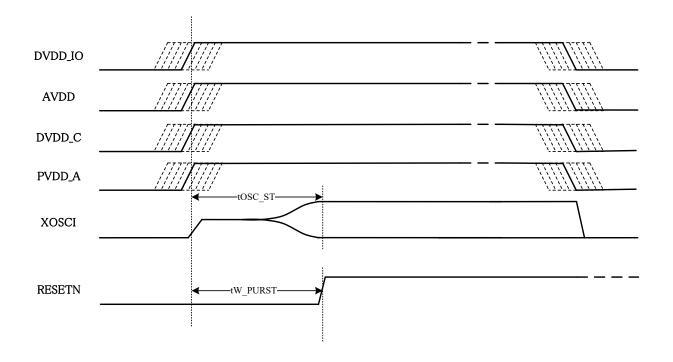

#### 11. Power on Sequence

When turning on the power, follow the sequence shown in the figure below:

#### Power On/Off Sequence

There are no restrictions on the power-on sequence between the above four power supplies (DVDD\_IO, AVDD, DVDD\_C, PVDD\_A,): Those power supplies can be turned on starting from any of them.

| Parameter                      | Symbol   | Min. | Тур. | Max. | Unit | Remarks |

|--------------------------------|----------|------|------|------|------|---------|

| The Oscillator activation time | tOSC_ST  |      |      | 10   | ms   |         |

| Reset time after power on      | tW_PURST | 10   | _    | _    | ms   |         |

This LSI should be used after the specified voltages have been applied to all the power supplies.

When applying a voltage to any input pin, do so after making sure that the power supply voltages have stabilized in the specified levels.

Apply reset after all the power supplies have reached the specified values and a stable clock has been input.

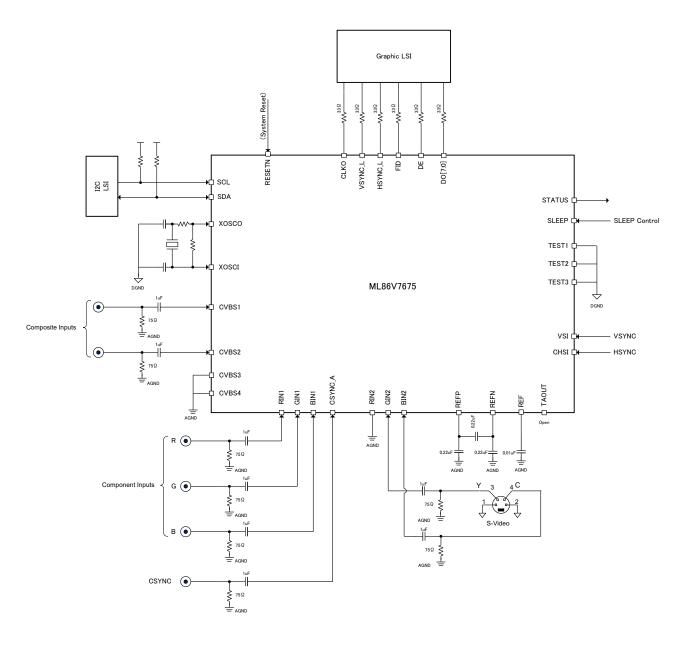

## 12. Example of Application Circuit

OExample of Generic Application Circuit

The example of the circuit appears here just for the purpose to show the application example, and then does not guarantee its characteristics. When using this LSI, verify the operation with the best suited circuit elements and circuit configurations for your system.

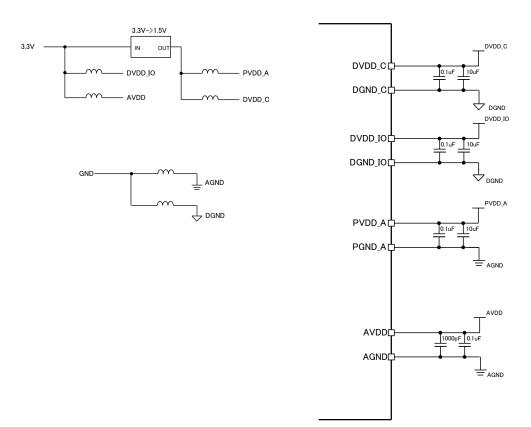

#### OExample of Power Supply/Ground Separation

[Notes on Board Layout]

- 1. It is recommended to add a damping resistor for digital output signal connection to reduce any digital noise.

- Connection with ceramic capacitors of about 0.1µF and 10µF is recommended between each of digital power supply (DVDD\_IO, DVDD\_C) and digital ground (DGND).

- Connection with ceramic capacitors of about 1000pF and 0.1μF is recommended between analog power supply (AVDD) and analog ground (AGND). Connection with ceramic capacitors of about 0.1μF and 10μF is recommended between analog power supply (PVDD\_A) and analog ground (AGND).

- 4. Avoid placing any noise source around TAOUT.

- 5. Avoid placing any noise source around REF, REFP and REFP. Wire as short as possible.

- 6. For the analog video signals, shorten the distance from the coupling capacitor to the input pin of the device as much as possible to avoid inducement interference.

- 7. It is recommended to assign large area for the analog power supply (AVDD) and the analog ground (AGND) for good separation from the digital power supply and the ground.

The example of the circuit appears here just for the purpose to show the application example, and then does not guarantee its characteristics. When using this LSI, verify the operation with the best suited circuit elements and circuit configurations for your system.

## 13. Electrical Characteristics

### **Absolute Maximum Ratings**

| Parameter                             | Symbol  | Condition                            | Rating                     | Unit |

|---------------------------------------|---------|--------------------------------------|----------------------------|------|

| Power supply voltage (for analog)     | AVDD    |                                      | –0.3 to +4.6               |      |

| Power supply voltage (for HPLL)       | PVDD_A  |                                      | -0.3 to +2.0               |      |

| Power supply voltage (for logic core) | DVDD_C  |                                      | -0.3 to +2.0               |      |

| Power supply voltage (for I/O)        | DVDD_IO | AGND = 0 V<br>PGND A = 0 V           | –0.3 to +4.6               | V    |

| Analog input voltage                  | VAI     | $DGN\overline{D} = 0 V$<br>Ta = 25°C | -0.3 to AVDD+0.3           | v    |

| Logic input voltage                   | VDI1    | 14 - 25 0                            | -0.3 to DVDD_IO+0.3        |      |

| Logic input voltage (5 V tolerant)    | VDI2    |                                      | -0.3 to +6.0 <sup>*1</sup> |      |

| Logic output voltage                  | VO      |                                      | -0.3 to DVDD_IO+0.3        |      |

| Output short-circuit current          | IOS     | _                                    | 16                         | mA   |

| Power dissipation                     | PD      | Ta = 85°C                            | 1.0                        | W    |

| Storage temperature                   | Tstg    | —                                    | –55 to +125                | °C   |

Note: Absolute maximum ratings are the marginal values that do not cause physical damage to the device. The device quality might be damaged if the rating of any one of these items is exceeded even for a moment. Be sure to use within this rating.

\*1: Specified when power is supplied.

### **Recommended Operating Conditions**

| Parameter                             | Symbol  | Condition    | Min. | Тур. | Max. | Unit |

|---------------------------------------|---------|--------------|------|------|------|------|

| Power supply voltage (for analog)     | AVDD    | AGND = 0 V   | 3.0  | 3.3  | 3.6  |      |

| Power supply voltage (for HPLL)       | PVDD_A  | PGND_A = 0 V | 1.35 | 1.5  | 1.65 | V    |

| Power supply voltage (for logic core) | DVDD_C  | DGND = 0 V   | 1.35 | 1.5  | 1.65 | v    |

| Power supply voltage (for I/O)        | DVDD_IO | DGND = 0 V   | 3.0  | 3.3  | 3.6  |      |

| Ambient temperature                   | Та      |              | -40  | 25   | +85  | °C   |

Note: Also avoid the situation where only some power supplies are powered on/off. All power supplies must be on or off.

## Electrical Characteristics

• DC Characteristics

|                            |                               |                     | $DVDD_IO, AVDD = 3.3$<br>DGND, A                         |      |      | / , Ta = -40 to |      |