Dear customer

ROHM Co., Ltd. ("ROHM"), on the 1st day of April, 2024, has absorbed into merger with 100%-owned subsidiary of LAPIS Technology Co., Ltd.

Therefore, all references to "LAPIS Technology Co., Ltd.", "LAPIS Technology" and/or "LAPIS" in this document shall be replaced with "ROHM Co., Ltd." Furthermore, there are no changes to the documents relating to our products other than the company name, the company trademark, logo, etc.

Thank you for your understanding.

ROHM Co., Ltd. April 1, 2024

## Dear customer

LAPIS Semiconductor Co., Ltd. ("LAPIS Semiconductor"), on the 1<sup>st</sup> day of October, 2020, implemented the incorporation-type company split (shinsetsu-bunkatsu) in which LAPIS established a new company, LAPIS Technology Co., Ltd. ("LAPIS Technology") and LAPIS Technology succeeded LAPIS Semiconductor's LSI business.

Therefore, all references to "LAPIS Semiconductor Co., Ltd.", "LAPIS Semiconductor" and/or "LAPIS" in this document shall be replaced with "LAPIS Technology Co., Ltd."

Furthermore, there are no changes to the documents relating to our products other than the company name, the company trademark, logo, etc.

Thank you for your understanding.

LAPIS Technology Co., Ltd. October 1, 2020

# ML7631

$13.56 \mathrm{MHz}$  wireless charging Tx LSI

The ML7631 is a wireless charging Tx LSI using 13.56MHz carrier frequency, which enables to feed 200mW wirelessly to an Rx device using the ML7630. The ML7631 controls wireless charging and data communication with the ML7630.

ML7631 is equipped with function to detect the illegal situation such as disappearance of the Rx device. This is an ideal solution for small rechargeable devices such as headset, ear-pads and wearables.

## Features

- Power transmission control

- Power transmission circuit embedded

- Abnormaly detection by software control and hardware control(voltage and current monitoring)

- Communication control

- Command generation function for ML7630 included

- Communication speed: 212kbps (13.56MHz/64)

- 1kbyte data flash for storing some data contents

- Host interface(I<sup>2</sup>C slave)

- Normal mode(100kbit/s), Fast mode(400kbit/s) available

- Each internal controller and external HOST microcontroller can access register function

- General Port(PORT)

- Input/Output port×11ch

- Reset

- Reset by RESET\_N port

- Power on reset by magnetic field detection

- Reset by WDT overflow

- Clock

- Low speed clock : Built-in RC oscillation (32.768kHz) for internal timer

- High speed clock : Crystal osillation(27.12MHz) 6.78MHz is used inside

- Package

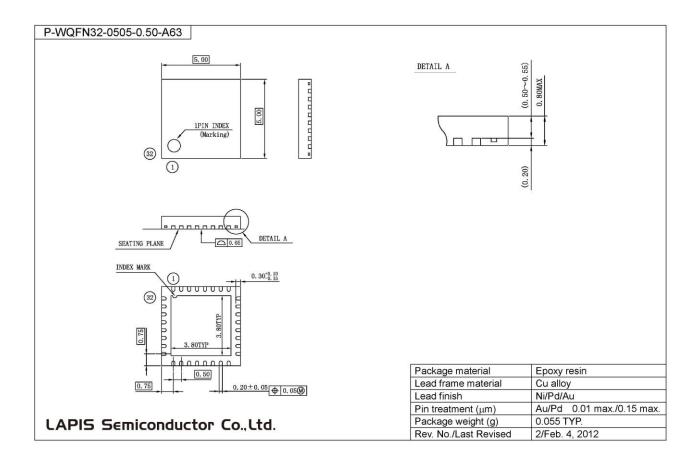

- WQFN 32 pin (P-WQFN32-0505-0.50)

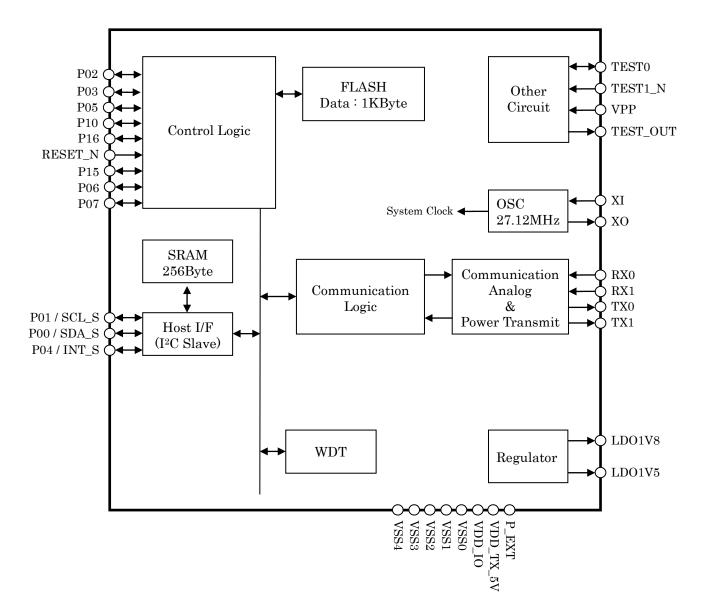

Functional block structure

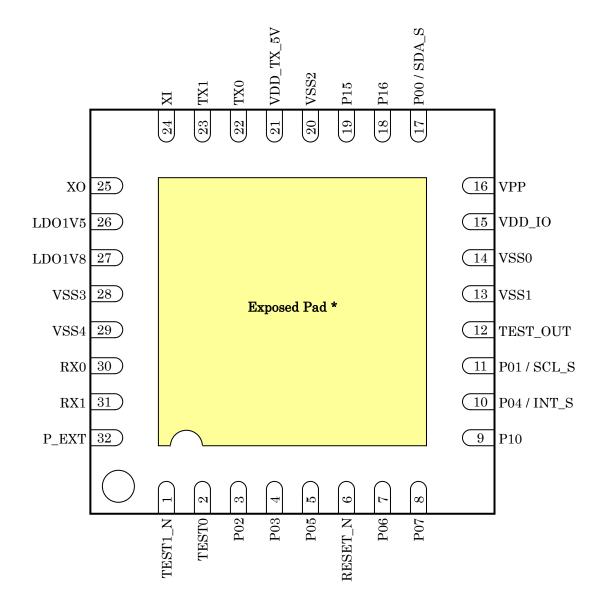

## Pin assignment (Top view)

\* Solder the exposed pad onto the PCB

## Pin description

#### • Power · GND · reference voltage pins

| PIN No. | Pin name  | In reset<br>(*1) | I/O<br>(*2) | Active<br>Level | Description              | Process in not use |

|---------|-----------|------------------|-------------|-----------------|--------------------------|--------------------|

| 14      | VSS0      |                  |             |                 |                          |                    |

| 13      | VSS1      |                  |             |                 |                          |                    |

| 20      | VSS2      | -                | -           | – Ground        |                          | -                  |

| 28      | VSS3      |                  |             |                 |                          |                    |

| 29      | VSS4      |                  |             |                 |                          |                    |

| 15      | VDD_IO    | -                | -           | -               | Logic IO voltage         | -                  |

| 26      | LDO1V5    | H(A)             | OA          | -               | Core 1.5V voltage output | -                  |

| 27      | LDO1V8    | H(A)             | OA          | -               | ADC 1.8V voltage output  | -                  |

| 32      | P_EXT     | -                | -           | -               | External voltage (5V)    | -                  |

| 21      | VDD_TX_5V | _                | _           | _               | TX voltage (5V)          | _                  |

## • Analog signal pins

| PIN No. | Pin name | In reset<br>(*1) | I/O<br>(*2) | Supply<br>Power | Active<br>Level | Description                              | Process in<br>not use |

|---------|----------|------------------|-------------|-----------------|-----------------|------------------------------------------|-----------------------|

| 30      | RX0      | -                | IA          | -               | -               | RF Data receiving                        | -                     |

| 31      | RX1      | -                | A           | -               | -               | RF Data receiving                        | -                     |

| 22      | TX0      | Z                | OA          | VDD_TX_         | -               | <ul> <li>RF Data transmitting</li> </ul> |                       |

| 23      | TX1      | Z                | OA          | 5V              | -               | RF Data transmitting                     | -                     |

## Clock pins

| PIN No. | Pin name | In reset<br>(*1) | I/O<br>(*2) | Supply<br>Power | Active<br>Level | Description              | Process in<br>not use |

|---------|----------|------------------|-------------|-----------------|-----------------|--------------------------|-----------------------|

| 24      | XI       |                  |             | LDO1V5          | -               | 27.12MHz oscillation pin | -                     |

| 25      | XO       | 0                | 0           | LDO1V5          | -               | 27.12MHz oscillation pin | _                     |

## • Reset pin

| PIN No | . Pin name | In reset<br>(*1) | I/O<br>(*2) | Supply<br>Power | Active<br>Level | Description | Process in not use |

|--------|------------|------------------|-------------|-----------------|-----------------|-------------|--------------------|

| 6      | RESET_N    | PU               |             | VDD_IO          | L               | Reset input | Open               |

• General pins

## Since the settings differ depending on the FW Ver., refer to the application note for details.

| PIN No. | Pin name       | In reset<br>(*1) | I/O<br>(*2)        | Supply<br>Power | Active<br>Level | Description                                               |

|---------|----------------|------------------|--------------------|-----------------|-----------------|-----------------------------------------------------------|

| 17      | P00 /<br>SDA_S | Z                | I/O                | VDD_IO          | -               | Input/Output port<br>HostIF(I <sup>2</sup> C slave) Data  |

| 11      | P01 /<br>SCL_S | Z                | I/O                | VDD_IO          | -               | Input/Output port<br>HostIF(I <sup>2</sup> C slave) Clock |

| 3       | P02            | Z                | I/O                | VDD_IO          | -               | Input/Output port                                         |

| 4       | P03            | Z                | I/O                | VDD_IO          | -               | Input/Output port                                         |

| 10      | P04 /<br>INT_S | Z                | I/O                | VDD_IO          |                 | Input/Output port<br>HostIF INToutput                     |

| 5       | P05            | Z                | I/O                | VDD_IO          | -               | Input/Output port                                         |

| 7       | P06            | Z                | I <sub>DA</sub> /O | VDD_IO          | -               | Input/Output port                                         |

| 8       | P07            | Z                | I <sub>DA</sub> /O | VDD_IO          | -               | Input/Output port                                         |

| 9       | P10            | Z                | I/O                | VDD_IO          | -               | Input/Output port                                         |

| 19      | P15            | Z                | I <sub>DA</sub> /O | VDD_IO          |                 | Input/Output port                                         |

| 18      | P16            | Z                | I/O                | VDD_IO          | -               | Input/Output port                                         |

#### ML7631

## • Test pins

| PIN No. | Pin name | In reset<br>(*1) | I/O<br>(*2) | Supply<br>Power | Active<br>Level | Description                 | Process in not use |

|---------|----------|------------------|-------------|-----------------|-----------------|-----------------------------|--------------------|

| 2       | TEST0    | PD               | I/O         | VDD_IO          | Н               | For test/For debugger       | Open               |

| 1       | TEST1_N  | PU               | I           | VDD_IO          | L               | For test/For debugger       | Open               |

| 16      | VPP      | -                | IA          | -               | -               | Power supply for Flash test | Open               |

| 12      | TEST_OUT | L(A)             | 0           | VDD_IO          | -               | Test output port            | Open               |

(\*1) In reset state :

| In reset state . |      |   |                         |

|------------------|------|---|-------------------------|

| Pin state        | L(O) | : | "L" level output        |

| definition       | H(O) | : | "H" level output        |

| in reset state   | L(A) | : | Analog "L" level output |

|                  |      |   | Analog "H" level output |

|                  | PU   | : | Pull-Up                 |

|                  | PD   | : | Pull-Down               |

|                  | Z    | : | Floating state          |

(\*2) I/O : For I/O definition, using under abbreviation

| I/O definition |                    |   | Analog input                                            |

|----------------|--------------------|---|---------------------------------------------------------|

| I/O demilion   | IA                 |   | Analog input                                            |

|                | OA                 | : | Analog output                                           |

|                | Ι                  | : | Digital input                                           |

|                | I/O                | : | Bi-directional pin                                      |

|                | I <sub>DA</sub> /O | : | Bi-directional pin, Input are digital and analog shared |

|                | 0                  | : | Digital output                                          |

## Electrical characteristics

## • Absolue maximum ratings

| Item                         | Symbol    | Condition             | Rating                          | Unit |

|------------------------------|-----------|-----------------------|---------------------------------|------|

| Power voltage (Digital IO)   | VDD_IO    | Ta=25°C               | -0.3 to +6.5                    | V    |

| Regulator input voltage      | P_EXT     | Ta=25°C               | -0.3 to +6.5                    | V    |

| Tx power voltage             | VDD_TX_5V | Ta=25°C               | -0.3 to +6.5                    | V    |

| Core & crystal power voltage | LDO1V5    | Ta=25°C               | -0.3 to +2.0                    | V    |

| Analog power voltage         | LDO1V8    | Ta=25°C               | -0.3 to +6.5                    | V    |

| Input voltage                | Vdin      | Ta=25°C, Digital port | -0.3 to V <sub>DD_IO</sub> +0.3 | V    |

|                              |           | Ta=25°C, TX0/TX1      | 6.5                             | V    |

|                              |           | Ta=25°C, RX0/RX1      | 12                              | V    |

| Input current                | li        | Ta=25°C, Digital port | -10 to +10                      | mA   |

| Output voltage               | Vdo       | Ta=25°C, Digital port | -0.3 to VDD_IO+0.3              | V    |

| Digital output current       | Ido       | Ta=25°C               | -12 to +20                      | mA   |

| Power dissipation            | PD        | Ta=25°C               | 2                               | W    |

| Storage temperature          | Tstg      |                       | -55 to +150                     | °C   |

#### • Recommended operating conditions

| Item                                 | Symbol                             | Condition                                          | Min.          | Тур.  | Max.          | Unit |

|--------------------------------------|------------------------------------|----------------------------------------------------|---------------|-------|---------------|------|

| Operating voltage                    | VDD_IO                             |                                                    | 1.8           | _     | 5.5           | V    |

|                                      | P_EXT                              |                                                    | 4.5           | 5.0   | 5.5           | V    |

|                                      | VDD_TX_5V                          | Normal                                             | 4.5           | 5.0   | 5.5           | V    |

| Operating temperature                | Ta1                                | Normal                                             | -40           | +25   | +85           | °C   |

|                                      | Ta2                                | Power transmission                                 | -10           | +25   | +50           | °C   |

| Crystal oscillator frequency         | $f_{XTL}$                          |                                                    | Тур<br>-0.05% | 27.12 | Тур<br>+0.05% | MHz  |

| Crystal oscillator load capacitance* | C <sub>DL</sub><br>C <sub>GL</sub> | NIHON DEMPA KOGYO<br>Co., Ltd.<br>NX2016SA(CL=6pF) | Тур<br>-1%    | 8     | Тур<br>+1%    | pF   |

|                                      | C <sub>DL</sub><br>C <sub>GL</sub> | NIHON DEMPA KOGYO<br>Co., Ltd.<br>NX2016SA(CL=8pF) | Тур<br>-1%    | 12    | Тур<br>+1%    | рF   |

|                                      | C <sub>DL</sub><br>C <sub>GL</sub> | KYOCERA Corporation<br>CX1210SB(CL=6pF)            | Тур<br>-1%    | 8     | Тур<br>+1%    | pF   |

|                                      | C <sub>DL</sub><br>C <sub>GL</sub> | KYOCERA Corporation<br>CX2016SB(CL=8pF)            | Тур<br>-1%    | 12    | Тур<br>+1%    | pF   |

|                                      | C <sub>DL</sub><br>C <sub>GL</sub> | TXC<br>SMD SEAM SEALING<br>XTAL 2.0 × 1.6(CL=8pF)  | Тур<br>-1%    | 12    | Тур<br>+1%    | pF   |

| LDO1V5 outside Capacitor             | $C_{LDO1V5}$                       |                                                    | Тур<br>-10%   | 2.2   | Тур<br>+10%   | μF   |

| P_EXT outside Capacitor              | C <sub>PEXT</sub>                  |                                                    | Тур<br>-10%   | 2.2   | Тур<br>+10%   | μF   |

| LDO1V8 outside Capacitor             | $C_{LDO1V8}$                       |                                                    | Тур<br>-10%   | 0.47  | Тур<br>+10%   | μF   |

| VDD_IO outside Capacitor             |                                    |                                                    | Тур<br>-10%   | 0.1   | Тур<br>+10%   | μF   |

| VDD_TX_5V outside Capacitor          | $C_{TX5V}$                         |                                                    | Тур<br>-10%   | 2.2   | Тур<br>+10%   | μF   |

\*) The optimum capacitance value varies depending on the circuit board. Please consult with the Crystal oscillation circuit manufacturer.

• Flash memory operating conditions

| Item                             | Symbo            | Condition    | Range           | Unit  |

|----------------------------------|------------------|--------------|-----------------|-------|

| Operating temperature (Ambience) | T <sub>OP</sub>  | Write/erase  | -40 to +85      | °C    |

| Operating voltage                | P_EXT            | Write/erase  | 2.7 to 5.5      | V     |

| Write time                       | $C_{\text{EPD}}$ | _            | 10,000          | times |

| Erase unit                       | _                | Sector erase | 1               | KB    |

| Erase time (Maximum)             | -                | Sector erase | 100             | ms    |

| Write time                       | _                | _            | 1 word (2 byte) | _     |

#### • Power transmission charactaristics

|                          | (`              | /DD_IO=1.8 to 5.5V, VDD_TX_5\ | /=4.5 to 5.5 | V, VSS=0V | , Ta=-40 to | +85°C) |

|--------------------------|-----------------|-------------------------------|--------------|-----------|-------------|--------|

| Item                     | Symbol          | Condition                     | Min.         | Тур.      | Max.        | Unit   |

| TX0/TX1 output frequency | F <sub>TX</sub> | _                             |              | 13.56     | -           | MHz    |

#### • Oscillation characteristic

|                                                          |                  | (VDD_IO=  | 1.8 to 5.5V, | P_EXT=4.5 | 5 to 5.5V, V | SS=0V) |

|----------------------------------------------------------|------------------|-----------|--------------|-----------|--------------|--------|

| Item                                                     | Symbol           | Condition | Min.         | Тур.      | Max.         | Unit   |

| Low speed embedded RC oscillator frequency <sup>*1</sup> | f <sub>LCR</sub> | -         | -5%          | 32.768    | +5%          | kHz    |

| *1 · 102/ cycle average                                  |                  | •         |              |           |              |        |

1:1024 cycle average

#### • Reset characteristics

|                                      | (VDD_IO=1.8 to 5.5V, P_EXT=4.5 to 5.5V, VSS=0V, Ta=-40 to +85°C) |           |      |      |      | +85°C) |

|--------------------------------------|------------------------------------------------------------------|-----------|------|------|------|--------|

| Item                                 | Symbol                                                           | Condition | Min. | Тур. | Max. | Unit   |

| RESET_N pulse width                  | P <sub>RST</sub>                                                 | _         | 200  | _    | _    | μs     |

| RESET_N noise removal<br>Pulse width | P <sub>NRST</sub>                                                | -         | _    | _    | 0.3  | μs     |

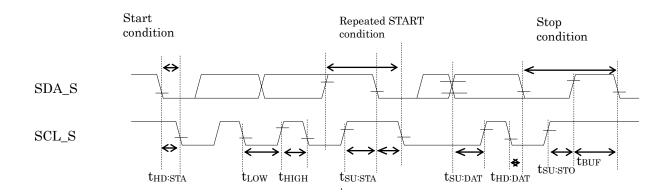

• AC characteristics (I<sup>2</sup>C bus interface: Standard mode 100 kHz)

| Ŷ                                                   |                         | (VDD_IO =1.8 to 5.5V, P_EXT=4.5 to 5.5V, VSS=0V, Ta=-40 to +85 |      |      | +85°C) |      |

|-----------------------------------------------------|-------------------------|----------------------------------------------------------------|------|------|--------|------|

| Parameter                                           | Symbol                  | Condition                                                      | Min. | Тур. | Max.   | Unit |

| SCL_S clock frequency                               | <b>f</b> <sub>SCL</sub> | _                                                              | -    | -    | 100    | kHz  |

| SCL_S hold time<br>(start/repeated start condition) | t <sub>HD:STA</sub>     | -                                                              | 4.0  | Ι    | -      | μs   |

| SCL_S "L" level time                                | t <sub>LOW</sub>        | _                                                              | 4.7  | _    | _      | μs   |

| SCL_S "H" level time                                | t <sub>ніGH</sub>       | _                                                              | 4.0  | _    | _      | μs   |

| SCL_S setup time<br>(repeated start condition)      | t <sub>SU:STA</sub>     | -                                                              | 4.7  | Ι    | -      | μs   |

| SDA_S hold time                                     | t <sub>HD:DAT</sub>     | _                                                              | 0    | -    | -      | μs   |

| SDA_S setup time                                    | t <sub>SU:DAT</sub>     | _                                                              | 0.25 | _    | _      | μs   |

| SDA_S setup time<br>(P: Stop condition)             | t <sub>SU:STO</sub>     | -                                                              | 4.0  | -    | -      | μs   |

| Bus free time                                       | t <sub>BUF</sub>        | -                                                              | 4.7  | —    | -      | μs   |

• AC characteristics (I<sup>2</sup>C bus interface: Fast mode 400 kHz)

| ,                                                   |                     | (VDD_IO =1.8 to 5.5V, P_EX | T=4.5 to 5.5 | SV, VSS=0V | ′, Ta=-40 to | +85°C) |

|-----------------------------------------------------|---------------------|----------------------------|--------------|------------|--------------|--------|

| Parameter                                           | Symbol              | Condition                  | Min.         | Тур.       | Max.         | Unit   |

| SCL_S clock frequency                               | f <sub>SCL</sub>    | -                          | -            | -          | 400          | kHz    |

| SCL_S hold time<br>(start/repeated start condition) | t <sub>HD:STA</sub> | -                          | 0.6          | _          | _            | μs     |

| SCL_S "L" level time                                | t <sub>LOW</sub>    | -                          | 1.3          | -          | -            | μs     |

| SCL_S "H" level time                                | t <sub>HIGH</sub>   | -                          | 0.6          | -          | _            | μs     |

| SCL_S setup time<br>(repeated start condition)      | t <sub>SU:STA</sub> | -                          | 0.6          | -          | -            | μs     |

| SDA_S hold time                                     | t <sub>HD:DAT</sub> | -                          | 0            | -          | -            | μs     |

| SDA_S setup time                                    | t <sub>SU:DAT</sub> | -                          | 0.1          | -          | _            | μs     |

| SDA_S setup time<br>(P: Stop condition)             | t <sub>SU:STO</sub> | -                          | 0.6          | -          | -            | μs     |

| Bus free time                                       | t <sub>BUF</sub>    | -                          | 1.3          | _          | _            | μs     |

When connecting the I2C slave to the I2C bus common to other devices, insert a multiplexer or level shifter between the I2C bus and ML7631.

• IO characteristics

| (Unless otherwise specified, VDD_IO=1.8 to 5.5V, P_EXT=4.5 to 5.5V, VSS=0V, Ta=-40 to +85°C) |        |                                                   |                |      |                |      |

|----------------------------------------------------------------------------------------------|--------|---------------------------------------------------|----------------|------|----------------|------|

| Item                                                                                         | Symbol | Condition                                         | Min.           | Тур. | Max.           | Unit |

| Output Voltage 1<br>(P00-P07, P10, P15, P16)                                                 | VOH1   | IOH=-1.0mA                                        | VDD_IO<br>-0.5 | -    | -              | V    |

| (100-107, 110, 113, 110)                                                                     | VOL1   | IOL=+0.5mA                                        | -              | _    | 0.4            | V    |

| Output Voltage 2<br>(P00-P07, P10, P15, P16)                                                 | VOL2   | 2.7V≤VDD_IO≤5.5V<br>IOL=+5.0mA                    | _              | -    | 0.6            | V    |

| (LED pin)                                                                                    |        | IOL=+2.0mA                                        | -              | _    | 0.4            | V    |

| Output Voltage 3<br>(SCL_S,SDA_S)<br>(I <sup>2</sup> C pin)                                  | VOL3   | IOL3= +3mA (I <sup>2</sup> Cspec)<br>(VDD_IO ≥2V) | _              | _    | 0.4            | V    |

| Output Voltage 4<br>(SCL_S,SDA_S)<br>(I <sup>2</sup> C mode selected)                        | VOL4   | IOL4= +2mA (I <sup>2</sup> Cspec)<br>(VDD_IO <2V) | _              | -    | VDD_IO<br>×0.2 | V    |

| Output Leakage 1<br>(P00-P07, P10, P15, P16,<br>SCL_S, SDA_S)                                | IOOH1  | VOH=VDD_IO<br>(at high impedance)                 | -              | -    | 1              | μA   |

|                                                                                              | IOOL1  | VOL=VSS<br>(at high impedance)                    | -1             | -    | -              | μΑ   |

| Input Current 1                                                                              | IIH1   | VIH1=VDD_IO                                       | -              | -    | 1              | μA   |

| (RESET_N, TEST1_N)                                                                           | IIL1   | VIL1=VSS                                          | -900           | -300 | -20            | μA   |

| Input Current 2<br>(TEST0)                                                                   | IIH2   | VIH2=VDD_IO                                       | 20             | 300  | 900            | μA   |

|                                                                                              | IIL2   | VIL2=VSS                                          | -1             | -    | _              | μA   |

|                                                                                              | IIH3   | VIH3=VDD_IO (In pull down)                        | 1              | 15   | 200            | μA   |

|                                                                                              | IIL3   | VIL3=VSS (In pull up)                             | -200           | -15  | -1             | μΑ   |

| Input Current 3<br>(P00-P07, P10, P15, P16)                                                  | IIH3Z  | VIH3=VDD_IO<br>(at high impedance)                | -              | -    | 1              | μA   |

|                                                                                              | IIL3Z  | VIL3=VSS<br>(at high impedance)                   | -1             | -    | -              | μΑ   |

| Input Voltage 1<br>(RESET_N, TEST0, TEST1_N,<br>P00-P07, P10, P15, P16)                      | VIH1   | -                                                 | 0.7×<br>VDD_IO | -    | VDD_IO         | V    |

|                                                                                              | VIL1   | -                                                 | 0              | -    | 0.3×<br>VDD_IO | V    |

| Input pin Capacitance<br>(RESET_N, TEST0, TEST1_N,<br>P00-P07, P10, P15, P16)                |        | f=10kHz<br>Vrms=50mV<br>Ta=25°C                   | _              | 10   | -              | pF   |

Typ. standard is at Ta=25°C, VDD\_IO=3.0V

• Power supply current

|                      | (VDD_IO=1.8 to 5.5V, P_EXT=4.5 to 5.5V, VSS=0V, Ta=-40 to |                                                                                                     |      |      |      | +85°C) |

|----------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|------|------|--------|

| Item                 | Symbol                                                    | Condition                                                                                           | Min. | Тур. | Max. | Unit   |

| Power supply current | IDD1                                                      | D1 HALT*1                                                                                           |      | 0.8  | 1.5  | mA     |

|                      | IDD2                                                      | CPU 6.78MHz operation<br>Peripherals stop                                                           | _    | 2.2  | 3.0  | mA     |

|                      | IDD3                                                      | CPU 6.78MHz operation<br>Power transmission mode<br>(100Ω instead of antenna<br>between TX0-TX1) *2 | -    | 85   | 105  | mA     |

\*1) CPU Stops. This status can be released by peripheral interrupt.

\*2) This condition and power supply current depend on the antenna.

If load resistance is small, the power supply current increases. It does not guarantee the current consumption when the system including the power receiving side is installed.

## Package dimensions

## Revision historys

|              |               | Pa                    | ge                    |                                                                                                               |

|--------------|---------------|-----------------------|-----------------------|---------------------------------------------------------------------------------------------------------------|

| Document No. | Issue Date    | Previous<br>Edition   | Current<br>Edition    | Change contents                                                                                               |

| PEDL7631-01  | Oct. 25, 2016 | -                     | -                     | Preliminary edition 1                                                                                         |

| FEDL7631-01  | Mar. 23, 2018 | -                     | -                     | Final edition 1                                                                                               |

| FEDL7631-02  | Jan. 15, 2019 | 9                     | 9                     | Add HALT description<br>Revise IO-pin description                                                             |

|              | Nov. 18, 2019 | 1<br>2<br>3<br>4<br>7 | 1<br>2<br>3<br>4<br>7 | Delet Unused block                                                                                            |

|              |               | 4<br>5                | 4<br>5                | Add Reset pin category<br>Rename Other pins to General pins<br>Added note for application note to general pin |

|              |               | 11                    | _                     | Delete Sample Circuit<br>(Described in the application note because it<br>depends on the FW)                  |

|              |               | 8                     | 8                     | Change wording of I2C notice                                                                                  |

|              |               | 9                     | 9                     | Add the conditions for current consumption during<br>power transmission<br>Change notice                      |

|              |               | 6                     | 6                     | Change note about external crystal capacity                                                                   |

|              |               |                       |                       |                                                                                                               |

|              |               |                       |                       |                                                                                                               |

#### Notes

- 1) The information contained herein is subject to change without notice.

- 2) Although LAPIS Semiconductor is continuously working to improve product reliability and quality, semiconductors can break down and malfunction due to various factors. Therefore, in order to prevent personal injury or fire arising from failure, please take safety measures such as complying with the derating characteristics, implementing redundant and fire prevention designs, and utilizing backups and fail-safe procedures. LAPIS Semiconductor shall have no responsibility for any damages arising out of the use of our Products beyond the rating specified by LAPIS Semiconductor.

- 3) Examples of application circuits, circuit constants and any other information contained herein are provided only to illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

- 4) The technical information specified herein is intended only to show the typical functions of the Products and examples of application circuits for the Products. No license, expressly or implied, is granted hereby under any intellectual property rights or other rights of LAPIS Semiconductor or any third party with respect to the information contained in this document; therefore LAPIS Semiconductor shall have no responsibility whatsoever for any dispute, concerning such rights owned by third parties, arising out of the use of such technical information.

- 5) The Products are intended for use in general electronic equipment (i.e. AV/OA devices, communication, consumer systems, gaming/entertainment sets) as well as the applications indicated in this document.

- 6) The Products specified in this document are not designed to be radiation tolerant.

- 7) For use of our Products in applications requiring a high degree of reliability (as exemplified below), please contact and consult with a LAPIS Semiconductor representative: transportation equipment (i.e. cars, ships, trains), primary communication equipment, traffic lights, fire/crime prevention, safety equipment, medical systems, servers, solar cells, and power transmission systems.

- 8) Do not use our Products in applications requiring extremely high reliability, such as aerospace equipment, nuclear power control systems, and submarine repeaters.

- 9) LAPIS Semiconductor shall have no responsibility for any damages or injury arising from non-compliance with the recommended usage conditions and specifications contained herein.

- 10) LAPIS Semiconductor has used reasonable care to ensure the accuracy of the information contained in this document. However, LAPIS Semiconductor does not warrant that such information is error-free and LAPIS Semiconductor shall have no responsibility for any damages arising from any inaccuracy or misprint of such information.

- 11) Please use the Products in accordance with any applicable environmental laws and regulations, such as the RoHS Directive. For more details, including RoHS compatibility, please contact a ROHM sales office. LAPIS Semiconductor shall have no responsibility for any damages or losses resulting non-compliance with any applicable laws or regulations.

- 12) When providing our Products and technologies contained in this document to other countries, you must abide by the procedures and provisions stipulated in all applicable export laws and regulations, including without limitation the US Export Administration Regulations and the Foreign Exchange and Foreign Trade Act.

- 13) This document, in part or in whole, may not be reprinted or reproduced without prior consent of LAPIS Semiconductor.

Copyright 2016-2019 LAPIS Semiconductor Co., Ltd.

# LAPIS Semiconductor Co., Ltd.

2-4-8 Shinyokohama, Kouhoku-ku, Yokohama 222-8575, Japan http://www.lapis-semi.com/en/