Dear customer

ROHM Co., Ltd. ("ROHM"), on the 1st day of April, 2024, has absorbed into merger with 100%-owned subsidiary of LAPIS Technology Co., Ltd.

Therefore, all references to "LAPIS Technology Co., Ltd.", "LAPIS Technology" and/or "LAPIS" in this document shall be replaced with "ROHM Co., Ltd." Furthermore, there are no changes to the documents relating to our products other than the company name, the company trademark, logo, etc.

Thank you for your understanding.

ROHM Co., Ltd. April 1, 2024

FEXK715x1\_AN\_PCB\_ design\_ Guidelines-01

# Bluetooth<sup>®</sup> low energy Module (MK71511/MK71521) Application Note PCB Design Guidelines for MK71511/MK71521

Issue Date: October 1, 2020

#### NOTES

- 1) The information contained herein is subject to change without notice.

- 2) When using LAPIS Technology Products, refer to the latest product information (data sheets, user's manuals, application notes, etc.), and ensure that usage conditions (absolute maximum ratings, recommended operating conditions, etc.) are within the ranges specified. LAPIS Technology disclaims any and all liability for any malfunctions, failure or accident arising out of or in connection with the use of LAPIS Technology Products outside of such usage conditions specified ranges, or without observing precautions. Even if it is used within such usage conditions specified ranges, semiconductors can break down and malfunction due to various factors. Therefore, in order to prevent personal injury, fire or the other damage from break down or malfunction of LAPIS Technology Products, please take safety at your own risk measures such as complying with the derating characteristics, implementing redundant and fire prevention designs, and utilizing backups and fail-safe procedures. You are responsible for evaluating the safety of the final products or systems manufactured by you.

- 3) Descriptions of circuits, software and other related information in this document are provided only to illustrate the standard operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. And the peripheral conditions must be taken into account when designing circuits for mass production. LAPIS Technology disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, and other related information.

- 4) No license, expressly or implied, is granted hereby under any intellectual property rights or other rights of LAPIS Technology or any third party with respect to LAPIS Technology Products or the information contained in this document (including but not limited to, the Product data, drawings, charts, programs, algorithms, and application examples, etc.). Therefore LAPIS Technology shall have no responsibility whatsoever for any dispute, concerning such rights owned by third parties, arising out of the use of such technical information.

- 5) The Products are intended for use in general electronic equipment (AV/OA devices, communication, consumer systems, gaming/entertainment sets, etc.) as well as the applications indicated in this document. For use of our Products in applications requiring a high degree of reliability (as exemplified below), please be sure to contact a LAPIS Technology representative and must obtain written agreement: transportation equipment (cars, ships, trains, etc.), primary communication equipment, traffic lights, fire/crime prevention, safety equipment, medical systems, servers, solar cells, and power transmission systems, etc. LAPIS Technology disclaims any and all liability for any losses and damages incurred by you or third parties arising by using the Product for purposes not intended by us. Do not use our Products in applications requiring extremely high reliability, such as aerospace equipment, nuclear power control systems, and submarine repeaters, etc.

- 6) The Products specified in this document are not designed to be radiation tolerant.

- 7) LAPIS Technology has used reasonable care to ensure the accuracy of the information contained in this document. However, LAPIS Technology does not warrant that such information is error-free and LAPIS Technology shall have no responsibility for any damages arising from any inaccuracy or misprint of such information.

- 8) Please use the Products in accordance with any applicable environmental laws and regulations, such as the RoHS Directive. LAPIS Technology shall have no responsibility for any damages or losses resulting non-compliance with any applicable laws or regulations.

- 9) When providing our Products and technologies contained in this document to other countries, you must abide by the procedures and provisions stipulated in all applicable export laws and regulations, including without limitation the US Export Administration Regulations and the Foreign Exchange and Foreign Trade Act..

- 10) Please contact a ROHM sales office if you have any questions regarding the information contained in this document or LAPIS Technology's Products.

- 11) This document, in part or in whole, may not be reprinted or reproduced without prior consent of LAPIS Technology.

- (Note) "LAPIS Technology" as used in this document means LAPIS Technology Co., Ltd.

Copyright 2020 LAPIS Technology Co., Ltd.

### LAPIS Technology Co., Ltd.

2-4-8 Shinyokohama, Kouhoku-ku,Yokohama 222-8575, Japan https://www.lapis-tech.com/en/

#### Preface

This application note describes the contents that you should be careful when designing a board equipped with Bluetooth<sup>®</sup> 5 compatible Bluetooth low energy module MK71511 and MK71521 made by Lapis Technology.

The following related documents are available, so please refer to them if necessary.

MK71511 Datasheet MK71521 Datasheet

•Bluetooth<sup>®</sup> is a registered trademark of Bluetooth SIG, Inc.

•All other company and product names are the trademarks or registered trademarks of the respective companies.

# Table of Contents

| NOTES                                                                                       | i   |

|---------------------------------------------------------------------------------------------|-----|

| Preface                                                                                     | ii  |

| Table of Contents                                                                           | iii |

| 1. MK71511/MK71521 Board Design Precautions                                                 |     |

| 1.1. Module bottom layout                                                                   | 1   |

| 1.2. PCB layout                                                                             | 2   |

| 1.3. Antenna Connection Wiring                                                              |     |

| 1.4. Power line                                                                             |     |

| 1.5. Unconnected terminals                                                                  |     |

| 1.6. Case 1 around the antenna (with no conductors placed to the left and right of antenna) |     |

| 1.7. Case 2 around the antenna (with conductors placed to the left and right of antenna)    |     |

| 2. Reference Land Pattern                                                                   |     |

| Revision history                                                                            |     |

|                                                                                             | 0   |

#### 1. MK71511/MK71521 Board Design Precautions

This document describes the contents that you should be careful when designing a board equipped with a Bluetooth low energy radio module (MK71511/MK71521).

#### 1.1. Module bottom layout

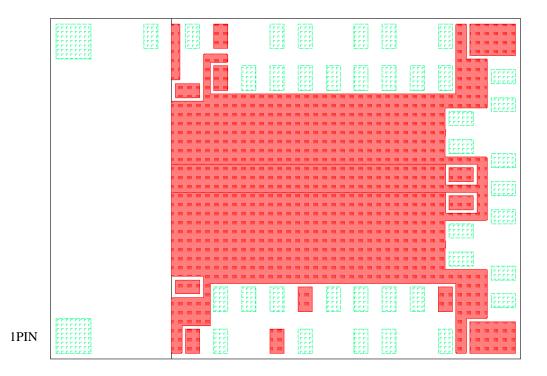

In Figure 1, The GND area is shown in red. The green areas represent individual signals. Resist is applied to the parts other than the terminals of the lowest layer. However, its effect may not be guaranteed in some cases.

When placing signal lines from each terminal of the MK71511/71521 module on layer 1 of the motherboard in use, or placing VIAs for signals, it is recommended to employ board design where such signal lines and VIAs are not placed on red and green areas in the lowest layer wiring diagram shown above to prevent signal short-circuit between boards.

Figure 1. MK71511/MK71521 Bottom layer layout

#### 1.2. PCB layout

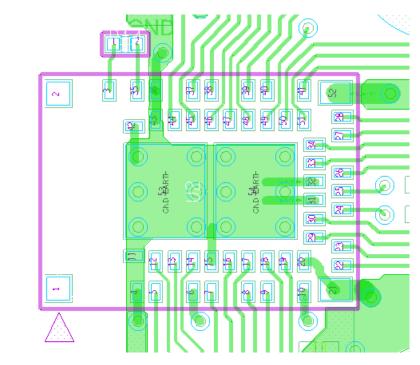

Figuire 2 shows a PCB top layer example.

Figure 2. Example of PCB top layer

#### 1.3. Antenna Connection Wiring

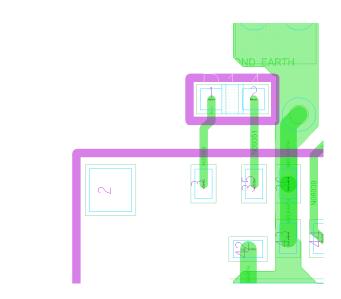

The ANT terminal (3PIN) and the RFIO terminal (35PIN) must be connected via the wiring of the customer manufactured board top layer . In addition, please mount jumper resistors such as antenna line wiring examples in the wiring line. Regarding wiring, it is desirable to use  $50\Omega$  impedance-controlled line at 2.4GHz, but if difficult, connect with as short a wire length as possible.

Figure 3. Example of antenna wiring

#### 1.4. Power line

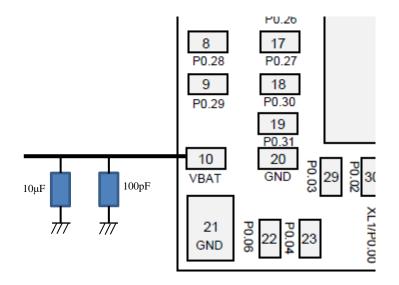

When wiring on the power terminal (VBAT 10PIN), we recommend a wiring width of 0.5 mm or more and a VIA diameter of 0.2 mm or more. If it is difficult to deploy a large VIA, use multiple smaller VIAs.

If the power line is noisy or the power supply voltage fluctuates frequently, it is recommended that the decoupling capacitor (example: 1 to 10  $\mu$ F) and bypass capacitor (example: 10 to 100 pF) be ground-aligned in parallel to the most recent power terminal (VBAT 10PIN).

Figure 4. Example of Power line

#### 1.5. Unconnected terminals

#### XL1 terminal (24PIN) and XL2 terminal (25PIN)

On the MK71511/MK71521, the XL1 terminal (24PIN) and XL2 terminal (25PIN) are connected to the crystal oscillator inside the module. Therefore, leave the terminals unconnected.

The MK71511A/MK71521A can be used as GPIO terminal forXL1 (24PIN) and XL2 (25PIN) terminal.

#### DCO terminal (7PIN)

The DCO terminal (7PIN) is a terminal for our testing. In either case, should not be connected.

#### P0.25 terminal (14PIN) and P0.26 terminal (16PIN) MK71521/MK71521A only

P0.02–0.31 is the GPIO terminal, and unused pins are usually open. However, if you are shipping products to the United States, when you use P0.25 terminal (14PIN) and P0.26 terminal (16PIN), connect a 10pF bypass capacitor between the two terminals and GND. If it is not used, connect to GND.

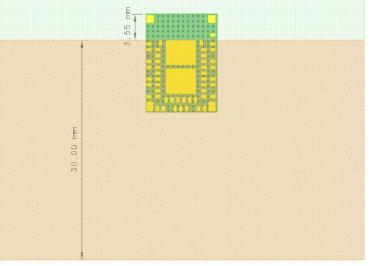

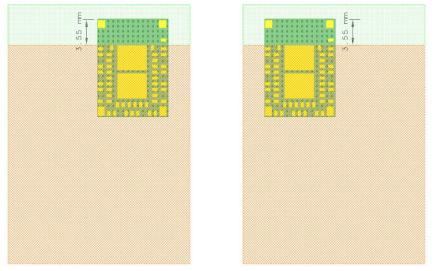

#### 1.6. Case 1 around the antenna (with no conductors placed to the left and right of antenna)

Please place the upper side of the module on the board end of the customer manufactured board to the extent that the module can be mounted. There is no problem even if it is placed in the center part of the board as in the module mounting example (1), even if it is placed on the right edge and the left edge of the board as in the module mounting example (2). However, be sure to mount the module so that there is the customer manufactured board under the antenna area.

Please place the GND surface like the example of module mounting (1) from 3.55mm below the antenna area board end of the module. Part placement and copper foil pattern placement are prohibited in areas above 3.55 mm. In addition, although it is a GND surface size, we recommend a size of 30mm x 25mm or more from the viewpoint of antenna performance.

It is a substrate material, but please choose the board thickness from 0.8mm to 1.6mm in a typical FR-4. As the board thickness is reduced and thicknesd, the antenna gain performance gradually decreases. From the viewpoint of antenna gain performance, the board thickness is recommended from 1.0 mm to 1.2 mm.

In the upper side and the upper and lower spaces of the antenna area, please do not place within 10.0 mm for metals (less than 2 mm thick) and within 5.0 mm of resins (less than 2 mm thick). In addition, antenna radiation is weakened in the direction in which metals are placed.

It is recommended, even in non-prohibited areas, to avoid placing high-permittivity materials whenever possible.

Even if the above conditions are satisfied, communication performance may decrease significantly depending on the structure of the product and the surrounding structure environment.

Example of module (1)

is the outline of the motherboard.

is the copper foil placeable area of the customer manufactured board.

Example of module (2)

is the outline of the motherboard.

is the copper foil placeable area of the customer manufactured board

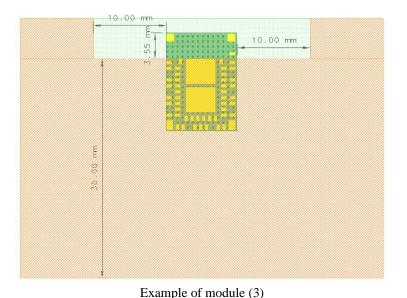

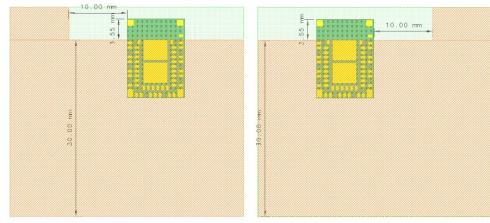

#### 1.7. Case 2 around the antenna (with conductors placed to the left and right of antenna)

Please place the upper side of the module on the board end of the customer manufactured board to the extent that the module can be mounted.

There is no problem even if it is placed in the center part of the board as shown in the module mounting example (3), even if it is placed on the right edge and the left edge of the board as in the module mounting example (4).

However, be sure to mount the module so that there is the customer manufacturing board under the antenna area.

Please place the GND surface as shown in the module mounting example (3) from 3.55mm below the antenna area board end of the module. Part placement and copper foil pattern placement are prohibited in areas above 3.55 mm and within 10 mm of the left and right antenna area edges. In addition, although it is a GND surface size, we recommend a size of 30mm x 25mm or more from the viewpoint of antenna performance.

It is a substrate material, but please choose the board thickness from 0.8mm to 1.6mm in a typical FR-4. As the board thickness is reduced and thickened, the antenna gain gradually decreases.

1.0mm to 1.2mm is recommended for board thickness.

It is recommended, even in non-prohibited areas, to avoid placing high-permittivity materials whenever possible.

In the upper side and the upper and lower spaces of the antenna area, please do not place within 10.0 mm for metals (less than 2 mm thick) and within 5.0 mm of resins (less than 2 mm thick). In addition, antenna radiation is weakened in the direction in which metals are placed.

It is also recommended that you avoid placing parts with high dielectric constants as much as possible, even in non-prohibited areas.

Even if you satisfy the above conditions, communication performance may decrease significantly depending on the structure of the product and the surrounding structure environment.

is the outline of the motherboard.

is the copper foil placeable area of the customer manufactured board

Example of module (4)

is the outline of the motherboard.

is the copper foil placeable area of the customer manufactured board

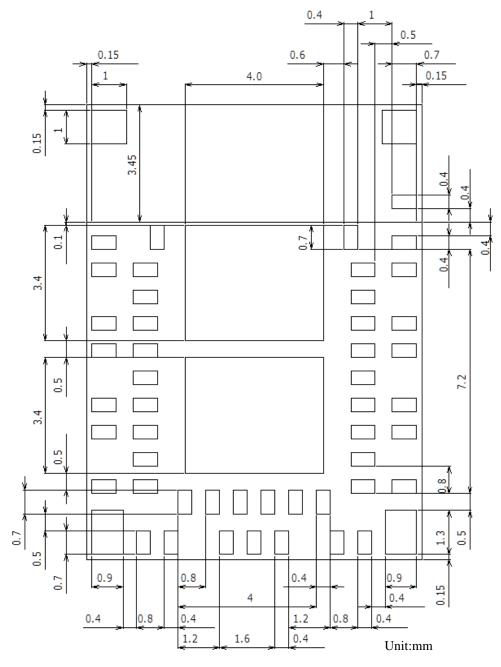

#### 2. Reference Land Pattern

Note:

The land pattern of the 53PIN and 54PIN terminals may cause air bubbles because the soldering area is large, causing voids. Depending on the void situation, please consider measures such as dividing the land pattern and changing the solder material to a low-void version.

Please fully evaluate various conditions (soldering conditions, etc.) by the customer and adjust it at the customer's responsibility. The figures in this document do not accurately show the actual shape and dimensions.

Please do not design with the value by measuring from the figure.

# Revision history

| Document No.                              | Date      | Page   |       | Remarks       |

|-------------------------------------------|-----------|--------|-------|---------------|

|                                           | 2         | Before | After |               |

| FEXK715x1_AN_PCB_<br>design_Guidelines-01 | 2020.10.1 | _      | _     | First edition |

|                                           |           |        |       |               |

|                                           |           |        |       |               |

|                                           |           |        |       |               |

|                                           |           |        |       |               |

|                                           |           |        |       |               |

|                                           |           |        |       |               |

|                                           |           |        |       |               |

|                                           |           |        |       |               |

|                                           |           |        |       |               |

|                                           |           |        |       |               |

|                                           |           |        |       |               |

|                                           |           |        |       |               |

|                                           |           |        |       |               |

|                                           |           |        |       |               |

|                                           |           |        |       |               |

|                                           |           |        |       |               |

|                                           |           |        |       |               |

|                                           |           |        |       |               |