#### お客様各位

# 資料中の「ラピステクノロジー」等名称の ローム株式会社への変更

2024 年4 月1 日をもって、ローム株式会社は、100%子会社である ラピステクノロジー株式会社を吸収合併しました。従いまして、本資料中にあります 「ラピステクノロジー株式会社」、「ラピステクノ」、「ラピス」といった表記に関しましては、全て「ローム株式会社」に読み替えて適用するものとさせていただきます。 なお、会社名、会社商標、ロゴ等以外の製品に関する内容については、変更はありません。 以上、ご理解の程よろしくお願いいたします。

2024年4月1日 ローム株式会社

# 資料中の「ラピスセミコンダクタ」等名称の ラピステクノロジー株式会社への変更

2020年10月1日をもって、ラピスセミコンダクタ株式会社のLSI事業部門は、 ラピステクノロジー株式会社に分割承継されました。従いまして、本資料中にあります 「ラピスセミコンダクタ株式会社」、「ラピスセミ」、「ラピス」といった表記に関しましては、 全て「ラピステクノロジー株式会社」に読み替えて適用するものとさせていただきます。 なお、会社名、会社商標、ロゴ等以外の製品に関する内容については、変更はありま せん。以上、ご理解の程よろしくお願いいたします。

2020年10月1日 ラピステクノロジー株式会社

Dear customer

LAPIS Semiconductor Co., Ltd. ("LAPIS Semiconductor"), on the 1<sup>st</sup> day of October, 2020, implemented the incorporation-type company split (shinsetsu-bunkatsu) in which LAPIS established a new company, LAPIS Technology Co., Ltd. ("LAPIS Technology") and LAPIS Technology succeeded LAPIS Semiconductor's LSI business.

Therefore, all references to "LAPIS Semiconductor Co., Ltd.", "LAPIS Semiconductor" and/or "LAPIS" in this document shall be replaced with "LAPIS Technology Co., Ltd."

Furthermore, there are no changes to the documents relating to our products other than the company name, the company trademark, logo, etc.

Thank you for your understanding.

LAPIS Technology Co., Ltd.

October 1, 2020

# **ML7630**

13.56MHz ワイヤレス給電用受電 LSI

#### ■ 概要

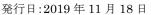

ML7630 は 13.56MHz ワイヤレス給電用受電デバイスです。ML7630 は送電側デバイス ML7631 と組み合わせることでワイヤレス給電システムを実現し、200mW の充電出力が可能です。

ML7630 は電圧電流制御が可能な充電制御 LDO、充電状態やサーミスタで電池温度を測定するための 10bit SA-ADC、充電制御機能など充電に必要な機能を 2.59mm 角の WL-CSP チップに搭載しており、ヘッドセットやイヤーパッドなどの小型ウェアラブルデバイスのワイヤレス給電に最適な LSI となっています。また NFC Forum Type 3 Tag 機能を搭載し、タッチによる Bluetooth®のペアリングなどの NFC 機能を実現することができます。

#### ■ 特長

- 充電制御 LDO

- 充電出力回路内蔵 出力電圧設定と電流制限機能を内蔵 200mW 充電出力

- ソフトウェア制御とハードウェア制御による異常検知機能(温度異常)

- 送電側への異常通知機能

- NFC 通信制御

- NFC Forum Type3 TAG 機能搭載

- 通信速度 : 212kbps (13.56MHz/64)

- TAG データ格納用 1Kbyte Data Flash

- ホストインタフェース(I<sup>2</sup>C スレーブ)

- 標準モード(100kbit/s)、ファーストモード(400kbit/s)対応

- ホストマイコンからアクセス可能なレジスタ機能

- 汎用ポート(PORT)

- 一 入出力ポート×15ch

- 逐次比較型 A/D コンバータ(SA-ADC)

- 分解能 10 ビット

- リセット

- RESET\_N 端子リセット

- 一 パワーオン検出リセット

- 一 WDT オーバーフローによるリセット

- クロック

- 低速側クロック 内蔵 RC 発振(32.768kHz)

- 高速側クロック RX0/RX1 アンテナ入力(13.56MHz)

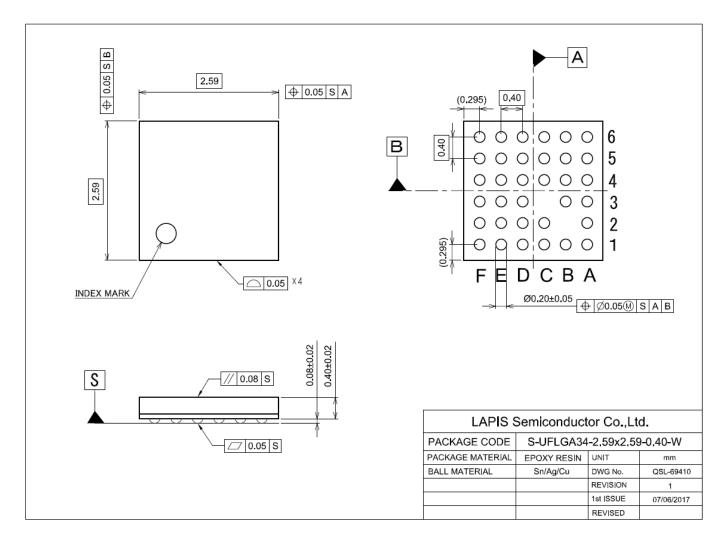

- パッケージ

- WL-CSP34pin

#### ■ ブロック図

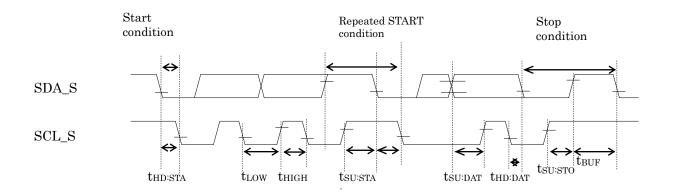

### ■ 端子配置

(Top View)

|        |        |                | •              |               |        | - |

|--------|--------|----------------|----------------|---------------|--------|---|

| P_ANT  | TEST0  | P03            | RESET_N        | P07           | P10    | A |

| RX1    |        | TEST1_N        | P05            | P06           | P13    | В |

| RX0    | VSS3   |                | P02            | TEST_<br>OUT  | VSS1   | С |

| BAT2   | BAT    | P01 /<br>SCL_S | VPP            | P12           | VSS0   | D |

| LDO1V8 | LDO1V5 | P00 /<br>SDA_S | P11            | P14           | VDD_IO | E |

| VSS4   | ISO_V  | VSS2           | P04 /<br>INT_S | P15 /<br>AIN0 | P16    | F |

| 1      | 2      | 3              | 4              | 5             | 6      |   |

(Bottom View)

| P16            | VDD_IO         | VSS0           | VSS1         | P13     | P10     | 6 |

|----------------|----------------|----------------|--------------|---------|---------|---|

| P15 /<br>AIN0  | P14            | P12            | TEST_<br>OUT | P06     | P07     | 5 |

| P04 /<br>INT_S | P11            | VPP            | P02          | P05     | RESET_N | 4 |

| VSS2           | P00 /<br>SDA_S | P01 /<br>SCL_S |              | TEST1_N | P03     | 3 |

| ISO_V          | LDO1V5         | ВАТ            | VSS3         |         | TEST0   | 2 |

| VSS4           | LDO1V8         | BAT2           | RX0          | RX1     | P_ANT   | 1 |

| F              | E              | D              | C            | В       | A       | _ |

#### ■ 端子説明

#### ● 電源・グランド・リファレンス電圧端子

| PIN No. | 端子名称   | リセット<br>時(※1) | I/O<br>(※2) | Active<br>Level | 端子機能                | 未使用時<br>の処理 |

|---------|--------|---------------|-------------|-----------------|---------------------|-------------|

| D6      | VSS0   |               |             |                 |                     |             |

| C6      | VSS1   |               |             |                 |                     |             |

| F3      | VSS2   | _             | _           | _               | グランド                | _           |

| C2      | VSS3   |               |             |                 |                     |             |

| F1      | VSS4   |               |             |                 |                     |             |

| E6      | VDD_IO | _             | ı           | ı               | ロジック IO 電源          | _           |

| E2      | LDO1V5 | H(A)          | ОА          | 1               | コア用 1.5V 電源出力       | _           |

| E1      | LDO1V8 | H(A)          | Оа          | _               | ADC 用 1.8V 電源出力     | _           |

| A1      | P_ANT  | _             | 1           | 1               | 整流入力                | _           |

| F2      | ISO_V  | _             | _           | _               | ロジック IO 電源(ホスト通信用)  | _           |

| D2      | BAT    | Z             | Оа          | ı               | 充電電圧出力              | _           |

| D1      | BAT2   | _             | lΑ          | _               | 電池電圧観測/Flash 書き込み電源 | GND         |

#### ● アナログ信号端子

| PIN No. | 端子名称 | リセット<br>時(※1) | I/O<br>(※2) | Active<br>Level | 端子機能              | 未使用時<br>の処理 |

|---------|------|---------------|-------------|-----------------|-------------------|-------------|

| C1      | RX0  | _             | lΑ          | _               | 磁界(プラス側) / データ受信  | ı           |

| B1      | RX1  | _             | lΑ          | _               | 磁界(マイナス側) / データ受信 | _           |

#### ● リセット端子

| PIN No. | 端子名称    | リセット<br>時(※1) | I/O<br>(※2) | 供給電源   | Active<br>Level | 端子機能   | 未使用時<br>の処理 |

|---------|---------|---------------|-------------|--------|-----------------|--------|-------------|

| A4      | RESET_N | PU            | 1           | VDD_IO | L               | リセット端子 | オープン        |

#### ● 汎用端子

FW Ver.によって設定が異なるため、詳細はアプリケーションノートをご参照ください。

| PIN No. | 端子名称        | リセット<br>時(※1) | I/O<br>(※2)        | 供給電源   | Active<br>Level | 端子機能                                           |

|---------|-------------|---------------|--------------------|--------|-----------------|------------------------------------------------|

| E3      | P00 / SDA_S | Z             | I/O                | ISO_V  | _               | 入出カポート<br>HostIF(I <sup>2</sup> C スレーブ) データ入出カ |

| D3      | P01 / SCL_S | Z             | I/O                | ISO_V  | -               | 入出カポート<br>HostIF(I <sup>2</sup> C スレーブ) クロック入力 |

| C4      | P02         | Z             | I/O                | VDD_IO | _               | 入出力ポート                                         |

| A3      | P03         | Z             | I/O                | VDD_IO | _               | 入出力ポート                                         |

| F4      | P04 / INT_S | Z             | I/O                | ISO_V  | _               | 入出力ポート<br>HostIF INT 出力                        |

| B4      | P05         | Z             | I/O                | VDD_IO | _               | 入出力ポート                                         |

| B5      | P06         | Z             | I <sub>DA</sub> /O | VDD_IO | _               | 入出力ポート                                         |

| A5      | P07         | Z             | I <sub>DA</sub> /O | VDD_IO | _               | 入出力ポート                                         |

| A6      | P10         | Z             | I/O                | VDD_IO | _               | 入出力ポート                                         |

| E4      | P11         | Z             | I/O                | ISO_V  | _               | 入出力ポート                                         |

| D5      | P12         | Z             | I/O                | ISO_V  | _               | 入出力ポート                                         |

| B6      | P13         | Z             | I/O                | VDD_IO | _               | 入出力ポート                                         |

| E5      | P14         | Z             | I/O                | VDD_IO | _               | 入出力ポート                                         |

| F5      | P15 / AIN0  | Z             | I <sub>DA</sub> /O | VDD_IO | _               | 入出力ポート/AD 入力                                   |

| F6      | P16         | Z             | I/O                | VDD_IO | _               | 入出力ポート                                         |

#### ● テスト端子

| PIN No. | 端子名称     | リセット<br>時(※1) | I/O<br>(※2) | 供給電源   | Active<br>Level | 端子機能           | 未使用時<br>の処理 |

|---------|----------|---------------|-------------|--------|-----------------|----------------|-------------|

| A2      | TEST0    | PD            | I/O         | VDD_IO | Н               | テスト用/デバッガ用端子   | オープン        |

| В3      | TEST1_N  | PU            | ı           | VDD_IO | L               | テスト用/デバッガ用端子   | オープン        |

| D4      | VPP      | _             | lΑ          | _      | _               | Flash テスト用電源端子 | オープン        |

| C5      | TEST_OUT | L(A)          | 0           | VDD_IO | _               | テスト出力端子        | オープン        |

(※1) リセット時: リセット状態で記載する状態を表しています。

| リセット時  | L(O) | : | 出力状態かつ"L"レベル出力 |

|--------|------|---|----------------|

| 端子状態定義 | H(O) | : | 出力状態かつ"H"レベル出力 |

|        | L(A) | : | アナログ L レベル出力   |

|        | H(A) | : | アナログ Hレベル出力    |

|        | PU   | : | Pull-Up        |

|        | PD   | : | Pull-Down      |

|        | Z    | : | フローティング状態      |

(※2) I/O: I/O 定義に関しましては、下記の略称を使用しております。

| I/O 定義 | lA                 | : | アナログ入力端子             |

|--------|--------------------|---|----------------------|

|        | ОА                 | : | アナログ出力端子             |

|        | I                  | : | デジタル入力端子             |

|        | I/O                | : | 双方向端子                |

|        | I <sub>DA</sub> /O | : | 双方向端子、入力はデジタルとアナログ共用 |

|        | 0                  | : | デジタル出力端子             |

#### ■ 電気的特性

#### ● 絶対最大定格

| 項目       | 記号                 | 条件              | 定格值                       | 単位 |

|----------|--------------------|-----------------|---------------------------|----|

| 電源電圧     | VDD_IO             | Ta=25°C         | -0.3~+6.5                 | V  |

|          | ISO_V              | Ta=25°C         | -0.3~+6.5                 | V  |

|          | P_ANT              | Ta=25°C         | -0.3~+6.5                 | V  |

|          | BAT2               | Ta=25°C         | -0.3~+6.5                 | V  |

| コア電源電圧   | LDO1V5             | Ta=25°C         | -0.3~+2.0                 | V  |

| アナログ電源電圧 | LDO1V8             | Ta=25°C         | -0.3~+6.5                 | V  |

| 入力電圧     | VDIN               | Ta=25℃、デジタルポート  | -0.3~V <sub>DD</sub> +0.3 | V  |

|          |                    | Ta=25°C、RX0/RX1 | 12                        | V  |

| 入力電流     | li                 | Ta=25℃、デジタルポート  | -10~+10                   | mA |

|          | I <sub>P_ANT</sub> | Ta=25°C         | 100                       | mA |

| 出力電圧     | Vdo                | Ta=25℃、デジタルポート  | -0.3~VDD+0.3              | V  |

| デジタル出力電流 | IDO                | Ta=25°C         | -12~+20                   | mA |

| 許容損失     | PD                 | Ta=25°C         | 0.9                       | W  |

| 保存温度     | Tstg               | _               | -55 <b>~</b> +150         | °C |

VDD: VDD\_IO 系の端子は VDD\_IO 電圧、ISO\_V 系の端子は ISO\_V 電圧

#### ● 推奨動作条件

| 項目              | 記号                  | 条件  | 最小            | 標準    | 最大            | 単位  |

|-----------------|---------------------|-----|---------------|-------|---------------|-----|

| 動作電圧            | VDD_IO              | _   | 1.8           | ı     | 5.5           | V   |

|                 | ISO_V               | _   | 1.8           | ı     | 5.5           | V   |

|                 | P_ANT               | 通信時 | 2.0           | 5.0   | 5.5           | V   |

|                 |                     | 充電時 | -             | ı     | 5.5           | V   |

| 入力電流            | P_ANT               | 通信時 | 0.5           | _     | _             | mA  |

|                 |                     | 充電時 | _             | 1     | 80            | mA  |

| 動作温度            | Ta1                 | 通信時 | -40           | +25   | +85           | °C  |

|                 | Ta2                 | 充電時 | -10           | +25   | +50           | °C  |

| LDO1V5 外付けキャパシタ | C <sub>LDO1V5</sub> | _   | Typ<br>-10%   | 2.2   | Typ<br>+10%   | μF  |

| P_ANT 外付けキャパシタ  | C <sub>PANT</sub>   | _   | Typ<br>-10%   | 2.2   | Typ<br>+10%   | μF  |

| LDO1V8 外付けキャパシタ | C <sub>LDO1V8</sub> | _   | Typ<br>-10%   | 0.47  | Typ<br>+10%   | μF  |

| VDD_IO 外付けキャパシタ | C <sub>VDDIO</sub>  | _   | Typ<br>-10%   | 0.1   | Typ<br>+10%   | μF  |

| ISO_V 外付けキャパシタ  | C <sub>ISOV</sub>   | _   | Typ<br>-10%   | 0.1   | Typ<br>+10%   | μF  |

| アンテナ入力周波数       | F <sub>ANT</sub>    | _   | Typ<br>-0.05% | 13.56 | Typ<br>+0.05% | MHz |

#### ● フラッシュメモリ動作条件

| 項目       | 記号        | 条件       | 範囲              | 単位 |

|----------|-----------|----------|-----------------|----|

| 動作温度(周囲) | $T_OP$    | 書き込み/消去時 | -20 to +60      | °C |

| 動作電圧     | P_ANT     | 書き込み/消去時 | 2.7 to 5.5      | V  |

| 書き換え回数   | $C_{EPD}$ |          | 10,000          | □  |

| 消去単位     | 1         | セクタ消去    | 1               | KB |

| 消去時間(最大) | ı         | セクタ消去    | 100             | ms |

| 書込み単位    | ı         | Г        | 1 word (2 byte) | -  |

#### ● RF 特性

(VDD\_IO=1.8 to 5.5V, P\_ANT=2.0 to 5.5V, VSS=0V, Ta=-40 to +85°C)

| 項目      | 記号                | 条件      | 最小  | 標準  | 最大  | 単位   |

|---------|-------------------|---------|-----|-----|-----|------|

| 入力レベル   | $V_{RX1}$         | RX0/RX1 | 2.0 | _   | 5.5 | V    |

| 入力データ振幅 | $V_{RX2}$         | RX0/RX1 | 50  | ı   | ı   | mV   |

| 通信速度    | F <sub>RX</sub>   | RX0/RX1 |     | 212 |     | kbps |

| 負荷変調抵抗  | R <sub>MODR</sub> | RX0/RX1 | 105 | _   | 220 | Ω    |

#### ● 給電特性

(VDD\_IO=1.8 to 5.5V, P\_ANT=2.0 to 5.5V, VSS=0V, Ta=-40 to +85°C)

| 項目           | 記号              | 条件       | 最小                    | 標準  | 最大 | 単位 |

|--------------|-----------------|----------|-----------------------|-----|----|----|

| BAT 端子出力電圧   | $V_{BAT}$       | 無負荷時     | -                     | 5.0 | 1  | V  |

| BAT 端子出力負荷特性 | $V_{BAT\_LOAD}$ | 45mA 負荷時 | V <sub>BAT</sub> -0.5 | -   | I  | V  |

BAT 端子出力電圧の設定方法についてはアプリケーションノートをご参照ください。

#### ● 通知特性

(VDD\_IO=1.8 to 5.5V, P\_ANT=2.0 to 5.5V, VSS=0V, Ta=-40 to +85°C)

| 項目           | 記号          | 条件    | 最小 | 標準  | 最大  | 単位 |

|--------------|-------------|-------|----|-----|-----|----|

| P_ANT 入力リミッタ | $V_{PANT1}$ | 通常時   | ı  | I   | 5.5 | V  |

|              | $V_{PANT2}$ | 異常通知時 | ı  | 3.0 | I   | V  |

#### ● 発振特性

(VDD\_IO=1.8 to 5.5V, P\_ANT=2.0 to 5.5V, VSS=0V)

|                             |                  | , = - |     |        |     |     |

|-----------------------------|------------------|-------|-----|--------|-----|-----|

| 項目                          | 記 <del>号</del>   | 条件    | 最小  | 標準     | 最大  | 単位  |

| 低速内蔵 RC 発振周波数 <sup>*1</sup> | f <sub>LCR</sub> |       | -5% | 32.768 | +5% | kHz |

\*1:1024 サイクルの平均値です。

#### ● SA-ADC 特性

(VDD\_IO=1.8 to 5.5V, P\_ANT=2.0 to 5.5V, VSS=0V, Ta=-40 to +85°C)

|             |           | ` = ' =                 |    | ,   | ,  | ,   |

|-------------|-----------|-------------------------|----|-----|----|-----|

| 項目          | 記号        | 条件                      | 最小 | 標準  | 最大 | 単位  |

| 分解能         | n         | _                       | _  | 10  | -  | bit |

| 積分非直線性誤差    | INL       | LDO1V8=1.8V             | -6 | _   | +6 | LSB |

| 微分非直線性誤差    | DNL       | LDO1V8=1.8V             | -6 | _   | +6 | LSB |

| ゼロスケール誤差    | ZSE       | _                       | -6 | _   | +6 | LSB |

| フルスケール誤差    | FSE       | _                       | -6 | _   | +6 | LSB |

| 入力インピーダンス   | RI        | _                       | _  | 6k  | ı  | Ω   |

| SA-ADC 基準電位 | $V_{REF}$ | LDO1V8=V <sub>REF</sub> | _  | 1.8 | _  | V   |

#### ● リセット特性

(VDD\_IO=1.8 to 5.5V, P\_ANT=2.0 to 5.5V, VSS=0V, Ta=-40 to +85°C)  $\mid$

| 項目                | 記号                | 条件 | 最小  | 標準 | 最大  | 単位 |

|-------------------|-------------------|----|-----|----|-----|----|

| RESET_N パルス幅      | P <sub>RST</sub>  | _  | 200 | _  | _   | μs |

| RESET_N ノイズ除去パルス幅 | P <sub>NRST</sub> | _  | _   | _  | 0.3 | μs |

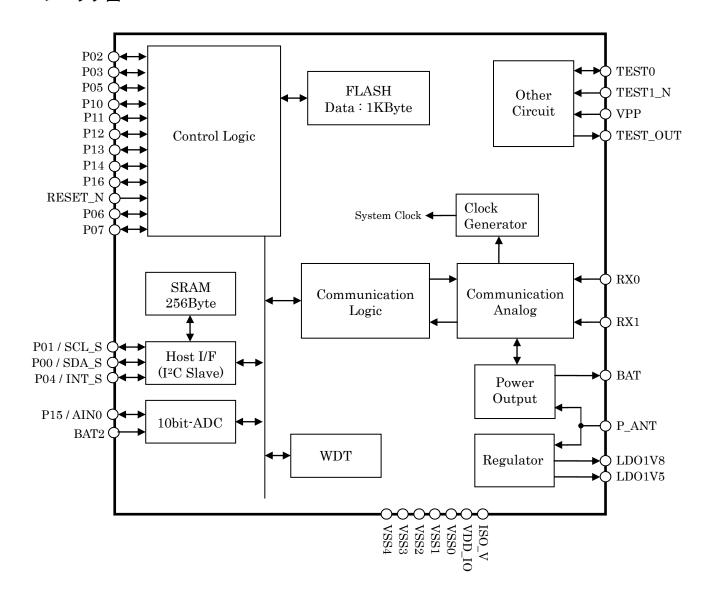

#### ● 交流特性 (I<sup>2</sup>C Bus Interface: Standard Mode 100 kHz)

(VDD\_IO/ISO\_V=1.8 to 5.5V, P\_ANT=2.0 to 5.5V, VSS=0V, Ta=-40 to +85°C)

| 項目                                               | 記号                  | 条件 | 最小   | 標準 | 最大  | 単位  |

|--------------------------------------------------|---------------------|----|------|----|-----|-----|

| SCL_S clock frequency                            | f <sub>SCL</sub>    | _  | -    | -  | 100 | kHz |

| SCL_S hold time (start/repeated start condition) | t <sub>HD:STA</sub> | -  | 4.0  | _  | _   | μs  |

| SCL_S "L" level time                             | $t_{LOW}$           | _  | 4.7  | -  | -   | μs  |

| SCL_S "H" level time                             | t <sub>HIGH</sub>   | _  | 4.0  | -  | -   | μs  |

| SCL_S setup time (repeated start condition)      | t <sub>SU:STA</sub> | -  | 4.7  | _  | _   | μs  |

| SDA_S hold time                                  | t <sub>HD:DAT</sub> | _  | 0    | -  | -   | μs  |

| SDA_S setup time                                 | t <sub>SU:DAT</sub> | _  | 0.25 | -  | _   | μs  |

| SDA_S setup time<br>(P: Stop condition)          | t <sub>su:sto</sub> | -  | 4.0  | _  | _   | μs  |

| Bus free time                                    | t <sub>BUF</sub>    | _  | 4.7  | _  | _   | μs  |

#### ● 交流特性 (I<sup>2</sup>C Bus Interface: Fast Mode 400 kHz)

(VDD\_IO/ISO\_V=1.8 to 5.5V, P\_ANT=2.0 to 5.5V, VSS=0V, Ta=-40 to +85°C)

|                                                  | \ -                 | ,,,,,,,,, _ |     | ,  | ,   | ,   |

|--------------------------------------------------|---------------------|-------------|-----|----|-----|-----|

| 項目                                               | 記号                  | 条件          | 最小  | 標準 | 最大  | 単位  |

| SCL_S clock frequency                            | f <sub>SCL</sub>    | _           | _   | _  | 400 | kHz |

| SCL_S hold time (start/repeated start condition) | t <sub>HD:STA</sub> | -           | 0.6 | _  | _   | μs  |

| SCL_S "L" level time                             | $t_{LOW}$           | _           | 1.3 | -  | -   | μs  |

| SCL_S "H" level time                             | t <sub>HIGH</sub>   | _           | 0.6 | _  | _   | μs  |

| SCL_S setup time (repeated start condition)      | t <sub>SU:STA</sub> | -           | 0.6 | _  | _   | μs  |

| SDA_S hold time                                  | t <sub>HD:DAT</sub> | _           | 0   | _  | _   | μs  |

| SDA_S setup time                                 | t <sub>SU:DAT</sub> | _           | 0.1 | -  | _   | μs  |

| SDA_S setup time<br>(P: Stop condition)          | t <sub>SU:STO</sub> | -           | 0.6 | -  | _   | μs  |

| Bus free time                                    | t <sub>BUF</sub>    | _           | 1.3 | _  | _   | μs  |

$I^2C$  スレーブは他のデバイスと共通の  $I^2C$  バスに接続する場合,他のデバイスの通信を阻害する恐れがございますので、本 LSI の  $ISO_V$  電源を落とさないようにしてください。磁界による  $P_ANT$  電源がない場合でも  $ISO_V$  電源を印加していれば、 $Hi^2$  状態を維持します。

#### ● IO 特性

(特に指定のない場合は、VDD\_IO=1.8 to 5.5V, P\_ANT=2.0 to 5.5V, VSS=0V, Ta=-40 to +85℃) │

| 項目                                                       | 記号                | 合は、VDD_IO=1.8 to 5.5V, P_AN<br>条件                           | 最小                   | 標準   | 最大                   | 単位 |

|----------------------------------------------------------|-------------------|-------------------------------------------------------------|----------------------|------|----------------------|----|

| <br>出力電圧 1                                               | VOH1              | IOH=-1.0mA                                                  | V <sub>DD</sub> -0.5 | _    | _                    | V  |

| (P00-P07, P10-P16)                                       | VOL1              | IOL=+0.5mA                                                  | _                    | _    | 0.4                  | V  |

| 出力電圧 2<br>(P00-P07, P10-P16)                             | VOL2              | 2.7V≦V <sub>DD</sub> ≦5.5V<br>IOL=+5.0mA                    | _                    | _    | 0.6                  | V  |

| _(LED 端子)                                                |                   | IOL=+2.0mA                                                  | _                    | -    | 0.4                  | V  |

| 出力電圧 3<br>(SCL_S,SDA_S)<br>_(I <sup>2</sup> C 端子)        | VOL3              | IOL3= +3mA (I <sup>2</sup> Cspec)<br>(VDD_IO ≧2V, ISO_V≧2V) | -                    | -    | 0.4                  | V  |

| 出力電圧 4<br>(SCL_S,SDA_S)<br>_(I <sup>2</sup> C 端子)        | VOL4              | IOL4= +2mA (I <sup>2</sup> Cspec)<br>(VDD_IO <2V, ISO_V<2V) | -                    | ı    | V <sub>DD</sub> ×0.2 | V  |

| 出力リーク 1                                                  | IOOH1             | VOH=V <sub>DD</sub> (at high impedance)                     | _                    | ı    | 1                    | μΑ |

| (P00-P07, P10-P16,<br>SCL_S, SDA_S)                      | IOOL1             | L1 VOL=VSS (at high impedance)                              |                      | ı    | _                    | μΑ |

| 入力電流 1                                                   | IIH1              | VIH1=V <sub>DD</sub>                                        | _                    | 1    | 1                    | μΑ |

| (RESET_N, TEST1_N)                                       | IIL1              | VIL1=VSS                                                    | -900                 | -300 | -20                  | μΑ |

| 入力電流 2                                                   | IIH2              | VIH2=V <sub>DD</sub>                                        | 20                   | 300  | 900                  | μА |

| (TEST0)                                                  | IIL2              | VIL2=VSS                                                    | -1                   | I    | -                    | μΑ |

|                                                          | IIH3              | VIH3=V <sub>DD</sub> (プルダウン時)                               | 1                    | 15   | 200                  | μΑ |

| 入力電流 3                                                   | IIL3              | VIL3=VSS (プルアップ時)                                           | -200                 | -15  | -1                   | μА |

| (P00-P07, P10-P16)                                       | IIH3Z             | VIH3=V <sub>DD</sub> (at high impedance)                    | _                    | _    | 1                    | μА |

|                                                          | IIL3Z             | VIL3=VSS (at high impedance)                                | -1                   | -    | _                    | μА |

| 入力電圧 1                                                   | VIH1              | _                                                           | 0.7×V <sub>DD</sub>  | _    | $V_{DD}$             | V  |

| (RESET_N, TEST0, TEST1_N, P00-P07, P10-P16)              |                   |                                                             | 0                    | 1    | 0.3×V <sub>DD</sub>  | V  |

| 入力端子容量<br>(RESET_N, TEST0, TEST1_N,<br>P00-P07, P10-P16) | CIN               | f=10kHz<br>Vrms=50mV<br>Ta=25°C                             | -                    | 10   | _                    | pF |

| リーク電流                                                    | I <sub>ISOV</sub> | ISO_V 端子に電位供給し、<br>磁界入力無し時の端子リーク                            | _                    | 100  | _                    | nA |

V<sub>DD</sub>: VDD\_IO 系の端子は VDD\_IO 電圧、ISO\_V 系の端子は ISO\_V 電圧

標準値は Ta=25°C, VDD\_IO=3.0V のとき

#### ■ パッケージ寸法図

### ■ 改版履歴

| 1°+ - 4>.1 No | <b>※</b> 仁口 | ページ              |                  | 亦正中宗                                                  |

|---------------|-------------|------------------|------------------|-------------------------------------------------------|

| ドキュメント No.    | 発行日         | 改版前              | 改版後              | 変更内容                                                  |

| PJDL7630-01   | 2016.09.27  | 1                | 1                | 暫定初版発行                                                |

| FJDL7630-01   | 2018.03.23  | -                | _                | 正式初版発行                                                |

| FJDL7630-02   | 2019.01.15  | 9                | 9                | IO 端子の説明を修正                                           |

|               | 2019.11.18  | 1<br>2<br>3<br>4 | 1<br>2<br>3<br>4 | 未使用ブロックの削除                                            |

|               |             | 4<br>5           | 4<br>5           | リセット端子追加<br>その他の端子を汎用端子に変更<br>汎用端子はアプリケーションノート参照の注記追加 |

|               |             | 11<br>12         | -                | サンプル回路例の削除<br>(FW に依存するためアプリケーションノートへ記載)              |

|               |             | 3                | 3                | TOP VIEW を追加                                          |

|               |             | 4                | 4                | BAT2 の未使用時の処理を追記                                      |

|               |             | 2                | 2                | BAT2 の接続先を ADC に変更                                    |

|               |             | 7                | 7                | BAT 出力電圧の説明を修正                                        |

#### ご注意

- 1) 本資料の記載内容は改良などのため予告なく変更することがあります。

- 2) ラピスセミコンダクタは常に品質・信頼性の向上に取り組んでおりますが、半導体製品は種々の要因で故障・誤作動する可能性があります。

- 万が一、本製品が故障・誤作動した場合であっても、その影響により人身事故、火災損害等が起こらないようご使用機器でのディレーティング、冗長設計、延焼防止、バックアップ、フェイルセーフ等の安全確保をお願いします。定格を超えたご使用や使用上の注意書が守られていない場合、いかなる責任もラピスセミコンダクタは負うものではありません。

- 3) 本資料に記載されております応用回路例やその定数などの情報につきましては、本製品の標準的な動作や使い方を説明するものです。したがいまして、量産設計をされる場合には、外部諸条件を考慮していただきますようお願いいたします。

- 4) 本資料に記載されております技術情報は、本製品の代表的動作および応用回路例などを示したものであり、それをもって、当該技術情報に関するラピスセミコンダクタまたは第三者の知的財産権その他の権利を許諾するものではありません。したがいまして、上記技術情報の使用に起因して第三者の権利にかかわる紛争が発生した場合、ラピスセミコンダクタはその責任を負うものではありません。

- 5) 本製品は、一般的な電子機器(AV機器、OA機器、通信機器、家電製品、アミューズメント機器など)および本資料に明示した用途への使用を意図しています。

- 6) 本資料に掲載されております製品は、耐放射線設計はなされておりません。

- 7) 本製品を下記のような特に高い信頼性が要求される機器等に使用される際には、ラピスセミコンダクタへ必ずご連絡の上、 承諾を得てください。

- ・輸送機器(車載、船舶、鉄道など)、幹線用通信機器、交通信号機器、防災・防犯装置、安全確保のための装置、医療機器、サーバー、太陽電池、送電システム

- 8) 本製品を極めて高い信頼性を要求される下記のような機器等には、使用しないでください。 ・航空宇宙機器、原子力制御機器、海底中継機器

- 9) 本資料の記載に従わないために生じたいかなる事故、損害もラピスセミコンダクタはその責任を負うものではありません。

- 10) 本資料に記載されております情報は、正確を期すため慎重に作成したものですが、万が一、当該情報の誤り・誤植に起因する損害がお客様に生じた場合においても、ラピスセミコンダクタはその責任を負うものではありません。

- 11) 本製品のご使用に際しては、RoHS 指令など適用される環境関連法令を遵守の上ご使用ください。お客様がかかる法令 を遵守しないことにより生じた損害に関して、ラピスセミコンダクタは一切の責任を負いません。本製品の RoHS 適合性な どの詳細につきましては、セールス・オフィスまでお問合せください。

- 12) 本製品および本資料に記載の技術を輸出又は国外へ提供する際には、「外国為替及び外国貿易法」、「米国輸出管理規則」など適用される輸出関連法令を遵守し、それらの定めにしたがって必要な手続を行ってください。

- 13) 本資料の一部または全部をラピスセミコンダクタの許可なく、転載・複写することを堅くお断りします。

Copyright 2016-2019 LAPIS Semiconductor Co., Ltd.

## ラピスセミコンダクタ株式会社

〒222-8575 神奈川県横浜市港北区新横浜 2-4-8 http://www.lapis-semi.com